1.本发明的实施方式总体涉及信号生成电路及图像形成装置。

背景技术:

2.作为用于电子照相方式的打印机的打印头,存在排列有多个led(light

‑

emitting diode:发光二极管)或有机el(electro

‑

luminescence:电致发光)等发光元件的打印头。另外,作为这样的打印头的一种存在clk同步式打印头,该clk同步式打印头使用传送图像数据所需要的时钟信号(传送clk)、以及开始发光定时用的信号(下面称为“sync”)和用于调整发光时间的时钟信号(下面称为“sync_clk”)。clk同步式打印头由于以搭载的ic(integrated circuit:集成电路)的动作速度、消耗电力或发热等为原因而受到制约,输入sync_clk频率存在上限。然而,sync_clk频率越低,与sync周期的理想值的偏差越大,颜色偏移量也越大。

技术实现要素:

3.[发明所要解决的课题]

[0004]

本发明的实施方式所要解决的课题是提供能够不提高sync_clk频率而使sync周期接近理想值的信号生成电路及图像形成装置。

[0005]

[用于解决课题的手段]

[0006]

实施方式中的信号生成电路具备生成部、期间更改部以及输出部。生成部对第一时钟信号进行分频而生成第二时钟信号,生成定时信号,该定时信号的周期是所述第二时钟信号的规定数量的波的周期的合计。期间更改部通过更改所述第二时钟信号的高电平期间和低电平期间中的至少任一期间的长度来更改所述定时信号的周期。输出部输出所述第二时钟信号和所述定时信号。

[0007]

实施方式中的信号生成电路,具备:生成部,对第一时钟信号进行分频而生成第二时钟信号,并且,生成定时信号,所述定时信号的周期是所述第二时钟信号的规定数量的波的周期的合计;更改部,通过更改所述第一时钟信号的频率,来更改所述第二时钟信号和所述定时信号的周期;以及输出部,输出所述第二时钟信号和所述定时信号。

[0008]

实施方式中的图像形成装置,具备:生成部,对第一时钟信号进行分频而生成第二时钟信号,并且,生成定时信号,所述定时信号的周期是所述第二时钟信号的规定数量的波的周期的合计;期间更改部,通过更改所述第二时钟信号的高电平期间和低电平期间中的至少任一期间的长度来更改所述定时信号的周期;以及发光部,基于所述第二时钟信号、所述定时信号和图像信号发射光。

[0009]

实施方式中的图像形成装置,具备:生成部,对第一时钟信号进行分频而生成第二时钟信号,并且,生成定时信号,所述定时信号的周期是所述第二时钟信号的规定数量的波的周期的合计;更改部,通过更改所述第一时钟信号的频率和所述规定数量,来更改所述第二时钟信号和所述定时信号的周期;以及控制部,确定所述第一时钟信号的频率和所述规

定数量。

附图说明

[0010]

图1为表示第一实施方式和第二实施方式所涉及的图像形成装置的构成的一例的图。

[0011]

图2为放大示出图1中的图像形成部和打印头及其周边构造的概要图。

[0012]

图3为表示图1中的图像形成装置的主要部分电路构成的一例的框图。

[0013]

图4为示出图3中的信号生成电路的主要部分电路构成等的第一实施方式所涉及的框图。

[0014]

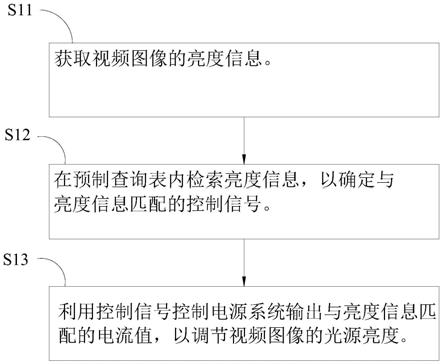

图5为示出基于图3中的处理器的第一实施方式所涉及的处理的一例的流程图。

[0015]

图6为示出第一实施方式所涉及的内部clk、sync_clk及sync的例子的时序图。

[0016]

图7为示出第一实施方式的变形例所涉及的内部clk、sync_clk以及sync的例子的时序图。

[0017]

图8为示出第一实施方式的变形例所涉及的内部clk、sync_clk以及sync的例子的时序图。

[0018]

图9为示出图3中的信号生成电路的主要部分电路构成等的、第二实施方式所涉及的框图。

[0019]

图10为示出通过图3中的处理器进行的第二实施方式所涉及的处理的一例的流程图。

[0020]

图11为示出第二实施方式所涉及的内部clk、sync_clk以及sync的例子的时序图。

[0021]

图12为示出用于确定设定值以及内部clk频率的表的一例的图。

[0022]

图13为示出用于确定设定值以及内部clk频率的表的一例的图。

[0023]

附图标记说明:

[0024]

100:图像形成装置;101:打印机;103:操作面板;106:供纸辊;108、108c、108k、108m、108y:图像形成部;109、109c、109k、109m、109y:打印头;110:转印带;111:二次转印辊;112:定影部;113:双面单元;114:排纸托盘;120:控制部;121:处理器;122:rom;123:ram;124:辅助存储设备;125:信号生成电路;131:通信i/f;132:驱动部;1081:感光鼓;1082:带电充电器;1083:显影器;1084:一次转印辊;1094:光源;1251:时钟生成部;1252:打印头i/f;1253:处理器i/f。

具体实施方式

[0025]

下面,使用附图来说明几个实施方式所涉及的图像形成装置。需要说明的是,有时在用于下面的实施方式的说明的各附图中适当更改各部分的比例尺。另外,在用于下面的实施方式的说明的各附图中,为了便于说明,有时以省略构成的方式示出。另外,在各附图和本说明书中,相同的符号表示相同的要素。

[0026]

[第一实施方式]

[0027]

图1为示出第一实施方式所涉及的图像形成装置100的主要部分构成的一例的框图。

[0028]

图像形成装置100例如是mfp(multifunction peripheral:多功能外围设备)、复

印机、打印机或传真机等。不过,下面假设图像形成装置100为mfp来进行说明。图像形成装置100例如具备印刷功能、扫描功能、复印功能以及传真功能等。印刷功能是使用色调剂等对图像形成介质p等形成图像的功能。图像形成介质p例如是片状的纸等。扫描功能是从形成有图像的原稿等读取图像的功能。复印功能是使用印刷功能在图像形成介质p上印刷使用扫描功能从原稿等读取的图像的功能。作为一例,图像形成装置100包括:打印机101、扫描仪102和操作面板103。

[0029]

打印机101具备印刷功能。打印机101包括:供纸托盘104、手动托盘105、供纸辊106、色调剂盒107、图像形成部108、打印头109、转印带110、二次转印辊111、定影部112、双面单元113及排纸托盘114。

[0030]

扫描仪102从原稿读取图像。扫描仪102例如是具备ccd(charge

‑

coupled device:电荷耦合器件)图像传感器等摄像元件的光学缩小方式。或者,扫描仪102为具备cmos(complementary metal

‑

oxide

‑

semiconductor:互补金属氧化物半导体)图像传感器等摄像元件的接触式传感器(cis(contact image sensor:接触式图像传感器))方式。或者,扫描仪102也可以为其他公知方式的。

[0031]

操作面板103具备在图像形成装置100与图像形成装置100的操作者之间进行输入输出的人机接口等。操作面板103例如具备用于该操作者操作的按钮和触摸面板等。该触摸面板例如层叠有液晶显示器或有机el显示器等显示器和基于触摸输入的指示设备。因此,该按钮和触摸面板作为接受由该操作者进行的操作的输入设备发挥功能。另外,该触摸面板所具备的显示器作为对该操作者通知各种信息的显示设备发挥功能。

[0032]

供纸托盘104收纳用于印刷的图像形成介质p。

[0033]

手动托盘105为用于手动插入图像形成介质p的台板。

[0034]

供纸辊106通过电机的作用而进行旋转,由此从供纸托盘104或手动托盘105送出收纳于供纸托盘104或手动托盘105的图像形成介质p。

[0035]

色调剂盒107储存有用于供给至图像形成部108c的色调剂等。图像形成装置100具备一个或多个色调剂盒107。作为一例,如图1所示图像形成装置100具备:色调剂盒107c、色调剂盒107m、色调剂盒107y以及色调剂盒107k这四个色调剂盒107。色调剂盒107c、色调剂盒107m、色调剂盒107y以及色调剂盒107k分别储存与cmyk(青色、品红色、黄色以及黑色)中的各种颜色对应的色调剂。需要说明的是,色调剂盒107储存的色调剂的颜色并不限于cmyk中的各种颜色,也可以是其他颜色。

[0036]

图像形成装置100具备一个或多个图像形成部108。作为一例,如图1所示图像形成装置100具备:图像形成部108c、图像形成部108m、图像形成部108y以及图像形成部108k这四个图像形成部108。图像形成部108c、图像形成部108m、图像形成部108y以及图像形成部108k分别利用与cmyk中的各种颜色对应的色调剂形成图像。

[0037]

图像形成装置100具备一个或多个打印头109。作为一例,如图1所示,图像形成装置100具备:打印头109c、打印头109m、打印头109y以及打印头109k这四个打印头109。打印头109c、打印头109m、打印头109y以及打印头109k分别与对应的cmyk中的各种颜色对应。

[0038]

打印头109通过照射基于对应的颜色分量的图像信号的曝光光,而在图像形成部108形成静电潜像。

[0039]

转印带110例如是环状的带,能够通过辊的作用而进行旋转。转印带110通过进行

旋转而将从各图像形成部108c转印的图像输送至二次转印辊111的位置。

[0040]

基于图2来进一步说明图像形成部108和打印头109。图2为放大示出图像形成部108和打印头109及其周边构造的概要图。需要说明的是,在图2中还示出了正交坐标系的坐标轴x、y及z。图像形成部108例如具有:感光鼓1081、带电充电器1082、显影器1083、一次转印辊1084、清洁器1085以及刮刀1086。

[0041]

感光鼓1081是配置成外周面与转印带110接触,并能够以与z轴平行的旋转轴为中心进行旋转的辊。感光鼓1081通过驱动机构以与转印带110相同的圆周速度沿图示箭头方向(顺时针方向)旋转。作为一例,相邻的感光鼓1081与感光鼓1081相距90[mm]。需要说明的是,该距离为感光鼓1081的中心之间的距离。因此,作为一例,图像形成部108y的感光鼓1081与图像形成部108k的感光鼓1081相距270[mm]。

[0042]

带电充电器1082使感光鼓1081的表面均匀带电。

[0043]

显影器1083向形成于感光鼓1081的表面的静电潜像供给对应颜色的色调剂。由此,显影器1083在感光鼓1081的表面形成使用该色调剂形成的色调剂图像(图像)。

[0044]

一次转印辊1084位于隔着转印带110与感光鼓1081相对的位置。一次转印辊1084与感光鼓1081之间产生转印电压。由此,一次转印辊1084将形成于感光鼓1081的表面的色调剂图像转印(一次转印)到转印带110上。此时,各种颜色的一次转印辊1084将各种颜色的色调剂图像重叠转印到转印带110上。

[0045]

清洁器1085和刮刀1086除去残留在感光鼓1081的表面的色调剂。

[0046]

打印头109例如安装在感光鼓1081的竖直下方与感光鼓1081相对的位置。作为一例,打印头109具备:透镜反射镜阵列1092、支承体1091、基板1093、光源1094、保护玻璃1095以及遮光体1096。

[0047]

支承体1091例如为矩形块状。支承体1091沿与感光鼓1081的旋转轴平行的z方向延伸,且位于与感光鼓1081的图示下方分离相对的位置。支承体1091支承透镜反射镜阵列1092、基板1093、光源1094、保护玻璃1095以及遮光体1096。

[0048]

透镜反射镜阵列1092例如为透明树脂或玻璃制造。透镜反射镜阵列1092具有通过将多个相同形状的透明的光学组件在z方向上排列并一体化而形成的构造。光学组件具备透镜和反射镜等。透镜反射镜阵列1092通过透镜和反射镜等对从光源1094入射的光进行反射和会聚,而使光朝向感光鼓1081的表面发射。

[0049]

基板1093为搭载光源1094和驱动光源1094的驱动电路等的电路基板。

[0050]

光源1094例如是在基板1093的表面沿z方向排列并呈线状装配多个半导体发光元件的光源。半导体发光元件的列沿着感光鼓1081的z方向排列设置有多列。光源1094为发光部的一例。

[0051]

光源1094发射基于将通过原稿读取装置10获得的图像数据、或者经由pc(personal computer:个人计算机)等外部设备获得的图像数据分解为各种颜色分量中的对应的颜色分量的图像数据(图像信号)的光。光源1094的多个半导体发光元件根据图像数据而点亮或熄灭。光源1094的多个半导体发光元件例如是led或oled(organic light emitting diode:有机发光二极管)等。

[0052]

保护玻璃1095设置在透镜反射镜阵列1092与感光鼓1081之间。保护玻璃1095是透明玻璃或透明树脂等。保护玻璃1095防止色调剂和尘埃等附着在透镜反射镜阵列1092。保

护玻璃1095抵接透镜反射镜阵列1092的一端而定位。保护玻璃1095沿z方向延伸。

[0053]

遮光体1096设置在透镜反射镜阵列1092与光源1094之间。遮光体1096沿z方向延伸设置,具有在z方向上延伸的狭缝1097。在遮光体1096的表面例如涂布有遮光材料。遮光体1096遮挡从光源1094发射的一部分光。例如,遮光体1096对通过与光源1094发射的光的光轴相距规定距离以上的位置的光进行遮挡。

[0054]

另外,支承体1091在保护玻璃1095的光的发射侧具有沿着z方向延伸的狭缝1098。狭缝1098具有使曝光时所需要的光分量通过的宽度,并遮挡曝光时所不需要的噪声光。

[0055]

从光源1094发射的光通过遮光体1096的狭缝1097入射到透镜反射镜阵列1092。透镜反射镜阵列1092反射和会聚来自光源1094的光并将其发射。从透镜反射镜阵列1092发射的光经由保护玻璃1095和狭缝1098而会聚到旋转的感光鼓1081的表面。

[0056]

此时,在感光鼓1081的表面形成沿z方向延伸的静电潜像的行。通过反复进行上述动作,在感光鼓1081表面沿周向一点一点地逐次形成静电潜像的行。并且,当感光鼓1081旋转一定量时,在感光鼓1081的表面形成与原稿的整个图像对应的颜色分量的静电潜像。

[0057]

返回对图1的说明。

[0058]

二次转印辊111具备彼此相对的两个辊。二次转印辊111向通过二次转印辊111之间的图像形成介质p转印(二次转印)形成在转印带110上的图像。

[0059]

定影部112对转印有图像的图像形成介质p进行加热及加压。由此,使转印于图像形成介质p上的图像定影。定影部112具备彼此相对的加热部1121和加压辊1122。

[0060]

加热部1121例如是具备用于对加热部1121进行加热的热源的辊。该热源例如是加热器。由热源加热的辊对图像形成介质p进行加热。

[0061]

或者,加热部1121也可以是具备悬挂于多个辊的环形带的加热部。例如,加热部1121具备:板状热源、环形带、带输送辊、张紧辊以及加压辊。环形带例如是膜状部件。带输送辊驱动环形带。张紧辊向环形带施加张力。加压辊在表面形成有弹性层。板状热源其发热部侧与环形带的内侧接触,并通过被向加压辊方向按压而在其与加压辊之间形成规定宽度的定影夹持部。这样的加热部1121由于是板状热源在形成夹持部区域的同时进行加热的构成,所以其在通电时的响应性比基于卤素灯的加热方式时高。

[0062]

加压辊1122对通过加压辊1122与加热部1121之间的图像形成介质p进行加压。

[0063]

双面单元113使图像形成介质p成为能够在背面印刷的状态。例如,双面单元113使用辊等使图像形成介质p转向,由此来使图像形成介质p的正反面翻转。

[0064]

排纸托盘114是印刷已结束的图像形成介质p被排出到的台板。

[0065]

图3是示出图像形成装置100的主要部分电路构成的一例的框图。

[0066]

作为一例,图像形成装置100包括:控制部120、通信i/f131、驱动部132、传感器部133、电源134、扫描仪102、操作面板103、打印头109c、打印头109m、打印头109y以及打印头109k。

[0067]

控制部120是进行对图像形成装置100的各部的控制等的电路。作为一例,控制部120包括:处理器121、rom(read

‑

only memory:只读存储器)122、ram(random

‑

access memory:随机存取存储器)123、辅助存储设备124以及信号生成电路125。

[0068]

处理器121相当于进行图像形成装置100的动作所需的运算及控制等处理的计算机的中枢部分。处理器121基于存储于rom122或辅助存储设备124等的固件、系统软件以及

应用软件等程序,控制各部以实现图像形成装置100的各种功能。另外,处理器121基于该程序执行后述的处理。需要说明的是,该程序的一部分或全部也可以组装到处理器121的电路内。处理器121例如是cpu(central processing unit:中央处理器)、mpu(micro processing unit:微处理单元)、soc(system on a chip:系统级芯片)、dsp(digital signal processor:数字信号处理器)、gpu(graphics processing unit:图形处理器)、asic(application specific integrated circuit:专用集成电路)、pld(programmable logic device:可编程逻辑器件)或fpga(field

‑

programmable gate array:现场可编程逻辑门阵列)等。或者,处理器121是将它们中的多个组合而成的处理器。

[0069]

rom122相当于以处理器121为中枢的计算机的主存储装置。rom122是专门用于读出数据的非易失性存储器。rom122存储上述程序中的例如固件等。另外,rom122还存储在处理器121进行各种处理时使用的数据等。

[0070]

ram123相当于以处理器121为中枢的计算机的主存储装置。ram123是用于数据读写的存储器。ram123被用作存储处理器121在进行各种处理时临时使用的数据的工作区等。ram123是典型的易失性存储器。

[0071]

辅助存储设备124相当于以处理器121为中枢的计算机的辅助存储装置。辅助存储设备124例如是eeprom(electric erasable programmable read

‑

only memory:电可擦可编程只读存储器)、hdd(hard disk drive:硬盘驱动器)或闪存等。辅助存储设备124存储上述的程序中的例如系统软件和应用软件等。另外,辅助存储设备124保存处理器121在进行各种处理时所使用的数据、通过处理器121的处理而生成的数据以及各种设定值等。需要说明的是,图像形成装置100也可以具备能够插入存储卡或usb(universal serial bus:通用串行总线)存储器等存储介质的接口以作为辅助存储设备124。该接口对该存储介质进行信息的读写。

[0072]

图4为示出信号生成电路125的主要部分电路构成等的框图。信号生成电路125例如是asic等。信号生成电路125生成输入到打印头109的信号。另外,信号生成电路125向打印头109输入信号。作为一例,信号生成电路125包括时钟生成部1251、打印头i/f1252以及处理器i/f1253。此外,信号生成电路125还具备进行图像处理的电路以及生成图像信号的电路等。

[0073]

时钟生成部1251生成用于信号生成电路125的动作的时钟信号。需要说明的是,下面将时钟生成部1251生成的时钟信号称为“内部clk”。需要说明的是,内部clk是第一时钟信号的一例。

[0074]

打印头i/f1252是生成sync和sync_clk等数字信号的电路。另外,打印头i/f1252是将sync、sync_clk以及各种信号输出并输入到打印头109的接口。因此,打印头i/f1252是输出sync和sync_clk的输出部的一例。

[0075]

打印头i/f1252通过对内部clk进行分频来生成sync_clk。此外,打印头i/f1252根据sync_clk及设定值n生成sync。需要说明的是,关于sync_clk和sync的生成以及设定值n,在后面详细说明。

[0076]

需要说明的是,sync_clk是第二时钟信号的一例。此外,sync是定时信号的一例。因此,打印头i/f1252是生成sync_clk和sync的生成部的一例。

[0077]

处理器i/f1253是用于信号生成电路125与处理器121进行通信的接口。信号生成

电路125通过处理器i/f1253接受来自处理器121的指示。

[0078]

返回对图3的说明。

[0079]

通信i/f131是用于图像形成装置100经由因特网及lan(local area network:局域网)等网络等进行通信的接口。

[0080]

驱动部132是用于驱动使图像形成装置100的各辊旋转的电机等的电路。

[0081]

传感器部133测量图像形成装置100的各种状态等。

[0082]

电源134向图像形成装置100的各部分供给电力。

[0083]

下面基于图5等来说明第一实施方式所涉及的图像形成装置100的动作。需要说明的是,下面的动作说明中的处理的内容是一例,可以适宜地利用能够获得相同的结果的各种处理。图5为示出通过图像形成装置100的处理器121进行的第一实施方式所涉及的处理的一例的流程图。处理器121例如基于存储于rom122或辅助存储设备124等的程序来执行该处理。

[0084]

处理器121例如随着图像形成装置100的启动,开始图5所示的处理。

[0085]

在图5的act11中,图像形成装置100的处理器121判定是否执行印刷。例如,处理器121根据通信i/f131接收到了从pc或服务器等发送的印刷任务,而判定为执行基于该印刷任务的印刷。或者,处理器121根据对操作面板103进行了指示执行复印或者印刷等的操作而判定执行印刷。处理器121如果不判定执行印刷,则在act11中判定为否,并重复act11。与此相对,若处理器121判定为执行印刷,则在act11中判定为是并进入act12。

[0086]

在act12中,处理器121确定印刷的处理速度v。例如,处理器121根据设定内容、印刷作业的内容或操作内容等确定处理速度v。例如,处理器121根据图像形成介质p的种类等确定处理速度v。

[0087]

在act13中,处理器121通过控制驱动部132使电机等进行动作,以与在act12中确定的处理速度v对应的速度驱动各辊等。

[0088]

在act14中,处理器121设定sync周期。需要说明的是,在这里,作为一例,以下面那样的条件的情况为例对sync周期的设定进行说明。

[0089]

内部clk频率f_c:120[mhz]

[0090]

分频比n:6

[0091]

sync_clk频率f_s:20[mhz]

[0092]

处理速度v:215[mm/秒]

[0093]

副扫描方向的解析度r:2400[dpi]

[0094]

形成于图像形成介质p的行与行的副扫描方向的间隔d为:

[0095]

d=(1/r)[in(英寸)]≈10.5833[μm]

ꢀꢀꢀ

(1)。

[0096]

另外,为了将副扫描方向的解析度设为r,将sync周期设为理想值h_i即可。在这里,理想值h_i为:

[0097]

h_i=(d/v)≈49.22481[μ秒]

ꢀꢀꢀ

(2)。

[0098]

如果能够将sync周期设为h_i,则不会发生以sync的误差为原因的颜色偏移。

[0099]

在这里,内部clk的周期t为:

[0100]

t=(1/f_c)≈0.00833[μ秒]

ꢀꢀꢀ

(3)。

[0101]

周期t为第一实施方式中的sync周期h的分辨率。即,sync周期h是周期t的倍数。因

此,h可以表示为:

[0102]

h=(n

·

t)

ꢀꢀꢀ

(4)。

[0103]

在这里,设定值n[dec]是自然数。

[0104]

为了将sync周期h设为h_i,将设定值n设为如下即可:

[0105]

n_i=(h_i/t)=5906.97

ꢀꢀꢀ

(5)。

[0106]

然而,设定值n是自然数。因此,为了使sync周期h最大程度地接近h_i,将n_i四舍五入为n=5907即可。如果采用其他写法,则为:

[0107]

n=floor((h_i/t) 0.5)=5907

ꢀꢀꢀ

(6)。

[0108]

在这里,floor(x)表示实数x的取整函数。当n=5907时,周期h为49.225[μ秒],周期h与周期h_i的误差e_l为:

[0109]

e_l=h-h_i≈﹣0.00019[μ秒]

ꢀꢀꢀ

(7)。

[0110]

另外,用百分比表示该误差的误差e_p为:

[0111]

(1-(h/h_i))

×

100≈﹣0.00039[%]

ꢀꢀꢀ

(8)。

[0112]

处理器121求解上述那样的设定值n。但是,处理器121求解n的方法不限于上述方法,可以是任何方法。处理器121通过将求解出的设定值n发送到信号生成电路125,来设定sync周期。

[0113]

从处理器121发送出的设定值n经由处理器i/f1253被输入到信号生成电路125。此外,输入到信号生成电路125的设定值n被输入至打印头i/f1252。

[0114]

打印头i/f1252基于输入的设定值n生成sync_clk和sync。使用图6说明sync_clk和sync的例子。图6为示出第一实施方式所涉及的内部clk、sync_clk及sync的例子的时序图。在图6中,示出了sync_clk(a1)~sync_clk(a7)和sync(a1)~sync(a7)来作为sync_clk和sync的例子。

[0115]

打印头i/f1252以使sync的周期h变为sync_clk的波的k个周期的合计的方式生成sync。其中,k为自然数,

[0116]

k=floor(n/n)=984

ꢀꢀꢀ

(9)。

[0117]

另外,若将n表现为以下形式:

[0118]

n=n

·

k m

ꢀꢀꢀ

(10),

[0119]

则m为:

[0120]

m=(n mod n)=n-n

·

k=3

ꢀꢀꢀ

(11)。

[0121]

其中,m为0以上的整数。此外,mod表示模运算符。

[0122]

sync_clk(a1)和sync(a1)表示n=n

·

k=6k时的sync_clk和sync的一例。

[0123]

sync_clk(a2)和sync(a2)表示n=n

·

k 1=6k 1时的sync_clk和sync的一例。

[0124]

sync_clk(a3)和sync(a3)表示n=n

·

k 2=6k 2时的sync_clk和sync的一例。

[0125]

sync_clk(a4)和sync(a4)表示n=n

·

k 3=6k 3时的sync_clk和sync的一例。

[0126]

sync_clk(a5)和sync(a5)表示n=n

·

k 4=6k 4时的sync_clk和sync的一例。

[0127]

sync_clk(a6)和sync(a6)表示n=n

·

k 5=6k 5时的sync_clk和sync的一例。

[0128]

sync_clk(a7)和sync(a7)表示n=n

·

k2=6k2时的sync_clk和sync的一例。其中,设k2=k 1。即,sync_clk(a7)和sync(a7)为k的值比sync_clk(a1)和sync(a1)大1时的sync_clk。

[0129]

sync_clk(a1)的sync_clk的周期是一定的。因此,sync(a1)的周期h_1为:

[0130]

h_1=k(t_s/2)(12)。

[0131]

在sync_clk(a2)~sync_clk(a6)中,对于sync一个周期,一次sync_clk的信号的电平为l(low:低)的期间(下面称为“l期间”)的长度比sync_clk的半周期长。需要说明的是,sync_clk的周期t_s为:

[0132]

t_s=(1/f_s)=n

·

t=6t=0.05[μ秒]

ꢀꢀꢀ

(13)。

[0133]

因此,sync_clk的半周期(t_s/2)为:

[0134]

t_s/2=3t

ꢀꢀꢀ

(14)。

[0135]

例如,相对于sync一个周期,sync_clk(a2)的一次l期间的长度为4t。即,相对于sync一个周期,sync_clk(a2)的一次l期间的长度比sync_clk的半周期(t_s/2)长t。另外,sync的周期为sync_clk的波的k个周期的合计,因此,sync(a2)的周期h_2为:

[0136]

h_2=k(t_s/2) t

ꢀꢀꢀ

(15)。

[0137]

需要说明的是,若对l期间进行补充的话,则l期间表示从信号的电平从由h变化为l起到下次从l向h变化时为止的期间。

[0138]

同样地,相对于sync一个周期,sync_clk(a3)的一次l期间的长度为5t。因此,sync(a3)的周期h_3为:

[0139]

h_3=k(t_s/2) 2t

ꢀꢀꢀ

(16)。

[0140]

相对于sync一个周期,sync_clk(a4)的一次l期间的长度为6t。因此,sync(4)的周期h_4为:

[0141]

h_4=k(t_s/2) 3t

ꢀꢀꢀꢀ

(17)。

[0142]

相对于sync一个周期,sync_clk(a5)的一次l期间的长度为7t。因此,sync(5)的周期h_5为:

[0143]

h_5=k(t_s/2) 4t

ꢀꢀꢀꢀ

(18)。

[0144]

相对于sync一个周期,sync_clk(a6)的一次l期间的长度为8t。因此,sync(6)的周期h_6为:

[0145]

h_6=k(t_s/2) 5t

ꢀꢀꢀꢀ

(19)。

[0146]

需要说明的是,在n=6、n=5907的情况下,k=984、m=3。因此,在n=6、n=5907时的sync_clk和sync为sync_clk(a4)和sync(a4)。

[0147]

由上述可知,处理器121作为通过进行act14的处理来进行控制以根据处理速度更改sync的周期的控制部的一例发挥功能。

[0148]

另外,根据上述可见,打印头i/f1252是通过更改l期间的长度来更改sync周期的期间更改部的一例。

[0149]

处理器121在act15中基于印刷任务等执行印刷。在印刷中,打印头i/f1252对基于act14的设定生成的sync_clk和sync进行输出并输入到打印头109。打印头109根据sync变为l期间之后sync_clk两次变为h(high:高)这一情况,以该第二次的h为触发使光源1094发光。由此,光源1094在每个sync周期h发光。通过重复该操作,图像形成装置100以前述方式在感光鼓1081形成基于静电潜像的图像。然后,形成于感光鼓1081的图像以前述的方式被转印到正在被以处理速度v进行输送的图像形成介质p。如此,图像形成装置100进行针对图像形成介质p的印刷。然后,图像形成装置100将印刷已结束的图像形成介质p排出到排纸托

盘114。需要说明的是,在图6中示出了成为发光的触发的定时q。处理器121在act15的处理之后返回act11。

[0150]

根据第一实施方式的图像形成装置100,信号生成电路125能够将sync_clk的l期间的长度更改周期t的倍数的时间。因此,第一实施方式的信号生成电路125中的sync周期h的分辨率与内部clk的周期t相等。即,sync周期h的分辨率约为0.00833[μ秒]。另外,如前述,上述实施方式中的周期h为49.225[μ秒]。而且,这种情况下的周期h与周期h_i的误差e_l约为

‑

0.00019[μ秒],误差e_p约为

‑

0.00039[%]。

[0151]

图像形成部108y的感光鼓1081与图像形成部108k的感光鼓1081距离270[mm]。由于行间隔d约为10.58333[μm],所以270[mm]约为25511.8行对应的长度。因此,270[mm]通过四舍五入为25512行对应的长度。25512行对应的颜色偏移量g变为:

[0152]

g=(d

·

e_p)/100

×

25512≈1.063[μm]

ꢀꢀꢀ

(20)。

[0153]

在现有的图像形成装置中,sync_clk的周期是固定的。因此,现有的sync周期的分辨率与sync_clk的周期t_s相等:

[0154]

t_s=(1/f_s)=6t=0.05[μ秒]

ꢀꢀꢀ

(21)。

[0155]

因此,现有的图像形成装置中的sync周期h_c为49.2[μ秒]。并且,周期h_c与周期h_i的误差e_lc约为0.02481[μ秒]。另外,用百分比表示该误差的误差e_pc约为0.050419[%]。因此,25512行对应的颜色偏移量g_c为

‑

136.13[μm]。

[0156]

如上所述,与sync_clk频率f_s相同的现有的信号生成电路相比,第一实施方式的信号生成电路125的sync周期h的分辨率高,与理想值的误差小。然后,由此第一实施方式的信号生成电路125能够使颜色偏移量比以往小。这也可以得知第一实施方式的颜色偏移量g小于现有的图像形成装置中的颜色偏移量g_c。

[0157]

第一实施方式的信号生成电路125通过使sync_clk的l期间的长度变长来使sync周期变化。与缩短l期间的长度相比,可以通过更简单的电路来实现使sync_clk的l期间的长度变长,因此能够降低成本。

[0158]

第一实施方式的信号生成电路125通过对sync一个周期改变一次sync_clk的l期间的长度来使sync周期变化。这样,信号生成电路125通过对一个周期仅改变一次长度,就能够以sync周期的分辨率t发生变化。

[0159]

第一实施方式的图像形成装置100根据处理速度确定设定值并设定sync周期。因此,在第一实施方式的图像形成装置100中,更改处理速度也能够减小颜色偏移量。

[0160]

上述第一实施方式也可以进行如下变形。

[0161]

在上述第一实施方式中,信号生成电路125通过使sync_clk的l期间的长度变长来设定sync周期h的长度。然而,信号生成电路125也可以通过使sync_clk的h期间的长度变长来设定sync周期h的长度。需要说明的是,h期间为信号的电平是h的期间。即,h期间表示从信号的电平从由l变化为h时起到下次从h向l变化时为止的期间。在图7中示出sync_clk的h期间的长度变长时的sync和sync_clk的示例。图7为示出第一实施方式的变形例所涉及的内部clk、sync_clk以及sync的例子的时序图。

[0162]

在图7中示出sync_clk(a1)和sync_clk(a7)~sync_clk(a12)、以及sync(a1)和sync(a7)~sync(a12)作为sync_clk和sync的例子。

[0163]

sync_clk(a8)和sync(a8)表示n=n

·

k 1=6k 1时的sync_clk和sync的一例。

[0164]

sync_clk(a9)和sync(a9)表示n=n

·

k 2=6k 2时的sync_clk和sync的一例。

[0165]

sync_clk(a10)和sync(a10)表示n=n

·

k 3=6k 3时的sync_clk和sync的一例。

[0166]

sync_clk(a11)和sync(a11)表示n=n

·

k 4=6k 4时的sync_clk和sync的一例。

[0167]

sync_clk(a12)和sync(a12)表示n=n

·

k 5=6k 5时的sync_clk和sync的一例。

[0168]

在sync_clk(a8)~sync_clk(a12)中,相对于sync一个周期,一次sync_clk的h期间的长度比sync_clk的半周期长。

[0169]

相对于sync一个周期,sync_clk(a8)的一次h期间的长度为4t。因此,sync(8)的周期h_8为:

[0170]

h_8=k(t_s/2) 2t

ꢀꢀꢀꢀ

(22)。

[0171]

相对于sync一个周期,sync_clk(a9)的一次h期间的长度为5t。因此,sync(a9)的周期h_9为:

[0172]

h_9=k(t_s/2) 2t

ꢀꢀꢀꢀ

(23)。

[0173]

相对于sync一个周期,sync_clk(a10)的一次h期间的长度为6t。因此,sync(a10)的周期h_10为:

[0174]

h_10=k(t_s/2) 3t

ꢀꢀꢀꢀ

(24)。

[0175]

相对于sync一个周期,sync_clk(a11)的一次h期间的长度为7t。因此,sync(a11)的周期h_11为:

[0176]

h_11=k(t_s/2) 4t

ꢀꢀꢀꢀ

(25)。

[0177]

相对于sync一个周期,sync_clk(a12)的一次h期间的长度为8t。因此,sync(a12)的周期h_12为:

[0178]

h_12=k(t_s/2) 5t

ꢀꢀꢀꢀ

(26)。

[0179]

需要说明的是,在n=6、n=5907的情况下,k=984、m=3。因此,当n=6、n=5907时的图7所示的sync_clk和sync为sync_clk(a10)和sync(a10)。

[0180]

需要说明的是,与使h期间的长度变短相比,可以通过更简单的电路来实现使sync_clk的h期间的长度变长,因此可以降低成本。

[0181]

在上述第一实施方式中,信号生成电路125通过对于sync一个周期使sync_clk的l期间的长度变长一次来设定sync周期h的长度。然而,信号生成电路125可以对于sync将一个周期h期间或l期间的长度更改两次以上。在图8中示出这种情况下的sync和sync_clk的例子。图8为示出第一实施方式的变形例所涉及的内部clk、sync_clk以及sync的例子的时序图。

[0182]

在图8中示出sync_clk(a6)和sync_clk(a13)~sync_clk(a17)、以及sync(a6)和sync(a13)~sync(a17)以作为sync_clk和sync的例子。需要说明的是,sync(a6)和sync(a13)~sync(a17)的周期h均相等。即,h_6=h_13=h_14=

……

=h_17=k(t_s/2) 4t。

[0183]

相对于sync一个周期,sync_clk(a13)的一次l期间的长度为5t,相对于sync一个周期,sync_clk(a13)的一次h期间的长度为5t。

[0184]

相对于sync一个周期,sync_clk(a14)的两次l期间的长度为5t。

[0185]

相对于sync一个周期,sync_clk(a15)的两次h期间的长度为5t。

[0186]

相对于sync一个周期,sync_clk(a16)的两次l期间的长度为4t,相对于sync一个周期,sync_clk(a16)的两次h期间的长度为4t。

[0187]

sync(a17)是sync_clk的(k 1)个波的长度。即,与sync(a1)相比,sync(a17)在sync一个周期中的sync_clk的波数多一个。

[0188]

相对于sync一个周期,sync_clk(a17)的一次l期间的长度为2t,相对于sync一个周期,sync_clk(a17)的一次h期间的长度为2t。即,sync_clk(a17)包括比sync_clk的半周期(t_s/2)短t的l期间。另外,sync_clk(a17)包括比sync_clk的半周期(t_s/2)短t的h期间。

[0189]

此外,相对于sync一个周期,sync_clk的3次以上的l期间或者h期间也可以长或短于sync_clk的半周期。

[0190]

在上述第一实施方式中,设定值n是将n_i四舍五入后得到的值。然而,设定值n也可以是通过对n_i进行舍去小数位或进位等其他方法取整而得到的值。

[0191]

图6~图8所示的各sync的l期间的长度是sync_clk的两个周期的量。但是,sync的l期间的长度不限于此。

[0192]

在上述第一实施方式中,图像形成装置100将第二次的h作为发光的触发。然而,发光的触发可以是第一次或第三次以后的h,另外,也可以用l来代替h。

[0193]

sync的l和h也可以与上述实施方式相反。sync_clk的l和h也可以与上述实施方式相反。内部clk的与l和h也可以与上述实施方式相反。

[0194]

[第二实施方式]

[0195]

第二实施方式所涉及的图像形成装置100的构成与第一实施方式相同,因此省略说明。

[0196]

不过,第二实施方式所涉及的图像形成装置100的时钟生成部1251包括图9所示的pll(phase locked loop:锁相环)1251a。图9是示出图3中的信号生成电路的主要部分电路构成等的第二实施方式的框图。

[0197]

pll1251a也被称为相位同步电路。pll1251a是对时钟生成部1251所生成的内部clk的频率进行微调的电路。pll1251a例如能够以0.001%为单位提高或降低内部clk的频率。此外,pll1251a例如能够在最大3%左右的范围内提高或者降低内部clk的频率即可。在这里,将pll1251a提高内部clk的频率的比例称为微调率。因此,作为一例,pll1251a的微调率的分辨率为0.001%,微调率范围为

‑

3%~﹢3%。需要说明的是,图像形成装置100调整内部clk的频率以使sync_clk的频率成为能够输入到打印头的频率范围内。

[0198]

此外,第二实施方式的打印头i/f1252不必具备使l期间和h期间的长度变化的功能。

[0199]

下面,基于图10等来说明第二实施方式所涉及的图像形成装置100的动作。需要说明的,下面的动作说明中的处理的内容是一例,能够适宜地利用能够获得相同的结果的各种处理。图10为示出通过图像形成装置100的处理器121进行的第二实施方式所涉及的处理的一例的流程图。处理器121例如基于存储在rom122或辅助存储设备124等的程序来执行该处理。

[0200]

在第二实施方式中,处理器121在图10的act13的处理之后进入act21。

[0201]

处理器121在act21中设定内部clk频率以及sync周期。需要说明的是,在这里,作为一例以下面那样的条件的情况为例来说明对sync周期的设定。

[0202]

内部clk基准频率f_c0:120[mhz]

[0203]

分频比n:6

[0204]

sync_clk基准频率f_s0:20[mhz]

[0205]

处理速度v:215[mm/秒]

[0206]

副扫描方向的解析度r:2400[dpi]

[0207]

在这里,内部clk基准频率f_c0是未进行基于pll1251a的调整时的内部clk的频率。另外,sync_clk基准频率f_s0是未进行基于pll1251a的调整时的sync_clk的频率。

[0208]

与第一实施方式相同,第二实施方式的副扫描方向的间隔d为:

[0209]

d=(1/r)[in(英寸)]≈10.5833[μm]

ꢀꢀꢀꢀꢀ

(27)。

[0210]

与第一实施方式相同,第二实施方式的sync周期的理想值h_i为:

[0211]

h_i=(d/v)≈49.22481[μ秒]

ꢀꢀꢀꢀꢀ

(28)。

[0212]

sync_clk周期t_s是第二实施方式中的sync周期h_b的分辨率。因此,能够表示为:

[0213]

h_b=(n_b

·

t_s)

ꢀꢀꢀꢀꢀ

(29)。

[0214]

即,sync周期h_b是周期t_s的倍数。需要说明的是,n_b表示第二实施方式中的设定值。设定值n_b[dec]为自然数。

[0215]

图11为示出第二实施方式所所涉及的内部clk、sync_clk以及sync的例子的时序图。图11示出了波形例1~波形例4四个波形例。

[0216]

·

波形例1

[0217]

波形例1是在将内部clk频率设为f_c0时的内部clk(b1)、sync_clk(b1)以及sync(b1)。即,波形例1是未进行基于pll1251a的调整时的内部clk、sync_clk和sync,因此是与现有的图像形成装置的内部clk、sync_clk和sync相同的波形。

[0218]

sync_clk(b1)周期t_31为:

[0219]

t_31=(1/f_s0)=0.05[μ秒]

ꢀꢀꢀꢀ

(30)。

[0220]

将sync(b1)周期h_31表示为:

[0221]

h_31=(n_31

·

t_31)

ꢀꢀꢀꢀꢀ

(31)时,

[0222]

n_31=floor((h_i/t_31) 0.5)=984

ꢀꢀꢀꢀ

(32)。

[0223]

在这里,n_31表示波形例1时的设定值n_b。因此,sync(b1)周期h_31为49.2[μ秒]。因此,周期h_31与周期h_i之间的误差e_l31为:

[0224]

e_l31=h_31-h_i≈0.02481[μ秒]。

[0225]

另外,用百分比表示该误差的误差e_p31为:

[0226]

e_p31=(1-(h_31/h_i))

×

100≈﹣0.078802[%]

ꢀꢀꢀꢀꢀ

(33)。

[0227]

并且,25512行对应的颜色偏移量g_31为:

[0228]

g_32=(d

·

e_p32)/100

×

25512≈﹣136.13[μm]

ꢀꢀꢀꢀꢀ

(34)。

[0229]

·

波形例2

[0230]

波形例2表示调整内部clk频率而使sync周期接近h_i时的内部clk(b2)、sync_clk(b2)和sync(b2)。波形例2的设定值n_32与波形例1的n_31相同,为:

[0231]

n_32=n_31=floor((h_i/t_31) 0.5)=984

ꢀꢀꢀꢀꢀ

(35)。

[0232]

如果将sync(b2)周期h_32设为比周期h_31大p_i[%]的值,则能够将周期h_32设为与周期h_i相同的长度。此时的p_i为:

[0233]

p_i=((h_i/h_31)—1)

×

100=0.0504

ꢀꢀꢀꢀꢀ

(36)。

[0234]

在这里,pll1251a能够使内部clk的频率以0.001%的分辨率变化。即,波形例2的微调率p_32[%]为0.001[%]的倍数。由于p_32优选尽可能接近p_i的值,所以例如p_32=

‑

0.050。pll1251a通过使内部clk的频率以微调率p_32变化,从而能够使周期h_32接近周期h_i。此时的周期h32为:

[0235]

h_32=h_31

×

(1 (p_32/100))=49.2246[μ秒]

ꢀꢀꢀꢀꢀ

(37)。

[0236]

因此,周期h_32和周期h_i的误差e_l32为:

[0237]

e_l32=h_32-h_i≈0.00021[μ秒]。

[0238]

另外,用百分比表示该误差的误差e_p32为:

[0239]

e_p32=(1-(h_32/h_i))

×

100≈0.000427[%]

ꢀꢀꢀꢀꢀ

(38)。

[0240]

并且,25512行对应的颜色偏移量g_32为:

[0241]

g_32=(d

·

e_p32)/100

×

25512≈1.152[μm]

ꢀꢀꢀꢀ

(39)。

[0242]

另外,内部clk(b2)的频率f_c32、sync_clk(b2)的频率f_s32、以及sync_clk(b2)的周期t_32分别为:

[0243]

f_c32=f_c0

×

(100 p_32)

÷

100=119.94[mhz]

ꢀꢀꢀꢀꢀ

(40),

[0244]

f_s32=f_c32

÷

6=19.99[mhz]

ꢀꢀꢀꢀꢀ

(41),

[0245]

t_32=t_31

×

(100 p_32)

÷

100=0.050025[μ秒]

ꢀꢀꢀꢀꢀ

(42)。

[0246]

综上,在波形例2的情况下,处理器121确定为p_32=

‑

0.050、n_32=984。

[0247]

·

波形例3

[0248]

波形例3示出了调整内部clk频率以及设定值n_b使sync周期接近h_i时的内部clk(b2)、sync_clk(b2)以及sync(b2)。不过,波形例3示出了使内部clk频率比内部clk基准频率f_c0长时的例子。因此,波形例3中的微调率p_3是正值。

[0249]

处理器121使用例如图12所示的表t1来确定波形例3的设定值n_33以及内部clk频率f_c33。图12为示出用于确定设定值和内部clk频率的表的一例的图。需要说明的是,图12省略一部分而加以示出。另外,图像形成装置100例如将表t1存储于辅助存储设备124。

[0250]

需要说明的是,表t1中的内部频率的各值为第一值的一例。另外,表t1中的设定值的各值为第二值的一例。因此,存储表t1的辅助存储设备124为对内部频率以及设定值的多个组合中的每一个存储颜色偏移量的存储部的一例。

[0251]

表t1示出了使微调率p每次变化作为微调率的分辨率的0.001%时的对应的内部clk频率f_c、sync_clk频率f_s、sync_clk分辨率(周期t)、处理速度v、解析度r、间隔d、sync周期理想值h_i、sync周期分辨率、设定值n_b、sync周期h、误差e_p、鼓间隔以及颜色偏移量g等。需要说明的是,在这些值中,也存在与微调率无关而固定的值。因此,图像形成装置100也可以将这样的固定值存储在不同于表t1的其他地方。另外,表t1为示出微调率为正值的情况的表。

[0252]

处理器121参照表t1,将颜色偏移量g变为最小时的微调率确定为波形例3中的微调率p_3。或者,处理器121根据表t1将颜色偏移量g变为规定的阈值t_1以下的情况下的微调率确定为波形例3中的微调率p_3。需要说明的是,在存在使多个颜色偏移量g变为规定阈值以下的微调率的情况下,处理器121例如将其中最小的微调率确定为微调率p_3。

[0253]

因此,处理器121例如将颜色偏移量最接近0的微调率55.9确定为微调率p_3的值。需要说明的是,微调率55.9的颜色偏移量约为0.147993。

[0254]

此外,处理器121参照表t1,将与微调率p_3对应的设定值n_b确定为波形例3中的设定值n_b3。

[0255]

因此,处理器121将与微调率55.9%对应的设定值990确定为设定值n_b4的值。

[0256]

综上,在波形例3的情况下,处理器121确定为p_3=55.9[%],n_b3=990。

[0257]

·

波形例4

[0258]

波形例4示出了调整内部clk频率以及设定值n而使sync周期接近h_i时的内部clk(b2)、sync_clk(b2)以及sync(b2)。但是,波形例4与波形例3不同,为降低内部clk频率而使sync周期接近h_i的示例。因此,波形例4中的微调率p_4为负的值。

[0259]

处理器121例如使用图13所示的表t2来确定波形例4的设定值n_34以及内部clk频率f_c34。图13为示出用于确定设定值以及内部clk频率的表的一例的图。需要说明的是,图13以省略部分的方式进行示出。另外,图像形成装置100例如将表t2存储于辅助存储设备124。

[0260]

需要说明的是,表t2中的内部频率的各值是第一值的一例。另外,表t2中的设定值的各值是第二值的一例。因此,存储表t2的辅助存储设备124是存储部的一例。

[0261]

表t2表示使微调率p每次变化作为微调率的分辨率的0.001%时的各自的内部clk频率f_c、sync_clk频率f_s、sync_clk分辨率(周期t)、处理速度v、解析度r、间隔d、sync周期理想值h_i、sync周期分辨率、设定值n_b、sync周期h、误差e_p、鼓间隔以及颜色偏移量g等。此外,在这些值中,也存在与微调率无关而值固定的值。因此,图像形成装置100也可以将这样的固定值存储在不同于表t1的场所。另外,表t2为示出微调率为负值的情况的表。

[0262]

处理器121参照表t2,将颜色偏移量g变为最小时的微调率确定为波形例4中的微调率p_4。或者,处理器121根据表t2将颜色偏移量g变为规定的阈值t_2以下时的微调率确定为波形例4中的微调率p_4。需要说明的是,在存在多个使颜色偏移量g变为规定的阈值以下的微调率的情况下,处理器121例如将其中最大的微调率确定为微调率p_4。

[0263]

因此,处理器121例如将颜色偏移量最接近0的微调率

‑

15.2确定为微调率p_4的值。需要说明的是,微调率

‑

15.2的颜色偏移量约为0.08517。

[0264]

进一步地,处理器121参照表t2,将与微调率p_4对应的设定值n_b确定为波形例4中的设定值n_b4。

[0265]

因此,处理器121将与微调率

‑

15.2%对应的设定值983确定为设定值n_b4的值。

[0266]

综上,处理器121参照表t2,确定p_4=

‑

15.2[%]、n_b4=983。

[0267]

需要说明的是,图像形成装置100还可以更改处理速度v。在这种情况下,图像形成装置100例如针对每个处理速度存储像表t1和表t2那样的表。

[0268]

另外,处理器121例如以下面的(i)或(ii)中的任一方式来确定将微调率设为正值或负值。

[0269]

(i)图像形成装置100预先确定将微调率设为正或负值。因此,处理器121例如使用表t1和表t2中任一者来确定微调率。

[0270]

(ii)处理器121例如参照表t1和表t2中的每一个表来求出正的微调率和负的微调率。然后,处理器121基于某些判定基准,将所求出的正的微调率或负的微调率的任一者确定为在内部clk频率的设定中使用的微调率。例如,处理器121将绝对值较小的微调率确定为在内部clk频率的设定中使用的微调率。或者,处理器121将颜色偏移量小的微调率确定

为在内部clk频率的设定中使用的微调率。

[0271]

处理器121通过将以如上方式确定的微调率发送到时钟生成部1251来对内部clk频率进行设定。从处理器121发送的微调率经由处理器i/f1253被输入到信号生成电路125。另外,输入到信号生成电路125的微调率被输入到时钟生成部1251。

[0272]

时钟生成部1251基于输入的微调率生成内部clk。

[0273]

另外,处理器121通过将以如上方式确定的设定值n发送到信号生成电路125来对sync周期进行设定。从处理器121发送的设定值n经由处理器i/f1253被输入到信号生成电路125。另外,输入到信号生成电路125的设定值n被输入到打印头i/f1252。

[0274]

打印头i/f1252基于输入的设定值n生成sync_clk和sync。

[0275]

在act22中,与第一实施方式的act15一样,处理器121基于印刷任务等执行印刷。但是,打印头i/f1252输出基于act21的设定生成的sync_clk和sync,进而将其输入打印头109。需要说明的是,在图12和图13中示出了成为发光的触发的定时q。处理器121在act22的处理之后,返回到act11。

[0276]

根据第二实施方式的图像形成装置100,信号生成电路125能够通过更改微调率来更改sync_clk频率和sync周期。由此,与以往相比,信号生成电路125能够降低颜色偏移量。

[0277]

另外,根据第二实施方式的图像形成装置100,信号生成电路125能够更改微调率和设定值。由此,与仅更改微调率相比,信号生成电路125能够降低颜色偏移量。

[0278]

另外,第二实施方式的图像形成装置100使用表来确定微调率和设定值。因此,与通过计算求出微调率和设定值相比,图像形成装置100能够更早地设定内部clk频率和sync周期。

[0279]

另外,第二实施方式的图像形成装置100参照表,将使颜色偏移量变为阈值以下的微调率和设定值的组合确定为在内部clk频率和sync周期的设定中使用的微调率和设定值的组合。由此,图像形成装置100能够减小颜色偏移量。

[0280]

与第一实施方式的图像形成装置100相比,第二实施方式图像形成装置100能够使颜色偏移量变小。与此相对,与第二实施方式的图像形成装置100相比,第一实施方式的图像形成装置100设定sync周期所花费的时间更短。

[0281]

上述第二实施方式也可以进行如下变形。

[0282]

在上述第二实施方式的波形例3和波形例4中,处理器121使用表t1和表t2等表求出了微调率和设定值。不过,处理器121也可以通过计算求出微调率和设定值。

[0283]

在上述第二实施方式的波形例2中,处理器121通过计算等求出了微调率和设定值。但是,处理器121也可以使用表来求出微调率和设定值。

[0284]

辅助存储设备124也可以通过使用表以外的方法,对内部频率和设定值的多个组合中的每一个存储颜色偏移量。

[0285]

上述第一实施方式和第二实施方式也可以进行如下那样的变形。

[0286]

实施方式的图像形成装置100还可以是能够执行第一实施方式所示的动作和第二实施方式所示的动作的两个动作。

[0287]

处理器121也可以是通过电路的硬件构成来实现在上述实施方式中通过程序实现的处理的一部分或全部。

[0288]

上述实施方式中的图像形成装置100例如在存储有用于执行上述处理的程序的状

态下被转让给图像形成装置100的管理者等。或者,图像形成装置100在未存储有该程序的状态下被转让给该管理者等。并且,该程序被另外转让给该管理者等,并基于通过该管理者或服务人员等进行的操作被存储于图像形成装置100。此时的程序的转让例如能够通过使用像磁盘介质或半导体存储器等那样的可移动的存储介质、或者经由因特网或lan等的下载来实现。

[0289]

虽然说明了本发明的几个实施方式,但这些实施方式只是作为例子而提出的,并非旨在限定发明的范围。这些新的实施方式能够以其他各种方式进行实施,能够在不脱离发明的宗旨的范围内进行各种省略、替换、更改。这些实施方式及其变形包括在发明的范围和宗旨中,同样地包括在权利要求书所记载的发明及其均等的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。