1.本技术涉及显示技术领域,尤其涉及一种显示面板。

背景技术:

2.随着显示技术的发展,对于显示要求越来越高,如何实现柔性显示的同时,保证显示面板能进行高频动态显示,进而保证画面的流畅是需要解决的技术问题。

3.因此,有必要提出一种技术方案以使显示面板实现柔性显示的同时,有利于显示面板实现高频显示。

技术实现要素:

4.本技术的目的在于提供一种显示面板,以使显示面板实现柔性显示的同时,有利于显示面板实现高频显示。

5.为实现上述目的,技术方案如下:

6.一种显示面板,所述显示面板包括n个级联的栅极驱动单元,所述n为正整数,第n级所述栅极驱动单元包括:

7.级传输出模块,与第一节点连接,用于响应所述第一节点的电压而交替地输出高电平的第n级级传信号和低电平的第n级级传信号,所述n为大于或等于1且小于或等于所述n的整数;

8.输入上拉模块,用于控制所述第一节点的电势;

9.输出上拉模块,与所述级传输出模块的输出端连接,且响应于低电平的所述第n级级传信号而输出高电平的第n级扫描信号;以及

10.输出下拉模块,与所述级传输出模块的输出端连接,且响应于高电平的所述第n级级传信号而输出低电平的第n级扫描信号;

11.其中,所述级传输出模块、所述输入上拉模块以及所述输出上拉模块中的晶体管均为p型低温多晶硅薄膜晶体管,所述输出下拉模块中的晶体管为n型金属氧化物薄膜晶体管。

12.一种显示面板,所述显示面板包括n个级联的栅极驱动单元,所述n为正整数,第n级所述栅极驱动单元包括:

13.第一p型低温多晶硅薄膜晶体管,所述第一p型低温多晶硅薄膜晶体管的栅极接入第一时钟信号,所述第一p型低温多晶硅薄膜晶体管的第一极接入起始信号或第n

‑

1级所述栅极驱动单元输出的第n

‑

1级级传信号,所述第一p型低温多晶硅薄膜晶体管的第二极与第一节点连接,所述n为大于或等于1且小于或等于所述n的整数;

14.第二p型低温多晶硅薄膜晶体管,所述第二p型低温多晶硅薄膜晶体管的栅极与所述第一节点连接,所述第二p型低温多晶硅薄膜晶体管的第一极接入第二时钟信号,所述第二p型低温多晶硅薄膜晶体管的第二极连接第n级级传信号的输出端;

15.第三p型低温多晶硅薄膜晶体管,所述第三p型低温多晶硅薄膜晶体管的栅极与所

述第n级级传信号的输出端连接,所述第三p型低温多晶硅薄膜晶体管的第一极接入恒压高电平,所述第三p型低温多晶硅薄膜晶体管的第二极连接第n级所述栅极驱动单元的输出端;以及

16.第一n型金属氧化物薄膜晶体管,所述第一n型金属氧化物薄膜晶体管的栅极连接所述第n级级传信号的输出端连接,所述第一n型金属氧化物薄膜晶体管的第一极接入第一恒压低电平,所述第一n型金属氧化物薄膜晶体管的第二极连接第n级所述栅极驱动单元的输出端;

17.其中,所述第二时钟信号的脉冲周期与所述第一时钟信号的脉冲周期相同,且所述第二时钟信号的相位与所述第一时钟信号的相位相反。

18.有益效果:本技术提供一种显示面板,通过将输入上拉模块、级传输出模块和输出上拉模块中的晶体管设置为p型低温多晶硅薄膜晶体管,将输出下拉模块中的晶体管设置为n型金属氧化物薄膜晶体管,使得栅极驱动单元可以采用低温制程制备得到,满足柔性显示面板的制程要求的同时,保证栅极驱动单元输出的扫描信号能实现快速上拉和快速下拉,进而使得栅极驱动单元能高频输出扫描信号,有利于显示面板实现高频显示。另外,栅极驱动单元使用p型低温多晶硅薄膜晶体管有利于节省制备栅极驱动单元的光罩数目。

附图说明

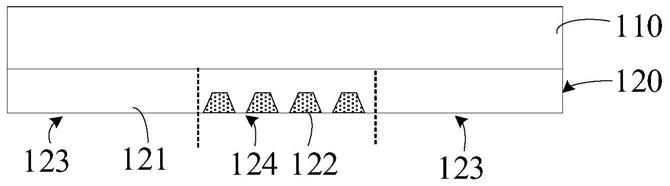

19.图1为本技术实施例显示面板的平面示意图;

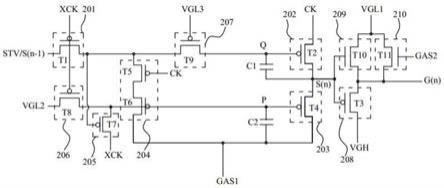

20.图2为图1所示栅极驱动电路中的第n级栅极驱动单元的电路图;

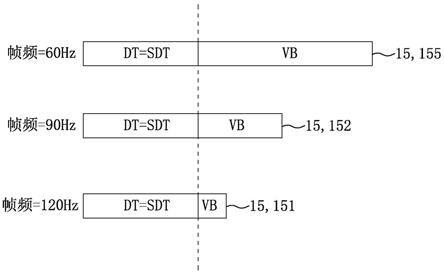

21.图3为图2所示栅极驱动单元对应的驱动时序图;

22.图4为本技术另一实施例解复用电路的平面示意图;

23.图5为本技术另一实施例解复用电路的平面示意图;

24.图6为图1所示显示面板的显示区的截面示意图;

25.图7为图1所示显示面板的外围区的截面示意图。

具体实施方式

26.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

27.针对上述背景技术的问题,本技术的发明人基于丰富的实践经验及大量创造性的探索发现,n型低温多晶硅薄膜晶体管由于需要进行沟道掺杂,导致n型低温多晶硅薄膜晶体管的制程温度较高,使得其通常不适合用于柔性显示工艺,而p型低温多晶硅薄膜晶体管可以采用低温制程制备得到,将p型低温多晶硅薄膜晶体管应用于柔性显示面板的栅极驱动电路的制备时,由于p型低温多晶硅薄膜晶体管的下拉能力差,导致p型低温多晶硅薄膜晶体管组成的栅极驱动电路输出的高电平的扫描信号下拉为低电平的扫描信号的下降沿对应的时间较长,导致p型低温多晶硅薄膜晶体管组成的栅极驱动电路较难支持高频显示,基于此,本技术通过使栅极驱动单元的输出下拉模块中的晶体管为n型金属氧化物薄膜晶体管,配合使输出上拉模块的晶体管为p型低温多晶体硅晶体管,再结合输入上拉模块、级

传输出模块中的晶体管均为p型低温多晶硅薄膜晶体管,以使栅极驱动单元满足柔性显示面板的低温制程要求的同时,保证栅极驱动单元具有快速的下拉能力和快速的上拉能力,有利于栅极驱动单元高频输出扫描信号,进而保证显示面板进行高频显示。

28.如图1所示,其为本技术实施例显示面板的平面示意图。显示面板100为液晶显示面板。显示面板100具有显示区100a和外围区100b,显示面板100包括栅极驱动电路20、像素电路30以及解复用电路40,像素电路30设置于显示面板100的显示区100a,栅极驱动电路20和解复用电路40设置于显示面板100的外围区100b。

29.在本实施例中,显示面板100包括多条扫描线和多条数据线,多条扫描线包括扫描线s1、扫描线s2以及扫描线s(n),多条数据线包括第一类数据线d(m)以及第二类数据线d(m 1),一条第一类数据线d(m)与一条第二类数据线d(m 1)相邻且交替地设置,第一类数据线d(m)传输的数据信号的极性与第二类数据线d(m 1)传输的数据信号的极性相反,例如,第一类数据线d(m)传输正极性的数据信号,第二类数据线d(m 1)传输负极性的数据信号。多条扫描线和多条数据线设置于显示面板100的显示区100a,多条扫描线沿行方向延伸且沿列方向排列,多条数据线沿列方向排列且沿行方向延伸。每个像素电路30与一条扫描线和一条数据线连接,每个像素电路30包括一个开关晶体管k,开关晶体管k的栅极与扫描线连接,开关晶体管k的第一极与数据线连接,开关晶体管k的第二极与像素电极连接。显示面板100还包括红色子像素r、绿色子像素g以及蓝色子像素b,同一列子像素为红色子像素r、绿色子像素g或者蓝色子像素b,一条数据线与一列子像素连接。

30.在本实施例中,开关晶体管k为n型金属氧化物薄膜晶体管,以减小开关晶体管k在显示过程中的漏电流,满足低频或者超低频显示过程中对画面维持时间长的要求。

31.请继续参阅图1,栅极驱动电路20位于显示面板100的显示区100a的相对两侧,一条扫描线与两个相对的栅极驱动单元goa连接,以实现扫描线的双边驱动。可以理解的是,栅极驱动电路20也可以只位于也显示面板100的显示区100a的一侧,一条扫描线与一个栅极驱动单元连接,以实现扫描线的单边驱动;或者,栅极驱动电路20也可以位于显示面板100的显示区100a的相对两侧,奇数行扫描线和偶数行扫描线分别与位于相对两侧的两个栅极驱动单元goa连接,以实现扫描线的单边驱动。

32.为了描述本技术的技术方案,以显示面板100的显示区100a的每侧的栅极驱动电路20均包括n个级联的栅极驱动单元为例进行说明。如图2所示,其为图1所示栅极驱动电路中的第n级栅极驱动单元的电路图。第n级栅极驱动单元goa(n)包括输入上拉模块201、级传输出模块202、级传维持模块203、第一节点维持模块204、第一节点反馈模块205、第二节点下拉模块206、电压钳位模块207、输出上拉模块208、输出下拉模块209以及触控维持模块210。其中,第n级栅极驱动单元goa(n)的输入上拉模块201、级传输出模块202、电压钳位模块207、级传维持模块203、第一节点反馈模块205、第一节点维持模块204以及第二节点下拉模块206组成逻辑控制模块,以交替地输出高电平的第n级级传信号s(n)和低电平的第n级级传信号s(n)。输出上拉模块208、输出下拉模块209以及触控维持模块210组成输出模块以输出高电平的第n级扫描信号或低电平的第n级扫描信号。输出上拉模块208以及输出下拉模块209响应于逻辑控制模块交替输出的高电平的第n级级传信号s(n)和低电平的第n级级传信号s(n),以输出高电平的扫描信号g(n)和低电平的扫描信号g(n)。

33.在本实施例中,输入上拉模块201用于控制第一节点q的电势,包括上拉和下拉第

一节点q的电势。输入上拉模块201通过电压钳位模块207与第一节点q连接,输入上拉模块201接收第一时钟信号xck,当输入上拉模块201在第一时钟信号xck的控制下导通时,将起始信号stv或第n

‑

1级栅极驱动单元goa(n

‑

1)输出的第n

‑

1级级传信号s(n

‑

1)通过导通的电压钳位模块207输出到第一节点q,以对第一节点q进行充电,进而控制第一节点q的电势。其中,输入上拉模块201中的晶体管为p型低温多晶硅薄膜晶体管。另外,第1级栅极驱动单元goa1将起始信号stv输出到第一节点q;n大于或等于2时,第n级栅极驱动单元goa(n)将第n

‑

1级级传信号输出到第一节点q。

34.具体地,输入上拉模块201包括第一p型低温多晶硅薄膜晶体管t1,第一p型低温多晶硅薄膜晶体管t1的栅极接入第一时钟信号xck,第一p型低温多晶硅薄膜晶体管t1的第一极接入起始信号stv或第n

‑

1级栅极驱动单元goa(n

‑

1)输出的第n

‑

1级级传信号s(n

‑

1),第一p型低温多晶硅薄膜晶体管t1的第二极通过电压钳位模块207与第一节点q连接。

35.在本实施例中,级传输出模块202用于输出第n级级传信号s(n),即输出本级的级传信号,以为下一级提供输入信号。级传输出模块202与第一节点q连接,用于接收第二时钟信号ck,且响应于第一节点q的电压而将第二时钟信号ck作为第n级级传信号s(n)输出,第二时钟信号ck为交替的高电平信号和低电平信号,以交替地输出高电平的第n级级传信号s(n)和低电平的第n级级传信号s(n),n为大于或等于1且小于或等于n的整数。其中,级传输出模块202中的晶体管为p型低温多晶硅薄膜晶体管。另外,第二时钟信号ck的脉冲周期与第一时钟信号xck的脉冲周期相同,且第二时钟信号ck的相位与第一时钟信号xck的相位相反。

36.具体地,级传输出模块202包括第二p型低温多晶硅薄膜晶体管t2,第二p型低温多晶硅薄膜晶体管t2的栅极与第一节点q连接,第二p型低温多晶硅薄膜晶体管t2的第一极接入第二时钟信号ck,第二p型低温多晶硅薄膜晶体管t2的第二极连接级传输出模块202输出第n级级传信号s(n)的输出端。

37.在本实施例中,级传维持模块203用于将第n级级传信号s(n)维持在高电平准位。级传维持模块203与第二节点p连接,级传维持模块203用于接入输入信号gas1,响应于第二节点p的电压将输入信号gas1输出至级传输出模块202的输出端,以维持第n级级传信号s(n)的电势。其中。级传维持模块203中的晶体管为p型低温多晶硅薄膜晶体管。输入信号gas1在显示面板100正常工作时均为高电平信号,使得级传维持模块203导通时将高电平信号输出到第n级级传信号s(n)的输出端。输入信号gas1在显示面板异常断电时为低电平信号,使得级传维持模块203输出低电平信号至第n级级传信号s(n)的输出端,第n级级传信号s(n)为低电平信号,输出上拉模块208响应于低电平的第n级级传信号而输出高电平的第n级扫描信号,开关晶体管k导通,显示面板显示。

38.具体地,级传维持模块203包括第四p型低温多晶硅薄膜晶体管t4,第四p型低温多晶硅薄膜晶体管t4的栅极与第二节点p连接,第四p型低温多晶硅薄膜晶体管的第一极接入输入信号gas1,第四p型低温多晶硅薄膜晶体管t4的第二极与级传输出模块202的输出端连接。

39.在本实施例中,第一节点维持模块204用于维持第一节点q的电势。第一节点维持模块204与第一节点q和第二节点p连接,第一节点维持模块204接入第二控制信号,且响应于第二节点p的电压和第二控制信号而维持第一节点q的电势。其中,第一节点维持模块204

中的晶体管为p型低温多晶硅薄膜晶体管。另外,第二控制信号为第二时钟信号ck。

40.具体地,第一节点维持模块204包括第五p型低温多晶硅薄膜晶体管t5以及第六p型低温多晶硅薄膜晶体管t6,第五p型低温多晶硅薄膜晶体管t5的栅极接入第二时钟信号ck,第五p型低温多晶硅薄膜晶体管t5的第一极通过电压钳位模块207连接第一节点q,第六p型低温多晶硅薄膜晶体管t6的栅极连接第二节点p,第六p型低温多晶硅薄膜晶体管t6的第一极接入输入信号gas1,第六p型低温多晶硅薄膜晶体管t6的第二极与第五p型低温多晶硅薄膜晶体管t5的第二极连接。第五p型低温多晶硅薄膜晶体管t5和第六p型低温多晶硅薄膜晶体管t6同时导通时,输入信号gas1的高电平信号输出至第一节点q,使得第一节点q的电势为高电平。

41.在本实施例中,第一节点反馈模块205与第一节点q和第二节点p连接,且第一节点反馈模块205接入第一时钟信号xck,响应于第一节点q的电压而将第一时钟信号xck输出至第二节点p,以调整第二节点p的电势。其中,第一节点反馈模块205中的晶体管为p型低温多晶硅薄膜晶体管。第一节点q的电势为高电平,则第一节点反馈模块205关闭;第一节点q的电势为低电平,则第一节点反馈模块205导通,第一时钟信号xck输出至第二节点p。第一时钟信号xck为高电平信号,则第二节点p的电势为高电平,第四p型低温多晶硅薄膜晶体管t4关闭;第一时钟信号xck为低电平信号,则第二节点p的电势为低电平,第四p型低温多晶硅薄膜晶体管t4导通。

42.具体地,第一节点反馈模块205包括第七p型低温多晶硅薄膜晶体管t7,第七p型低温多晶硅薄膜晶体管t7的栅极与第一节点q连接,第七p型低温多晶硅薄膜晶体管t7的第一极接入第一时钟信号xck,第七p型低温多晶硅薄膜晶体管t7的第二极与第二节点p连接。

43.在本实施例中,第二节点下拉模块206用于拉低第二节点p的电势。第二节点下拉模块206与第二节点p连接,接收第二恒压低电平vgl2和第一时钟信号xck,响应于第一时钟信号xck的控制而将第二恒压低电平vgl2输出至第二节点p,进而拉低第二节点p的电势。其中,第二节点下拉模块206中的晶体管为p型低温多晶硅薄膜晶体管。

44.具体地,第二节点下拉模块206包括第八p型低温多晶硅薄膜晶体管t8,第八p型低温多晶硅薄膜晶体管t8的栅极接入第一时钟信号xck,第八p型低温多晶硅薄膜晶体管t8的第一极连接第二恒压低电平vgl2,第八p型低温多晶硅薄膜晶体管t8的第二极连接第二节点p。

45.在本实施例中,电压钳位模块207用于维持第一节点q的电势。电压钳位模块207连接在输入上拉模块201与第一节点q之间,电压钳位模块207接入第三恒压低电平vgl3,且响应于第三恒压低电平vgl3而处于导通状态。其中,电压钳位模块207中的晶体管为p型低温多晶硅薄膜晶体管。另外,第三恒压低电平vgl3与第二恒压低电平vgl2相同。

46.具体地,电压钳位模块207包括第九p型低温多晶硅薄膜晶体管t9,第九p型低温多晶硅薄膜晶体管t9的栅极接入第三恒压低电平vgl3,第九p型低温多晶硅薄膜晶体管t9的第一极连接第一节点q,第九p型低温多晶硅薄膜晶体管t9的第二极连接与输入上拉模块201的输出端。

47.在本实施例中,第n级栅极驱动单元还包括第一电容器c1,第一电容器c1的第一极连接第一节点q,第一电容器c1的第二极连接级传输出模块202的输出端。第一电容器c1用于通过耦合作用对第一节点q的电势进行自举。

48.在本实施例中,第n级栅极驱动单元还包括第二电容器c2,第二电容器c2的第一极连接第二节点p,第二电容器c2的第二极接入输入信号gas1。

49.在本实施例中,输出上拉模块208的输入端与级传输出模块202的输出端连接,接收恒压高电平vgh,且响应于低电平的第n级级传信号s(n)而输出恒压高电平信号,以输出高电平的第n级扫描信号g(n)。其中,输出上拉模块208的晶体管为p型低温多晶硅薄膜晶体管,以使得输出上拉模块208具有良好的上拉能力,使低电平的第n级扫描信号上拉为高电平的第n级扫描信号的上升沿时间较短,有利于栅极驱动电路能高频输出扫描信号。

50.具体地,输出上拉模块208包括第三p型低温多晶硅薄膜晶体管t3,第三p型低温多晶硅薄膜晶体管t3的栅极与级传输出模块202的输出端连接,第三p型低温多晶硅薄膜晶体管t3的第一极接入恒压高电平vgh,第三p型低温多晶硅薄膜晶体管t3的第二极与第n级栅极驱动单元goa(n)输出第n级扫描信号的输出端连接。

51.在本实施例中,输出下拉模块209的输入端与级传输出模块202的输出端连接,输出下拉模块209接收第一恒压低电平vgl1,且响应于高电平的第n级级传信号s(n)而输出第一恒压低电平vgl1,进而输出低电平的第n级扫描信号g(n)。其中,输出下拉模块209中的晶体管为n型金属氧化物薄膜晶体管,以使输出下拉模块209具有良好的下拉能力,使高电平的第n级扫描信号下拉为低电平的第n级扫描信号对应的下降沿时间较短,有利于栅极驱动电路能高频输出扫描信号。另外,第一恒压低电平vgl1大于第二恒压低电平vgl2。

52.具体地,输出下拉模块209包括第一n型金属氧化物薄膜晶体管t10,第一n型金属氧化物薄膜晶体管t10的栅极连接级传输出模块202的输出端,第一n型金属氧化物薄膜晶体管t10的第一极接入第一恒压低电平vgl1,第一n型金属氧化物薄膜晶体管t10的第二极与第n级栅极驱动单元goa(n)输出第n级扫描信号的输出端连接。

53.在本实施例中,触控维持模块210的输出端与第n级栅极驱动单元goa(n)输出第n级扫描信号的输出端连接,触控维持模块210接收第一恒压低电平vgl1,触控维持模块210接收第一控制信号gas2,且响应于第一控制信号gas2而将第一恒压低电平vgl1输出至第n级栅极驱动单元goa(n)的输出端,进而输出低电平的扫描信号g(n)。触控维持模块210中的晶体管为n型金属氧化物薄膜晶体管,以使触控维持模块210能快速地实现下拉,有利于栅极驱动电路高频输出扫描信号。显示面板100处于触控阶段时,第一控制信号gas2为高电平信号,触控维持模块210导通,触控维持模块210输出第一恒压低电平vgl1作为扫描信号,显示面板100的栅极驱动单元均输出低电平的扫描信号,像素电路30的开关晶体管k处于关闭状态,像素电路不工作。显示面板100处于显示阶段时,第一控制信号gas2为低电平,触控维持模块210关闭。

54.具体地,触控维持模块210包括第二n型金属氧化物薄膜晶体管t11,第二n型金属氧化物薄膜晶体管t11的栅极接入第一控制信号gas2,第二n型金属氧化物薄膜晶体管gas2的第一极接入第一恒压低电平vgl1,第二n型金属氧化物薄膜晶体管t11的第二极连接第n级栅极驱动单元goa(n)的输出端。

55.本技术栅极驱动电路的栅极驱动单元由p型低温多晶硅薄膜晶体管和n型金属氧化物薄膜晶体管组成,由于p型低温多晶硅薄膜晶体管和n型金属氧化物薄膜晶体管均可以采用低温制程制备得到,栅极驱动电路可以采用低温制程制备得到,满足柔性显示面板的低温制程要求。另外,栅极驱动单元的输出上拉模块中的晶体管为p型低温多晶硅薄膜晶体

管,使得输出上拉模块能快速地实现上拉,即快速地将低电平的扫描信号上拉为高电平的扫描信号,栅极驱动单元的输出下拉模块中的晶体管为n型金属氧化物薄膜晶体管,使得输出下拉模块能快速地实现下拉,即快速地将高电平的扫描信号下拉为低电平的扫描信号,快速地上拉配合快速地下拉使得栅极驱动单元能快速交替地输出高电平的扫描信号和低电平的扫描信号,进而实现扫描线的高频驱动,有利于显示面板实现高频显示。

56.如图3所示,其为图2所示栅极驱动单元对应的驱动时序图。其中,s(n

‑

1)为第n

‑

1级级传信号,xck为第一时钟信号,ck为第二时钟信号,s(n)为第n级级传信号,g(n)为第n级扫描信号,q(n)为第一节点的电势,p(n)为第二节点的电势,第n级栅极驱动单元goa(n)的驱动过程包括如下几个阶段:

57.充电阶段t1,第n

‑

1级级传信号s(n

‑

1)为低电平信号,第一时钟信号xck为低电平信号,第二时钟信号ck为高电平信号。第一p型低温多晶硅薄膜晶体管t1导通,第n

‑

1级级传信号s(n

‑

1)的低电平信号输入到第一节点q,以对第一节点q进行充电,第一节点q的电势变低,第二p型低温多晶硅薄膜晶体管t2导通,第二时钟信号ck的高电平信号输出为高电平的第n级级传信号s(n),第一n型金属氧化物薄膜晶体管t10导通,输出低电平的扫描信号g(n)。另外,第八p型低温多晶硅薄膜晶体管t8导通,第二恒压低电平vgl2写入到第二节点p,第七p型低温多晶硅薄膜晶体管t7导通,第一时钟信号xck的低电平信号写入到第二节点p,第二节点p的电势为低电平,第四p型低温多晶硅薄膜晶体管t4导通,输入信号gas1的高电平信号输出至级传输出模块202的输出端。

58.输出阶段t2,第n

‑

1级级传信号s(n

‑

1)为高电平信号,第一时钟信号xck为高电平信号,第二时钟信号ck为低电平信号。第一p型低温多晶硅薄膜晶体管t1关闭,第九p型低温多晶硅薄膜晶体管t9导通,第一电容器c1保持第一节点q的电势为低电平,第二时钟信号ck的低电平信号输出为第n级级传信号s(n),第n级级传信号s(n)为低电平信号,第一电容器c1的耦合作用使得第一节点q的电势进一步地拉低,第二p型低温多晶硅薄膜晶体管t2导通输出低电平信号的第n级级传信号,第三p型低温多晶硅薄膜晶体管t3导通,输出高电平的扫描信号g(n)。第八p型低温多晶硅薄膜晶体管t8关闭,第七p型低温多晶硅薄膜晶体管t7导通,第一时钟信号xck的高电平信号输出至第二节点p,第二节点p的电势为高电平,第四p型低温多晶硅薄膜晶体管t4关闭,第六p型低温多晶硅薄膜晶体管t6关闭。

59.下拉阶段t3,第n

‑

1级级传信号s(n

‑

1)为高电平信号,第一时钟信号xck为低电平信号,第二时钟信号ck为高电平信号。第一p型低温多晶硅薄膜晶体管t1导通,第n

‑

1级级传信号s(n

‑

1)的高电平信号通过导通的第一p型低温多晶硅薄膜晶体管t1和导通的第九p型低温多晶硅薄膜晶体管t9输出至第一节点q,第一节点q的电势为高电平,第二p型低温多晶硅薄膜晶体管t2关闭。第七p型低温多晶硅薄膜晶体管t7关闭,第八p型低温多晶硅薄膜晶体管t8导通,第二恒压低电平vgl2写入到第二节点p,第二节点p的电势为低电平,第四p型低温多晶硅薄膜晶体管t4导通,第六p型低温多晶硅薄膜晶体管t6导通,第五p型低温多晶硅薄膜晶体管t5关闭,输入信号gas1的高电平信号输出为高电平的第n级级传信号,第一n型金属氧化物薄膜晶体管t10导通输出低电平的扫描信号g(n)。

60.第一节点上拉阶段t4,第n

‑

1级级传信号s(n

‑

1)为低电平信号,第一时钟信号xck为高电平信号,第二时钟信号ck为低电平信号。第一p型低温多晶硅薄膜晶体管t1关闭,第一电容器c1维持第一节点q的电势为高电平,第二p型低温多晶硅薄膜晶体管t2关闭。第七p

型低温多晶硅薄膜晶体管t7关闭,第八p型低温多晶硅薄膜晶体管t8关闭,第二电容器c2维持第二节点p的电势为低电平,第六p型低温多晶硅薄膜晶体管t6导通,第五p型低温多晶硅薄膜晶体管t5导通,输入信号gas1的高电平信号输出至第一节点q,第一节点q的电势上拉。

61.需要说明的是,充电阶段t1、输出阶段t2、下拉阶段t3以及第一节点上拉阶段t4依次进行且组成一个驱动周期。由于在输出阶段t2,第三p型低温多晶硅薄膜晶体管t3具有快速的上拉能力,在下拉阶段t3,第一n型金属氧化物薄膜晶体管t10具有快速的下拉能力,保证高电平的扫描信号和低电平的扫描信号能交替快速地输出,栅极驱动电路能高频地输出扫描信号,有利于显示面板实现高频显示,配合显示面板的像素电路能实现低频或超低频显示,使得显示面板能实现高频低频的动态显示。

62.在本实施例中,如图1所示,解复用电路40包括多条数据总线、多个第一类开关demux1、多个第二类开关demux2,多条数据总线包括数据总线i1、数据总线i2、数据总线i3以及数据总线i4,多个第一类开关demux1与第一类控制信号线连接,多个第二类开关demux2与第二类控制信号线连接,相邻两条数据总线传输的数据信号的极性相反,每条数据总线与一个第一类开关demux1和一个第二类开关demux2连接,与同一个数据总线连接的第一类开关demux1和第二类开关demux2中的一者与第一类数据线d(m)连接且另一者和与第一类数据线d(m)相邻的第二类数据线d(m 1)连接。第一类开关demux1与第二类开关demux2均为p型低温多晶硅薄膜晶体管,即解复用电路40中的晶体管为p型低温多晶硅薄膜晶体管,以使解复用电路40的制程满足柔性显示面板的低温制程要求的同时,使得解复用电路40中的晶体管与栅极驱动电路20中的晶体管相同,有利于简化制程。

63.如图4所示,其为本技术另一实施例解复用电路的平面示意图。图4所示解复用电路40与图1所示解复用电路基本相似,不同之处在于,解复用电路40还包括第三类开关demux3,第三类开关demux3为p型低温多晶硅薄膜晶体管,每条数据总线与一个第一类开关demux1、一个第二类开关demux2以及一个第三类开关demux3连接,第一类开关demux1和第三类开关demux3均与第一类数据线d(m)和第二类数据线中的一者连接,第二类开关demux2与第一类数据线d(m)和第二类数据线d(m 1)中的另一者连接。

64.如图5所示,其为本技术另一实施例解复用电路的平面示意图。图5所示解复用电路与图4所示解复用电路基本相似,不同之处在于,解复用电路还包括第四类开关demux4、第五类开关demux5以及第六类开关demux6,第四类开关demux4、第五类开关demux5以及第六类开关demux6均为p型低温多晶硅薄膜晶体管,每条数据总线与一个第一类开关demux1、一个第二类开关demux2、一个第三类开关demux3、一个第四类开关demux4、一个第五类开关demux5以及一个第六类开关demux6连接,第一类开关demux1、第三类开关demux3以及第五类开关demux5均与第一类数据线和第二类数据线中的一者连接,第二类开关demux2、第四类开关demux4以及第六类开关demux6均与第一类数据线和第二类数据线中的另一者连接。

65.如图6及图7所示,图6为图1所示显示面板的显示区的截面示意图,图7为图1所示显示面板的外围区的截面示意图。结合图6和图7可知,显示面板100包括基板101、缓冲层102、p型低温多晶硅有源层103、第一栅极绝缘层104、第一金属层105、层间绝缘层106、第二金属层107、第二栅极绝缘层108、n型金属氧化物有源层109、第三金属层110、第一钝化层111、平坦化层112、公共电极层113、第二钝化层114以及像素电极层115。

66.在本实施例中,基板101为聚酰亚胺层。由于基板101为聚酰亚胺层,聚酰亚胺层在

高温制程下性能会受影响,故基板101上的膜层需要在低温制程下制备得到。

67.在本实施例中,缓冲层102位于显示面板100的显示区100a和外围区100b,且缓冲层102设置于基板101上。缓冲层102的制备材料为氮化硅或氧化硅中的至少一种。

68.在本实施例中,p型低温多晶硅有源层103设置于缓冲层102上,p型低温多晶硅有源层103位于显示面板100的显示区100a和外围区100b,p型低温多晶硅有源层103包括上述栅极驱动电路20中的第一p型低温多晶硅薄膜晶体管t1的有源层、第二p型低温多晶硅薄膜晶体管t2的有源层、第三p型低温多晶硅薄膜晶体管t3的有源层、第四p型低温多晶硅薄膜晶体管t4的有源层、第五p型低温多晶硅薄膜晶体管t5的有源层、第六p型低温多晶硅薄膜晶体管t6的有源层、第七p型低温多晶硅薄膜晶体管t7的有源层、第八p型低温多晶硅薄膜晶体管t8的有源层、第九p型低温多晶硅薄膜晶体管t9的有源层以及解复用电路40中的晶体管的有源层。p型低温多晶硅有源层103不需要进行轻掺杂,使得避免采用高温制程,且减少需要的光罩数目。

69.在本实施例中,第一栅极绝缘层104位于显示面板100的显示区100a和外围区100b,且第一栅极绝缘层104覆盖p型低温多晶硅有源层103和缓冲层102。第一栅极绝缘层104的制备材料为氮化硅或氧化硅中的至少一种。

70.在本实施例中,第一金属层105设置于第一栅极绝缘层104上,第一金属层105包括第一p型低温多晶硅薄膜晶体管t1至第九p型低温多晶硅薄膜晶体管t9的栅极,第一p型低温多晶硅薄膜晶体管t1至第九p型低温多晶硅薄膜晶体管t9的栅极1051均设置于外围区100b,第一金属层105还包括与第二n型金属氧化物薄膜晶体管t11的栅极、第一n型金属氧化物薄膜晶体管t10的栅极以及开关晶体管k的栅极连接的传输导线1052,传输导线1052设置显示区100a和外围区100b。第一金属层105的制备材料选自钼、铝、钛、铜、银以及镍中的至少一种。

71.在本实施例中,层间绝缘层106位于显示面板100的显示区100a和外围区100b,层间绝缘层106覆盖第一金属层105和第一栅极绝缘层104。层间绝缘层106的制备材料为氮化硅和氧化硅中的至少一种。

72.在本实施例中,第二金属层107设置于层间绝缘层106上,第二金属层107包括第一p型低温多晶硅薄膜晶体管t1至第九p型低温多晶硅薄膜晶体管t9的源漏电极1071,第一p型低温多晶硅薄膜晶体管t1至第九p型低温多晶硅薄膜晶体管t9的源漏电极1071通过贯穿层间绝缘层106和第一栅极绝缘层104的过孔与对应的低温多晶硅有源层接触,第二金属层107还包括第二n型金属氧化物薄膜晶体管t11以及第一n型金属氧化物薄膜晶体管t10的栅极1072、开关晶体管k的栅极1073,即p型低温多晶硅薄膜晶体管的源漏电极与n型金属氧化物薄膜晶体管的栅极同层设置,第二n型金属氧化物薄膜晶体管t11以及第一n型金属氧化物薄膜晶体管t10的栅极1072设置于外围区100b,开关晶体管k的栅极1073设置于显示区100a。第二金属层107的制备材料选自钼、铝、钛、铜、银以及镍中的至少一种。

73.在本实施例中,第二栅极绝缘层108位于显示区100a和外围区100b,第二栅极绝缘层108覆盖第二金属层107和层间绝缘层106。第二栅极绝缘层108的制备材料为氮化硅或氧化硅中的至少一种。

74.在本实施例中,n型金属氧化物有源层109设置于第二栅极绝缘层108上,n型金属氧化物有源层109包括第二n型金属氧化物薄膜晶体管t11的有源层和第一n型金属氧化物

薄膜晶体管t10的有源层1091、开关晶体管k的有源层1092。n型金属氧化物有源层109的制备材料为铟镓锌氧化物。

75.在本实施例中,第三金属层110设置于n型金属氧化物有源层109和第二栅极绝缘层108,第三金属层110包括第二n型金属氧化物薄膜晶体管t11和第一n型金属氧化物薄膜晶体管t10的源漏电极1101、开关晶体管k的源漏电极1102,第三金属层110还包括触控引线1103。第三金属层110选自钼、铝、钛、铜、银以及镍中的至少一种。在外围区100b,n型金属氧化物薄膜晶体管的源极与对应电性连接的p型低温多晶硅薄膜晶体管的漏极通过贯穿第二栅极绝缘层108的过孔连接。

76.在本实施例中,第一钝化层111位于显示区100a和外围区100b,第一钝化层111覆盖第三金属层110和第二栅极绝缘层108。第一钝化层111的制备材料选自氮化硅和氧化硅中的至少一种。

77.在本实施例中,平坦化层112位于显示区100a和外围区100b,平坦化层112设置于第一钝化层111上。平坦化层112为有机层。平坦化层112的制备材料为聚酰亚胺、聚丙烯酸酯等。

78.在本实施例中,公共电极层113设置于平坦化层112上。公共电极层113包括多个公共电极,多个公共电极复用为触控电极,多个公共电极分时复用。多个公共电极与对应电性连接的触控走线1103通过贯穿平坦化层112和第一钝化层111的过孔电性连接。公共电极层113的制备材料为氧化铟锌。

79.在本实施例中,第二钝化层114位于显示区100a和外围区100b,第二钝化层114覆盖公共电极层113和平坦化层112,第二钝化层114的制备材料选自氮化硅和氧化硅中的至少一种。

80.在本实施例中,像素电极层115位于显示区100a,像素电极层115设置于第二钝化层114上,像素电极层115包括多个像素电极,像素电极与对应的开关晶体管k的漏极通过贯穿第二钝化层114、平坦化层112以及第一钝化层111的过孔连接。像素电极层115的制备材料为氧化铟锡。

81.本实施例显示面板将p型低温多晶硅薄膜晶体管采用顶栅设计,n型金属氧化物薄膜晶体管采用底栅设计,p型低温多晶硅薄膜晶体管的源漏电极与n型金属氧化物薄膜晶体管的栅极同层设置,传输触控信号的触控走线与n型金属氧化物薄膜晶体管的源漏电极同层设置,公共电极复用为触控电极。由于p型低温多晶硅薄膜晶体管和n型金属氧化物薄膜晶体管均可以采用低温制程制备得到,满足柔性显示面板的低温制程要求,有利于显示面板实现柔性显示。

82.以上实施例的说明只是用于帮助理解本技术的技术方案及其核心思想;本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例的技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。