含内嵌式电阻式随机存取存储器的显示驱动集成电路以及含该显示驱动集成电路的显示装置

1.相关申请的交叉引用

2.本技术要求申请号为62/899621,申请日为2019年9月12日,名称为“用于显示像素补偿的内嵌式rram”的美国临时申请的权益,并将该申请的内容整体援引于此。

技术领域

3.本发明总体涉及显示驱动集成电路,尤其涉及含内嵌式电阻式随机存取存储器的显示驱动集成电路以及含该显示驱动集成电路的显示装置。

背景技术:

4.显示驱动集成电路(ddic)在特定微处理器/微控制器/专用集成电路(asic)/接口与包括但不限于液晶显示器(lcd)、发光二极管(led)显示器、有机发光二极管(oled)显示器等在内的特定显示装置之间提供接口功能。显示驱动器一般通过行业标准的通用接口接收命令和数据,并生成具有相应电压/电流/时间安排的信号,以使得显示器显示所需的图像。

5.ddic还可提供像素补偿功能。显示面板在经历过长时间持续的电应力之后会发生老化。例如,显示面板通常包括数万个显示像素,这些显示像素可受控显示图像或活动图像。每一显示像素可包括用于驱动显示元件的薄膜晶体管(tft)。长时间使用后的电应力将暂时性或永久性地改变薄膜晶体管和显示元件的特性,进而影响显示质量。

6.由于显示面板的老化取决于显示面板的使用情况,因此可以对其进行预先补偿。因此,显示面板通常均配备能够对tft驱动元件和/或显示元件的特性变化进行补偿的ddic。

技术实现要素:

7.本发明的一个方面涉及一种显示驱动集成电路。该显示驱动集成电路用于接收针对显示面板的显示感测信号的输入端;与所述输入端连接的电阻式随机存取存储器,该电阻式随机存取存储器用于存储表示所述显示感测信号的感测值;显示补偿逻辑,该显示补偿逻辑与所述电阻式随机存取存储器连接,以接收所述感测值,该显示补偿逻辑用于根据所述感测值确定补偿值,以使得所述显示面板能够调节显示控制信号;以及输出端,该输出端与所述显示补偿逻辑连接,以向所述显示面板发送显示补偿电压信号。所述显示补偿电压信号基于所述补偿值生成。在一些实施方式中,所述显示感测信号表示流过所述显示面板的显示像素以及与该显示像素连接的显示像素驱动元件的电流。

8.在一些实施方式中,所述显示驱动集成电路还包括与所述显示补偿逻辑连接的数模转换器,该数模转换器用于将所述补偿值转换成所述显示补偿电压信号。在一些实施方式中,所述显示驱动集成电路还包括与所述输入端连接的积分放大器,该积分放大器用于将所述显示感测信号转换成感测电压信号。在一些实施方式中,所述显示驱动集成电路还

包括与所述积分放大器连接的模数转换器,该模数转换器用于将所述感测电压信号转换成用于存入所述电阻式随机存取存储器的感测值。

9.在一些实施方式中,所述显示驱动集成电路还包括与所述积分放大器连接的比较器,该比较器用于获取所述感测电压信号,并将其与参考电压信号相比较,该比较器还用于生成数字值,以作为用于存入所述电阻式随机存取存储器的感测值。

10.在一些实施方式中,所述显示驱动集成电路还包括与所述输入端连接的电流比较器,该电流比较器用于获取所述显示感测信号,并将其与参考电流信号相比较,该电流比较器还用于生成数字值,以作为用于存入所述电阻式随机存取存储器的感测值。所述显示感测信号表示流过与显示元件连接的显示像素驱动元件的电流。

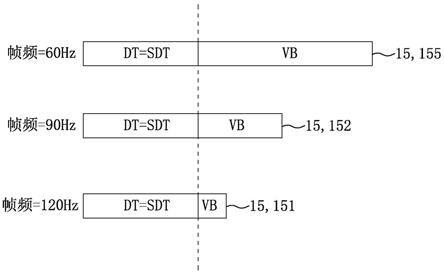

11.本发明的一个方面涉及一种显示驱动集成电路。该显示驱动集成电路包括:用于接收针对显示面板的显示感测信号的输入端;与所述输入端连接的积分放大器,该积分放大器用于将所述显示感测信号转换成感测电压信号;与所述积分放大器连接的第一电压放大器,该第一电压放大器用于通过放大所述感测电压信号而生成模拟感测信号;与所述第一电压放大器连接的电阻式随机存取存储器,该电阻式随机存取存储器用于存储所述模拟感测信号;与所述电阻式随机存取存储器连接的第二电压放大器,该第二电压放大器用于通过放大所述模拟感测信号而生成显示补偿电压信号;以及输出端,该输出端与所述第二电压放大器连接,以向所述显示面板发送所述显示补偿电压信号。

12.在一些实施方式中,所述第一电压放大器用于通过根据所述电阻式随机存取存储器的电阻状态放大所述感测电压信号而生成所述模拟感测信号。

13.本发明的另一方面涉及一种显示装置。该显示装置包括:显示面板;以及显示驱动集成电路,该显示驱动集成电路与所述显示面板连接,以控制该显示面板。该显示驱动集成电路包括:用于接收针对显示面板的显示感测信号的输入端;与所述输入端连接的电阻式随机存取存储器,该电阻式随机存取存储器用于存储表示所述显示感测信号的感测值;显示补偿逻辑,该显示补偿逻辑与所述电阻式随机存取存储器连接,以接收所述感测值,该显示补偿逻辑用于根据所述感测值确定补偿值,以使得所述显示面板能够调节显示控制信号;以及输出端,该输出端与所述显示补偿逻辑连接,以向所述显示面板发送显示补偿电压信号。所述显示补偿电压信号基于所述补偿值生成。

14.本发明的另一方面涉及一种显示装置。该显示装置包括:显示面板;以及显示驱动集成电路,该显示驱动集成电路与所述显示面板连接,以控制该显示面板。该显示驱动集成电路包括:用于接收针对显示面板的显示感测信号的输入端;与所述输入端连接的积分放大器,该积分放大器用于将所述显示感测信号转换成感测电压信号;与所述积分放大器连接的第一电压放大器,该第一电压放大器用于通过放大所述感测电压信号而生成模拟感测信号;与所述第一电压放大器连接的电阻式随机存取存储器,该电阻式随机存取存储器用于存储所述模拟感测信号;与所述电阻式随机存取存储器连接的第二电压放大器,该第二电压放大器用于通过放大所述模拟感测信号而生成显示补偿电压信号;以及输出端,该输出端与所述第二电压放大器连接,以向所述显示面板发送所述显示补偿电压信号。

15.当参考附图考察下文及下附权利要求时,本文公开的各装置、系统及方法的上述和其他特征以及操作方法和相关结构元件的功能将变得更加显而易见,所有附图均构成本说明书的一部分。然而,应该明确理解的是,附图仅出于说明和描述目的,并不旨在界定出

本发明的限制范围。应该理解的是,无论是上文的概述内容,还是下文的详述内容,均仅为举例性和阐述性内容,并不对所要求保护的本发明有所限制。

附图说明

16.本技术各种实施方式的某些特征具体描述于下附权利要求中。通过参考下文具体描述以及附图,可以获得对本技术特征和优点的更佳理解,下文具体描述给出了对本发明原理加以利用的说明性实施方式。通过参考以下附图,可更加易于理解本发明的非限制性实施方式。

17.图1所示为根据一种例示实施方式包括显示驱动集成电路的显示装置。

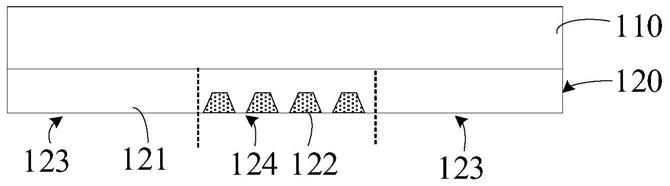

18.图2所示为根据一种例示实施方式包括显示驱动集成电路的另一显示装置。

19.图3所示为根据一种例示实施方式包括显示驱动集成电路的又一显示装置。

20.图4所示为根据一种例示实施方式包括显示驱动集成电路的又一显示装置。

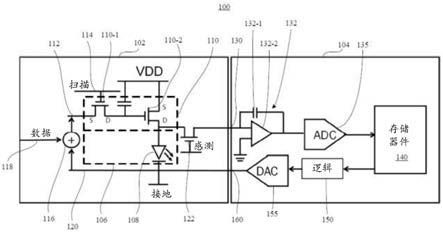

21.图5所示为根据一种例示实施方式包括显示驱动集成电路的又一显示装置。

具体实施方式

22.以下,参考附图,描述本发明的非限制性实施方式。应该理解的是,本文公开的任何实施方式的具体特征和方面均可与本文公开的任何其他实施方式的具体特征和方面一起使用且/或相互结合。还应该理解的是,此类实施方式为举例,而且仅阐述了本发明范围内的一小部分实施方式。对于本发明所属技术领域的技术人员而言容易理解的各种变化和修饰均视为落于如下附权利要求进一步限定的本发明精神、范围及构思之内。

23.本文公开的技术提供能够补偿显示像素的显示质量变化的ddic。该ddic可包括能够减小芯片大小、能耗以及电路成本的内嵌式电阻式随机存取存储器(rram)。本文提供的技术方案能够提高ddic以及配备ddic显示装置的性能。

24.以下,参考附图,描述各实施方式。首先,参考图1,该图1所示为根据一种例示实施方式的显示装置100。显示装置100包括显示面板102以及ddic 104。显示面板102包括具有多个像素的像素阵列。图1中示出了一个例示像素106。像素106包括显示元件108以及用于控制显示元件108的显示像素驱动元件110。显示元件108可以为任何发光元件,如lcd单元、led、oled等。在图示实施方式中,显示元件108为oled。显示像素驱动元件110可包括一个或多个二极管、一个或多个晶体管或其组合,或者包括其他电路。在图示实施方式中,显示像素驱动元件110包括两个薄膜晶体管110

‑

1和110

‑

2。

25.像素106与数据线112连接,以接收数据信号/显示控制信号,并且与扫描线114连接,以接收扫描信号(scan)。虽然图1中未示出,但显示面板包括多条数据线112和多条扫描线114。数据线112与数据源116连接,该数据源116根据显示数据输入(data)118以及ddic 104提供的补偿信号120提供数据信号。tft 110

‑

1的栅极与扫描线114连接,tft 110

‑

1的源极与数据线112连接,tft 110

‑

1的漏极与tft 110

‑

2的栅极连接。tft 110

‑

2的源极与电压vdd连接,tft 110

‑

2的漏极与显示元件108连接。显示元件108的一端与tft 110

‑

2的漏极连接,显示元件108的另一端接地。当来自扫描线114的扫描信号导通tft 110

‑

1的栅极时,数据线112提供数据信号,以控制tft 110

‑

2的栅极。取决于提供至tft 110

‑

2栅极的控制信号的幅度,vdd可向显示元件108提供可变电流,从而使得显示元件108变暗或变亮。

26.为了向像素106提供补偿,显示面板102还包括感测元件122。感测元件122可包括一个或多个二极管、一个或多个晶体管或其组合,或者包括其他电路。在图示实施方式中,感测元件122为tft。感测元件122连接于像素106与ddic 104的输入端130之间。感测元件122可用于感测显示感测信号。显示感测信号可例如包括流过显示像素驱动元件110的tft 110

‑

2的电流,流过显示元件108的电流,以及/或者同时流过显示像素驱动元件110的tft 110

‑

2以及显示元件108的电流。

27.ddic 104包括输入端130、存储器件140、显示补偿逻辑150以及输出端160。输入端130用于接收显示面板102的显示感测信号。例如,输入端130可从显示面板的感测元件122接收显示感测信号。存储器件140与输入端130连接,且用于存储表示显示感测信号的感测值。存储器件140包括电阻式随机存取存储器(rram)。rram 140既可在数字模式(图1)下操作,也可在模拟模式(图5)下操作。在现有技术中,存储器件可以为片上静态随机存取存储器(sram)、片外nor闪存等。sram的存储单元一般需要六个晶体管,而rram的存储单元仅需要一个晶体管,因此占用更小的芯片面积。此外,sram为需要通过备用电源保持数据的易失性存储器,而rram为非易失性存储器,无需通过备用电源保持数据,因此功耗更小。rram所需的读取电流与sram阵列相近或者更小。此外,rram阵列的响应快于sram阵列。将片外nor闪存作为存储器件140的缺点可能会存在包括输入/输出带宽有限、功耗高以及成本更高在内的缺点。

28.显示补偿逻辑150与rram 140连接,以接收感测值,并用于根据该感测值确定补偿值,从而使得显示面板102能够调节显示控制信号(如data)。显示补偿逻辑150可例如编程为内含补偿值查找表。显示补偿逻辑150可读取感测值,并根据查找表确定对应的补偿值。

29.输出端160与显示补偿逻辑150连接,以向显示面板102发送显示补偿电压信号。显示补偿电压信号根据补偿值生成。数据源116接收显示补偿电压信号120以及显示数据输入(data)118,以生成针对显示像素106的数据信号。在一种实施方式中,数据源116为通过将显示补偿电压信号120与显示数据输入(data)118相加而生成针对显示像素106的数据信号的加法器。

30.在一些实施方式中,ddic 104可进一步包括数模转换器(dac)155,该dac与显示补偿逻辑150连接,并用于将接收自显示补偿逻辑150的补偿值转换为显示补偿电压信号120。接收自显示补偿逻辑150的补偿值可例如为表示显示像素106补偿水平的数字值。dac 155将该数字值转换为模拟显示补偿电压信号,该信号可由显示面板102内的数据源116用于生成针对显示像素106的数据信号。

31.在一些实施方式中,ddic 104可进一步包括积分放大器132,该积分放大器与输入端130连接,并用于将接收自输入端130的显示感测信号转换为感测电压信号。感测元件122的输出端可例如向ddic的输入端130提供电流信号(显示感测信号)。该电流信号由积分放大器132转换为电压信号(感测电压信号)。在图示实施方式中,积分放大器132包括与放大器132

‑

2并联的电容器132

‑

1。

32.在一些实施方式中,ddic 104可进一步包括模数转换器(adc)135,该adc与积分放大器132连接,并用于获取感测电压信号,并将其转换为待存储于rram 140内的感测值。adc 135可例如将模拟感测电压信号转换为待存储于以数字模式编程的rram 140内的数字值。

33.由于ddic 104可内嵌rram 140,因此ddic 104提供了一种快速补偿方案。由于

rram 140中每一存储单元可由一个晶体管构成,因此rram 140占据更小的芯片面积,从而降低ddic 104的制造成本。另外,rram 140为非易失性存储器,而且功耗低于sram等现有存储器。本文公开的技术所提供的ddic 104性能更高且成本更低。

34.现在参考图2,该图2所示为根据一种例示实施方式的显示装置200。显示装置200包括显示面板202和ddic 204。显示面板202包括具有多个像素的像素阵列。图2中示出了一个例示像素206。像素206包括显示元件208以及用于控制显示元件208的显示像素驱动元件210。显示像素驱动元件210包括两个薄膜晶体管210

‑

1和210

‑

2。像素206与数据线212连接,以接收数据信号/显示控制信号,并与扫描线214连接,以接收扫描信号(scan)。虽然图2中未示出,但显示面板202包括多条数据线212和多条扫描线214。显示面板202还包括数据源216,该数据源216根据显示数据输入(data)218以及ddic 204提供的补偿信号220提供数据信号。显示面板202还包括感测元件222。显示面板202与图1显示面板102类似,关于显示面板202的细节,可以参考显示面板102。

35.ddic 204包括输入端230、积分放大器232、比较器235、存储器件240、显示补偿逻辑250、dac 255以及输出端260。输入端230用于接收显示面板202的显示感测信号。输入端230可例如从显示面板202的感测元件222接收显示感测信号。积分放大器232与输入端230连接,并用于将接收自输入端230的显示感测信号转换为感测电压信号。例如,感测元件222的输出端可向ddic的输入端230提供电流信号(显示感测信号)。该电流信号由积分放大器232转换成电压信号(感测电压信号)。在图示实施方式中,积分放大器232包括与放大器232

‑

2并联的电容器232

‑

1。

36.比较器235与积分放大器232连接,并用于获取感测电压信号,并将其与一个或多个参考电压信号(vref)进行比较,以生成待作为感测值存储于存储器件240中的数字值。例如,在一种最简单的形式中,比较器235可将感测电压信号与参考电压信号相比较。比较器235可通过生成逻辑“1”表示感测电压信号大于参考电压信号,并可通过生成逻辑“0”表示感测电压信号不大于参考电压信号。例如,逻辑“1”可表示显示像素功能正常,无需补偿,而逻辑“0”可表示显示像素品质下降,需要补偿机制提升其显示像素的发光效果;反之亦然。随后,比较器235可将该一个比特的数字数据发送给存储器件240,以供保存。在一些实施方式中,比较器235可将感测电压信号与多个参考电压信号比较,并生成多个比特的数字值,以表示显示像素的补偿水平。

37.存储器件240通过积分放大器232和比较器235与输入端230连接。存储器件240用于存储表示输入端230所接收显示感测信号的感测值。在图示实施方式中,存储器件240与比较器235连接,以接收且存储比较器235生成的感测值。存储器件240包括电阻式随机存取存储器(rram)。rram 240可在数字模式、模拟模式或数模混合模式下操作。在图2所示实施方式中,rram 240以数字模式或数模混合模式编程,以存储比较器235生成的数字感测值。

38.显示补偿逻辑250与rram 240连接,以接收感测值,并用于根据该感测值确定补偿值,以使得显示面板202能够调节显示控制信号(如data)。例如,显示补偿逻辑250可编程为内含补偿值查找表。显示补偿逻辑250可读取感测值,并根据查找表确定对应的补偿值。在一些实施方式中,显示补偿逻辑250可与rram 240集成在一起。

39.dac 255与显示补偿逻辑250连接,并用于将接收自显示补偿逻辑250的补偿值转换成显示补偿电压信号220。接收自显示补偿逻辑250的补偿值可例如为表示显示像素206

补偿水平的数字值。dac 255将该数字值转换为模拟显示补偿电压信号220,该信号可由显示面板202内的数据源216用于生成针对显示像素206的数据信号。

40.输出端260通过dac 255与显示补偿逻辑250连接,以将显示补偿电压信号220发送给显示面板202。显示面板202内的数据源216接收显示补偿电压信号220以及显示数据输入218,以生成针对显示面板202内显示像素206的数据信号。

41.由于ddic 204可内嵌rram 240,因此ddic 204提供了一种高效快速的补偿方案。ddic 204内含的比较器235生成的感测值所包含的数字可少于用于生成表示电压信号的数字值的adc 135(图1)的输出所包含的数字。由于rram 240中每一存储单元可由一个晶体管构成,因此rram 240占据更小的芯片面积,从而降低ddic 204的制造成本。另外,rram 240为非易失性存储器,而且功耗低于sram等现有存储器。本文公开的技术所提供的ddic 204性能更高且成本更低。

42.图3所示为根据一种例示实施方式的显示装置300。显示装置300包括显示面板302和ddic 304。显示面板302包括具有多个像素的像素阵列。图3中示出了一个例示像素306。像素306包括显示元件308以及用于控制显示元件308的显示像素驱动元件310。显示像素驱动元件310包括两个薄膜晶体管310

‑

1和310

‑

2。像素306与数据线312连接,以接收数据信号/显示控制信号,并与扫描线314连接,以接收扫描信号(scan)。虽然图3中未示出,但显示面板包括多条数据线312和多条扫描线314。显示面板302还包括数据源316,该数据源316根据显示数据输入(data)318以及ddic 304提供的补偿信号320提供数据信号。显示面板302还包括感测元件322。显示面板302与图1显示面板102类似,关于显示面板302的细节,可以参考显示面板102。

43.ddic 304包括输入端330、电流比较器335、存储器件340、显示补偿逻辑350、dac 355以及输出端360。输入端330用于接收针对显示面板302的显示感测信号。输入端330可例如从显示面板302的感测元件322接收显示感测信号。在图示实施方式中,显示元件308断开连接,而且显示感测信号为电流信号,该电流信号表示流过与显示元件308连接的显示像素驱动元件310

‑

2的电流。

44.电流比较器335与输入端330连接,并用于获取显示感测信号,且将其与参考电流信号(i

ref

)相比较,以生成待作为感测值存入存储器件340的数字值。

45.例如,在一种最简单的形式中,电流比较器335可将显示感测信号与一个参考电流信号相比较。比较器335可通过生成逻辑“1”表示显示感测信号大于参考电流信号,并可通过生成逻辑“0”表示显示感测信号不大于参考电流信号。例如,逻辑“1”可表示显示像素驱动元件310

‑

2功能正常,无需补偿,而逻辑“0”可表示显示像素驱动元件310

‑

2品质下降,需要补偿机制提升显示像素306的发光效果。随后,电流比较器335可将该一个比特的数字数据发送给存储器件340,以供保存。在一些实施方式中,电流比较器335可将显示感测信号与多个参考电流信号比较,并生成多个比特的数字值,以表示显示像素306的补偿水平。在该方案中,可预先确定显示面板302的多种补偿水平。

46.存储器件340通过电流比较器335与输入端330连接。存储器件340用于存储表示输入端330所接收显示感测信号的感测值。在图示实施方式中,存储器件340与电流比较器335连接,以接收且存储电流比较器335生成的感测值。存储器件340包括rram。rram 340可在数字模式、模拟模式或数模混合模式下操作。在图3所示实施方式中,rram 340以数字模式或

数模混合模式编程,以存储电流比较器335生成的数字感测值。

47.显示补偿逻辑350与rram 340连接,以接收感测值,并用于根据该感测值确定补偿值,以使得显示面板302能够调节显示控制信号(如data)。例如,显示补偿逻辑350可编程为内含补偿值查找表。显示补偿逻辑350可读取感测值,并根据查找表确定对应的补偿值。在一些实施方式中,显示补偿逻辑350可与rram 340集成在一起。

48.dac 355与显示补偿逻辑350连接,并用于将接收自显示补偿逻辑350的补偿值转换成显示补偿电压信号。接收自显示补偿逻辑350的补偿值可例如为表示显示像素306补偿水平的数字值。dac 355将该数字值转换为模拟显示补偿电压信号,该信号可由显示面板302内的数据源318用于生成针对显示像素306的数据信号。

49.输出端360通过dac 355与显示补偿逻辑350连接,以将显示补偿电压信号发送给显示面板302。显示面板302内的数据源316接收显示补偿电压信号320以及显示数据输入(data)318,以生成针对显示面板302内显示像素306的数据信号。

50.由于ddic 304可内嵌rram 340,因此ddic 304提供了一种高效快速的补偿方案。ddic 304内含的电流比较器335生成的感测值所包含的数字可少于用于生成表示电压信号的数字值的adc 135(图1)的输出所包含的数字。由于rram 340中每一存储单元可由一个晶体管构成,因此rram 340占据更小的芯片面积,从而降低ddic 304的制造成本。另外,rram 340为非易失性存储器,而且功耗低于sram等现有存储器。本文公开的技术所提供的ddic 304性能更高且成本更低。

51.图4所示为根据一种例示实施方式的另一显示装置400。显示装置400包括显示面板402和ddic 404。显示面板402包括具有多个像素的像素阵列。图4中示出了一个例示像素406。像素406包括显示元件408以及用于控制显示元件408的显示像素驱动元件410。显示像素驱动元件410包括两个薄膜晶体管410

‑

1和410

‑

2。像素406与数据线412连接,以接收数据信号/显示控制信号,并与扫描线414连接,以接收扫描信号(scan)。虽然图4中未示出,但显示面板包括多条数据线412和多条扫描线414。显示面板402还包括数据源416,该数据源416根据显示数据输入(data)418以及ddic 404提供的补偿信号420提供数据信号。显示面板402还包括感测元件422。显示面板402与图1显示面板102类似,关于显示面板402的细节,可以参考显示面板102。

52.ddic 404包括输入端430、电流adc(cadc)435、存储器件440、显示补偿逻辑450、dac 455以及输出端460。输入端430用于接收针对显示面板402的显示感测信号。输入端430可例如接收流过显示面板402的感测元件422的显示感测信号i

d

。在图示实施方式中,显示像素驱动元件410

‑

2断开连接,而且显示感测信号为电流信号,该电流信号表示流过显示元件408的电流。

53.cadc 435与输入端430连接,并用于将显示感测信号i

d

转换为待存入电阻式随机存取存储器的感测值。

54.存储器件440通过cadc 435与输入端430连接。存储器件440用于存储表示输入端430所接收显示感测信号的感测值。在图示实施方式中,存储器件440与cadc 435连接,以接收且存储cadc 435生成的感测值。存储器件440包括rram。rram 440可在数字模式、模拟模式或数模混合模式下操作。在图4所示实施方式中,rram 440以数字模式或数模混合模式编程,以存储cadc 435生成的数字感测值。

55.显示补偿逻辑450与rram 440连接,以接收感测值,并用于根据该感测值确定补偿值,以使得显示面板402能够调节显示控制信号(如data)。例如,显示补偿逻辑450可编程为内含补偿值查找表。显示补偿逻辑450可读取感测值,并根据查找表确定对应的补偿值。在一些实施方式中,显示补偿逻辑450可与rram 440集成在一起。

56.dac 455与显示补偿逻辑450连接,并用于将接收自显示补偿逻辑450的补偿值转换成显示补偿电压信号420。接收自显示补偿逻辑450的补偿值可例如为表示显示像素406补偿水平的数字值。dac 455将该数字值转换为模拟显示补偿电压信号420,该信号可由显示面板402内的数据源416用于生成针对显示像素406的数据信号。

57.输出端460通过dac 455与显示补偿逻辑450连接,以将显示补偿电压信号420发送给显示面板402。显示面板402内的数据源416接收显示补偿电压信号420以及显示数据输入418,以生成针对显示面板402内显示像素406的数据信号。

58.由于ddic 404可内嵌rram 440,因此ddic 404提供了一种高效快速的补偿方案。由于rram 440中每一存储单元可由一个晶体管构成,因此rram 440占据更小的芯片面积,从而节省ddic 404的制造成本。另外,rram 440为非易失性存储器,而且功耗低于sram等现有存储器。本文公开的技术所提供的ddic 404性能更高且成本更低。

59.图5所示为根据一种例示实施方式的另一显示装置500。显示装置500包括显示面板502和ddic 504。显示面板502包括具有多个像素的像素阵列。图5中示出了一个例示像素506。像素506包括显示元件508以及用于控制显示元件508的显示像素驱动元件510。显示像素驱动元件510包括两个薄膜晶体管510

‑

1和510

‑

2。像素506与数据线512连接,以接收数据信号/显示控制信号,并与扫描线514连接,以接收扫描信号(scan)。虽然图5中未示出,但显示面板502包括多条数据线512和多条扫描线514。显示面板502还包括数据源516,该数据源516根据显示数据输入(data)518以及ddic 504提供的补偿信号520提供数据信号。显示面板502还包括感测元件522。显示面板502与图1显示面板102类似,关于显示面板502的细节,可以参考显示面板102。

60.ddic 504包括输入端530、积分放大器532、第一放大器535、存储器件540、第二放大器550以及输出端560。输入端530用于接收针对显示面板502的显示感测信号。输入端530可例如从显示面板502的感测元件接收显示感测信号。积分放大器532与输入端530连接,并用于将接收自输入端530的显示感测信号转换成感测电压信号。感测元件522的输出端可例如向ddic 504的输入端530提供电流信号(显示感测信号)。该电流信号由积分放大器532转换为电压信号(感测电压信号)。在图示实施方式中,积分放大器532包括与放大器532

‑

2并联的电容器532

‑

1。

61.第一放大器535与积分放大器532连接,且用于通过放大感测电压信号而生成待存入存储器件540的模拟感测信号。

62.存储器件540与第一放大器535连接。存储器件540用于存储模拟感测信号。存储器件540包括rram。在一些实施方式中,第一电压放大器535用于根据电阻式随机存取存储器540的电阻状态放大感测电压信号,从而生成模拟感测信号。积分放大器532生成的感测电压信号可例如为约1~3伏,电阻式随机存取存储器540的电阻状态可处于10kω~200kω范围。第一电压放大器535可将感测电压信号放大至3~5伏,以令其作为模拟感测信号。在一些实施方式中,取决于电阻式随机存取存储器540的电阻状态,第一电压放大器535可通过

增大或减小感测电压信号而生成待存入rram 540的模拟感测信号。

63.rram 540可在数字模式、模拟模式或数模混合模式下操作。在图5所示实施方式中,rram 540以模拟模式或数模混合模式编程,以存储模拟感测信号。

64.第二放大器550与rram 540连接,以接收模拟感测信号,并用于通过放大模拟感测信号而生成显示补偿电压信号520,该显示补偿电压信号可由显示面板502内的数据源516用于生成针对显示像素506的数据信号。取决于补偿方案,第二放大器550可通过增大或减小模拟感测信号的幅度而生成显示补偿电压信号520。

65.输出端560与第二放大器550连接,以将显示补偿电压信号520发送至显示面板502。显示面板502内的数据源516接收显示补偿电压信号520以及显示数据输入518,以生成针对显示面板502内显示像素506的数据信号。

66.由于ddic 504可内嵌rram 540,因此ddic 504提供了一种高效快速的补偿方案。由于ddic 504结构中不包含adc和dac,因此可降低ddic 504的成本。此外,由于rram 540内的每一存储单元可由少于现有存储器件的晶体管组成,因此rram 540占据更小的芯片面积,从而节省ddic 504的制造成本。另外,rram 540为非易失性存储器,而且功耗低于sram等现有存储器。本文公开的技术所提供的ddic 504性能更高且成本更低。

67.虽然本文中给出了具体的例示实施方式,但是对这些例示实施方式所做的修饰仍处于考虑范围之内。例如,某种实施方式中的个别部件可与其他实施方式中的部件相组合。此外,在符合本发明精神的情况下,还可省略某种实施方式中的个别部件。

68.虽然本文中描述了本发明之原理的示例和特征,但是在不脱离本发明实施方式的精神和范围的情况下,还可进行修饰和更改,并且存在其他的实现形式。此外,“包括”、“具有”、“包含”、“含有”四词以及其他类似形式旨在在含义上等同,而且为开放性词语,也就是说,这些词当中的任一词后所跟的一个或多个物项并不旨在为这一或这些物项的穷举式罗列,也不旨在为仅限于所列出的一个或多个物项。必须注意的是,在本文和下附权利要求书中,除非上下文另外明确指出,否则未指明数目之物不但包含单数之意,还涵盖复数之意。

69.本文所给出的实施方式的描述详细程度足以令本领域技术人员能够实践所公开的技术方案。除此之外,还可使用其他实施方式,或者从中导出其他实施方式,因此在不脱离本发明范围的情况下,还可在结构上和逻辑上做出替代和变化。因此,该“具体实施方式”部分不应理解为具有限制性,而且各种实施方式的范围仅由下附权利要求以及这些权利要求所有等效物限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。