技术特征:

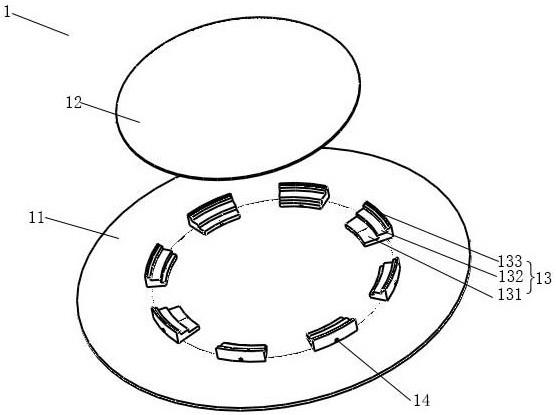

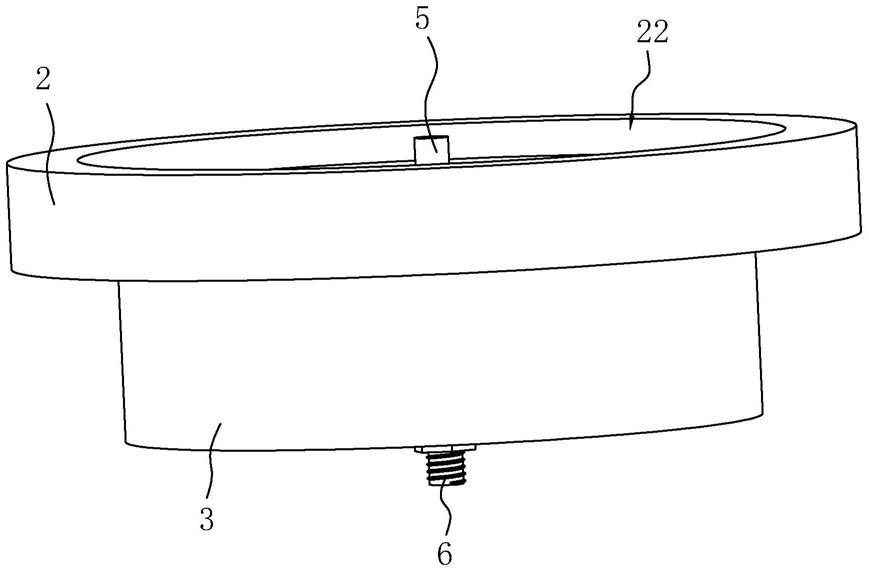

1.一种晶圆测试结构,其特征在于,包括:多个待测电阻、第一测试垫和多个第二测试垫;其中,多个所述待测电阻层叠设置,且相邻的两个所述待测电阻之间设置有绝缘层;多个所述待测电阻的第一端分别与所述第一测试垫电连接,多个所述待测电阻与多个所述第二测试垫一一对应,且每个所述待测电阻的第二端电连接相对应的一个所述第二测试垫。2.根据权利要求1所述的晶圆测试结构,其特征在于,所述第一测试垫和多个所述第二测试垫,与多个所述待测电阻中位于顶层的所述待测电阻同层。3.根据权利要求1所述的晶圆测试结构,其特征在于,所述第一测试垫和所述第二测试垫均为铜焊垫。4.根据权利要求1所述的晶圆测试结构,其特征在于,所述绝缘层为氧化硅层。5.根据权利要求1所述的晶圆测试结构,其特征在于,所述待测电阻包括有源区、栅极、电容器和金属层中的一种或者多种。6.根据权利要求5所述的晶圆测试结构,其特征在于,所述有源区设置在阱内,所述阱设置在基底内,所述有源区周向设置有浅沟槽隔离。7.根据权利要求1

‑

6任一项所述的晶圆测试结构,其特征在于,所述第一测试垫连接测试机台的电压输出端,多个所述第二测试垫连接所述测试机台的接地端;所述测试机台测量所述第二测试垫上的电流值,并根据所述电压输出端的电压值以及所述电流值,计算与所测的所述第二测试垫对应的所述待测电阻的电阻值。8.根据权利要求1

‑

6任一项所述的晶圆测试结构,其特征在于,所述晶圆测试结构还包括第一导线,每个绝缘层内设置有一条所述第一导线,所述第一导线贯穿相对应的所述绝缘层,且电连接与所述第一导线邻接的两个所述待测电阻的第一端。9.根据权利要求8所述的晶圆测试结构,其特征在于,所述第一导线为硅通孔或者接触孔。10.根据权利要求9所述的晶圆测试结构,其特征在于,所述第一导线位于相邻的两层所述待测电阻的重合区域内。11.根据权利要求8所述的晶圆测试结构,其特征在于,所述第一测试垫连接测试机台的电流输出端,待测的所述第一导线远离所述第一测试垫的一侧的任一所述第二测试垫连接所述测试机台的接地端;所述测试机台测量与待测的所述第一导线相邻接的两个所述待测电阻对应的所述第二测试垫上的电压值,并根据所述电流输出端的电流值和测量的所述电压值之差,计算待测的所述第一导线的电阻值。12.根据权利要求7所述的晶圆测试结构,其特征在于,所述晶圆测试结构还包括第二导线和第三导线;所述第二导线电连接顶层的所述待测电阻和所述第一测试垫,所述第三导线设置为多条,每条所述第三导线分别电连接各所述待测电阻的第二端和相对应的所述第二测试垫。13.一种晶圆测试结构的制作方法,其特征在于,包括:步骤a:提供基底,所述基底内设置有有源区,所述有源区为一个待测电阻;步骤b:利用化学气相沉积工艺在所述待测电阻上形成绝缘层;步骤c:利用物理气相沉积工艺在所述绝缘层上形成金属层,所述金属层为一个所述待

测电阻;重复步骤b和步骤c,直至形成所需个数的所述待测电阻;形成与各所述待测电阻的第一端电连接的第一测试垫,并形成与各所述待测电阻的第二端一一对应且电连接的第二测试垫。14.根据权利要求13所述的晶圆测试结构的测试方法,其特征在于,还包括:利用化学气相沉积工艺在所述待测电阻上形成绝缘层后,利用化学机械研磨对所述绝缘层进行平坦化处理;和/或,利用物理气相沉积工艺在所述绝缘层上形成金属层后,利用化学机械研磨对所述金属层进行平坦化处理。15.根据权利要求13所述的晶圆测试结构的制作方法,其特征在于,利用化学气相沉积工艺在所述待测电阻上形成绝缘层之后,还包括:刻蚀所述绝缘层形成孔状结构,所述孔状结构暴露所述待测电阻的第一端;在所述孔状结构内沉积导电材料,所述导电材料填充满所述孔状结构,以形成第一导线。16.一种晶圆,其特征在于,包括晶粒和位于所述晶粒外的切割道,所述晶粒内设置有集成电路,所述切割道内设置有晶圆测试结构;所述集成电路包括多个待测器件,所述晶圆测试结构包括多个待测电阻、第一测试垫和多个第二测试垫,多个所述待测电阻与多个所述待测器件一一对应且关键尺寸相同;多个所述待测电阻层叠设置,且相邻的两个所述待测电阻之间设置有绝缘层,多个所述待测电阻的第一端电连接所述第一测试垫,多个所述待测电阻与多个所述第二测试垫一一对应,且每个所述待测电阻的第二端电连接相对应的一个所述第二测试垫。

技术总结

本申请提供一种晶圆测试结构及其制作方法、晶圆,涉及半导体技术领域,用于解决晶圆测试结构所占用空间较大的技术问题,该晶圆测试结构包括:多个待测电阻、第一测试垫和多个第二测试垫;其中,多个待测电阻层叠设置,且相邻的两个待测电阻之间设置有绝缘层;多个待测电阻的第一端分别与第一测试垫电连接,多个待测电阻与多个第二测试垫一一对应,且每个待测电阻的第二端电连接相对应的一个第二测试垫。通过将各待测电阻的一端共接,将各待测电阻的另一端分别引出并连接第二测试垫,使得各待测电阻共用一个第一测试垫,在保证各待测电阻可以正常测量的基础上,减少了第一测试垫和第二测试垫的总数量,从而减少了测试结构所占用的空间。间。间。

技术研发人员:汪海 许杞安

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:2021.07.09

技术公布日:2021/10/19

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。