1.本技术涉及半导体技术领域,尤其涉及一种晶圆测试结构及其制作方法、晶圆。

背景技术:

2.晶圆(wafer)包括多个晶粒和隔离各晶粒的切割道(scribe line),在晶粒上形成集成电路后,切割封装之前,需要对晶粒进行挑选测试,通过挑选测试将晶粒分类,将有缺陷或者不具备正常工作能力的晶粒标注上记号,并在切割晶圆时将这些晶粒过过滤出来丢弃,从而避免不良的晶粒进入封装及后续制程。

3.挑选测试包括晶圆可接受测试(wafer acceptance test,简称wat),晶圆可接受测试通常包含多项破坏测试,一般在切割道上制作测试结构(test key),通过对这些测试结构的检测,从而推断出晶粒中集成电路的元件的工作性能。晶圆可接受测试的重要测试参数包括测试结构中的待测电阻的电阻值。

4.然而,随着晶粒中集成电路的复杂化,待测电阻数量的增加,导致测试结构所占用的空间较大。

技术实现要素:

5.鉴于上述问题,本技术实施例提供一种晶圆测试结构及其制作方法、晶圆,用于减少测试结构所占用的空间。

6.为了实现上述目的,本技术实施例提供如下技术方案:

7.第一方面,本技术实施例提供一种晶圆测试结构,其包括:多个待测电阻、第一测试垫和多个第二测试垫;其中,多个所述待测电阻层叠设置,且相邻的两个所述待测电阻之间设置有绝缘层;多个所述待测电阻的第一端分别与所述第一测试垫电连接,多个所述待测电阻与多个所述第二测试垫一一对应,且每个所述待测电阻的第二端电连接相对应的一个所述第二测试垫。

8.本技术实施例提供的晶圆测试结构具有如下优点:

9.本技术实施例提供的晶圆测试结构中,多个待测电阻层叠设置,相邻的两个待测电阻之间设置绝缘层,以使各待测电子之间电气隔离;多个待测电阻的第一端均电连接于第一测试垫上,多个待测电阻的第二端分别电连接一个第二测试垫。通过将各待测电阻的一端共接,将各待测电阻的另一端分别引出并各连接第二测试垫,使得各待测电阻共用一个第一测试垫,在保证各待测电阻的电阻值可以正常测量的基础上,减少了第一测试垫和第二测试垫的总数量,从而减少了晶圆测试结构所占用的空间,提高了切割道的空间利用率。同时,本技术实施例中将多个待测电阻层叠设置在一个测试结构内,避免了将独立的待测电阻与测试垫进行连接,实现了通过一个层叠的测试结构对多个待测电阻进行测试,进而缩减了待测电阻所占据的面积。

10.如上所述的晶圆测试结构,所述第一测试垫和多个所述第二测试垫,与多个所述待测电阻中位于顶层的所述待测电阻同层。

11.如上所述的晶圆测试结构,所述第一测试垫和所述第二测试垫均为铜焊垫。

12.如上所述的晶圆测试结构,所述绝缘层为氧化硅层。

13.如上所述的晶圆测试结构,所述待测电阻包括有源区、栅极、电容器和金属层中的一种或者多种。

14.如上所述的晶圆测试结构,所述有源区设置在阱内,所述阱设置在基底内,所述有源区周向设置有浅沟槽隔离。

15.如上所述的晶圆测试结构,所述第一测试垫连接测试机台的电压输出端,多个所述第二测试垫连接所述测试机台的接地端;所述测试机台测量所述第二测试垫上的电流值,并根据所述电压输出端的电压值以及所述电流值,计算与所测的所述第二测试垫对应的所述待测电阻的电阻值。

16.如上所述的晶圆测试结构,所述晶圆测试结构还包括第一导线,每个绝缘层内设置有一条所述第一导线,所述第一导线贯穿相对应的所述绝缘层,且电连接与所述第一导线邻接的两个所述待测电阻的第一端。

17.如上所述的晶圆测试结构,所述第一导线为硅通孔或者接触孔。

18.如上所述的晶圆测试结构,所述第一导线位于相邻的两层所述待测电阻的重合区域内。

19.如上所述的晶圆测试结构,所述第一测试垫连接所述待测机台的电流输出端,待测的所述第一导线远离所述第一测试垫的一侧的任一所述第二测试垫连接所述测试机台的接地端;所述测试机台测量与待测的所述第一导线相邻接的两个所述待测电阻对应的所述第二测试垫上的电压值,并根据所述电流输出端的电流值和测量的所述电压值之差,计算待测的所述第一导线的电阻值。

20.如上所述的晶圆测试结构,所述晶圆测试结构还包括第二导线和第三导线;所述第二导线电连接顶层的所述待测电阻和所述第一测试垫,所述第三导线设置为多条,每条所述第三导线分别电连接各所述待测电阻的第二端和相对应的所述第二测试垫。

21.第二方面,本技术实施例提供一种晶圆测试结构的制作方法,其包括:

22.步骤a:提供基底,所述基底内设置有有源区,所述有源区为一个待测电阻;

23.步骤b:利用化学气相沉积工艺在所述待测电阻上形成绝缘层;

24.步骤c:利用物理气相沉积工艺在所述绝缘层上形成金属层,所述金属层为一个所述待测电阻;

25.重复步骤b和步骤c,直至形成所需个数的所述待测电阻;

26.形成与各所述待测电阻的第一端电连接的第一测试垫,并形成与各所述待测电阻的第二端一一对应且电连接的第二测试垫。

27.本技术实施例提供的晶圆测试结构具有如下优点:

28.本技术实施例中的晶圆测试结构的制作方法中,将多个待测电阻层叠设置在一个测试结构内,实现了通过一个层叠的测试结构对多个待测电阻进行测试,进而缩减了待测电阻所占据的面积。同时,各待测电阻共用一个第一测试垫,在保证各待测电阻的电阻值可以正常测量的基础上,减少了晶圆测试结构所占用的空间,提高了切割道的空间利用率。

29.如上所述的晶圆测试结构的制作方法,还包括:利用化学气相沉积工艺在所述待测电阻上形成绝缘层后,利用化学机械研磨对所述绝缘层进行平坦化处理;和/或,利用物

理气相沉积工艺在所述绝缘层上形成金属层后,利用化学机械研磨对所述金属层进行平坦化处理。

30.如上所述的晶圆测试结构的制作方法,利用化学气相沉积工艺在所述待测电阻上形成绝缘层之后,还包括:刻蚀所述绝缘层形成孔状结构,所述孔状结构暴露所述待测电阻的第一端;在所述孔状结构内沉积导电材料,所述导电材料填充满所述孔状结构,以形成第一导线。

31.第三方面,本技术实施例提供一种晶圆,其包括晶粒和位于所述晶粒外的切割道,所述晶粒内设置有集成电路,所述切割道内设置有晶圆测试结构;所述集成电路包括多个待测器件,所述晶圆测试结构包括多个待测电阻、第一测试垫和多个第二测试垫,多个所述待测电阻与多个所述待测器件一一对应且关键尺寸相同;多个所述待测电阻层叠设置,且相邻的两个所述待测电阻之间设置有绝缘层,多个所述待测电阻的第一端电连接所述第一测试垫,多个所述待测电阻与多个所述第二测试垫一一对应,且每个所述待测电阻的第二端电连接相对应的一个所述第二测试垫。

32.本技术实施例提供的晶圆具有如下优点:

33.本技术实施例提供的晶圆中,通过晶圆测试结构中的各待测电阻获得集成电路中的各待测器件的电学参数,晶圆测试结构中的各待测电阻的一端共接,将各待测电阻的另一端分别引出连接第二测试垫,使得各待测电阻共用一个第一测试垫,在保证各待测电阻的电阻值可以正常测量的基础上,减少了第一测试垫和第二测试垫的总数量,从而减少了晶圆测试结构所占用的空间,提高了切割道的空间利用率。

附图说明

34.为了更清楚地说明本技术实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

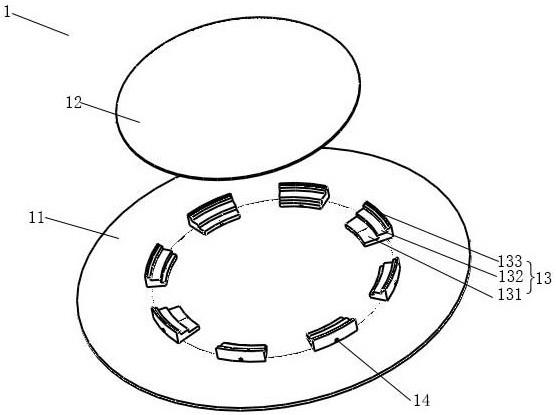

35.图1为相关技术中的晶圆测试结构的结构示意图;

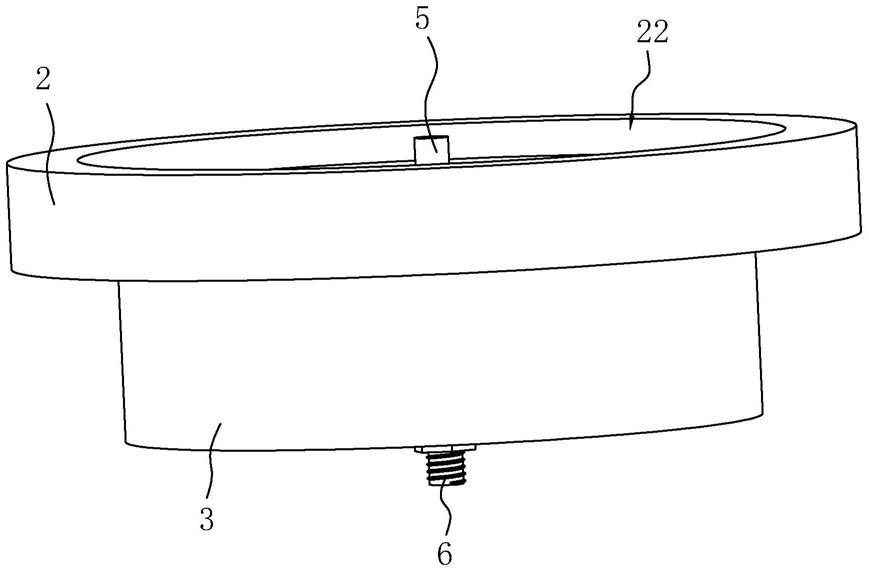

36.图2为本技术实施例中的晶圆的结构示意图;

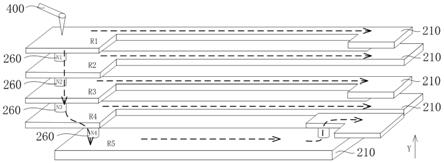

37.图3为本技术实施例中的晶圆测试结构的结构示意图;

38.图4为本技术实施例中的晶圆测试结构的电流示意图;

39.图5为本技术实施例中的第一测试垫和第二测试垫的分布示意图。

40.附图标记说明:

41.100

‑

晶圆;110

‑

晶粒;

42.120

‑

切割道;200

‑

晶圆测试结构;

43.210

‑

待测电阻;220

‑

绝缘层;

44.230

‑

第一测试垫;240

‑

第二测试垫;

45.250

‑

基底;251

‑

浅沟槽隔离;

46.252

‑

阱;260

‑

第一导线;

47.270

‑

第二导线;280

‑

第三导线;

48.300

‑

测试垫;400

‑

探针。

具体实施方式

49.参照图1,相关技术中,晶圆测试结构200中的每个待测电阻210的两端分别设置有一个测试垫300,通过测试待测电阻210两端的两个测试垫300的电压值之差,以及待测电阻210两端的两个测试垫300中任一测试垫300的电流值,计算该待测电阻210的电阻值。上述晶圆测试结构200所需的测试垫300较多,使得晶圆测试结构200所占用的空间较大,切割道120的空间利用率较低。

50.针对上述技术问题,本技术实施例提供一种晶圆测试结构及晶圆,晶圆测试结构中的各待测电阻的一端均电连接第一测试垫,各待测电阻的另一端分别电连接一个第二测试垫,通过各待测电阻的一端共用一个第一测试垫,从而减少了第一测试垫和第二测试垫的总数量,进而减少了晶圆测试结构所占用的空间,提高了切割道的空间利用率。

51.为了使本技术实施例的上述目的、特征和优点能够更加明显易懂,下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本技术的一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有作出创造性劳动的前提下所获得的所有其它实施例,均属于本技术保护的范围。

52.参照图2,晶圆100包括晶粒110和切割道120,切割道120位于晶粒110外。示例性的,晶圆100包括多个晶粒110,切割道120位于各晶粒110之间,切割道120与各晶粒110相邻接。

53.晶粒110内设置有集成电路(integrated circuit,简称ic),集成电路通过沉积、显影、刻蚀、掺杂、热处理等工艺形成。集成电路包括多个元件(电阻器、电容器、晶体管、二极管等)、叠层以及互连线等,集成电路中的部分结构为待测器件,待测器件通常为多个,通过检测待测器件的电性参数(例如电阻值),以监控集成电路的工艺情况。

54.切割道120内设置有晶圆测试结构200,晶圆测试结构200包括多个待测电阻210,晶圆测试结构200中的多个待测电阻210与集成电路中的多个待测器件一一对应,且各待测电阻210与其相对应的待测器件的关键尺寸(critical dimension,简称cd)相同,以使待测电阻210可以表征相对应的待测器件,通过测试待测电阻210的电性参数可以获得待测器件的电性参数。切割道120内的晶圆测试结构200可以与晶粒110内的集成电路同时形成。

55.参照图3,晶圆测试结构200包括多个待测电阻210,多个待测电阻210依次层叠设置,相邻的两个待测电阻210之间设置有绝缘层220,以将相邻两层的待测电阻210电气隔离,避免各待测电阻210之间电连接。示例性的,绝缘层220可以氧化硅层(例如sio2层)或者氮化硅层(例如si3n4层)。

56.待测电阻210可以包括有源区、栅极、电容器或者金属层(例如铜互连金属层)中的一种或者多种。示例性的,晶圆测试结构200中的一个待测电阻210为有源区,即测量有源区的电阻值。如图3所示,有源区设置在阱(well)252中,阱252设置在基底250中。

57.其中,基底250可以为p型基底,即基底250中的空穴浓度大于自由电子浓度,基底250主要以空穴作为载流子导电。通过在基底250内进行离子注入形成阱252,阱252具有一定的离子浓度。如图3所示,有源区位于阱252内,且有源区周向设置有浅沟槽隔离(shallow trench isolation,简称sti)251。制作浅沟槽隔离251时,通常以氮化硅为掩膜,对基底250进行图形化处理,以在基底250上形成凹槽,再在凹槽内沉积氧化物,以将有源区隔离。

58.参照图4和图5,多个待测电阻210的第一端分别与第一测试垫230电连接,多个待测电阻210中的每个待测电阻210的第二端电连接一个第二测试垫240。可以理解的是,第一测试垫230的数量为一个,第二测试垫240的数量与待测电阻210的数量相同。

59.如此设置,如图4和图5所示,通过将各待测电阻210的第一端共接,并使其共用一个第一测试垫230,减少了第一测试垫230的数量,从而减少了第一测试垫230和第二测试垫240的总数量,进而减少了晶圆测试结构200所占用的空间。

60.第一测试垫230和各第二测试垫240的材质均为导电材料,以使晶圆测试结构200具有导电性。示例性的,第一测试垫230和各第二测试垫240的材质均为金属,例如第一测试垫230和各第二测试垫240为铜(cu)焊垫或者铝(al)焊垫。

61.在一种可能的示例中,如图4所示,每个绝缘层内设有一条第一导线260,第一导线260贯穿其所在的绝缘层,且第一导线260的两端分别电连接与其所在的绝缘层相邻接的两个待测电阻210的第一端,即第一导线260将各待测电阻210的第一端之间电连接。

62.其中,第一导线260位于相邻的两层待测电阻210的重合区域内,以避免第一导线260延伸至待测电阻210的投影区域外,减少晶圆测试结构200所占空间。各第一导线260之间可以对齐,各第一导线260可以为硅通孔(through silicon via,简称tsv)或接触孔(contact,简称ct),其材质为铜或钨(w)。

63.例如,如图3和图4所示,位于最上层的待测电阻210与位于次上层的待测电阻210之间的绝缘层220中设置有一个第一导线260。该第一导线260的上端与最上层的待测电阻210的第一端相接触,该第一导线260的下端与次上层的待测电阻210的第一端相接触,该第一导线260与最上层的待测电阻210、次上层的待测电阻210均电连接。该第一导线260位于最上层的待测电阻210与次上层的待测电阻210的重合区域内,即第一导线260在竖直方向(图4所示y方向)的正投影位于最上层的待测电阻210与次上层的待测电阻210的正投影的范围内。

64.继续参照图4和图5,当晶圆测试结构200连接到测试机台上时,通过测试机台的探针400通过第一测试垫230(图4中未画出)提供电流或者电压。晶圆测试结构200中的电流方向如图4所示,电流经第一导线260流入顶层以下的各待测电阻210中。

65.需要说明的是,如图5所示,晶圆测试结构200还包括第二导线270和第三导线280,其中,第二导线270电连接顶层的待测电阻210和第一测试垫230,从而将各待测电阻210的第一端与第一测试垫230电连接。第三导线280设置为多条,多条第三导线280与多个待测电阻210一一对应,每条第三导线280连接一个待测电阻210与该待测电阻210相对应的第二测试垫240。可以理解的是,第三导线280、待测电阻210与第二测试垫240之间一一对应。

66.参照图5,第一测试垫230和多个第二测试垫240位于同一层,且与多个待测电阻210中位于顶层的待测电阻210同层。如图5所示,第一测试垫230、第二测试垫240与最上层的待测电阻210位于同一层,即第一测试垫230和第二测试垫240位于最上层的待测电阻210的同一层,以使第一测试垫230、第二测试垫240显露,便于测量,且提高测量准确性。

67.在一种可能的示例中,晶圆测试结构200包括五个待测电阻210以及四层绝缘层220。为方便描述,如图4所示,这五个待测电阻210由上至下分别定义为第一电阻r1,第二电阻r2,第三电阻r3,第四电阻r4和第五电阻r5,本技术实施例及以下各实施例均以上述五个电阻为例进行阐述。当待测电阻210数量不为五个时的晶圆测试结构200的具体结构及测试

原理,参照待测电阻210数量为五个时的晶圆测试结构200的具体结构及测试原理。

68.上述晶圆测试结构200包括一个第一测试垫230和五个第二测试垫240。如图4和图5所示,与第一电阻r1电连接的第二测试垫240为pad1,与第二电阻r2电连接的第二测试垫240为pad2,与第三电阻r3电连接的第二测试垫240为pad3,与第四电阻r4电连接的第二测试垫240为pad4,与第五电阻r5电连接的第二测试垫240为pad5,第一测试垫230为pad6。

69.pad6与第一电阻r1之间连接有第二导线270。如图4和图5所示,第一电阻r1与第二电阻r2之间、第二电阻r2与第三电阻r3之间、第三电阻r3与第四电阻r4之间、第四电阻r4与第五电阻r5之间分别连接有一个第一导线260。具体的,第一电阻r1与第二电阻r2之间的第一导线260为n1,第二电阻r2与第三电阻r3之间的第一导线260为n2,第三电阻r3与第四电阻r4之间的第一导线260为n3,第四电阻r4与第五电阻r5之间的第一导线260为n4。

70.如图4和图5所示,第一电阻r1与pad1之间、第二电阻r2与pad2之间、第三电阻r3与pad3之间、第四电阻r4与pad4之间、第五电阻r5与pad5之间分别连接有一个第三导线280。

71.测量时,第一测试垫230连接测试机台的电压输出端,每个第二测试垫240连接测试机台的接地端。测试机台测量第二测试垫240上的电流值,并根据电压输出端的电压值以及电流值,计算所测量的第二测试垫240相对应的待测电阻210的电阻值。

72.测试机台包括多个探针400,探针400分别扎在第一测试垫230和任一待测电阻210相对应的第二测试垫240上,测试机台通过探针400向第一测试垫230和第二测试垫240提供电压,并测量电流。

73.示例性的,测试机台的多个探针400分别扎在第一测试垫230和所有的第二测试垫240上,第一测试垫230上的电压值(电压输出端的电压值)为vm,第二测试垫240接地,即第二测试垫240上的电压值为0。测量pad1、pad2、pad3、pad4、pad5上的电流分别为i1、i2、i3、i4、i5。相应的,第一电阻r1、第二电阻r2、第三电阻r3、第四电阻r4、第五电阻r5的电阻值分别为:r1=vm/i1,r2=vm/i2;r3=vm/i3;r4=vm/i4;r5=vm/i5。

74.本技术实施例中的晶圆测试结构200还可以获得第一导线260的电阻值。具体的,第一测试垫230连接测试机台的电流输出端,待测的第一导线260远离第一测试垫230的一侧的任一第二测试垫240连接测试机台的接地端,例如,多个待测电阻210中底层的待测电阻210所对应的第二测试垫240连接测试机台的接地端,以使得电流输出端的电流流经待测的第一导线260。

75.测试机台测量与待测的第一导线260相邻接的两个待测电阻210对应的第二测试垫240上的电压值,并根据电流输出端的电流值和测量的电压值之差,计算待测的第一导线260的电阻值。

76.示例性的,n1的电阻值可以通过下述过程获得:第一测试垫230连接测试机台的电流输出端,电流输出端的电流值为ih,pad3接地。测试机台测量n1相邻接的第一电阻r1与第二电阻r2分别对应的pad1和pad2上的电压值,例如,pad1的电压值为vh,pad2的电压值为v1,则n1的电阻值为:rn1=(vh

‑

v1)/ih。

77.本技术实施例提供的晶圆测试结构200中,多个待测电阻210层叠设置,相邻的两个待测电阻210之间设置绝缘层220,以使各待测电子之间电气隔离;多个待测电阻210的第一端均电连接于第一测试垫230上,多个待测电阻210的第二端分别电连接一个第二测试垫240。通过将各待测电阻210的一端共接,将各待测电阻210的另一端分别引出并各连接第二

测试垫240,使得各待测电阻210共用一个第一测试垫230,在保证各待测电阻210的电阻值可以正常测量的基础上,减少了第一测试垫230和第二测试垫240的总数量,从而减少了晶圆测试结构200所占用的空间,提高了切割道120的空间利用率。同时,多个待测电阻210层叠设置在一个测试结构200内,避免了将独立的待测电阻210与测试垫进行连接,实现了通过一个层叠的测试结构200对多个待测电阻210进行测试,进而缩减了待测电阻210所占据的面积。

78.本技术实施例还提供一种晶圆测试结构的制作方法,参照图1至图5,该晶圆测试结构的制作方法包括:

79.步骤a:提供基底,基底内设置有有源区,有源区为一个待测电阻。

80.本技术实施例中的晶圆测试结构200可以测量有源区的电阻值,有源区可以设置在阱252内,阱252设置在基底250。其中,基底250可以为p型基底250,通过在基底250内进行离子注入形成阱252。有源区位于阱252内,且有源区周向设置有浅沟槽隔离251。

81.步骤b:利用化学气相沉积工艺在待测电阻上形成绝缘层。

82.绝缘层220通过化学气相沉积(chemical vapor deposition,简称为cvd)工艺形成在基底250上。绝缘层220覆盖有源区,以将有源区电气隔离。绝缘层220的材质可以包括氧化硅或者氮化硅。

83.形成绝缘层220后可以对绝缘层220背离基底250的表面进行平坦化处理,以使形成在绝缘层220上的各膜层较为平整。示例性的,通过化学机械研磨(chemical mechanical polishing,简称为cmp)对绝缘层220的上表面平坦化处理。

84.在一些可能的示例中,绝缘层220内设置有第一导线260,第一导线260贯穿绝缘层220,用于电连接绝缘层220两侧的待测电阻210。第一导线260可以为硅通孔或者接触孔,其材质为铜或钨。

85.具体的,形成绝缘层220后,刻蚀绝缘层220形成孔状结构,孔状结构暴露待测电阻210的第一端,即孔状结构贯穿绝缘层220。待测电阻210在基底250上的正投影覆盖孔状结构在基底250上的正投影。形成孔状结构后,在孔状结构内沉积导电材料,导电材料填充满孔状结构,以形成第一导线260。

86.步骤c:利用物理气相沉积工艺在绝缘层上形成金属层,金属层为一个待测电阻。

87.金属层可以为铜互连层,金属层利用物理气相沉积(physical vapor deposition,简称为pvd)工艺形成在绝缘层220上,且金属层的第一端与绝缘层220内的第一导线260相接触,从而与第一导线260电连接。

88.形成金属层后,可以对金属层背离基底250的表面进行平坦化处理,以平整金属层的该表面。例如,通过化学机械研磨对金属层的上表面平坦化处理。

89.可以理解的是,晶圆测试结构200中的金属层和绝缘层220可以均进行平坦化处理,以使各金属层和各绝缘层220背离基底250的表面较为平整,也可以对金属层和绝缘层220中某层或者某几层进行平坦化处理,以保证较为关键的膜层的平整度。

90.重复步骤b和步骤c,直至形成所需个数的待测电阻210。即重复金属层和绝缘层220的形成步骤,直至形成所需个数的待测电阻210,待测电阻210与绝缘层220交替层叠设置。

91.再形成与各待测电阻210的第一端电连接的第一测试垫230,并形成与各待测电阻

210的第二端一一对应且电连接的第二测试垫240。第一测试垫230和各第二测试垫240的材质均为导电材料,例如第一测试垫230和各第二测试垫240为铜(cu)焊垫或者铝(al)焊垫。第一测试垫230和多个第二测试垫240位于同一层,且与多个待测电阻210中位于顶层的待测电阻210同层。如图5所示,第一测试垫230、第二测试垫240与最上层的待测电阻210位于同一层。

92.本技术实施例提供的晶圆测试结构200的制作方法中,多个待测电阻210层叠设置,相邻的两个待测电阻210之间设置绝缘层220,实现了通过一个层叠的测试结构200对多个待测电阻210进行测试,进而缩减了待测电阻210所占据的面积。同时,各待测电阻210共用一个第一测试垫230,在保证各待测电阻210的电阻值可以正常测量的基础上,减少了晶圆测试结构200所占用的空间,提高了切割道120的空间利用率。

93.本说明书中各实施例或实施方式采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分相互参见即可。

94.在本说明书的描述中,参考术“一个实施方式”、“一些实施方式”、“示意性实施方式”、“示例”、“具体示例”、或“一些示例”等的描述意指结合实施方式或示例描述的具体特征、结构、材料或者特点包含于本技术的至少一个实施方式或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施方式或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施方式或示例中以合适的方式结合。

95.最后应说明的是:以上各实施例仅用以说明本技术的技术方案,而非对其限制;尽管参照前述各实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。