一种用于5g rru的从时钟同步系统及方法

技术领域

1.本发明涉及5g移动通信技术领域,尤其涉及一种用于5g rru的从时钟同步系统及方法。

背景技术:

2.随着5g手机的推出及日益普及,5g应用的需求不断扩大,大数据、虚拟现实vr、无人驾驶、物联网等应用技术的大量使用,都促使5g应用正式走入大众视野,并逐渐进入千家万户。5g技术具有高速度、低延时、高吞吐量等优点,与之相适应,对于5g应用中的时钟同步(包括时钟频率同步与时钟相位同步)的精度要求也更高。传统的2g/3g/4g移动网络的时钟同步精度一般只达到微妙的数量级,对于满足一般应用可谓绰绰有余,但随着5g技术的应用推广,这样的精度就显得捉襟见肘了。对于5g应用来说,至少需要达到亚微秒的量级才能满足5g业务的正常开展以及人们的日常生活需求。

3.5g技术的运用,离不开5g网络的基站建设与合理布局。虽然从降低成本的角度考量,各大运营商在布局5g网络时,尽可能充分利用现有的3g/4g各站点基础设施,如共享基站机房、天线塔台等,但添加一些必需的5g相关设施也是必不可少的。一般情况下,一套完备的5g基站设施包括连接到核心业务网的基站处理单元bbu、若干射频拉远单元rru、天馈收发单元aau,以及配套的设施如中继设备rru hub、供电系统、光纤馈线设施、防雷设施等。当然,在这些设施中,还有一个不可或缺的关键设施——精确授时系统——来统一各个部件的工作使它们步调一致,协同工作。其中,授时系统是与业务处理紧密关联的,而与业务处理相关的设施主要是基站处理单元bbu、射频拉远单元rru以及中继设备rru、hub。

4.通常来说,实现精确授时系统最简单、最直接的方案是采用高精度的授时设备如gps、北斗bds,其精度可达亚微秒级,完全可以满足5g网络的业务需求,但是使用这些授时设备,一方面价格比较昂贵,如果在每个bbu、rru及rru hub设施中都使用,成本过高;另一方面,这些授时设备主要依靠卫星工作,其安装和选址比较困难,在接收不到卫星信号的地区无法正常工作。

5.为了降低成本,采用同步以太网synce及(或)ieee 1588协议规范成为实现时钟同步的替代解决方案。其中,同步以太网通过硬件编解码的方式来传输和恢复时钟信号,其精度可达毫秒到微秒级,为了达到更高的精度,通常还需要配合应用ieee 1588协议规范。ieee 1588协议规范由ieee 1588工作组所制定,该规范所定义的高精度时间同步协议(ptp,precision time protocol),由于其开放性,被广泛应用于测量和自动化系统中,该协议特别适合于以太网及分布式网络环境的应用。目前该协议规范已更新到v2版本,以满足分布式网络环境下的更高精度的时钟同步需求,其精度可达到亚微秒级甚至次纳秒级。

6.在5g基站系统中,通常基带处理单元bbu一端采用主时钟模式,而射频拉远单元rru一端则采用从时钟模式,通过光纤直接或间接(通过rru hub)与bbu相连。为了既控制成本,又满足一定的同步精度需求,本发明所要解决的问题,就是在既有的软硬件平台条件下,确定一种合适的ieee 1588v2实现方案,解决rru设备的从时钟同步问题。

7.当前的5g rru系统平台采用的是如附图2所示的系统架构,即通过fpga arm rf及前端的组织方式,实现4*4mimo无线射频功能,其各个部件或模块的基本功能如下:

8.·

fpga:实现rru的基带信号处理及业务分发功能;

9.·

arm:实现rf配置、系统监控及运维管理等功能;

10.·

rf及前端:具有4*4mimo通道,与fpga及外部的天线单元aau相连,实现将来自fpga的基带业务信号以及来自aau的rf终端用户业务信号进行信号转换处理与分发传递。

11.现有的5g rru系统平台中,fpga并非内嵌arm核的那种集成芯片,故而需要外接arm处理器以实现特定的配置、管理等功能。

12.为了实现ieee 1588时钟同步,并尽可能地提高同步精度,fpga需要具备时间戳管理亦即“打戳”的能力,另外还需要具备识别和处理ptpv2报文的能力。由于来自bbu的ptpv2报文在通过光口/电口到达rru时,fpga是最先处理该报文的部件——报文数据是经过编码的,fpga需要先进行解码,然后才能从中识别出ptpv2报文并进行“打戳”处理——因此,“打戳”这个工作非交给fpga莫属,否则将达不到所需要的时钟同步精度。至于ptpv2报文的处理,是一个比较复杂的工作,如果完全交给fpga来做,显然不现实——即使是对于具有内嵌arm核的fpga芯片,这部分工作也是交给芯片内的arm核来完成的。因此,对于作为从时钟的5g rru来说,fpga只需实现识别ptpv2报文的功能就可以了,相关的ptpv2报文处理工作则交给外部的arm处理器来完成。fpga需要做的一个额外工作就是将来自arm处理器的ptpv2报文在编码并通过光口/电口发给bbu之前进行“打戳”处理。

13.为了实现对于ptp报文的处理,arm处理器通常采用开源的协议栈以及开源的上层应用来完成,但这里有一个难点,那就是开源的协议栈是基于linux内核的(至少v3.0以上的内核才支持),而linuix内核的ptp实现机理又是基于高精度的ptp时钟源的,且只有更新、更高版本的内核才支持完全的ptp功能及其扩展特性。当前系统平台的arm处理器是arm9的,linux内核版本则基于v2.6,如果要实现ptp功能,在不考虑更换arm处理器的前提下,要么升级内核到高版本,要么从高版本中移植ptp功能到当前内核版本,尽管这两者都具有难度。但却是一个必须要跨过的槛。

技术实现要素:

14.本发明提供了一种用于5g rru的从时钟同步系统及方法,基于已有的平台,实现了rru设备的从时钟同步,同时具有成本低的优点。

15.为了实现本发明的目的,所采用的技术方案是:一种用于5g rru的从时钟同步系统,其特征在于:包括fpga、arm和hcu,

16.fpga,用于识别bbu发送来的ptpv2报文并进行转发,同时给ptpv2报文加上时间戳;

17.所述arm,用于处理fpga发送来的ptpv2报文,从中提取接收时间戳,计算出链路延迟及时间偏移,并控制hcu;

18.所述hcu,接收arm驱动信号时,实现ptp硬件时钟,同时输出1pps及高精度tod信息供fpga同步,实现与bbu的同步。

19.作为本发明的优化方案,fpga包括pmacu单元和tsu单元,pmacu单元实现ptpv2报文的转发,在tsu单元中给ptpv2报文加上时间戳。

20.作为本发明的优化方案,fpga和arm之间通过rmmi接口实现ptpv2报文传输,fpga包括mii转rmmi模块。

21.为了实现本发明的目的,所采用的技术方案是,一种用于5g rru的从时钟同步装置进行同步的方法,包括如下步骤:

22.1)bbu通过向rru发送sync报文,通知rru开始进行时间同步;

23.2)rru中的fpga解码后识别出sync报文,tsu单元给sync报文加上时间戳,然后交给pmacu单元发给arm;

24.3)arm接收到sync报文,提交给上层的开源ptp协议栈应用程序,开源ptp协议栈应用程序处理sync报文并将对应的时间戳信息作为sync报文的接收戳信息t2;

25.4)开源ptp协议栈应用程序若检测sync报文为一步同步报文,则从sync报文中提取bbu的发送时间戳信息t1;

26.5)开源ptp协议栈应用程序生成delay req报文,arm将delay req报文发送给pmacu单元;

27.6)pmacu单元将接收到的delay req报文,由tsu单元加上时间戳,然后发送给bbu,同时arm从fpga获取delay req报文的时间戳信息t3;

28.7)bbu收到delay req报文后,生成delay resp报文发送给rru;

29.8)rru收到delay resp报文,从报文中提取bbu的接收时间戳信息t4,经过将上述时间戳信息参与计算后,arm控制hcu进行对时操作,hcu输出1pps及高精度tod信息供fpga同步,实现与bbu的同步。

30.作为本发明的优化方案,在步骤4)处,开源ptp协议栈应用程序若检测sync报文为二步同步报文,执行如下步骤:

31.41)bbu会发出follow up报文,fpga接收follow up报文,由tsu单元加上时间戳,并发送给arm;

32.42)arm接收到follow up报文,将其提交给开源ptp协议栈应用程序,开源ptp协议栈应用程序忽略follow up报文的打戳信息,从sync报文中提取bbu的发送时间戳信息t1,然后跳转到上述步骤5)。

33.作为本发明的优化方案,fpga给收到的所有报文加上时间戳信息,fpga同时判断是不是ptpv2报文,将是ptpv2报文标记好时间信息后送给pmacu单元;fpga将非ptpv2报文丢弃时间信息后发送给pmacu单元。

34.本发明具有积极的效果:1)本发明基于现有的平台,解决rru的从时钟同步问题,可以有效的节约成本;

35.2)本发明通过时钟同步芯片,大大降低了研发周期和成本;

36.3)本发明易于扩展,具有普适性。

附图说明

37.下面结合附图和具体实施方式对本发明作进一步详细的说明。

38.图1是本发明用于5g rru的从时钟同步系统的系统架构图;

39.图2是现有5g rru的系统架构图;

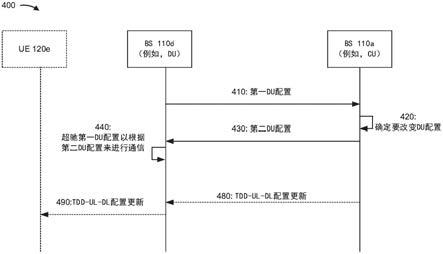

40.图3是用于sync报文为一步同步报文的处理流程图;

41.图4是用于sync报文为二步同步报文的处理流程图;

42.图5是fpga的pmacu单元逻辑图;

43.图6是fpga的tsu单元逻辑图;

44.图7是数据字段的数据区结构图;

45.图8是udp数据为1588数据的长度字段值。

具体实施方式

46.下面结合附图对本发明的实现做进一步详细的描述:

47.如图1所示,一种用于5g rru的从时钟同步系统,包括fpga、arm和hcu,

48.fpga,用于识别bbu发送来的ptpv2报文并进行转发,同时给ptpv2报文加上时间戳;

49.arm,用于处理fpga发送来的ptpv2报文,从中提取接收时间戳,计算出链路延迟及时间偏移,并控制hcu;

50.hcu,接收arm驱动信号时,实现ptp硬件时钟,同时输出1pps及高精度tod信息供fpga同步,实现与bbu的同步。其中hcu(hardware clock unit)为第三方的时钟同步芯片,加入该芯片后,5g rru系统除了要实现原先所需要实现的基本功能外,各个模块新增的功能如下:

51.fpga:新增两个功能单元pmacu(peer mac unit)单元和时间戳处理tsu(time stamping unit)单元。在pmacu单元中通过mac接口(mii/rmii)实现ptpv2报文的转发;在tsu中实现ptpv2报文的“打戳”功能;

52.·

arm:linux内核中实现ptpv2报文的处理、加入开源ptp协议栈及其上层应用、hcu的驱动等;

53.·

hcu:实现ptp硬件时钟(ptp hardware clock)的相关功能、输出1pps及高精度tod信息供fpga及其它需要精确同步的部件使用。

54.如图3所示,一种用于5g rru的从时钟同步装置进行同步的方法,包括如下步骤:

55.1)bbu通过向rru发送sync报文,通知rru开始进行时间同步;

56.2)rru中的fpga解码后识别出sync报文,tsu单元给sync报文加上时间戳,然后交给pmacu单元发给arm;

57.3)arm接收到sync报文,提交给上层的开源ptp协议栈应用程序,开源ptp协议栈应用程序处理sync报文并将对应的时间戳信息作为sync报文的接收戳信息t2;

58.4)开源ptp协议栈应用程序若检测sync报文为一步同步报文,则从sync报文中提取bbu的发送时间戳信息t1;

59.5)开源ptp协议栈应用程序生成delay req报文,arm将delay req报文发送给pmacu单元;

60.6)pmacu单元将接收到的delay req报文,由tsu单元加上时间戳,然后发送给bbu,同时arm从fpga获取delay req报文的时间戳信息t3;

61.7)bbu收到delay req报文后,生成delay resp报文发送给rru;

62.8)rru收到delay resp报文,从报文中提取bbu的接收时间戳信息t4,经过将上述时间戳信息(t1、t2、t3、t4)参与计算后,arm控制hcu进行对时操作,hcu输出1pps及高精度

tod信息供fpga同步,实现与bbu的同步。

63.如图4所示,在上述的步骤4)处,开源ptp协议栈应用程序若检测sync报文为二步同步报文,执行如下步骤:

64.41)bbu会发出follow up报文,fpga接收follow up报文,由tsu单元加上时间戳,并发送给arm;

65.42)arm接收到follow up报文,将其提交给开源ptp协议栈应用程序,开源ptp协议栈应用程序忽略follow up报文的打戳信息,从sync报文中提取bbu的发送时间戳信息t1,然后跳转到上述步骤5)。

66.在步骤8)处,arm通过一定算法计算出链路延迟及时间偏移,并控制hcu进行对时操作。

67.需要指出的是,遵从ieee 1588规范的主从时钟同步是一个逐步调优的过程,这个过程由主时钟bbu端发起并周期性地进行,以期达到一个较为稳定和理想的同步状态。

68.fpga中实现的功能主要是标记时间戳功能的tsu单元以及ptpv2报文转发功能的pmacu单元,其中tsu单元有具体分为打时间戳和报文解析两部分功能。由于rru与bbu之间通信规定的1588的协议数据使用的是udp协议的包承载,使用的是标准的以太网mac协议,二者之间mac帧格式是ip帧。因此报文解析的前提是fpga检测到以太网mac帧格式,首先检测数据帧是不是ip帧,然后才检测是不是udp协议的报文。

69.本发明中使用的帧格式见表1,其中,当类型值等于0x0800时表明该数据帧是ip帧,数据字段包括ip头和负载数据,数据前20字节为标准ip头,8位协议取值定义取值为17(应用中,1588协议数据采用udp包来承载,对应的值是17)。

70.7字节1字节6字节6字节2字节46

‑

1500字节4字节前导码起始帧目的物理地址源物理地址类型数据帧序列检测

71.表1

72.数据字段的数据区包括udp的包头和udp负载,见图7。其中,源/目的端口指明发方和接收方的端口号,udp数据区就是上层应用实际发送或接收的数据,1588协议数据就包含在这里的udp负载区段。由于udp数据可由用户随意指定,因此,在1588实现中,需要根据udp报头中的端口信息和长度字段来辅助判断当前接收到的是否是1588数据,也就是说,如果udp数据为1588数据,必须同时满足以下几个条件:

73.1)端口号为标准1588协议指定的端口:319或320;

74.2)长度字段值至少达到ptp报头的大小(即34字节),参见图8;

75.3)ptp报头的版本字段取值为2。

76.因此,fpga对报文的正确解析,检测出ptpv2报文后,就可以进行打时间戳。如果按照先解析报文是不是ptp类型的报文,再进行打时间戳,会导致时间戳的延时。为了同时进行报文解析和打时间戳,通信协议规定,不管报文是不是ptpv2报文,都会为其打时间戳,同时判断是不是ptp报文,将是ptp的报文标记好时间信息后,送到pmacu单元,不是ptp报文则直接丢弃时间信息,并把报文送到pmacu模块,这样可以做到尽量减小对时间同步的影响。

77.fpga对来自arm或bbu的报文的正确解析后,时间戳也已经标记完成,标记的具体位置本发明中是由以太网的帧格式决定。帧格式的前8个字节分别表示位同步和帧起始位置,因此只要fpga识别出第七个字节处,检测到帧的起始位,就对此刻的时间信息记下,完

成时间戳功能。

78.fpga将标记好时间戳的报文送到arm或bbu的功能是在pmacu模块实现的,如图5所示,包括收发数据的fifo存储单位、mii转rmii模块、mdio、fpga自带的mac的ip等。由于现有平台中arm处理器功能的限制,fpga和arm之间只能通过rmii接口实现ptp报文传输。fpga不能直接调用rmii协议,因此需要由mii转rmii模块,通过调用mii协议的ip,并在数据的输入输出端加入fifo模块,保证数据传输过程完全对齐,最终实现ptpv2报文的正确传输。

79.fpga中tsu单元,该部分功能是首先对进入tsu单元的以太网数据包在计数器模块内计数,等确定好7字节后,产生使能信号,确定时间信息后,触发寄存器的使能信号,将时间信息存入寄存器。并在后续和报文打包送入pmacu单元,供后续计算延时,具体见图6。

80.本发明的第二个目的是实现成本控制,所采用的技术方案能够尽可能地降低成本。因为无需更换更高级的fpga芯片或arm芯片。

81.本发明的第三个目的是实现研发时间可控,要求所选用的技术方案易于实现,可在既定的研发周期内完成,不至于因研发周期过长导致最终研发出的产品失去市场机会。采用的第三方时钟同步芯片,其驱动是基于开源的实现,且有技术支持提供保障,因此,移植到现有的平台,所需花费的研发时间可控。

82.比较起来,arm的linux内核的ptp功能移植的工作量和难度都要大得多,为了减轻研发负担及降低难度,移植时不追求功能大而全,而采用最小移植策略,即从支持ptp功能的较低版本(v3.x)的内核中移植相关功能代码,不相干的代码一律剔除,移植目标是只需达到可支持基本的ptp时钟同步功能即可。

83.至于ptpv2报文的处理,这部分可以完全基于开源的实现,几乎不占用研发周期。

84.总之,以上几方面措施可保证项目的研发时间可控。

85.本发明的第四个目的是易于扩展,要求所采用的技术方案具有良好的扩展性,在功能升级时,不需要做太大的架构改动就容易实现。

86.实现本发明第四个目的的技术方案是:所采用的时钟同步方案基于开源的实现,ptp协议栈运行在arm处理器系统中,功能易于扩展。本技术方案的组织架构较为开放,具有通用性,架构中的第三方时钟芯片与arm处理器甚至fpga芯片均不必局限于单一的某种型号,产品设计者可以根据自己所使用产品的相应芯片型号进行替换,只要保持同样的组织架构,均可实现相同的功能,并达到预期的精度要求。本技术方案的设计思路不仅适用于从时钟的同步设计,也适用于主时钟的同步设计,当然,后者对于fpga所要实现的功能要求更多也更复杂一些。

87.以上所述实施例仅表达了本发明的实施方式,其描述较为具体和详细,并不能因此而理解为对本发明专利范围的限制。应当指出的是,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。