1.本发明涉及神经网络运算领域,特别涉及一种基于异构计算的嵌入式神经网络加速系统。

背景技术:

2.随着近些年深度学习的迅速发展和广泛的应用,卷积神经网络(cnn)已经成为检测和识别领域最好的方法,它可以自动地从数据集中学习提取特征,而且网络层数越多,提取的特征越有全局性。通过局部连接和权值共享可以提高模型的泛化能力,大幅度提高了识别分类的精度。

3.现有公开号为cn110991631a的中国专利,其公开了一种基于fpga的神经网络加速系统。该系统依据卷积神经网络天然具有的并行性以及全连接层的稀疏性,通过运算资源重用,并行处理数据和流水线设计,并利用全连接层的稀疏性设计稀疏矩阵乘法器大大提高运算速度,减少资源的使用,从而在不影响卷积神经网络推断准确率的情况下,提高推断速度。

4.上述的这种基于fpga的神经网络加速系统具有降低系统整体功耗的优点,但是上述的这种基于fpga的神经网络加速系统依旧存在着一些缺点,如:运算速度较慢。

技术实现要素:

5.针对背景技术中提到的问题,本发明的目的是提供一种基于异构计算的嵌入式神经网络加速系统,以解决背景技术中提到的问题。

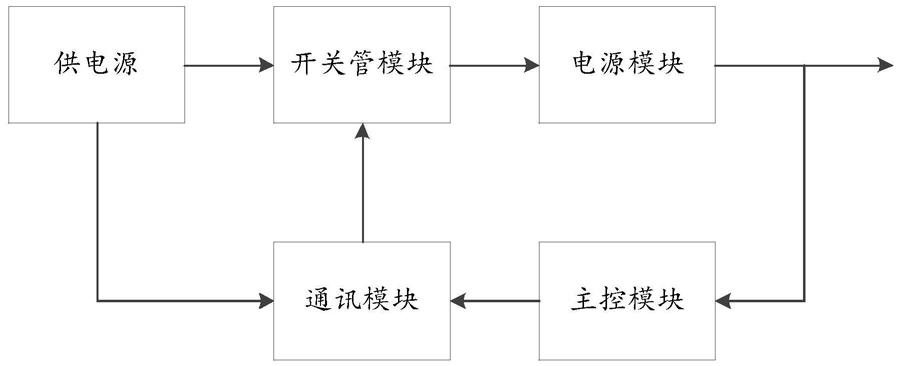

6.本发明的上述技术目的是通过以下技术方案得以实现的:一种基于异构计算的嵌入式神经网络加速系统,具体包括以下步骤:s1、接收数据以获取待检测图像的参数,将用于视频图像处理的整个卷积适配于脉动阵列并将其获取,将离线开发好的神经网络模型和参数转换成加速器能识别的神经网络指令;s2、利用fpga模块和数据预处理模块接收所述神经网络指令并存储;s3、利用所述数据预处理模块执行神经网络应用程序,并将接收的数据存储至存储器中,并利用加速器发出信号,所述数据预处理模块内设有对输入数据进行行对齐转换的线性储存器,所述数据预处理模块根据输入图像尺寸及卷积核的大小对图像数据进行数据对齐预处理并生成卷积矩阵,并行输入到fpga模块的卷积核中;s4、利用所述fpga模块形成的卷积核参数获取模块、二值化卷积神经网络结构和缓存模块;s5、利用所述加速器开始进行神经网络运算,以产生运算数据;s6、完成神经网络运算,利用所述加速器发出一第二信号至该处理器,利用所述处理器继续执行该神经网络应用程序进行运算。

7.较佳的,所述s1中接收数据以获取待检测图像的参数时采用的是无线数据接收模

块。

8.较佳的,所述s1中使用指令控制单元,指令控制单元用于从指令缓存单元中获取神经网络指令,并将神经网络指令进行译算。

9.较佳的,所述神经网络指令的译算采用指令控制单元,所述指令控制单元用于获取运算指令将运算指令译码为第一微指令和第二微指令,并将所述第一微指令发送给压缩单元,将所述第二微指令发送给所述运算单元和存储单元,所述存储单元用于存储输入数据、处理后的输入数据、运算指令以及运算结果。

10.较佳的,所述输入数据包括至少一个输入神经元和/或至少一个权值,所述处理后的输入数据包括处理后的输入神经元和/或处理后的权值。

11.较佳的,所述fpga模块用于接收来自上位机的控制指令,并根据控制指令确定awg的工作状态,awg的工作状态为输入状态或输出状态。

12.较佳的,所述fpga模块集成在fpga芯片内,所述fpga芯片包含arm模块,所述arm模块通过内部的协议控制单元对网络数据按预设的协议进行数据处理。

13.综上所述,本发明主要具有以下有益效果:本基于异构计算的嵌入式神经网络加速系统在进行嵌入式神经网络加速时通过异构计算实现,通过接受数据获取待检测图像的参数后,使用离线开发好的神经网络模型和参数转换成加速器能识别的神经网络指令,再利用fpga模块和数据预处理模块接收神经网络指令并存储和进行卷积计算,之后利用加速器完成加速,能够加快运算速度。

具体实施方式

14.下面对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

15.实施例1一种基于异构计算的嵌入式神经网络加速系统,具体包括以下步骤:s1、接收数据以获取待检测图像的参数,将用于视频图像处理的整个卷积适配于脉动阵列并将其获取,将离线开发好的神经网络模型和参数转换成加速器能识别的神经网络指令;s2、利用fpga模块和数据预处理模块接收神经网络指令并存储;s3、利用数据预处理模块执行神经网络应用程序,并将接收的数据存储至存储器中,并利用加速器发出信号,数据预处理模块内设有对输入数据进行行对齐转换的线性储存器,数据预处理模块根据输入图像尺寸及卷积核的大小对图像数据进行数据对齐预处理并生成卷积矩阵,并行输入到fpga模块的卷积核中;s4、利用fpga模块形成的卷积核参数获取模块、二值化卷积神经网络结构和缓存模块;s5、利用加速器开始进行神经网络运算,以产生运算数据;s6、完成神经网络运算,利用加速器发出一第二信号至该处理器,利用处理器继续执行该神经网络应用程序进行运算。

16.其中,s1中接收数据以获取待检测图像的参数时采用的是无线数据接收模块。

17.其中,s1中使用指令控制单元,指令控制单元用于从指令缓存单元中获取神经网络指令,并将神经网络指令进行译算。

18.其中,神经网络指令的译算采用指令控制单元,指令控制单元用于获取运算指令将运算指令译码为第一微指令和第二微指令,并将第一微指令发送给压缩单元,将第二微指令发送给运算单元和存储单元,存储单元用于存储输入数据、处理后的输入数据、运算指令以及运算结果。

19.其中,输入数据包括至少一个输入神经元和/或至少一个权值,处理后的输入数据包括处理后的输入神经元和/或处理后的权值。

20.其中,fpga模块用于接收来自上位机的控制指令,并根据控制指令确定awg的工作状态,awg的工作状态为输入状态或输出状态。

21.其中,fpga模块集成在fpga芯片内,fpga芯片包含arm模块,arm模块通过内部的协议控制单元对网络数据按预设的协议进行数据处理。

22.综上,本基于异构计算的嵌入式神经网络加速系统在进行嵌入式神经网络加速时通过异构计算实现,通过接受数据获取待检测图像的参数后,使用离线开发好的神经网络模型和参数转换成加速器能识别的神经网络指令,再利用fpga模块和数据预处理模块接收神经网络指令并存储和进行卷积计算,之后利用加速器完成加速,能够加快运算速度。

23.尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。

技术特征:

1.一种基于异构计算的嵌入式神经网络加速系统,其特征在于:具体包括以下步骤:s1、接收数据以获取待检测图像的参数,将用于视频图像处理的整个卷积适配于脉动阵列并将其获取,将离线开发好的神经网络模型和参数转换成加速器能识别的神经网络指令;s2、利用fpga模块和数据预处理模块接收所述神经网络指令并存储;s3、利用所述数据预处理模块执行神经网络应用程序,并将接收的数据存储至存储器中,并利用加速器发出信号,所述数据预处理模块内设有对输入数据进行行对齐转换的线性储存器,所述数据预处理模块根据输入图像尺寸及卷积核的大小对图像数据进行数据对齐预处理并生成卷积矩阵,并行输入到fpga模块的卷积核中;s4、利用所述fpga模块形成的卷积核参数获取模块、二值化卷积神经网络结构和缓存模块;s5、利用所述加速器开始进行神经网络运算,以产生运算数据;s6、完成神经网络运算,利用所述加速器发出一第二信号至该处理器,利用所述处理器继续执行该神经网络应用程序进行运算。2.根据权利要求1所述的一种基于异构计算的嵌入式神经网络加速系统,其特征在于:所述s1中接收数据以获取待检测图像的参数时采用的是无线数据接收模块。3.根据权利要求1所述的一种基于异构计算的嵌入式神经网络加速系统,其特征在于:所述s1中使用指令控制单元,指令控制单元用于从指令缓存单元中获取神经网络指令,并将神经网络指令进行译算。4.根据权利要求1所述的一种基于异构计算的嵌入式神经网络加速系统,其特征在于:所述神经网络指令的译算采用指令控制单元,所述指令控制单元用于获取运算指令将运算指令译码为第一微指令和第二微指令,并将所述第一微指令发送给压缩单元,将所述第二微指令发送给所述运算单元和存储单元,所述存储单元用于存储输入数据、处理后的输入数据、运算指令以及运算结果。5.根据权利要求4所述的一种基于异构计算的嵌入式神经网络加速系统,其特征在于:所述输入数据包括至少一个输入神经元和/或至少一个权值,所述处理后的输入数据包括处理后的输入神经元和/或处理后的权值。6.根据权利要求1所述的一种基于异构计算的嵌入式神经网络加速系统,其特征在于:所述fpga模块用于接收来自上位机的控制指令,并根据控制指令确定awg的工作状态,awg的工作状态为输入状态或输出状态。7.根据权利要求1所述的一种基于异构计算的嵌入式神经网络加速系统,其特征在于:所述fpga模块集成在fpga芯片内,所述fpga芯片包含arm模块,所述arm模块通过内部的协议控制单元对网络数据按预设的协议进行数据处理。

技术总结

本发明公开了基于异构计算的嵌入式神经网络加速系统,其技术方案要点是:具体包括以下步骤:S1、接收数据以获取待检测图像的参数,将用于视频图像处理的整个卷积适配于脉动阵列并将其获取,将离线开发好的神经网络模型和参数转换成加速器能识别的神经网络指令;S2、利用FPGA模块和数据预处理模块接收所述神经网络指令并存储;S3、利用所述数据预处理模块执行神经网络应用程序,并将接收的数据存储至存储器中,并利用加速器发出信号;S4、利用所述FPGA模块形成的卷积核参数获取模块、二值化卷积神经网络结构和缓存模块;基于异构计算的嵌入式神经网络加速系统具有运算速度快的优点。入式神经网络加速系统具有运算速度快的优点。

技术研发人员:丁钰 高凌云

受保护的技术使用者:无锡锦铖人工智能科技有限公司

技术研发日:2020.04.17

技术公布日:2021/10/21

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。