cni综合检测仪通用硬件处理平台

技术领域

1.本发明涉航空cni外场检测仪的通用处理平台,尤其是基于软件无线电的cni综合检测仪通用处理平台。

背景技术:

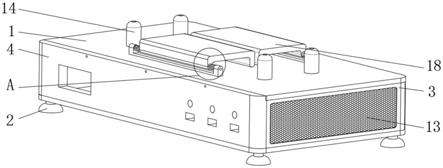

2.随着航空电子、计算机技术的快速发展,航空电子系统综合化程度日益提高,对系统测试也提出了更高的要求。机载通信导航识别子系统(cni)是飞机重要组成部分。飞机上安装了一定数量不同种类的通信导航识别设备,这些设备组成了“机载通信导航识别子系统”,完成各种通信联络、导航和识别任务。大量独立的电子设备的安装,造成航空电子设备体积、重量、种类和耗电不断增加,使用和维护也日益复杂,加重了飞机驾驶员和外场飞机维护人员的工作负担。当前各种飞机cni子系统功能多达十余种,频段覆盖从2mhz-6000mhz,波形体制不同,带宽差异大,信号调制方式不一。为了确保飞机的cni子系统工作正常,需要地面工作人员使用外场检测仪定期对机载设备进行检测维护或排故。现在cni外场检测设备其射频信道通常针对某项功能专门设计,普适性差;采用资源堆叠方式完成多个功能的测试覆盖,不同cni功能测试由不同硬件处理实现,体积重量大,功耗高,经济性不佳;硬件处理平台不通用,升级空间小,不能适应未来新出现的cni功能波形。现有cni检测设备其射频通道采用超外差体制,信号经过两级变频和多级放大滤波,存在大量模拟电路和分立元器件,芯片化水平差,没有进行综合化设计,需要外场飞机保障人员数量多,造成工作不便。

3.通常外场测试系统的硬件环境大都是机箱形式存在的。在搭建硬件系统时,测试系统的搭建是本着积木式结构的机箱,机箱要根据飞机cni功能需要选取相应种类和数量的模板、仪器。随着测试规模的发展,积木式添加模板或仪器,增加测试功能,实现单个系统的测试。这种积木式、模块化的结构体积重量大。

技术实现要素:

4.本发明的目的是针对现有技术存在不足之处,提供一种具备良好的通用性、高度综合化,扩展性,体积重量小,携带方便,能够降低成本,方便外场保障人员排故、维护的cni综合检测仪硬件处理平台,通过该平台能够完成现有多个cni功能测试检测。

5.本发明的上述目的可以通过以下技术方案予以实现:一种cni综合检测仪通用硬件处理平台,包括:分别与电源及接口单元连接的射频调理单元、收发通道单元、数字处理单元,以及连接射频调理单元的连接器和时钟单元,其特征在于:数字处理单元通过收发通道单元相连射频调理单元进行双向通信;射频调理单元通过采用流水线架构,实现2mhz-6000mhz信号频段滤波、信号幅度调理和适配处理,处理信号通过收发通道单元,综合使用零中频处理和直接射频处理,对接收信号进行频率变换、滤波和放大采样,将模拟射频信号变换为数字信号,同时将待发射数字信号变换为模拟信号;数字处理单元利用内置主控现场可编程门阵列fpga控制收发通道单元的收发数据,将完成初步处理的数据送入信号处理

fpga对cni各功能波形的调制解调、解扩解跳和参数测量,参数测量数据通过外部存储器连接接口(emif)送入并行数字信号处理器dsp组和嵌入式处理器powerpc完成纠错编译码、组帧解帧、参数解算、数据算法和对波形的基带处理,对外实现千兆网口和rs232调试通信,基于软件无线电加载不同信号处理软件实现不同cni功能检测。

6.本发明的有益效果是具备良好的通用性。本发明采用分别与电源及接口单元连接的射频调理单元、收发通道单元、数字处理单元,以及连接射频调理单元的连接器和时钟单元这些通用的综合处理器等公用模块,基于软件无线电加载不同信号处理软件软将数字化处理尽量前移,获得了最大的电路密度和检测能力;通过通用的综合处理器等公用模块将传统的cni系统中的众多设备功能划分为数十个软件功能模块,通过综合零中频处理和直接射频处理的技术手段,基于同样的硬件平台和软件无线电实现不同cni功能的检测测试,使得硬件处理平台具备良好的通用性。通过加载不同cni功能算法软件实现不同cni功能的检测测试,具备高度通用性。

7.高度综合化。本发明以可编程的通用硬件处理模块为基础,采用大规模集成soc芯片以及高度集成化,充分采用综合化设计技术、数字化技术和模块化技术,通过综合应用零中频和直接射频处理技术,把系统按照功能模块划分为射频处理、功能信号处理和数据处理几大部分,用系统管理控制、数据处理和信号处理等软件实现各系统功能。这样一来,所实现的cni检测系统统与传统的系统相比在功能上更加强大、结构上更加紧凑、可靠性更高。

8.扩展性好。本发明采用流水线架构,实现2mhz-6000mhz信号频段滤波、信号幅度调理和适配处理,易于纳入新功能、可扩展增强现有功能。在不破坏现有设备的情况下,能通过升级软件方便纳入未来新的cni功能检测,能适应未来cni功能波形发展。

9.体积重量小,携带方便,方便外场保障人员排故维护。本发明以可编程逻辑器件和可编程射频soc器件为基础:通过收发通道单元相连射频调理单元进行双向通信的数字处理单元,通过功能软件化实现,缩小了体积、减轻了重量,提高维修性和保障性,收发通道单元采用soc芯片可以有效地降低电子信息系统产品的开发成本,降低全寿命周期成本。其体积和重量相对于同类型处理平台减少了30%~40%,寿命周期成本降低了40%~50%。

10.良好的经济性。本发明通过在通用处理平台上运行不同软件实现不同功能的检测,显著提高了外场飞机地面检测的效能。对新技术、新的性能特性要求以及对平台变化、任务变化的适应性明显提高,可大大减轻后勤保障方面的负担,成本费用将大大减小。维护人员可实现对机载cni系统模块的扫描和系统故障的定位与隔离,大量地节约了地面维修时间与维修成本。

11.本发明适应多种cni功能波形,频域上覆盖2mhz-6000mhz,功能上覆盖短波通信(hf)、超短波通信(uv)、无线电罗盘(adf)、信标(xs)、仪表着陆(ils)、塔康(tacan)、精密测距(dmep)、微波着陆(mls)、无线电高度表(alt)、航管应答(atc)、敌我识别(iff)、卫通(satcom)、船舶自动识别(ais)、频谱分析等。

附图说明

12.下面结合附图和实施例对本发明进一步说明。

13.图1是本发明的基于软件无线电的cni综合检测仪通用处理平台组成示意图。

14.图2是图1电源及接口单元的电路原理示意图。

15.图3是图1的时钟单元电路原理示意图。

16.图4是图1的工作流程图。

17.为了使本发明实现的技术手段、创作特征、达成目的与功效易于明白了解,下面对本发明进一步阐述。

具体实施方式

18.参阅图1。在以下描述的优选实施例中,一种cni综合检测仪通用硬件处理平台,包括:分别与电源及接口单元连接的射频调理单元、收发通道单元、数字处理单元,以及连接射频调理单元的连接器和时钟单元,其特征在于:数字处理单元通过收发通道单元相连射频调理单元进行双向通信;射频调理单元通过采用流水线架构,实现2mhz-6000mhz信号频段滤波、信号幅度调理和适配处理,处理信号通过收发通道单元,综合使用零中频处理和直接射频处理,对接收信号进行频率变换、滤波和放大采样,将模拟射频信号变换为数字信号,同时将待发射数字信号变换为模拟信号;数字处理单元利用内置主控现场可编程门阵列fpga控制收发通道单元的收发数据,将完成初步处理的数据送入信号处理fpga对cni各功能波形的调制解调、解扩解跳和参数测量,参数测量数据通过外部存储器连接接口(emif)送入并行数字信号处理器dsp组和嵌入式处理器powerpc完成纠错编译码、组帧解帧、参数解算、数据算法和对波形的基带处理,对外实现千兆网口和rs232调试通信,基于软件无线电加载不同信号处理软件实现不同cni功能检测。

19.进一步地,所述电源及接口单元为通用硬件平台提供工作所需直流电源和接口,直流电源包括5v、3.3v、2.5v、1.8v、1.5v、1.3v和1.2v等。接口包括dsp jtag接口、fpga jtag接口、网口和rs232接口等。

20.进一步地,收发通道单元包括采用多种soc芯片完成多种cni功能信号处理的并行高速模数转换器ad组。在可选的实施例中,并行高速模数转换器ad组包括但不限于,与射频调理单元和主控fpga射频收发器进行双向通信的ad9361、ad9371、ad9265、ad7606、ad9957和ad7606。

21.使用零中频(亦称为zero-if或zif)架构的ad9361收发器,以实现带宽200khz-68mhz、收发频率300mhz-6000mhz的cni功能信号。ad9361可以支持多种可编程无线电应用,调制方案和网络规范,具备高性能、高集成度。当使用ad9361的内部lo(适用于具有推荐性能的参考时钟源)时,ad9361将在无噪底限制时实现约-40db的evm。evm具体表示接收机对信号进行解调时产生的iq分量与理想信号分量的接近程度,是考量调制信号质量的一种指标。ad9361接收器正交校准使用一种算法来分析接收到的整个数据频谱,从而在整个带宽上创建平均校正。ad9361使用初始化校准来减少优化硬件设计提供的正交不平衡。初始化校准使用处于单一频率且采用单一衰减设置的cw信号音。对于单载波用例和相对较窄的带宽(如20mhz),该校正在目标带宽上会产生良好的镜像抑制。这被称为非频率相关算法。该算法对接收到的数据执行操作并实时更新。

22.ad9371使用分布在有用信号带宽上的多个内部生成的信号音进行初始发送路径校准,并确定跨多个发送衰减设置的校正系数。运行期间,发送信号路径跟踪校准使用实际

发送的数据并定期更新校正系数;在通过注入测试音进行初始化期间以及使用实际接收到的数据进行操作期间运行接收镜像抑制校准,校准可根据频率相关不平衡以及非频率相关不平衡进行调整。该算法会实时更新。

23.ad9371采用更先进的算法和电路实施校正,在占用的信号带宽上的性能优于ad9361,两者之差约为25db。ad9361和ad9371都优化了模拟信号和lo路径,从本质上减少了正交不平衡。

24.ad9265是一款16位、125msps模数转换器adc,旨在支持需要高性能、低成本、小尺寸且具多功能性的通信应用。具有宽带宽、差分采样保持模拟输入放大器,支持用户可选的各种输入范围。ad9265adc内核采用多级、差分流水线架构完成频率2mhz-30mhz的短波信号接收数字化。

25.ad9957采用集成了高速dds、14bit dac、通用i/q调制器与捷变上变频器,内置参考时钟倍频器电路和数字滤波器,完成2mhz-30mhz的短波信号和无线电罗盘信号的模拟信号输出。ad9957可用作通用i/q调制器与捷变上变频器,内置参考时钟倍频器允许使用低成本、低频外部时钟用作该系统时钟,接收交错的正交i/q数据流并且对其插值,并且当与时钟同步时合成对传输有用的信号;同时仍可提供优良的动态性能。输入端对符号进行编码和脉冲整形,输入端采样得到的数据进行二进制编码,数据格式化为二进制补码或偏移二进制,正交调制模式时向i/q两路提供数据。

26.ad7606实现无线电罗盘sin/cos的采样。ad7606采用5v单电源供电,可以处理

±

10v和

±

5v双极性输入信号,同时所有通道均能以高达200ksps的吞吐速率采样。输入箝位保护电路可以耐受高达

±

16.5v的电压。无论以何种采样频率工作,ad7606的模拟输入阻抗均为1mω。它采用单电源工作方式,具有片内滤波和高输入阻抗,因此无需驱动运算放大器和外部双极性电源。ad7606抗混叠滤波器的3db截止频率为22khz;当采样速率为200ksps时,它具有40db抗混叠抑制特性。

27.为实现对cni功能的全面覆盖,收发通道单元包括5种型号,6块soc芯片,实现cni功能射频信号的收发处理,分别为ad9361_a、ad9361_b、ad9371、ad9265、ad9957和ad7606。不同cni功能信号具有不同的工作频率、带宽,本发明通过上述soc芯片完成cni功能全覆盖。当测试某个cni功能时,根据待测cni功能信号特点,选取不同soc芯片完成处理,具体如下所述。

28.对于收发频率70mhz-6000mhz,带宽200khz-68mhz的cni功能信号,选取自身集成了低噪声放大器lna、有源混频器mixer、功放驱动放大器、模/数转换器或者模拟/数字转换器adc和模/数转换器dac的ad9361芯片收发通道进行处理。ad9361芯片采用零中频架构,具备高性能、高集成度,通过正交误差校准和直流偏置校准的功能优化很好的解决了此前零中频架构的直流偏置和正交误差限制;完全集成的锁相环pll可针对所有接收和发射通道提供低功耗的小数n分频频率合成。本实施例采用两块ad9361,最多支持4t4r,满足部分cni功能同时4通道收发要求,同时也为未来功能扩展留足空间。主控fpga通过spi串行接口完成ad9361初始化,包括时钟配置、射频rf输入接口配置、增益设置、工作频率配置、带宽配置。主控fpga通过低电压差分信号lvds和ad9361进行数据交互,完成数据收发,将频率70mhz-6000mhz,带宽200khz-68mhz的cni功能接收信号通过射频调理单元初步处理以后,进入ad9361经过放大、变频到基带、滤波和采样处理,采样数据通过低电压差分信号lvds接

口送入主控fpga。主控fpga待发射数据经过lvds送入ad9361,经过滤波、上变频后放大送到射频调理单元进行进一步处理。

29.对于收发频率300mhz-6000mhz,带宽大于68mhz的cni功能信号,选取ad9371收发通道进行处理。ad9371发射器合成带宽最大可达250mhz,接收器带宽最大可达100mhz,适合处理带宽较大的cni功能信号。ad9371芯片和ad9361类似,也采用零中频架构,内部集成lna、混频器、滤波器、adc和dac。主控fpga通过spi串行接口完成ad9371初始化,包括时钟配置、增益设置、工作频率配置、带宽配置、采样频率配置。主控fpga通过jesd204b接口和ad9371进行数据交互,完成数据收发。频率300mhz-6000mhz,带宽大于68mhz的cni功能接收信号通过射频调理单元初步处理以后,进入ad9371,经过放大、变频到基带、滤波和采样处理,采样数据通过jesd204b接口送入主控fpga。主控fpga待发射数据经过jesd204b送入ad9371,经过滤波、上变频后放大送到射频调理单元进行进一步处理。

30.对于频率较低的短波信号,采用直接射频处理,完成接收短波信号的数字化。选用ad9265,它是16位、采样速率最高可达80mhz的模数转换器adc,特点是:小尺寸、宽带宽、多功能通信应用。芯片采用多级、差分流水线架构,并集成了输出纠错逻辑。ad9265输出数据通过并行接口送入主控fpga。

31.选用ad9957完成2mhz-30mhz的短波信号和无线电罗盘信号的模拟信号输出。ad9957将一个高速、直接数字频率合成器dds、一个高性能、高速、14位数模转换器dac、时钟乘法器电路、数字滤波器和其它dsp功能集成在一个芯片上,该器件可以在工作速度、功耗和频谱性能方面提供更好的性能。待发送短波和无线电罗盘信号通过主控fpga送入ad9957,进行数字-模拟转换后,进入射频调理单元进行进一步处理。

32.实现无线电罗盘sin/cos采样选用ad7606芯片,ad7606芯片是一款16位、8通道同步采样模数数据采集系统,各器件均内置模拟输入箝位保护、二阶抗混叠滤波器、采样保持放大器、16位电荷再分配逐次逼近模数转换器adc、灵活的数字滤波器、2.5v基准电压源、基准电压缓冲以及高速串行和并行接口。ad7606输出数据通过串行接口送入主控fpga。

33.进一步地,数字处理单元包括:带有双倍速率同步动态随机存储器ddr、非易失flash闪存的主控现场可编程门阵列fpga、信号处理fpga,与主控fpga和信号处理fpga进行双向通信的数字信号处理器dsp组和powerpc。主控fpga通过并行总线与ad9957、ad7606进行数据交互,通过spi串行外设接口实现对ad9957的控制。

34.主控fpga完成的功能主要是前端收发通道单元的控制、状态收集和数据预处理,还包括串口接口、flash接口以及协议解析等,选用xilinx公司的zynq-7000系列中型号为xc7z045-ffg900实现。xc7z045采用28nm制造工艺,配备双核arm cortex-a9处理器,该处理器与基于28nm的可编程逻辑集成,可实现优异的性能功耗比和最大的设计灵活性,具有高达6.25m的逻辑单元以及从6.6gb/s到12.5gb/s的收发器。zynq-7000可扩展处理平台(epp)将双armcortex-a9mpcore处理器系统与可编程逻辑和硬ip外设紧密集成在一起,提供了灵活性、可配置性和性能的完美组合。主控fpga同时连接ad9361、ad9371、ad9265、ad9957和ad7606,适配多种制式不同频率、不同带宽cni功能信号。同时主控fpga还通过gtx和信号处理fpga完成数据交互。

35.信号处理fpga通过低功耗吉比特收发器gtx和主控fpga完成数据交互,同时通过emif总线和dsp1、dsp2以及powerpc连接,完成数据交互,完成对cni各功能波形的调制解

调、解扩解跳、参数测量等功能。信号处理fpga可以选用xilinx kintex ultrascale系列的高性能fpga xcku085-2flva1517,它提供多达4100个dsp slice,56.9mb bram,能够满足现在和将来cni技术发展需要。外围硬件电路主要包含jtag下载电路、bpi配置电路以及ddr3数据缓存接口电路。

36.数字信号处理器dsp组通过外部存储器接口emif总线与信号处理fpga实现数据交互功能,完成通信信号纠错编译码、组帧解帧,导航识别的参数解算、数据算法处理,完成对波形的基带处理等;powerpc芯片处理器完成cni功能的数据处理、协议处理,对外实现千兆网口、rs232调试通信等。

37.数字信号处理器dsp组中的dsp1、dsp2选用德州仪器(ti)推出的高端dsp芯片tms320c6455bctza,可实现更高性能、更精简代码、拥有更多片上存储器以及超高带宽的集成外设,应用范围更加广泛。

38.powerpc处理器采用freescale p2020nxn2khc,其包含两个内核,每个内核运行的频率均配置为1ghz。针对不同cni功能调用不同程序完成数据处理、功能协议处理,对外实现千兆网口、rs232调试通信等。

39.与射频调理单元相连的捷变收发器ad9361,通过spi串行外设接口与主控fpga完成控制通信。ad9361通过两个并行的数据总线接口p0和p1,采用低压差分信号lvds接口模式实现主控fpga与ad9361之间的数据交互。

40.与射频调理单元相连的捷变收发器ad9371的jesd204b数字接口由4条lane组成,通过一组gtx总线与主控fpga的gtx接口连接,完成数据通信;通过串行外设接口spi与主控fpga进行数据交互,完成控制通信。

41.与射频调理单元相连的ad9265输出数据直接由16位lvds/lvcmos输出端口连接到主控fpga,设置与控制通过三线式spi接口由主控fpga完成。

42.进一步地,数字处理单元中包括ddr,用于cni功能信号处理数据存储;包括flash,用于数字处理软件的存储。

43.连接器连接平台和外部数据接口、射频接口、调试接口。

44.射频调理单元实现2mhz-6000mhz射频信号调理适配处理,由滤波器、数控衰减、低噪放组成,完成信号滤波、幅度调理、接口适配等处理。

45.参阅图2。电源单元主要由电源隔离电路、电源保护电路和电源转换电路组成,主要实现emi共模滤波、浪涌电流限制;电源保护电路实现负载断电保护、短路防护和过热过流保护功能;电源转换电路主要实现将外部 28v输入电压转换为每个单元需要的电源电压。

46.接口单元包括网口、串口、dsp jtag接口和fpga jtag接口,主要是完成调试接口。

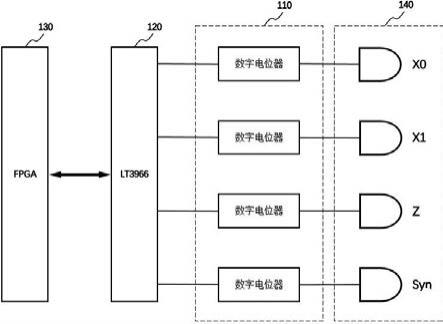

47.参阅图3。时钟单元为处理平台提供时钟支持。100mhz主时钟与射频开关切换相连,可以选择内外时钟源。射频开关与射频功分器相连,时钟信号通过功分后,送入与功分器相连的adclk944时钟分发芯片,为模块的fpga、pll等提供参考时钟源。数字处理单元dsp6455的clk2时钟接接口与25mhz有源晶振相连,由其提供时钟。dsp6455的clk1时钟接口与ics512倍频器相连,由其倍频后提供50mhz时钟。ad9265和ad9957采样时与锁相环芯片ad9520相连,由其提供时钟。powerpc时钟引脚分别与66.667mhz晶振和125mhz晶振相连,由其提供系统时钟和网口时钟。

48.参阅图4。在数字处理单元接收cni功能待测命令,根据待测cni功能加载dsp1、dsp2处理程序和主控fpga处理程序,根据待测功能配置射频调理单元的射频调理通道,初始化收发通道单元的收发通道,产生激励波形,接收待测射频信号,待测射频信号经射频调理单元送入收发通道单元,在此完成滤波、放大、变频、数字化等处理,送入数字处理单元进行处理解算,完成功能信号参数解算,形成测试结果和产生结果上报,结束程序,若收到新测试命令,返回dsp组,根据待测cni功能加载dsp1、dsp2处理程序和主控fpga处理程序,直到形成测试结果和产生结果上报,结束程序。

49.如果待测cni功能信号带宽小于68mhz,使用ad9361,设置本振频率、滤波器参数、收发采样频率和agc参数,配置收发数据端口,启动自校准,配置收发功能;如果待测cni功能信号带宽大于68mhz,使用ad9371,设置本振频率、滤波器参数、收发采样频率和agc参数,配置jesd204b接口,启动自校准,配置收发功能;如要测试短波功能,配置ad9265、ad9957工作参数和采样频率、数据接口;如测试无线电罗盘功能,则配置ad9265、ad7606工作参数和dsp产生激励基带数据,经emif总线送主控fpga,在主控fpga内部完成成型滤波、调制,送收发通道完成上变频,送入收发通道单元,经射频调理单元完成滤波、放大、变频等处理后送出,检测结果上报。

50.以上所述为本发明较佳实施例,应该注意的是上述实施例对本发明进行说明,然而本发明并不局限于此,并且本领域技术人员在脱离所附权利要求的范围情况下可设计出替换实施例。对于本领域内的普通技术人员而言,在不脱离本发明的精神和实质的情况下,可以做出各种变型和改进,这些变型和改进也视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。