1.本发明涉及功率因数校正领域,特别涉及一种延长掉电保持时间电路和方法。

背景技术:

2.随着现代工业的高速发展,电力系统的非线性负荷日益增多。这些非线性负荷产生的谐波电流注入到电网,使公用电网的电压波形产生畸变,严重地污染了电网的环境,为减小和消除谐波,应进行功率因数校正(powerfactor correct,pfc),从而获得接近正弦波的输入电流及接近1的功率因数。

3.一般pfc电路的输出电压vo是一个稳定的输出电压值(稳压型pfc),pfc电路输出通常与dc

‑

dc变换器连接。稳压型pfc电路设计简单,技术方案成熟。但其通常所需要的磁芯体积较大,开关过程中的损耗较大,为弥补以上缺陷,行业内提出了一种输出电压可变化的pfc电路(跟随型pfc),其输出电压随着输入电压的变化而变化。如st公司的pfc控制器l6563,其tbo引脚通过外接一个电阻器,即可实现输出电压跟随输入电压变化,其变化趋势如图1所示。在最低输入电压vin_min时刻,其输出电压为vo_min,在最高输入电压vin_max时刻,其输出电压为vo_max。跟随型pfc与稳压型pfc相比较,其磁芯尺寸约能够减小40%,其低压效率约提升1.2%。但跟随型pfc低压下输出电压较低,电容存储的能量降低,其掉电保持时间较稳压型pfc明显降低。

4.在突然断电的情况下,许多电子设备、仪器来不及做出反应,从而造成数据的丢失或者服务的中断。因此越来越多的电子设备、仪器要求提供较长掉电保持功能。

5.为保持较长的掉电保持时间,其通常做法为:1.pfc输出端增加大容量的储能电容或超级电容;2.增添额外电路,如申请号为201320603095.7的专利,提出的一种延长掉电保持时间的电路,其结构图如图2所示。

6.增加大容量的储能电容或超级电容,通常需要增添较多的成本和体积,不具备经济适用性。而201320603095.7的专利应用在跟随型pfc电路中将存在以下问题:

7.1、pfc电路的输出纹波电压较小,通常在10v左右,该电路的效果与电容c1、电容c2直接并联效果基本相当,这就同样需要较大储能电容,不具备经济适用性;

8.2、器件通常存在漏电流,长期工作后电容c2的电压会释放到与电容c1电压相等,其效果与输出端直接并联电容c2一样,同样需要较大储能电容,不具备经济适用性;

9.3、电流导通器件导通时,电容c2与电容c1易产生较大冲击电流,易损坏器件。

10.因此,现有的延长掉电保持时间的技术应用在跟随型pfc电路中存在明显不足,无法经济、高效的解决跟随型pfc电路低压输入下掉电保持时间短问题。

技术实现要素:

11.针对现有技术的不足,本发明提供一种延长掉电保持时间电路及方法。本发明几乎不增加开关电源的体积和成本下,却能显著延长跟随型pfc低压输入下的掉电保持时间。

12.本发明提供一种延长掉电保持时间电路,包括pfc电路、时间延长电路、dc

‑

dc电路

和控制电路。pfc电路、时间延长电路、dc

‑

dc电路依次串联连接,控制电路第一输出端与pfc电路连接。时间延长电路包括开关s2和电容c2。开关s2一端与电容c2一端电联接,且开关s2和电容c2连接在pfc电路的输出正端与输出负端之间。开关s2的控制端与控制电路的第二输出端连接,电容c2一端还与控制电路的第一输入端连接。

13.优选地,延长掉电保持时间电路还包括电阻r1,开关s2一端通过电阻r1与电容c2一端电联接,电阻r1用于限流。

14.优选地,延长掉电保持时间电路还包括二极管d1,开关s2与二极管d1并联连接,电容c2一端还与二极管d1的阴极连接。

15.延长掉电保持时间电路包括二极管d1的基础上,优选地,还包括电阻r1,开关s2一端通过电阻r1与电容c2一端电联接,电阻r1用于限流。

16.优选地,开关s2是mosfet或igbt或晶闸管或继电器。

17.一种延长掉电保持时间的控制方法,适用于前述不包括二极管d1的延长掉电保持时间电路,包括如下步骤:

18.步骤一,启动电源,确保输入电压正常,控制电路开始工作,执行步骤二;

19.步骤二,闭合开关s2,通过控制电路设置pfc电路输出电压vo为vo_p,然后判断电压vc2是否达到vo_p,若否,则进行步骤二,若是,则执行步骤三;

20.步骤三:关断开关s2,通过控制电路设置pfc电路输出电压vo为额定电压vo_nom,输出电压vo由vo_p快速下降至vo_nom,判断电压vc2是否下降至vo_th,若是,则返回执行步骤二,若否,则执行步骤四;

21.步骤四:判断是否进入掉电保持状态,若否,则执行步骤三,若是,则执行步骤五;

22.步骤五:控制电路控制开关s2进行软开通,每周期逐步增大开关s2的导通时间。

23.本发明还提供一种延长掉电保持时间的控制方法,适用于前述包括二极管d1的延长掉电保持时间电路,包括如下步骤:

24.步骤一,启动电源,确保输入电压正常,控制电路开始工作,执行步骤二;

25.步骤二,通过控制电路设置pfc电路输出电压vo为vo_p,然后判断电压vc2是否达到vo_p,若否,则进行步骤二,若是,则执行步骤三;

26.步骤三:通过控制电路设置pfc电路输出电压vo为额定电压vo_nom,输出电压vo由vo_p快速下降至vo_nom,判断电压vc2是否下降至vo_th,若是,则返回执行步骤二,若否,则执行步骤四;

27.步骤四:判断是否进入掉电保持状态,若否,则执行步骤三,若是,则执行步骤五;

28.步骤五:控制电路控制开关s2进行软开通,每周期逐步增大开关s2的导通时间。

29.相关术语解释:

30.电联接:包括直接或间接连接,并且还包括感应耦合之类的连接方式。

31.本发明仅使用开关和电容构建时间延长电路,具有如下技术效果:

32.1、在几乎不增加开关电源的体积和成本的情况下实现电压跟随;

33.2、且本发明电路仅需增添较小容量的电容即可明显延长掉电保持时间;

34.3、另外在器件开通过程中降低了冲击电流;

35.4、较传统解决方案相比,具有更小体积、更低成本、更高可靠性的优势。

附图说明

36.图1为跟随型输pfc输出电压与输入电压变化趋势图;

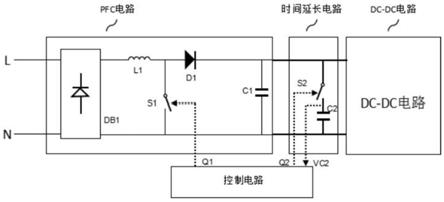

37.图2为现有延长掉电保持时间电路原理图;

38.图3为本发明实施例一电路原理图;

39.图4为本发明电路在各阶段关键节点的电压波形图;

40.图5为本发明实施例一的控制方法流程图;

41.图6为本发明实施例二的电路原理图;

42.图7为本发明实施例三的电路原理图;

43.图8为本发明实施例三的控制方法流程图;

44.图9为本发明实施例四的电路原理图。

具体实施方式

45.第一实施例

46.如图3所示,为本发明实施例一的电路原理图,一种延长掉电保持时间电路包括pfc电路,时间延长电路,dc

‑

dc电路,控制电路。pfc电路、时间延长电路、dc

‑

dc电路依次串联连接,控制电路第一输出端与pfc电路连接。pfc电路包括整流桥db1、电感l1、开关s1、二极管d1和电容c1。整流桥db1的第一输入端、第二输入端分别与交流电压的l端、n端连接,整流桥db1的第一输出端与电感l1的一端连接;电感l1的另一端与开关s1的一端、二极管d1的阳极连接,二极管d1的阴极与电容c1的一端连接,该连接点作为pfc电路的输出正端;电容c1的另一端与开关s1的另一端、整流桥db1的第二输出端连接,该连接点作为pfc电路的输出负端;开关s1的控制端与控制电路的第一输出端连接,控制电路通过输出第一输出信号q1控制开关s1的闭合和关断。时间延长电路包括开关s2和电容c2。开关s2与电容c2串联连接,并连接在pfc电路的输出正端与输出负端之间。开关s2与输出正端相连,电容c2与输出负端相连。开关s2的控制端与控制电路的第二输出端连接,控制电路的第二输出信号q2用于控制开关s2的闭合和关断,开关s2与电容c2的连接点与控制电路的第一输入端连接,控制电路通过第一输入端检测电容c2的电压幅值vc2。开关s2可以是mosfet、igbt、晶闸管或继电器等。pfc电路的输出电压vo波形和电容c2的电压vc2波形如图4所示。

47.如图5所示,实施例一的具体工作步骤及顺序如下:

48.步骤一,启动电源,确保输入电压正常,控制电路开始工作,执行步骤二;

49.步骤二,闭合开关s2,通过控制电路设置pfc电路输出电压vo为vo_p,vo_p的电压值通常设定为大于或等于pfc电路的最大输出电压值vo_max,该阶段为启动阶段,在此阶段pfc电路输出电压为vo_p,电容c2电压vc2逐步上升,判断电压vc2是否达到vo_p,若否,则进行步骤二,若是,则执行步骤三;

50.步骤三:关断开关s2,通过控制电路设置pfc电路输出电压vo为额定电压vo_nom,输出电压vo由vo_p快速下降至vo_nom,电容c2电压vc2基本保持为vo_p,在此阶段由于器件的一些漏电流存在,电压vc2以极其缓慢的斜率下降,判断电压vc2是否下降至vo_th,vo_th的电压值通常设置为小于vo_p,若是,则返回执行步骤二,若否,则执行步骤四;

51.步骤四:判断是否进入掉电保持状态,通常在输入电压关断、pfc电路保护或故障情况下视为电路进入掉电保持状态,若否,则执行步骤三,若是,则执行步骤五;

52.步骤五:控制电路控制开关s2进行软开通,每周期逐步增大开关s2的导通时间,减少器件所承受的电流应力,降低器件损坏的风险。

53.本实施例电路通过启动阶段或正常工作阶段,在电容c2储存了较多的能量,依据公式

54.thold=0.5*c*(vo_p2‑

v12)/p(公式1),

55.thold为掉电保持时间,c为电容c2的电容值,vo_p为掉电起始时刻电容c2的电压值、v1为掉电结束时刻电容c2的电压值,p为输出功率。

56.通常v1值为dc

‑

dc电路的最低工作电压值,当vo_p电压较高时,较少的电容值,即可显著增加电路的掉电保持时间。

57.第二实施例

58.如图6所示,为本发明的实施例二原理图,与实施例一相比,区别之处在于:时间延长电路还包括电阻r1,开关s2、电容c2与电阻r1串联连接,并连接在pfc电路的输出正端与输出负端之间。开关s2的控制端与控制电路的第二输出端连接,电阻r1和电容c2的连接点与控制电路的第一输入端连接。

59.电阻r1用以限流,更大程度的降低了开关s2开通过程中器件的电流应力,有利于选择更低规格的器件。

60.本实施例的控制方法及电路工作原理与实施例一相同,在此不作赘述。

61.第三实施例

62.如图7所示,为本发明的实施例三原理图,与实施例一相比,区别之处在于:本实施例的时间延长电路还包括二极管d2,开关s2与二极管d2并联连接,二极管d2阳极连接输出正端,二极管阴极连接电容c2一端,开关s2、二极管d2和电容c2的连接点与控制电路的第一输入端连接。

63.如图8所示,本实施例的具体工作步骤及顺序与实施例一相比,区别之处在于:执行步骤二时,无闭合开关s2的操作;执行步骤三时,无关断开关s2的操作。

64.第四实施例

65.如图9所示,为本发明实施例四原理图,与实施例三相比,区别之处在于:本实施例的时间延长电路还包括电阻r1,开关s2、电阻r1和电容c2依次串联连接,并连接在pfc电路的输出正端与输出负端之间,开关s2与二极管d2并联连接,二极管d2的阳极连接输出正端,二极管d2的阴极连接电阻r1的一端,电阻r1另一端和电容c2的连接点与控制电路的第一输入端连接,电阻r1的作用同实施例二中提及的电阻r1。

66.本实施例的控制方法及电路工作原理与实施例三相同,在此不作赘述。

67.以上公开的仅为本发明的优选实施例,但是本发明并非局限于此,任何本领域的技术人员在未脱离本发明的核心思想的前提下对本发明进行的若干修饰均应该落在本发明权利要求的保护范围之类。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。