performance[j].ieee transactions on power electronics,2013,28(1):573

‑

590)开展了栅极电感对mosfet关断漏源极电压过冲的影响研究,但并未考虑测试回路中栅极电阻、漏极电感等寄生参数偏大导致栅极电感变化影响较小这一因素,因此当改变栅极电感时,mosfet关断漏源极电压过冲变化现象不明显。

[0008]

此外,中国专利,如申请号:cn2021102768523,公开号:cn113067571 a公开一种改善关断特性的碳化硅mosfet驱动电路及控制方法,包括:pwm驱动模块,用于基于接收的pwm信号,向碳化硅mosfet发送驱动信号,以控制所述碳化硅mosfet的通断;还包括:pwm驱动模块,用于基于接收的pwm信号,向碳化硅mosfet发送驱动信号,以控制所述碳化硅mosfet的通断;还包括:电压变化率控制模块,包括电压变化率控制电路,基于所述碳化硅mosfet的漏源极电压的变化,改变所述电压变化率控制电路的通断状态,以改变所述碳化硅mosfet的漏源极电压变化率;和/或电流变化率控制模块,包括电流变化率控制电路,基于所述碳化硅mosfet的漏极电流的变化,改变所述电流变化率控制电路的通断状态,以改变所述碳化硅mosfet的漏极电流变化率。然而,该现有技术的实现过程较为复杂,需要设计多个监测和控制电路,成本较高,不利于电网系统的经济运行。

技术实现要素:

[0009]

针对现有方法存在的问题,本发明提出了一种抑制碳化硅mosfet电压过冲的栅极电感匹配方法、电路及其应用。此方法可以有效抑制碳化硅mosfet关断漏源极电压过冲,其技术方案如下:

[0010]

抑制碳化硅mosfet电压过冲的栅极电感匹配测试电路,包括直流电容母排、栅极信号源、碳化硅mosfet模块、碳化硅sbd模块;其特征为:所述直流电容母排一端与碳化硅sbd模块阴极端相连,一端通过共源极电感l

s

与碳化硅mosfet模块源极端相连;所述栅极信号源与栅极电阻r

g

、栅极电感l

g

、碳化硅mosfet模块栅极端、碳化硅mosfet源极端、共源极电感串联l

s

依次串联;所述碳化硅mosfet模块漏极端通过漏极电感与碳化硅sbd模块阳极相连;所述碳化硅sbd模块与负载电感l

load

并联;所述碳化硅mosfet模块包括器件电路模型、栅源极电容c

gs

、栅漏极电容c

gd

、漏源极电容c

ds

和体二极管;所述碳化硅sbd模块由肖特基二极管以及二极管的寄生电阻r

f

和寄生电容c

f

构成。

[0011]

本发明还公开一种抑制碳化硅mosfet电压过冲的栅极电感匹配方法,其特征为:包括以下步骤:

[0012]

步骤一:搭建基于碳化硅mosfet的双脉冲测试平台获取碳化硅mosfet的关断特性和二极管的导通特性;

[0013]

步骤二:计算栅极电感理论匹配值:

[0014]

步骤三:计算栅极回路实际设计中所引入的寄生电感:

[0015]

步骤四:计算栅极电感实际设计中所引入的附加电感值,并将相应电感值的电感元器件串联接入栅极回路。

[0016]

本发明还公开一种将抑制碳化硅mosfet电压过冲的栅极电感匹配方法应用于碳化硅mosfet保护电路中。

[0017]

有益效果

[0018]

本发明可以有效抑制碳化硅mosfet在关断过程中产生的漏源极电压过冲,且未引

入高开关损耗等附生问题。

[0019]

本发明操作简便,计算所需电路参数易获得,器件寄生电容可以通过数据手册获得,共源极电感可以通过阻抗分析仪获得,栅极电感可以通过ansys q3d获得。

[0020]

本发明更加实用,成本较低,一般情况下驱动板设计所引入的栅极回路寄生电感要低于栅极电感最优值,故可以直接向栅极回路串联相应电感值的电感元器件来实现本发明提出的方法,不需要额外的电路设计。

[0021]

本发明通过调整碳化硅mosfet栅极回路的寄生电感、附加电感值,对器件关断漏源极电压过冲实现有效抑制,对提高碳化硅mosfet在应用中的经济性和可靠性具有重要意义,有利于保证电力系统的可靠运行。

附图说明

[0022]

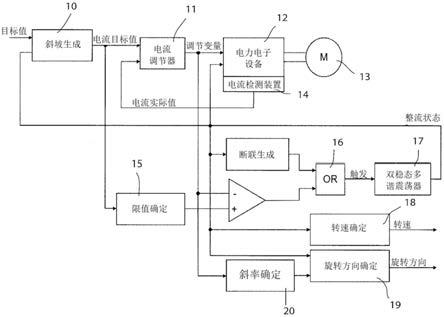

图1双脉冲测试平台电路原理图;

[0023]

图2关断漏源极电压过冲抑制方法流程图;

[0024]

图3不同栅极电感条件下碳化硅mosfet关断漏源极电压波形。

具体实施方式

[0025]

抑制碳化硅mosfet电压过冲的栅极电感匹配测试电路,包括直流电容母排、栅极信号源、碳化硅mosfet模块、碳化硅sbd模块;其特征为:所述直流电容母排一端与碳化硅sbd模块阴极端相连,一端通过共源极电感l

s

与碳化硅mosfet模块源极端相连;所述栅极信号源与栅极电阻r

g

、栅极电感l

g

、碳化硅mosfet模块栅极端、碳化硅mosfet源极端、共源极电感串联l

s

依次串联;所述碳化硅mosfet模块漏极端通过漏极电感与碳化硅sbd模块阳极相连;所述碳化硅sbd模块与负载电感l

load

并联;所述碳化硅mosfet模块包括器件电路模型、栅源极电容c

gs

、栅漏极电容c

gd

、漏源极电容c

ds

和体二极管;所述碳化硅sbd模块由肖特基二极管以及二极管的寄生电阻r

f

和寄生电容c

f

构成。所述栅极驱动测试源输出的栅极驱动测试信号采用一个双脉冲波形,在第一个脉冲结束阶段获得碳化硅mosfet的关断特性和二极管的导通特性,在第二个脉冲开始阶段获得碳化硅mosfet的开通特性和二极管的关断特性。

[0026]

本发明所提出的抑制碳化硅mosfet电压过冲的栅极电感匹配方法,包括以下步骤:

[0027]

步骤一:搭建基于碳化硅mosfet的双脉冲测试平台获取碳化硅mosfet的关断特性和二极管的导通特性;

[0028]

栅极驱动测试信号采用一个双脉冲波形,在第一个脉冲结束阶段获得碳化硅mosfet的关断特性和二极管的导通特性,在第二个脉冲开始阶段获得碳化硅mosfet的开通特性和二极管的关断特性;

[0029]

步骤二:计算栅极电感匹配值:

[0030]

碳化硅mosfet关断过程主要分为关断延时、漏源极电压上升、漏极电流下降和栅源极电压持续下降四个阶段。关断漏源极电压过冲现象发生在漏极电流下降阶段,此阶段栅极回路和功率回路kvl方程可如式(1)和式(2)表示。

[0031][0032][0033]

其中,r

g

和l

g

分别为栅极电阻和栅极电感。l

d

为漏极电感,l

s

为共源极电感,c

gs

、c

gd

、c

ds

分别为器件栅源极电容、栅漏极电容和漏源极电容。r

f

和c

f

为续流二极管寄生电阻与寄生电容。l

load

为负载电感。—v

gl

为驱动负压,v

dc

为母线电压。

[0034]

漏极电流i

d

和栅极电流i

g

可由式(3)和式(4)求得。

[0035][0036][0037]

其中,g

fs

为跨导,v

th

为阈值电压。

[0038]

联立式(1)—(4),并简化栅源极电压变化率可得漏源极电压过冲表达式(5),其中各参数如式(6)所示。

[0039][0040][0041][0042]

当a<0时,

[0043]

当a>0时,

[0044]

可以得出,当a=0即时,δv

ds

取到极小值,电压过冲最小。

[0045]

由式(5)可以得出当栅极电感满足电压过冲最小,此时栅极电感值

即为匹配计算值;其中,漏源极电容c

ds

、栅漏极电容c

gd

、共源极电感l

s

。

[0046]

由于碳化硅mosfet的漏源极电容c

ds

、栅漏极电容c

gd

在开关过程中是随阻断电压的变化而变化的,结合器件的数据手册中器件内部电容的变化曲线,计算所需参数为漏源极电容c

ds

、栅漏极电容c

gd

的最小值;

[0047]

共源极电感l通过阻抗分析仪进行提取。将阻抗分析仪测量端子分别连接器件源极与共源极汇流点,阻抗分析仪测量完毕后,通过内置的等效电路计算功能,直接得到共源极电感l

s

。阻抗分析仪的测量方法为自动平衡电桥法,在考虑测量精度和操作便携性时,是110mhz频率下的最佳选择方案。

[0048]

步骤三:提取栅极回路设计所引入的寄生电感:

[0049]

由于栅极回路分为多段且不便于连接阻抗分析仪的测量端子,采用仿真数值计算法将栅极回路pcb设计图导入ansys q3d软件中,将栅极回路电流路径划分为多个路径段,分别为电源模块至驱动芯片段、驱动芯片至驱动电阻段、驱动电阻至器件栅极段、器件共源极汇流点至驱动芯片段、驱动芯片至电源模块段。其中,电源模块至驱动芯片段和驱动芯片至电源模块段又可分为开通栅极电流段和关断栅极电流段。构建栅极回路每个路径段的rlc电路等效模型,提取其自寄生电感值与相互之间的互寄生电感值,将关断栅极电流路径每一段的电感值相加即可得到栅极回路原寄生电感值。

[0050]

步骤四:计算栅极电感附加电感值,并将相应电感值的电感元器件串联接入栅极回路。

[0051]

由于步骤二所述计算得到的栅极电感最佳匹配值为栅极回路总寄生电感值,而栅极回路在设计中会引入寄生电感,影响实际应用中最佳匹配值的设置。通过步骤三可以提取栅极回路设计所引入的寄生电感,将栅极电感最佳匹配值减去栅极回路设计所引入的寄生电感值,得到栅极电感附加电感值,最后将与附加电感值相近的电感元器件串联接入栅极回路。

[0052]

具实施例1

[0053]

以某1200v/36a碳化硅mosfet为例

[0054]

步骤一:搭建双脉冲测试平台,母线电压v

dc

为500v,栅极电阻r

g

取10ω。

[0055]

步骤二:计算栅极电感匹配值,

[0056][0057]

[0058][0059]

由式(5)

‑

(6)可以看出,因式a的大小由栅极电感l

g

、共源极电感l

s

、栅极电阻r

g

、栅漏极电容c

gd

、漏源极电容c

ds

共同决定。由式(7)得出电压过冲δv

ds

在a=0时取得极小值。由于碳化硅mosfet的漏源极电容c

ds

、栅漏极电容c

gd

在开关过程中是随阻断电压的变化而变化的,结合器件的数据手册中器件内部电容的变化曲线,可以得到漏源极电容c

ds

、栅漏极电容c

gd

的最小值作为计算所需参数,分别为77pf和7.6pf。由此可以得出,要使得电压过冲达到极小值,需要调整栅极电感和共源极电感的电感值以达到匹配。对于既定的功率回路设计来说,共源极电感是固定不变的,通过agilent 4294a阻抗分析仪对功率回路共源极电感l

s

进行测量,将阻抗分析仪测量端子分别连接器件源极与共源极汇流点,阻抗分析仪测量完毕后,通过内置的等效电路计算功能,可以直接得到共源极电感l

s

为10nh。故可以通过调整栅极电感实现匹配。通过公式计算栅极电感匹配值为101nh。

[0060]

步骤三:将栅极回路pcb设计图导入ansys q3d软件中,分段进行计算,获得栅极回路每段的rlc电路等效模型,最后将关断栅极电流路径每一段的电感值相加得到栅极回路原寄生电感值为13nh。

[0061]

步骤四:选取较为接近的电感值92nh的电感元器件串联接入栅极回路,此时栅极回路总寄生电感约为105nh。同时,选取电感值为8nh和150nh的电感元器件串联接入栅极回路(栅极回路总寄生电感分别约为21nh和163nh)作为对比。

[0062]

实验结果如图3所示。当选取匹配计算所得电感值时,碳化硅mosfet关断漏源极电压过冲的峰值达到最小值,实现了较好的抑制效果。

[0063]

本发明相对现有技术存在如下优势:

[0064]

(1)本发明提出的基于栅极电感匹配机制的碳化硅mosfet关断漏源极电压过冲抑制方法具有有效性且无附生问题。应用本发明提出的漏源极电压过冲抑制方法时,只需要改变碳化硅mosfet栅极回路的寄生电感,在有效抑制碳化硅mosfet关断漏源极电压过冲的同时,未引入高开关损耗等附生问题。

[0065]

(2)本发明提出的基于栅极电感匹配机制的碳化硅mosfet关断漏源极电压过冲抑制方法具有更强的实用性。应用本发明提出的方法时,栅极电感最优值可以通过提取器件漏源极电容、栅漏极电容以及功率回路共源极电感计算得出,一般情况下驱动板设计所引入的栅极回路寄生电感要低于栅极电感最优值,故可以直接向栅极回路串联相应电感值的电感元器件。应用本发明所提出的方法,操作简便且成本较低。

[0066]

(3)本发明提出的基于栅极电感匹配机制的碳化硅mosfet关断漏源极电压过冲抑制方法具有更高的准确性。本发明所提出的方法,在控制电路其他寄生参数的前提下,充分考虑了不同栅极电感影响下的碳化硅mosfet漏源极电压过冲变化,并进行了实验验证。

[0067]

(4)本发明提出的基于栅极电感匹配机制的碳化硅mosfet关断漏源极电压过冲抑制方法具有更广泛的适用性。此方法可应用于不同型号的三端功率器件和不同的功率回路布局。

[0068]

以上显示和描述了本发明的基本原理、主要特征和本发明的优点。本行业的技术人员应该了解,本发明不受上述实施例的限制,上述实施例和说明书中描述的只是本发明

的原理,在不脱离本发明精神和范围的前提下本发明还会有各种变化和改进,这些变化和改进都落入要求保护的本发明的范围内。本发明要求的保护范围由所附的权利要求书及其等同物界定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。