1.本技术通常涉及功率控制电路领域。更具体地说,并且不做任何限制,本描述针对用于内部电源生成的功率晶体管栅极电荷采集器。

技术实现要素:

2.一些实施例提供了在栅极放电期间恢复部分功率晶体管栅极电荷的电路,以便生成再循环的逻辑电源电压。该再循环的逻辑电源电压代替输入逻辑电源电压的一部分,该部分由输入电压vin生成;再循环的逻辑电源电压可提高功率电路的整体效率。

3.在一个方面,描述了栅极电荷采集器的实施例。栅极电荷采集器包括:具有第一板和第二板的采集电容器,第二板耦合到下导轨;以及低侧采集晶体管,其具有耦合到低侧功率晶体管的栅极的第一端子和耦合到第一板的第二端子,其中第一板被进一步耦合以向调节器发送电压。

4.在另一方面,描述了集成功率电路的实施例。集成功率电路包括:低侧功率晶体管和高侧功率晶体管,它们串联耦合在第一管脚和第二管脚之间;栅极驱动器,其被耦合以向低侧功率晶体管的栅极提供低侧栅极控制信号,并且向高侧功率晶体管的栅极提供高侧栅极控制信号;以及栅极电荷采集器,其包括:采集电容器,其具有第一板和第二板,第二板耦合到下导轨;第一n型金属氧化物硅(nmos)采集晶体管,其具有耦合到高侧功率晶体管的栅极的第一端子和耦合到第一板的第二端子;以及第二nmos采集晶体管,其具有耦合到低侧功率晶体管的栅极的第一端子和耦合到第一板的第二端子,其中第一板被进一步耦合以提供采集的电压。

5.在又一方面,描述了集成功率电路的实施例。集成功率电路包括:功率晶体管,其耦合在第一管脚和第二管脚之间;栅极驱动器,其被耦合以向功率晶体管的栅极提供栅极控制信号;以及栅极电荷采集器,其包含:采集电容器,其具有第一板和第二板,第二板耦合到下导轨;以及n型金属氧化物硅(nmos)采集晶体管,其具有耦合到功率晶体管的栅极的第一端子和耦合到第一板的第二端子;其中第一板被进一步耦合以提供采集的电压。

附图说明

6.在附图的图中,说明书的实施例通过示例而非限制的方式示出,在附图中,类似的附图标记指示类似的元件。在本说明书中对“一(an)”或“一个(one)”实施例的不同引用不一定是指同一实施例,并且此类引用可意指至少一个。此外,当结合实施例描述特定特征、结构或特性时,无论是否明确描述,该描述均包括结合其他实施例的这种特征、结构或特性。术语“耦合(couple)”或“耦合(couples)”意指间接或直接电连接,除非有限定,如在可包括无线连接部的“可通信地耦合”中。因此,如果第一设备耦合到第二设备,则该连接可通过直接电连接,或者通过经由其他设备和连接部的间接电连接。

7.附图并入说明书并形成说明书的一部分,以说明说明书的一个或多个示例性实施例。结合所附权利要求并参考附图,在以下详细说明中描述了各种优点和特征,其中:

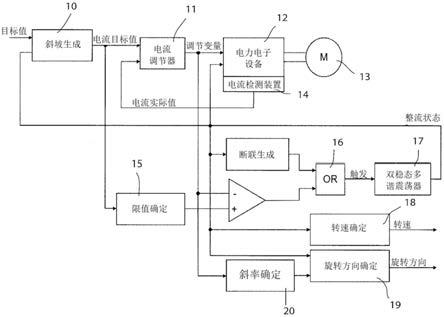

8.图1a描绘了根据实施例的含有栅极电荷采集器的dc/dc升压转换器的示例;

9.图1b描绘了根据实施例的含有栅极电荷采集器的dc/dc升压转换器的示例;

10.图1c描绘了根据实施例的含有栅极电荷采集器的dc/dc升压转换器的示例;

11.图1d描绘了根据实施例的含有栅极电荷采集器的dc/dc降压转换器的示例;

12.图2描绘了根据实施例的图1a的电路操作期间的各种电压电平;

13.图3描绘了根据实施例的dc/dc升压转换器内的各种电路的框图;

14.图4a针对模拟,其比较含有栅极电荷采集器的电路与没有栅极电荷采集器的现有技术电路中增加的逻辑电平电流负载上avdd电源电流生成的效率;

15.图4b描绘了图5的现有技术电路和图1a的电路在输出电流iout范围内的效率计算;

16.图4c描绘了由栅极电荷采集器提供的效率提高;

17.图5描绘了根据现有技术的dc/dc升压转换器内的各种电路的框图;

18.图6描绘了根据现有技术的dc/dc升压转换器的示例;以及

19.图7描绘了在图6的电路操作期间的各种电压电平。

具体实施方式

20.现在将参考附图详细描述本发明的具体实施例。为了提供对本发明更彻底的理解,阐述了许多具体细节。然而,本发明可在没有这些具体细节的情况下实施。在其他情况下,未详细描述众所周知的特征,以避免不必要地使描述复杂化。

21.图5描绘了根据现有技术的dc/dc升压转换器500的高级框图。dc/dc升压转换器500描绘输入电压vin,其通过电感器l耦合到开关节点sw。低侧功率晶体管m1与高侧功率晶体管m2串联耦合在下导轨(其可为接地层)和输出电压vout(其示为耦合到输出电容器cout和由输出电阻器rout表示的负载)之间。在所示的实施例中,低侧功率晶体管m1是n型金属氧化物硅(nmos)功率晶体管,而高侧功率晶体管m2是p型金属氧化物硅(pmos)功率晶体管,尽管这些不是限制。低侧功率晶体管m1的栅极被耦合以接收低侧栅极控制信号ls_gate,而高侧功率晶体管m2被耦合以接收高侧栅极控制信号hs_gate,这两种控制信号均由升压栅极驱动器502提供。升压栅极驱动器502从升压控制电路505接收控制信号。操作升压控制电路505和升压栅极驱动器502的功率由内部低压差(ldo)调节器508提供,该调节器负责从输入电压生成栅极驱动器电源电压vmax(本图中未具体示出)和逻辑电源电压avdd两者。内部ldo调节器508还可向其他控制电路和任何附加电路,诸如监控电路(未具体示出)提供逻辑电源电压avdd。栅极驱动器电源电压vmax是输入电压vin和输出电压vout中较大的一个。为了操作dc/dc升压转换器500,内部ldo调节器508有时可汲取大电流,因此期望提高系统效率。该描述旨在通过在低侧功率晶体管m1和高侧功率晶体管m2上采集一部分栅极电荷以提供一部分逻辑电源电压avdd来减少该问题。栅极电荷以其他方式路由至接地层,并且在每次栅极放电时丢失。为了更好地理解如何采集该栅极电荷,我们首先更仔细地观察升压栅极驱动器502。

22.图6描绘了根据现有技术的dc/dc升压转换器600的稍微更详细的示例。dc/dc升压转换器600再次包括串联耦合在下导轨和提供输出电压vout的输出节点之间的低侧功率晶体管m1和高侧功率晶体管m2。低侧功率晶体管m1和高侧功率晶体管m2之间的开关节点sw通

过电感器l耦合到输入电压vin。输出晶体管cout耦合在输出电压vout和下导轨之间;输出电阻器rout表示输出端上的负载。

23.栅极驱动器602是升压栅极驱动器502的示例实施例。栅极驱动器602耦合到低侧功率晶体管m1的栅极和高侧功率晶体管m2的栅极,并且包括四个栅极控制晶体管。第一p型栅极控制晶体管m3与第一n型栅极控制晶体管m4串联耦合在栅极驱动器电源电压vmax和下导轨之间,其中第一p型栅极控制晶体管m3和第一n型栅极控制晶体管m4之间的节点提供低侧栅极控制信号ls_gate。类似地,第二p型栅极控制晶体管m5与第二n型栅极控制晶体管m6串联耦合在栅极驱动器电源电压vmax和下导轨之间,其中第二p型栅极控制晶体管m5和第二n型栅极控制晶体管m6之间的节点提供高侧栅极控制信号hs_gate。逻辑电路604接收由前述电压控制和/或电流控制提供的一个或多个升压控制信号。逻辑电路604分别向栅极控制晶体管m3、m4、m5、m6的栅极提供四个中间控制信号:低侧

‑

p控制信号ls_p、低侧

‑

n控制信号ls_n、高侧

‑

p控制信号hs_p和高侧

‑

n控制信号hs_n。

24.图7描绘了与驱动低侧功率晶体管m1和高侧功率晶体管m2中的一个有关的时序。图7含有两个曲线图700a、700b。曲线图700a描绘了功率晶体管栅极上的电压。尽管低侧功率晶体管m1(其为nmos)由栅极变高而导通,并且高侧功率晶体管m2(其为pmos)由栅极变高而关断,但这两个功率晶体管的栅极以相同的方式驱动。由于类似的栅极驱动方法,仅给出一个示例波形,其中名称ls_gate和hs_gate由功率栅极控制信号xx_gate代替,以指示所示电压可指高侧栅极控制信号hs_gate或低侧栅极控制信号ls_gate。曲线图700b描绘了驱动曲线图700a中所示的功率栅极控制信号xx_gate的栅极驱动器602的各个栅极控制晶体管上的电压。类似于上图,名称ls_p和hs_p由中间

‑

p控制信号xx_p代替,以指示电压可指低侧

‑

p控制信号ls_p或高侧

‑

p控制信号hs_p上的电压,并且名称ls_n和hs_n由中间

‑

n控制信号xx_n代替,以指示电压可指低侧

‑

n控制信号ls_n或高侧

‑

n控制信号hs_n上的电压。

25.中间

‑

p控制信号xx_p和中间

‑

n控制信号xx_n之间的栅极驱动器不重叠是避免交叉传导所必要的。这种不重叠被显示并标记为p

‑

死区时间tdead,p和n

‑

死区时间tdead,n,它们均得到了很好的控制。在p

‑

死区时间tdead,p和n

‑

死区时间tdead,n两者期间,功率栅极控制信号xx_gate均是高阻抗的。中间

‑

p控制信号xx_p和中间

‑

n控制信号xx_n在围绕p

‑

死区时间tdead,p的区域中的转换被分成六个时间段,由圈起的数字1

‑

6表示。为了便于区分时间段,p

‑

死区时间tdead,p和n

‑

死区时间tdead,n由长虚线描画,而其他时间段由较短虚线描画。

26.在时间段(1)期间,中间

‑

n控制信号xx_n和中间

‑

p控制信号xx_p均耦合到地。中间

‑

p控制信号xx_p使得对应的p型栅极控制晶体管(第一p型栅极控制晶体管m3或第二p型栅极控制晶体管m5)导通电流,并且中间

‑

n控制信号xx_n使得对应的n型栅极控制晶体管(第一n型栅极控制晶体管m4或第二n型栅极控制晶体管m6)关断。这导致对应的功率栅极控制信号xx_gate为高电位,高电位在图6中为栅极驱动器电源电压vmax的值。在时间段(2)期间,中间

‑

n控制信号xx_n保持关断,并且中间

‑

p控制信号xx_p上升。在p

‑

死区时间tdead,p(其也是时间段(3))期间,与中间

‑

n控制信号xx_n和中间

‑

p控制信号xx_p相关联的两个栅极控制晶体管均处于关断状态,并且功率栅极控制信号xx_gate是高阻抗的。这个出现在中间

‑

p控制信号xx_p上升之后和中间

‑

n控制信号xx_n上升之前的p死区时间tdead,p用于避免栅极驱动器电源电压vmax和接地层之间的潜在交叉电流,并且还用于提高效率。在时间

段(4)期间,p

‑

死区时间tdead,p已结束,并且中间

‑

n控制信号xx_n上的电压上升到栅极驱动器电源电压vmax。中间

‑

n控制信号xx_n上的增加电压开始将功率栅极控制信号xx_gate上的电压拉至接地。在时间段(5)期间,功率栅极控制信号xx_gate的动态转换随着功率栅极控制信号xx_gate处于低电位而结束。在持续直到中间

‑

p控制信号xx_p接地的时间段(6)期间,反向操作关断中间

‑

n控制信号xx_n和中间

‑

p控制信号xx_p,这将使得功率栅极控制信号xx_gate再次充电至高电位。

27.图1a描绘了根据实施例的含在集成电路芯片101a中并含有栅极电荷采集器106a的dc/dc升压转换器100a的示例。dc/dc升压转换器100a含有串联耦合在第一管脚p1和第二管脚p2之间的低侧功率晶体管m1和高侧功率晶体管m2,其中开关节点sw耦合到第三管脚。在dc/dc升压转换器100a的操作期间,第一管脚p1耦合到接地层,第二管脚p2耦合到输出电容器cout和由电阻器rout表示的负载,并且第三管脚p3耦合到电感器l并通过电感器l耦合到输入电压vin。为了简单且不失一般性,假设低侧功率晶体管m1和高侧功率晶体管m2的栅极既在低侧功率晶体管m1的情况下承受栅极驱动器电源电压vmax,又在高侧功率晶体管m2的情况下承受接地层,从而不违反最大允许栅极/源极或栅极/体电位。在其他实施例中(未具体示出),低侧栅极控制信号ls_gate的高电位和高侧栅极控制信号hs_gate的低电位被箝位到安全电位,使得低侧功率晶体管m1和高侧功率晶体管m2的栅极是安全的。

28.低侧功率晶体管m1和高侧功率晶体管m2被反相位启用,使得dc/dc升压转换器100a以连续操作操作,以对电感器l进行充电和放电,用于向输出电容器cout的能量传输。低侧功率晶体管m1和高侧功率晶体管m2的栅极的导通和关断表现出特征性的非重叠行为,以避免交叉传导。这种不重叠由逻辑电路104提供的适当的栅极驱动拓扑来保证,以通过栅极驱动器102控制低侧栅极控制信号ls_gate和高侧栅极控制信号hs_gate。低侧

‑

p控制信号ls_p和低侧

‑

n控制信号ls_n之间以及高侧

‑

p控制信号hs_p和高侧

‑

n控制信号hs_n之间类似的栅极驱动不重叠可用来避免栅极驱动器交叉传导。这种方法在高功率和/或高效率系统中或者在峰值效率和/或轻负载效率至关重要的系统中可能特别重要,其中低侧功率晶体管m1和高侧功率晶体管m2很大,并且还需要不可忽略的栅极驱动电路。

29.栅极驱动器102含有第一p型栅极控制晶体管m3和第一n型栅极控制晶体管m4以及第二p型栅极控制晶体管m5和第二n型栅极控制晶体管m6,晶体管m3和晶体管m4串联耦合在栅极驱动器电源电压vmax和下导轨之间,以提供低侧栅极控制信号ls_gate,,晶体管m5和晶体管m6串联耦合在栅极驱动器电源电压vmax和下导轨之间,以提供高侧栅极控制信号hs_gate。栅极驱动器102从逻辑电路104接收低侧

‑

p控制信号ls_p、低侧

‑

n控制信号ls_n、高侧

‑

p控制信号hs_p和高侧

‑

n控制信号hs_n,逻辑电路104本身接收升压控制信号作为输入。

30.栅极电荷采集器106a含有两个控制栅极电荷采集的晶体管和一个可临时存储采集的栅极电荷的电容器。低侧采集晶体管mharvls耦合在低侧栅极控制信号ls_gate和采集电容器charv的第一板之间,并且高侧采集晶体管mharvhs耦合在高侧栅极控制信号hs_gate和采集电容器charv的第一板之间。在本技术中给出的示例中的每一个中,低侧采集晶体管mharvls和高侧采集晶体管mharvhs为简单起见被示为nmos晶体管,尽管可使用任何类型的晶体管。采集栅极控制信号gharv控制低侧采集晶体管mharvls和高侧采集晶体管mharvhs的时序。采集电容器charv的第二板耦合到下导轨。如下所示,采集的电压vpre是未

调节的电压,其小于栅极驱动器电源电压vmax且大于逻辑电源电压avdd。采集的电压vpre也会随时间发生很大变化,不适合用作电源电压。因此,采集的电压vpre被提供给采集调节器108,采集调节器108可调节采集的电压vpre以在avdd电容器cavdd上生成再循环逻辑电源电压avddrecyl,从而为电阻器负载ravdd供电。采集调节器108可为简单的ldo调节器或任何其他电路,其从不受控的采集的电压vpre生成具有受控电压的再循环逻辑电源电压avddrecyl。参考图2描述栅极电荷采集器106a的操作如何与栅极驱动器102的操作相适应。

31.图2类似于图7,但描述了由栅极电荷采集器106a带来的差异。曲线图200a再次描绘了功率栅极控制信号xx_gate上的电荷,其中功率栅极控制信号202描绘了当没有电荷采集时的电荷损失,并且功率栅极控制信号204描绘了当采集电荷时的电荷损失。还示出了采集的电压vpre 206和再循环的逻辑电源电压avddrecyl。曲线图200b再次描绘了中间

‑

n控制信号xx_n和中间

‑

p控制信号xx_p,并且还描绘了采集栅极控制信号gharv。

32.中间

‑

p控制信号xx_p和中间

‑

n控制信号xx_n在时间段tdead,p期间的转换再次分为六个部分,其再次由圈起的数字1

‑

6表示。在时间段(1)期间,中间

‑

n控制信号xx_n和中间

‑

p控制信号xx_p两者均连接到接地层。中间

‑

p控制信号xx_p上的低值使得第一p型栅极控制晶体管m3和第二p型栅极控制晶体管m5中相应的一个导通电流。中间

‑

n控制信号xx_n上的低值使得第一n型栅极控制晶体管m4和第二n型栅极控制晶体管m6中的相应一个关断。功率栅极控制信号xx_gate为高电位,在本例中,高电位的值等于栅极驱动器电源电压vmax。在时间段(2),中间

‑

n控制信号xx_n保持低电位,并且中间

‑

p控制信号xx_p上升到高电位。在p

‑

死区时间tdead,p(其也是时间段(3))的开始时,中间

‑

n控制信号xx_n将n型栅极控制晶体管m4、m6中的各自一个保持在关断状态,并且中间

‑

p控制信号xx_p将p型栅极控制晶体管m3、m5中的各自一个保持在关断状态。

33.一旦中间控制晶体管xx_n和xx_p两者在时间段(3)内保持各自的栅极控制晶体管关断,采集栅极控制信号gharv被拉至高电位,使得相应的栅极/源极电压vgs,harv现在大于采集的电压vpre加上采集晶体管的阈值电压vth,并且低侧采集晶体管mharvls和高侧采集晶体管mharvhs被启用。代替如由功率栅极控制信号202中的旧波形所指示的具有浮动电位的功率栅极控制信号xx_gate,功率栅极控制信号204现在减少如由波形所指示的采集电流。然后,采集的电压vpre 206增加到接近功率栅极控制信号xx_栅极204的值,并且跟随栅极电位直到p

‑

死区时间tdead,p的结束。

34.在时间段(4)期间,中间

‑

n控制信号xx_n上升至高电位,并且开始将功率栅极控制信号xx_gate拉至低电位。同时,采集栅极控制信号gharv被拉至低电位,以停止采集。功率栅极控制信号204现在进一步放电到低电位,并且由于功率栅极控制信号204的采样,采集电容器charv上的采集的电压vpre处于高值。在时间段(5)和(6)期间,栅极切换没有从较旧的切换模式改变。从非受控采集的电压vpre 206,诸如采集调节器108的后调节器进一步将存储在采集电容器charv上的电荷降频转换为逻辑电源电压avddrecyl,该逻辑电源电压avddrecyl可存储在逻辑电平电容器cavdd上并提供给电阻器负载ravdd。

35.考虑到还需要在低侧功率晶体管m1和高侧功率晶体管m2之间提供死区时间,尽管为了简单起见,图1a描绘了单个采集栅极控制信号gharv,但是低侧采集栅极控制信号gharvls和高侧采集栅极控制信号gharvhs可用于分别控制来自功率晶体管的栅极采集的时序,如将在其他示例中示出的。

36.图3描绘了根据实施例的dc/dc升压转换器300的高级框图。该图中对输入逻辑电源电压avddin、再循环逻辑电源电压avddrecyl和包括avddin和avddrecl两者的多路复用逻辑电源电压avddmux之间进行区分。先前看到的内部ldo调节器308向升压控制电路305和升压栅极驱动器302提供电源导轨,现在由栅极电荷采集器306和判定电路310支持提供电源导轨。栅极电荷采集器306被耦合以在低侧功率晶体管m1和高侧功率晶体管m2上存在切换活动的任何时候采集低侧功率晶体管m1和高侧功率晶体管m2上的一部分栅极电荷。在调节采集的电压vpre之后,结果被提供给判定电路310作为再循环的逻辑电源电压avddrecyl。判定电路310多路复用来自内部ldo调节器308的输入逻辑电源电压avddin和来自栅极电荷采集器306的再循环的逻辑电源电压avddrecyl,以提供多路复用的逻辑电源电压avddmux。因为在dc/dc升压转换器300的操作期间可存在低侧功率晶体管m1和高侧功率晶体管m2不切换的时间段,所以判定电路310必须保证再循环逻辑电源电压avddrecyl的使用不干扰关键的切换操作。在一个实施例中,判定电路310利用再循环的逻辑电源电压avddrecyl仅向升压转换器的非切换关键的部分供电。在一个实施例中,一旦低侧功率晶体管m1和高侧功率晶体管m2的切换开始或停止,并且再循环的逻辑电源电压avddrecyl建立或崩溃,判定电路310就确保输入逻辑电源电压avddin和再循环的逻辑电源电压avddrecyl的适当复用。

37.图4a针对模拟,其比较含有栅极电荷采集器的电路与没有栅极电荷采集器的现有技术电路中增加的逻辑电平电流负载上avdd电源电流生成的效率。首先模拟了电流负载i_avdd增加水平下的电流消耗,表1示出了现有技术电路的结果,并且表2提供了具有栅极电荷采集器的电路的结果。

38.表1没有栅极电荷采集器

39.i_avddi_sumi_vmaxi_vini_harv01.334ma1.33ma4.5ua020ua1.354ma1.33ma24.5ua040ua1.374ma1.33ma44.4ua060ua1.393ma1.33ma64.3ua080ua1.413ma1.33ma84.2ua0100ua1.433ma1.33ma104ua0

40.在这些表中,i_avdd是电流负载,i_vmax是为提供栅极驱动器电源电压而生成的电流,i_vin是为提供逻辑电源电压而生成的电流,i_sum是生成的电流之和(i_vmax i_vin),并且i_harv是栅极电荷采集器采集的电流。在表1中,未采集任何栅极电荷,并且采集的电流i_harv对于电流负载i_avdd的所有值均为零。随着电流负载i_avdd值的增加,作为i_max汲取的栅极电流保持不变,但是为提供逻辑电源电压而生成的电流i_vin增加,因此i_sum也随着电流负载i_avdd的增加而增加。

41.表2具有栅极电荷采集器

42.i_avddi_sumi_vmaxi_vini_harv01.33ma1.33ma0020ua1.33ma1.33ma024.5ua40ua1.33ma1.33ma044.4ua

60ua1.33ma1.33ma064.3ua80ua1.33ma1.33ma084.2ua100ua1.33ma1.33ma0104ua

43.在表2中,栅极电荷采集器提供逻辑电源电压,因此无需为此目的生成电流i_vin。由于为提供栅极驱动器电源电压i_vmax而生成的电流是恒定的,因此i_sum的值也是恒定的。基于以上两个表中所示的生成的电流之和i_sum的值,在输入电压vin等于3.8v、输出电压vout等于4.6v且输出电流iout等于10ma的情况下进行效率计算。结果在下面的表3和图4a中示出,其描述了现有技术电路的效率随着电流负载i_avdd的增加而线性降低,同时电路的效率在电流负载i_avdd的值之间保持恒定。

44.表3效率提高

[0045][0046]

图4b描绘了图5的现有技术电路和图1a的电路在输出电流iout范围内的效率计算。在图4b中,两个电路的效率随着输出电流iout的增加而增加。在最低输出电流iout值为1.00e

‑

03时,使用栅极电荷采集器提供微小但明显的改进,而在最高输出电流iout值为1.00e

‑

01时,效率实际上是相同的。在图4c中更清楚地量化了相对于现有技术的效率提高。在该曲线中,可看出,栅极电荷采集器在最低输出电流iout为1.00e

‑

3时的效率提高约1.44%,而在最高输出电流iout为1.00e

‑

1时的效率提高约0.08%。

[0047]

还执行了模拟,以确定采集的电压vpre和再循环的逻辑电源电压avddrecyl的斜坡时间。采集的电压vpre上升的速率取决于采集晶体管mharvls和mharvhs的大小,而再循环的逻辑电源电压avddrecyl上升的速率取决于调节器108的带宽。在输入电压vin为3.8v且输出电压vout为4.6v的情况下执行模拟。在一个实施例中,采集的电压vpre在约10μs内斜坡上升至约4.5v的平均电压,而再循环的逻辑电源电压avddrecyl在约60μs内斜坡上升至约1.8v的值。

[0048]

尽管栅极电荷采集器106a已被描述为具有用于高侧功率晶体管m2的pmos功率晶体管的dc/dc升压转换器100a的一部分,但是栅极电荷采集器可用于其他电路中。图1b描绘了根据实施例的实施在ic芯片101b上并含有栅极电荷采集器106b的dc/dc升压转换器100b。dc/dc升压转换器100b在大多数方面类似于dc/dc升压转换器100a,但在几个重要方面有所不同。为了避免重复,相似之处不再重复,只注重不同之处。在dc/dc升压转换器100b中,没有为高侧功率晶体管m2配备pmos功率晶体管,而是利用了nmos功率晶体管来配备。众所周知,自举栅极驱动器(未具体示出)向高侧驱动器电路提供自举电压vboot。此外,尽管

栅极电荷采集器106a中示出了单个采集栅极控制信号gharv,但是栅极电荷采集器106b含有两个单独的栅极控制信号。高侧采集栅极控制信号gharvhs提供给高侧采集晶体管mharvhs,并且低侧采集栅极控制信号gharvls提供给低侧采集晶体管mharvls。在至少一个实施例中,在第一p型栅极控制晶体管m3和第一n型栅极控制晶体管m4两者的第一死区时间期间,低侧采集栅极控制信号gharvls被耦合为高,第一死区时间发生在第一p型栅极控制晶体管m3已经关断且n型栅极控制晶体管m4尚未导通时。类似地,在第二p型栅极控制晶体管m5和第二n型栅极控制晶体管m6两者的第二死区时间期间,高侧采集栅极控制信号gharvhs被耦合为高,第二死区时间发生在第二p型栅极控制晶体管m5已经关断且第二n型栅极控制晶体管m6尚未导通时。

[0049]

图1c描绘了dc/dc升压转换器100c,其实施在ic芯片101c上,并且含有在第一管脚p1和第二管脚p2之间与二极管d1串联耦合的低侧功率晶体管m1。开关节点sw位于低侧功率晶体管m1和二极管d1之间。在dc/dc升压转换器100c的操作期间,第一管脚p1耦合到接地层,管脚p2耦合到输出电容器cout以向由电阻器rout表示的负载提供输出电压vout。因为在该应用中仅使用单个功率晶体管,所以栅极驱动器102c仅含有与栅极驱动器电源电压vmax和下导轨之间的第一n型栅极控制晶体管串联耦合的第一p型栅极控制晶体管,并且从逻辑电路104接收低侧

‑

p控制信号ls_p和高侧

‑

n控制信号ls_n。栅极电荷采集器106c包括低侧采集晶体管mharvls,其耦合在低侧功率晶体管m1的栅极和采集电容器charv的第一板之间。

[0050]

图1d描绘了根据实施例的实施在ic芯片101d上并含有栅极电荷采集器106d的dc/dc降压转换器100d的高级框图。对于dc/dc降压转换器100d,低侧功率晶体管m1与高侧功率晶体管m2串联耦合在第一管脚p1和第二管脚p2之间。低侧功率晶体管m1和高侧功率晶体管m2之间的节点耦合到第三管脚p3。在dc/dc降压转换器100d的操作期间,管脚p1耦合到接地层,管脚p2耦合到输入电压vin,并且管脚p3被耦合以提供输出电压vout。栅极驱动器102再次被耦合以向低侧功率晶体管m1的栅极提供低侧栅极控制信号ls_gate,并且向高侧功率晶体管m2的栅极提供高侧栅极控制信号hs_gate。栅极电荷采集器106d以类似于先前描述的栅极电荷采集器106a、106b的方式操作。在所示的实施例中,高侧功率晶体管m2是pmos功率晶体管,并且低侧功率晶体管m1是nmos功率晶体管。然而,高侧功率晶体管m2和低侧功率晶体管m1两者均可为nmos功率晶体管。在一个实施例中,高侧功率晶体管m2可由二极管代替,如图1c所示。

[0051]

栅极电荷采集器从一个或多个功率晶体管中采集当前在功率晶体管的栅极放电时被浪费的一部分栅极电荷。栅极电荷采集器对于每个功率晶体管只需要一个相应的采集晶体管,其中采集控制信号提供电荷采集的适当时序和在其上存储采集的电荷的采集电容器。采集过程提供不受控的采集的电荷,然后可将其发送到调节器,该调节器将采集的电荷降频转换为具有恒定电压的逻辑电源电压。用于导通和关断功率晶体管的栅极电荷最初从输入电压vin或输出电压vout汲取,在一些实施例中,其本身可通过升频转换从输入电压vin获得。栅极电荷采集可允许这些电荷中的一些被再循环和降频转换,以提供低于功率栅极电压的逻辑电平电压。通过接管部分内部逻辑电源的生成,提高了ic芯片的整体效率。

[0052]

权利要求不限于任何特定实施例或示例,并且没有任何特定部件、元件、步骤、动作或功能是必要的,因此必须将其包括在权利要求的范围内。除非明确说明,否则以单数形

式提及的元件并不意指“一个且仅一个”,而是“一个或多个”。该描述包括上述元件的所有结构和功能等同物,并且这些等同物涵盖在权利要求中。因此,在下面所附权利要求的精神和范围内,可通过各种修改和变更来实践本文所描述的示例性实施例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。