1.本公开涉及一种用于制造碳化硅(sic)器件的方法。

背景技术:

2.sic是一种新兴的半导体材料,其良好地适合于功率电子设备和需要承受恶劣环境条件的电子设备。sic是与硅(si)实质上不同的半导体材料。从器件制造的角度看,sic和si之间的关键区别在于掺杂剂在这些材料中的扩散。直到温度超过大约1800摄氏度时,掺杂剂才开始在sic中大量扩散;相比之下,当温度超过大约750摄氏度时,掺杂剂开始在si中扩散。

技术实现要素:

3.本公开提供了一种利用扩散系数在sic与si之间的大差异来制造碳化硅器件的方法,如所附权利要求所述。

附图说明

4.现在将参照附图仅以举例的方式描述本发明的实施方案,其中:

5.图1示出了待填充和平面化(planarization,平坦化)的表面形貌的总体形状;

6.图2示出了在回流之前在可回流的电介质的第一次沉积之后的表面状态;

7.图3示出了第一层可回流的电介质的退火/回流之后的表面状态;

8.图4示出了可回流的电介质的第二次沉积之后的表面状态;

9.图5示出了沉积的可回流的电介质的堆叠体的第二次退火/回流之后的表面状态;

10.图6示出了所述方法中的步骤;

11.图7示出了所述方法中的步骤,还结合了重复沉积和加热可回流的电介质的步骤;

12.图8示出了在bpsg(4重量%硼、4重量%磷)沉积和在950℃回流30分钟的两次循环后的半导体结构体的横截面图像;

13.图9示出了包括待填充和平面化的导电膜的表面形貌的总体形状的示意性横截面图;

14.图10示出了在具有形貌特征的层的顶部上可回流的电介质的第一次沉积之后的表面状态;

15.图11示出了将可回流的电介质的第一沉积层退火/回流之后的表面状态;

16.图12示出了可回流的电介质的第二次沉积之后的表面状态;

17.图13示出了可回流的电介质的一个或多个沉积层的第二次退火/回流之后的表面状态;

18.图14示出了包括待填充和平面化的介电膜的表面形貌的总体形状的示意性横截面图;

19.图15示出了在具有形貌特征的层的顶部上可回流的电介质的第一次沉积之后的

表面状态;

20.图16示出了将可回流的电介质的第一沉积层退火/回流之后的表面状态;

21.图17示出了可回流的电介质的第二次沉积之后的表面状态;以及

22.图18示出了可回流的电介质的一个或多个沉积层的第二次退火/回流之后的表面状态。

具体实施方式

23.如上所述,si和sic中各种掺杂剂的扩散系数的差异(即掺杂剂扩散的不同温度)使得在sic器件的制造中可以采用平面化和填充工艺,而在si器件的制造中无法采用该工艺。

24.本文描述了这样的方法,其中通过一个或多个循环,将可回流的介电材料沉积在非平面的表面(例如包括sic衬底中的沟槽)上,并且通过在足以引起回流的温度下将电介质和下面的层退火,可回流的电介质提供了在sic表面的非平面的形貌(topography)上方的平面的表面,这可以得到更可制造的和更高产量的器件。非平面的表面形貌可以由sic构成,或者由在下面的sic衬底上的介电膜和/或导电膜构成。

25.本文描述的实施方案可以解决以下技术问题:用介电材料填充下面的形貌(非平面的表面)而没有空隙(void)或接缝(seam),并且还在非平面的表面上方产生平面的介电层。介电膜的沉积倾向于产生在沉积之后仍然保留的空隙和接缝。因为由空隙和接缝引入膜中的不均匀的蚀刻特性,以及可能导致可靠性问题的空隙俘获水分的倾向,消除这些空隙和接缝是令人感兴趣的。在非平面的表面的顶部上产生平面的表面是令人感兴趣的,因为这对后续图案水平有影响。相对于非平面的表面,平面的表面在光刻期间允许更大的聚焦预算深度(depth of focus budget);这随后允许在光刻期间分辨平面的表面的顶部上的特征(所述特征在非平面的表面上无法分辨)。

26.本公开提供了一种利用扩散系数在sic与si之间的大差异来制造碳化硅器件的方法。通过沉积可回流的介电材料、然后在足以引起回流的温度下使可回流的介电材料退火的一个或多个循环,解决了填充和平面化的技术问题。电介质的回流可以消除空隙和接缝,并且使介电层的表面变成平面的。已经发现在多个循环中重复该过程增强了所述方法的填充和平面化效果。该方法不适用于si器件加工,因为由于扩散该方法将对掺杂剂在si内的分布具有严重影响。

27.本文描述的方法的实施方案的优点在于其能够使用通常用于cmos技术(包括遗留技术节点(legacy technology nodes)(>0.6um))的制造的加工设备容易地实施。实施本发明所需的能力是pecvd沉积工具和加热炉。当前工艺水平的用于填充和平面化的方法是hdpe氧化物沉积,然后进行cmp,这些能力是在用于<0.5um技术节点的制造设施中的。因此,实施方案可以实现无空隙和无接缝填充和平面化的目标,而无需在cmp能力上进行资本投资。

28.引起可回流的电介质回流所需的温度通常超过750摄氏度。因此,本公开的该特征无法容易地应用于si器件的平面化中,因为由于扩散该方法将对掺杂剂在si内的分布具有严重影响。相比之下,本文描述的方法可以用作sic器件制造中的填充和平面化的手段,而不会由于扩散而影响掺杂剂在sic内的分布。

29.所述方法可以包括利用可回流的电介质填充sic中的沟槽或者使功能层(诸如sic外延层、先前的导电层、先前的介电层或先前的磁性层)的顶部上的其他非平面的形貌平面化,然后使可回流的电介质平面化。通过沉积可回流的电介质以及将可回流的介电膜和下面的层在足以引起电介质回流的温度下退火的一个或多个循环,可以实现填充和平面化。可以在第一次可回流的电介质沉积之后,以及然后在每个随后的可回流的电介质沉积之后,施加多次退火,以实现平面化的表面。

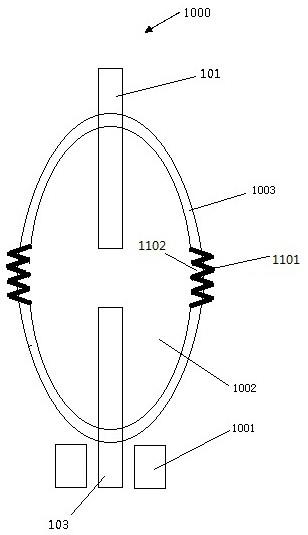

30.图1示出了半导体结构体1的示意性横截面,其包括待填充和平面化的sic 2的层。在本实例中,存在三个待填充的沟槽4。然而,可以存在任何数量的沟槽。表面也可以是任何具有非平面的形貌的表面。

31.如图2所示,可以将可回流的电介质6沉积在sic 2的上表面3上。该图显示了横剖面视图,其示出了在具有非平面的形貌特征的sic 2的层的顶部上可回流的电介质6的第一次沉积之后介电材料6的表面7的状态。

32.可回流的介电材料的实例是硼磷硅酸盐玻璃(bpsg)。该bpsg可以包含4重量%的硼和4重量%的磷。然而,可以使用任何可回流的介电材料,即能够通过流动而形成不同形状的任何介电材料。可以使用任何已知的沉积方法将可回流的介电材料沉积在非平面的表面上,一种已知的方法是通过等离子体增强化学气相沉积(pecvd)来沉积膜。

33.在将可回流的介电材料6沉积在sic 2的表面3上之后,可以在足以引起可回流的介电材料6的回流的温度下加热可回流的介电材料6和下面的层,使得可回流的介电材料6填充sic 2的表面上的任何沟槽4或其他非平面的形貌。

34.图3示出了第一层可回流的电介质6的退火/回流之后表面7的状态。这完成了沉积介电材料6、随后回流介电材料6回流的第一次循环。典型的回流条件的实例将是在950摄氏度下达30分钟以诱导bpsg的回流。然而,退火温度可以为750摄氏度至1350摄氏度之间的任何温度。例如,退火时间可以为1分钟至24小时。

35.如图4所示,然后可以重复沉积介电材料6、随后回流介电材料6的过程。图4示出了可回流的电介质6的第二次沉积之后电介质6的表面7的状态。在完成沉积介电材料6、随后回流介电材料6的第一次循环之后,进行第二次循环。第二次循环包括进一步沉积介电材料6、随后回流介电材料6。对于可以重复的这样的循环的次数没有限制。如图4所示,空隙8可以在介电材料6中形成,随后通过介电材料6的回流将其移除(如图5所示)。

36.图5示出了在沉积介电材料6、随后回流介电材料6的循环之后的表面状态。结果是任何空隙8已经被填充并且电介质6的所得表面7是平面的。

37.图6示出了所述方法中的步骤。这些包括提供非平面的sic表面的步骤(步骤s1)、在所述表面上方沉积可回流的介电材料的步骤(步骤s2)和加热所述可回流的介电材料至足以引起所述可回流的介电材料回流的温度的步骤(步骤s3)。

38.图7示出了所述方法中的步骤,包括重复所述沉积和加热所述可回流的电介质的步骤的另一步骤(步骤s4)。

39.所述方法允许用介电膜6填充下面的形貌,并且在非平面的表面3的顶部上产生平面的介电膜6。由于在沉积介电膜期间有形成空隙和接缝的倾向(其在沉积之后仍然存在),填充具有非平面的形貌的表面中的空间是一个挑战。消除这些空隙和接缝防止了由空隙和接缝引入膜中的不均匀的蚀刻特性的形成,并且还防止可能导致可靠性问题的空隙俘获水

分的倾向。在非平面的表面的顶部上产生平面的表面对后续图案水平影响。相对于非平面的表面,平面的表面在光刻期间允许更大的聚焦预算深度;这随后允许在光刻期间分辨平面的表面的顶部上的特征(所述特征在非平面的表面上无法分辨)。

40.通过沉积可回流的电介质、然后在足以引起回流的温度下使可回流的电介质退火的一个或多个循环,解决了这些技术问题。电介质的回流导致消除了空隙和接缝,并且使电介质的表面变成平面的。已经发现在多个循环中重复该过程增强了该方法的填充和平面化效果。

41.本文所公开的方法的实施方案显著不同于化学机械抛光(cmp)方法。cmp是当前工艺水平的用于在si器件制造中进行平面化的技术。cmp涉及沉积膜以覆盖并填充下面的形貌,随后通过化学和机械方法将膜抛光至平面的状态。

42.本文公开的方法的优点在于其简单性和其能够使用通常用于互补金属氧化物半导体(cmos)技术(包括遗留技术节点)的制造的加工设备容易地实施。实施本发明所需的能力是等离子体增强化学气相沉积(pecvd)沉积工具和加热炉。用于传统cmos技术节点的制造现场通常不具有cmp能力。因此,本方法实现了无空隙和无接缝填充和平面化的目标,而无需在cmp能力上进行资本投资。

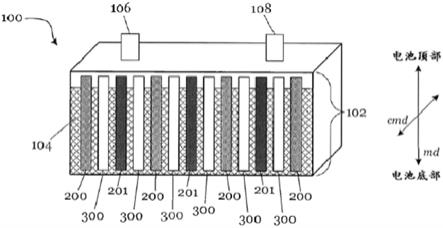

43.图8示出了根据实施方案的sic器件的半导体结构体的扫描电子显微镜(sem)横截面。半导体结构体1可以是图5所示的半导体结构体。相同的附图标记已在不同的图中用于类似或等同的特征以帮助理解,并且不旨在限制所示实施方案。半导体结构体1包括具有非平面的上表面3的sic衬底2,所述非平面的上表面3由sic衬底2中的沟槽4形成。半导体结构体1由bpsg(4重量%硼、4重量%磷)沉积和在950℃回流30分钟的两次循环后形成。

44.图9至13示出了根据另一个实施方案的制造方法中的不同阶段中的半导体结构体1(诸如功率dmos结构)的示意性横截面,其中非平面的表面9包括在具有平面的表面3的sic衬底2上的导电膜10。

45.图9示出了半导体结构体1,其包括具有平面的上表面3的sic衬底2,以及通过绝缘层11与sic衬底隔开的导电膜10。导电膜10是图案化的,并且由此与下面的sic衬底2一起提供了非平面的表面9。

46.图10示出了在非平面的表面9上沉积介电材料6(其为bpsg)之后的半导体结构体1。沉积是保形的,并且所得的介电材料6的层具有非平面的上表面7,其基本上遵循下面的非平面的表面9的形状。

47.图11示出了在引起介电材料6的回流的加热/退火之后的半导体结构体1。由于掺杂剂在sic中的低扩散系数(与si相比),sic器件性能不会显著地降低。

48.图12示出了沉积另外的介电材料6(其为bpsg)之后的半导体结构体1。在介电材料6中形成空隙8。介电材料6的上表面7不是完全平面的,但是位于图案化的导电膜10的上方。

49.图13示出了在引起介电材料6的回流的加热/退火之后的根据实施方案的半导体结构体1。半导体结构体1现在包括介电层12(由介电材料6形成),所述介电层12包括基本上平面的表面7。介电层12基本上不含空隙。

50.图14至18示出了根据不同实施方案的制造方法中的不同阶段中的半导体结构体1的示意性横截面,其中非平面的表面9包括在具有平面的表面3的sic衬底2上的介电膜13。

51.图14示出了半导体结构体1,其包括具有平面的上表面3的sic衬底2,以及直接位

于sic衬底2顶部上的介电膜13。介电膜13是图案化的,并且由此与下面的sic衬底2一起提供了非平面的表面9。

52.图15示出了在非平面的表面9上沉积介电材料6之后的半导体结构体1。沉积是保形的,并且所得的介电材料6的层具有非平面的上表面7,其基本上遵循下面的非平面的表面9的形状。

53.图16示出了在引起介电材料6的回流的加热/退火之后的半导体结构体1。重要的是,介电膜13不是可回流的,并且因此在加热期间保持其形状。由于掺杂剂在sic中的低扩散系数(与si相比),sic器件性能不会显著地降低。

54.图17示出了沉积另外的介电材料6之后的半导体结构体1。在介电材料6中形成空隙8。介电材料6的上表面7不是完全平面的,但是位于图案化的介电膜13的上方。

55.图18示出了在引起介电材料6的回流的第二步加热/退火之后的根据实施方案的半导体结构体1。半导体结构体1现在包括介电层12(由介电材料6形成),所述介电层12包括在非平面的表面9上方的基本上平面的表面7,所述非平面的表面9包括介电膜13和下面的sic衬底2。介电层12基本上不含空隙。

56.大体上,本发明的实施方案提供了一种形成半导体结构体的方法。所述方法包括在碳化硅(sic)器件的制造中提供非平面的表面,在非平面的表面上沉积可回流的介电材料(例如bpsg或psg),然后加热可回流的介电材料以引起可回流的介电材料的回流。加热需要处于足够的温度并且达足够的时间,以引起可回流的介电材料的回流,并且由此提供基本上无空隙和基本上平面的介电层。所述方法典型地在用于制造sic器件的cmos工艺中进行。

57.所述方法通常包括多个沉积步骤和引起回流的加热步骤(多个回流循环)。例如,所述方法可以包括沉积介电材料的第一层和加热以引起介电材料的第一层回流的第一步骤,随后直接在第一层上沉积介电材料的第二层,然后是加热以引起介电材料的第二层回流的步骤,从而提供具有平面的顶表面的无空隙介电层。

58.非平面的表面可以包括sic衬底中的一个或多个沟槽。通常,非平面的表面包含在sic器件加工期间产生的非平面的形貌。非平面的表面可以包括在下面的sic衬底(例如外延sic层)上的图案化的导电膜或图案化的(非可回流的)介电膜。然后,sic衬底可以是基本上平面的。导电膜可以包含wsi、ti、tiw、co、cu、mo、w、ni、pt、ta、tasi、tisi、cosi、ptsi中的一种。介电膜可以包含sio2、sin、未掺杂多晶硅、sion中的一种。

59.温度(足以引起回流)可以在750℃至1350℃的范围内,并且可以例如是950℃。处于或高于该温度的加热时间可以在1分钟至24小时的范围内,但是通常为约30分钟。加热步骤可以包括加热炉加热或快速热处理(rtp)加热。

60.可回流的介电材料可以包括硼磷硅酸盐玻璃(bpsg),并且bpsg可以包含0至12重量%的硼和0.1至12重量%的磷。备选地,可回流的介电材料可以包括磷硅酸盐玻璃(psg)。

61.沉积介电材料的步骤可以包括等离子体增强化学气相沉积(pecvd)、低压化学气相沉积(lpcvd)和常压化学气相沉积(cvd)中的一种。

62.本发明的实施方案还提供了一种半导体结构体。半导体结构体包括sic器件的非平面的表面以及在该表面上方的介电层,其中介电层的上表面是基本上平面的,并且其中介电层基本上不含空隙。非平面的表面可以包括包含至少一个沟槽的sic衬底。非平面的表

面可以包括平面的sic衬底以及位于所述sic衬底上的图案化的介电膜,或者可以包括平面的sic衬底以及位于所述sic衬底上的图案化的导电膜。介电层的上表面可以是基本上平面的,具有<50nm rms的表面粗糙度。半导体结构体典型地是通过本文所述的方法的实施方案形成的半导体结构体。

63.本说明书中公开或示出的每个特征可以单独地或与本文中公开或示出的任何其他特征以任何适当的组合结合在本发明中。另外,尽管在不具有多项从属关系的情况下草拟了所附权利要求,但是在本公开的范围内包括具有多项从属关系的权利要求,包括彼此不兼容的要求保护的特征的所有组合。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。