半导体装置及其控制方法

1.[相关申请]

[0002]

本申请享有以日本专利申请2019-163202号(申请日:2019年9月6日)为基础申请的优先权。本申请通过参照该基础申请而包含基础申请的全部内容。

技术领域

[0003]

本实施方式涉及一种半导体装置及其控制方法。

背景技术:

[0004]

在多个存储器芯片经由接口芯片与外部端子连接的半导体装置中,有时进行搭载于各芯片的工作周期调整电路的调整(校正)动作。此时,期望有效率地进行各芯片的工作周期调整电路的调整动作。

技术实现要素:

[0005]

一实施方式提供一种能够有效率地进行各芯片的工作周期调整电路的调整动作的半导体装置及其控制方法。

[0006]

实施方式的半导体装置具备:第1芯片,与被输入来自主机装置的信号的端子电连接;及第2芯片,与第1芯片电连接。第2芯片具有调整周期信号的占空比的第1工作调整电路,第1芯片具有调整周期信号的占空比的第2工作调整电路。第1工作调整电路在第1期间进行第1调整动作,第2工作调整电路在第2期间进行第2调整动作,第1期间与第2期间具有重复的期间。

附图说明

[0007]

图1是表示应用了第1实施方式的半导体装置的系统的构成的图。

[0008]

图2是表示第1实施方式的半导体装置的构成的图。

[0009]

图3是表示第1实施方式的半导体装置的动作的波形图。

[0010]

图4是表示第2实施方式的半导体装置的动作的波形图。

[0011]

图5是表示第3实施方式的半导体装置的构成的图。

[0012]

图6是表示第3实施方式的半导体装置的动作的波形图。

[0013]

图7是表示第4实施方式的半导体装置的构成的图。

[0014]

图8(a)及8(b)是表示第4实施方式的半导体装置的动作的波形图。

[0015]

图9是表示第5实施方式的半导体装置的构成的图。

[0016]

图10是表示第5实施方式的半导体装置的动作的波形图。

[0017]

图11是表示第6实施方式的半导体装置的构成的图。

[0018]

图12是表示第6实施方式的半导体装置的动作的波形图。

具体实施方式

[0019]

以下,参照附图详细地说明实施方式的半导体装置。此外,本发明并不受这些实施方式限定。

[0020]

(第1实施方式)

[0021]

第1实施方式的半导体装置,例如是包含多个存储器芯片及接口芯片的半导体存储装置,多个存储器芯片经由接口芯片与外部端子连接。在半导体装置中,有时进行搭载在各芯片上的工作周期调整电路(dcc:duty cycle corrector)的调整动作。此时,期望有效率地进行各芯片的dcc的调整动作。

[0022]

在像nand(not and,与非)型闪速存储装置那样进行与时钟信号等周期信号同步的动作的半导体装置(例如半导体存储装置)中,必须将时钟信号的dcd(duty cycle distortion:工作周期失真)抑制得较小。因此,作为对所产生的dcd进行校正的电路,存在dcc。

[0023]

dcc将经输入的时钟信号的占空比调整为已设定的目标占空比并输出,且将该目标占空比预先调整为适当的占空比(例如占空比=50%),在设定了适当的目标占空比的状态下锁定。将动作前在一定期间内输入时钟信号使dcc锁定的调整动作称为训练(training)序列。

[0024]

在近年来的半导体装置中,为了提高安装密度,所积层的存储器芯片数不断增多。此时,为了减少各存储器芯片的外部负载,实现高速化,有时采用如下构成:将被称为fbi(frequency boosting interface,频率增加接口)芯片的接口芯片与外部端子连接,通过多个通道将接口芯片与多个存储器芯片间连接。在接口芯片及各存储器芯片上搭载着读取用dcc,在接口芯片上还搭载着写入用dcc。在该构成中,对半导体装置内的各dcc执行所述训练序列。例如,在存储器系统中,对所搭载的每个存储器芯片依次进行训练时,积层存储器芯片数越多,则越有可能导致训练时间变长,系统动作的o/h(overhead,开销)变大。

[0025]

因此,在半导体装置中,通过一并执行各存储器芯片内的读取用dcc的调整动作和接口芯片内的读取用dcc的调整动作,谋求缩短总训练时间。

[0026]

具体来说,应用了半导体装置1的系统sys构成为图1所示那样。图1是表示应用了半导体装置1的系统sys的构成的图。

[0027]

系统sys包含主机ha及半导体装置1。半导体装置1能够经由通信媒质(例如串行总线等)与主机ha连接。主机ha可以是控制器等装置,也可以是计算机或移动终端等电子机器。半导体装置1可以构成为包含多个存储器芯片的多芯片模块。半导体装置1具有接口芯片fbi及多个存储器芯片cp1-1~cp1-4、cp2-1~cp2-4。

[0028]

半导体装置1能以积层了多个存储器芯片cp1、cp2的mcp(multi chip package,多芯片封装)的形式安装。在以mcp的形式安装半导体装置1的情况下,在半导体装置1中,接口芯片fbi及多个存储器芯片cp1-1~cp1-4、cp2-1~cp2-4的周围可以用模具树脂密封。

[0029]

接口芯片fbi电连接在外部端子组1a和多个通道ch1、ch2之间。外部端子组1a能够与主机ha电连接。多个存储器芯片cp1-1~cp1-4、cp2-1~cp2-4经由多个通道ch1、ch2与接口芯片fbi连接。在图1中,例示了经由通道ch1在接口芯片fbi上连接4个存储器芯片cp1-1~cp1-4,经由通道ch2在接口芯片fbi上连接4个存储器芯片cp2-1~cp2-4的构成。

[0030]

半导体装置1从主机ha接收到时钟信号后,进行与时钟信号同步的动作。半导体装

置1也可以与时钟信号同步地进行数据的锁存。

[0031]

例如,如图2所示,外部端子组1a包含用于数据信号dq[7∶0]的端子1a1-7~1a1-0、用于读取使能信号re-/re的端子1a2-1、1a2-2、及用于数据选通信号dqs/dqs-的端子1a3-1、1a3-2。图2是表示半导体装置1的构成的图。

[0032]

在读取用dcc的训练序列中,读取使能信号re-/re是从主机ha供给的时钟信号。数据选通信号dqs/dqs-是作为应答而回传给主机ha的时钟信号。

[0033]

随着所要求的存取速度的高速化,在半导体装置1中,能够与时钟信号的双沿同步地进行和指令相关的动作。因此,时钟信号可以包含差动信号。读取使能信号re-和读取使能信号re构成一对差动信号。数据选通信号dqs和数据选通信号dqs-构成一对差动信号。

[0034]

在数据的锁存中,为了分别适当地确保数据的设置时间及保存时间,较理想的是数据的占空比成为适当的值(例如占空比≒50%)。因此,接口芯片fbi及各存储器芯片cp1、cp2具有dcc作为用于调整时钟信号的工作周期的电路。

[0035]

接口芯片fbi具有指令解码器(cmd decorder)101、读取用dcc(dcc for read)102、读取用dcc(dcc for read)103、写入用dcc(dcc for write)104、节点组n1~n6及通道接口109。

[0036]

节点组n1与用于数据信号dq[7∶0]的端子1a1-7~1a1-0电连接。节点组n1包含个数与数据信号dq[7∶0]的比特宽(例如8比特宽)对应的节点。节点组n1经由内部总线与指令解码器101的输入节点电连接。内部总线的比特宽对应于数据信号dq[7∶0]的比特宽。

[0037]

节点组n2与用于读取使能信号re-/re的端子1a2-1、1a2-2电连接。节点组n2包含个数与读取使能信号re-/re的比特宽(例如2比特)对应的节点。节点组n2经由内部总线分别与读取用dcc102的输入节点和读取用dcc103的输入节点电连接。内部总线的比特宽对应于读取使能信号re-/re的比特宽。

[0038]

节点组n3与用于数据选通信号dqs/dqs-的端子1a3-1、1a3-2电连接。节点组n3包含个数与数据选通信号dqs/dqs-的比特宽(例如2比特)对应的节点。节点组n3经由内部总线分别与读取用dcc103的输出节点和写入用dcc104的输入输出节点电连接。内部总线的比特宽对应于数据选通信号dqs/dqs-的比特宽。

[0039]

节点组n4经由内部总线分别与节点组n1和指令解码器101的输入节点电连接。节点组n4包含个数与数据信号dq[7∶0]的比特宽(例如8比特宽)对应的节点。节点组n4能够经由通道接口109与通道ch1及通道ch2中的至少一个电连接。在读取用dcc的训练序列中,通道接口109将节点组n4与通道ch1及通道ch2这两者电连接。

[0040]

节点组n5经由内部总线与读取用dcc102的输出节点电连接。节点组n5、节点组n2包含个数与读取使能信号re-/re的比特宽(例如2比特)对应的节点。节点组n5能够经由通道接口109与通道ch1及通道ch2中的至少一个电连接。在读取用dcc的训练序列中,通道接口109将节点组n5与通道ch1及通道ch2这两者电连接。

[0041]

节点组n6经由内部总线与写入用dcc104的输入输出节点电连接。节点组n6包含个数与数据选通信号dqs/dqs-的比特宽(例如2比特)对应的节点。节点组n6能够经由通道接口109与通道ch1及通道ch2中的至少一个电连接。在读取用dcc的训练序列中,通道接口109将节点组n6与通道ch1及通道ch2这两者电连接。

[0042]

读取用dcc102以设定占空比调整经由节点组n2接收到的读取使能信号re-/re的

占空比,将调整后的读取使能信号re-/re供给到节点组n5。在训练序列中,将该设定占空比调整为目标占空比(例如占空比=50%)。

[0043]

读取用dcc102具有工作周期校正电路102a、工作周期检测电路102b及校正量决定电路102c。在训练序列中,通过工作周期校正电路102a、工作周期检测电路102b及校正量决定电路102c进行比如使设定占空比接近目标占空比的反馈动作。即,工作周期校正电路102a以设定占空比校正读取使能信号re-/re的占空比。工作周期检测电路102b检测校正后的读取使能信号re-/re的占空比,并将所检测出的占空比供给到校正量决定电路102c。校正量决定电路102c根据所检测出的占空比和目标占空比(例如占空比=50%)来决定校正量,并根据所决定的校正量来变更工作周期校正电路102a的设定占空比。设定占空比也可以是能以k阶度(k为2以上的整数,例如k=64)变更。当所检测出的占空比小于目标占空比时,校正量决定电路102c使工作周期校正电路102a的设定占空比的阶度值递增。当所检测出的占空比大于目标占空比时,校正量决定电路102c使工作周期校正电路102a的设定占空比的阶度值递减。工作周期校正电路102a再次以设定占空比校正读取使能信号re-/re的占空比。工作周期检测电路102b检测校正后的读取使能信号re-/re的占空比,如果所检测出的占空比与目标占空比(例如占空比=50%)大致一致,则将校正量固定为当前的校正量,使dcc成为锁定状态。

[0044]

读取用dcc103以设定占空比调整经由节点组n2接收到的读取使能信号re-/re的占空比,将调整后的读取使能信号re-/re作为数据选通信号dqs/dqs-供给到节点组n3。在训练序列中,将该设定占空比调整为目标占空比(例如占空比=50%)。

[0045]

读取用dcc103具有工作周期校正电路103a、工作周期检测电路103b及校正量决定电路103c。在训练序列中,通过工作周期校正电路103a、工作周期检测电路103b及校正量决定电路103c进行比如使设定占空比接近目标占空比的反馈动作。例如,工作周期检测电路103b检测校正后的读取使能信号re-/re的占空比,如果所检测出的占空比与目标占空比(例如占空比=50%)大致一致,则将校正量固定为当前的校正量,使dcc成为锁定状态。

[0046]

与通道ch1连接的各存储器芯片cp1具有端子组tm1~tm3、存储单元阵列111及周边电路112。

[0047]

端子组tm1经由通道ch1与节点组n4电连接。端子组tm1包含个数与数据信号dq[7∶0]的比特宽(例如8比特宽)对应的端子。端子组tm1与周边电路112电连接。

[0048]

端子组tm2经由通道ch1与节点组n5电连接。端子组tm2包含个数与读取使能信号re-/re的比特宽(例如2比特)对应的端子。端子组tm2与周边电路112电连接。

[0049]

端子组tm3经由通道ch1与节点组n6电连接。端子组tm3包含个数与数据选通信号dqs/dqs-的比特宽(例如2比特)对应的端子。端子组tm3与周边电路112电连接。

[0050]

存储单元阵列111例如二维地排列着多个存储单元。周边电路112设置在存储单元阵列111的周边,且电连接在端子组tm1~tm3和存储单元阵列111之间。周边电路112根据经由接口芯片fbi及端子组tm1从主机ha接收到的指令,控制对存储单元阵列111中的各存储单元的访问动作(例如读取动作、写入动作)。

[0051]

周边电路112具有接收器113、驱动器114、指令解码器(cmd decorder)115、输出阻断(输出off)电路116、输出控制(output control)电路117、读取用dcc(dcc for read)118及输出阻断(输出off)电路119。

[0052]

接收器113的输入节点与端子组tm1电连接,输出节点与指令解码器115电连接。驱动器114的输入节点与输出阻断电路116电连接,输出节点与端子组tm1电连接。指令解码器115的输入节点与接收器113电连接,输出节点分别与输出阻断电路116及输出控制电路117电连接。输出阻断电路116的输入节点与指令解码器电连接,输出节点与驱动器114电连接。输出控制电路117的输入节点与指令解码器115电连接,输出节点分别与读取用dcc118及输出阻断电路119电连接。读取用dcc118的输入节点与端子组tm2及输出控制电路117电连接,输出节点与输出阻断电路119电连接。输出阻断电路119的输入节点分别与读取用dcc118及输出控制电路117电连接,输出节点与端子组tm3电连接。

[0053]

读取用dcc118以设定占空比调整经由端子组tm2接收到的读取使能信号re-/re的占空比,将调整后的读取使能信号re-/re供给到输出阻断电路119。在训练序列中,将该设定占空比调整为目标占空比(例如占空比=50%)。

[0054]

读取用dcc118具有工作周期校正电路118a、工作周期检测电路118b及校正量决定电路118c。在训练序列中,通过工作周期校正电路118a、工作周期检测电路118b及校正量决定电路118c进行比如使设定占空比接近目标占空比的反馈动作。例如,工作周期检测电路118b检测校正后的读取使能信号re-/re的占空比,如果所检测出的占空比与目标占空比(例如占空比=50%)大致一致,则将校正量固定为当前的校正量,使dcc成为锁定状态。

[0055]

输出阻断电路116配置在指令解码器115及驱动器114之间。输出阻断电路116从指令解码器115接收指令的解码结果。输出阻断电路116例如根据指令是指示一并执行模式的读取用dcc的调整动作的调整指令,阻断对驱动器114的电源供给等,由此停止从驱动器114向端子组tm1的数据信号dq[7∶0]的输出。即,输出阻断电路116非活性化端子组tm1。

[0056]

此外,当根据调整指令的执行完成而解除输出阻断电路116的电源供给的阻断并重新开始电源供给时,驱动器114成为能够向端子组tm1输出应输出的数据信号dq[7∶0]的状态。

[0057]

输出控制电路117配置在指令解码器115、读取用dcc118及输出阻断电路119之间。输出控制电路117从指令解码器115接收指令的解码结果。输出阻断电路116例如根据指令是指示一并执行模式的读取用dcc的调整动作的调整指令,向读取用dcc118指示调整动作的开始,并且向输出阻断电路119指示数据选通信号dqs/dqs-的输出停止。

[0058]

输出阻断电路119配置在输出控制电路117和端子组tm3之间。输出阻断电路119能够从读取用dcc118接收调整后的读取使能信号re-/re,将调整后的读取使能信号re-/re作为数据选通信号dqs/dqs-输出到端子组tm3。输出阻断电路119当从输出控制电路117接收到停止输出数据选通信号dqs/dqs-的指示时,根据该指示而停止向端子组tm3输出数据选通信号dqs/dqs-。即,输出阻断电路119非活性化端子组tm3。

[0059]

此外,当根据调整指令的执行完成而解除输出控制电路117的输出停止的指示时,输出阻断电路119成为能够将调整后的读取使能信号re-/re作为数据选通信号dqs/dqs-输出到端子组tm3的状态。

[0060]

与通道ch2连接的各存储器芯片cp2具有端子组tm1~tm3、存储单元阵列111及周边电路112。端子组tm1~tm3、存储单元阵列111及周边电路112分别与存储器芯片cp1中的端子组tm1~tm3、存储单元阵列111及周边电路112相同。

[0061]

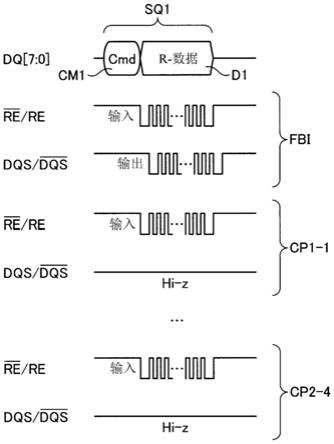

在读取用dcc的训练序列sq1中,半导体装置1例如进行如图3所示的动作。图3是表

示半导体装置1的动作的波形图。

[0062]

接口芯片fbi当从主机ha接收到指示读取用dcc的调整动作的调整指令cm1时,将调整指令cm1供给到指令解码器101,并且经由通道ch1供给到存储器芯片cp1-1~cp1-4,经由通道ch2供给到存储器芯片cp2-1~cp2-4。

[0063]

在接口芯片fbi中,指令解码器101对调整指令cm1进行解码。指令解码器101当根据调整指令cm1,解释为被指示一并执行模式下的读取用dcc的调整动作时,向读取用dcc102及读取用dcc103指示dcc的调整动作的开始。

[0064]

读取用dcc102及读取用dcc103当分别从主机ha经由端子1a2-1、1a2-2接收到读取使能信号re/re(读取用时钟信号)时,使用读取使能信号re-/re,开始用于使设定占空比接近目标占空比的反馈动作。

[0065]

另外,接口芯片fbi将由读取用dcc102调整后的读取使能信号re-/re经由通道接口109及通道ch1向多个存储器芯片cp1-1~cp1-4的端子组tm2广播发送。与此同时,接口芯片fbi将由读取用dcc102调整后的读取使能信号re-/re经由通道接口109及通道ch2向多个存储器芯片cp2-1~cp2-4的端子组tm2广播发送。

[0066]

此时,向存储器芯片cp1-1~cp1-4及cp2-1~cp2-4供给的读取使能信号re-/re也可以是如下构成:选通(停止)向各存储器芯片的re-/re输出直到接口芯片fbi的读取用dcc102被锁定为止,dcc102被锁定后向各存储器芯片供给re-/re输出。

[0067]

在共有通道ch1、ch2的各存储器芯片cp1、cp2中,指令解码器115对调整指令cm1进行解码。指令解码器115当根据调整指令cm1,解释为被指示一并执行模式下的读取用dcc的调整动作时,经由输出控制电路117对读取用dcc118指示dcc的调整动作的开始。读取用dcc118成为能够开始dcc的调整动作的状态。

[0068]

与此相应,与通道ch1连接的各存储器芯片cp1-1~cp1-4中的读取用dcc118当分别接收到图3所示的读取使能信号re-/re(读取用时钟信号)时,使用读取使能信号re-/re,开始用于使设定占空比接近目标占空比的反馈动作。与此同时,与通道ch2连接的各存储器芯片cp2-1~cp2-4中的读取用dcc118当分别接收到图3所示的读取使能信号re-/re(读取用时钟信号)时,使用读取使能信号re-/re,开始用于使设定占空比接近目标占空比的反馈动作。

[0069]

此时,各存储器芯片cp1-1~cp1-4、cp2-1~cp2-4的端子组tm1都成为高阻抗状态。因此,接口芯片fbi根据从各存储器芯片cp1-1~cp1-4、cp2-1~cp2-4的端子组tm1经由通道接口109接收到的高阻抗的信号,将虚拟数据d1(例如全部为“0”(all“0”))作为数据信号dq[7∶0]经由节点组n1及端子1a1-7、1a1-0回传给主机ha。数据d1的大小是以如下方式预先决定的,即,数据d1的传送期间成为与利用接口芯片fbi及各存储器芯片的dcc完成调整动作所需的充分的期间对应的大小。

[0070]

另外,各存储器芯片cp1-1~cp1-4、cp2-1~cp2-4的端子组tm3都成为高阻抗状态。因此,接口芯片fbi根据从各存储器芯片cp1-1~cp1-4、cp2-1~cp2-4的端子组tm3经由通道接口109接收的高阻抗的信号,产生代替的数据选通信号dqs/dqs-。例如,接口芯片fbi将由读取用dcc103调整后的读取使能信号re-/re作为图3所示的数据选通信号dqs/dqs-经由节点组n3及端子1a3-1、1a3-2回传给主机ha。

[0071]

此处,共有通道ch1的存储器芯片cp1-1~cp1-4的数据信号dq、数据选通信号dqs/

dqs-当分别同时传输时,可能在通道ch1上发生短路。共有通道ch2的存储器芯片cp2-1~cp2-4的数据信号dq、数据选通信号dqs/dqs-当分别同时传输时,可能在通道ch2上发生短路。如果对多个芯片(接口芯片fbi、存储器芯片cp1、cp2)逐个地进行dcc的训练,以使信号在通道ch1、ch2上不发生短路,则有dcc的训练时间长时间化的倾向。

[0072]

与此相对,在图3所示的训练序列sq1中,在接收到构成指令cm1后,共有通道ch1、ch2的各存储器芯片cp1、cp2接收读取使能信号re-/re。在各存储器芯片cp1、cp2中,通过输出控制电路117的控制,dcc118接收读取使能信号re-/re并开始dcc的调整动作。另外,在各存储器芯片cp1、cp2中,通过输出阻断电路116、119使端子组tm1、tm3成为高阻抗状态。即,以如下方式进行控制:在接收到指示dcc的调整动作的指令cm1后,停止从各存储器芯片cp1、cp2向接口芯片fbi输出数据信号dq及数据选通信号dqs/dqs-,对主机ha侧从接口芯片fbi回传虚拟数据信号dq及虚拟数据选通信号dqs/dqs-的输出。由此,能够使所有芯片一并地执行读取用dcc的训练,因此能够大幅地缩短dcc的训练执行时间。

[0073]

如上所述,在第1实施方式中,在半导体装置1中,一并执行各存储器芯片cp1、cp2内的读取用dcc118的调整动作和接口芯片fbi内的读取用dcc102、103的调整动作。由此,在半导体装置1中,能够有效率地进行各芯片的dcc的调整动作,能够缩短总训练时间。

[0074]

此外,接口芯片fbi及各存储器芯片cp1、cp2应接收的调整指令cm1也可以作为用于指示读取用dcc的构成动作的专用指令而准备。

[0075]

或者,调整指令cm1也可以与单独执行时的训练指令相同,在该情况下,也可以是如下方法:利用设置特征指令预先设定切换一并执行模式与单独执行模式的寄存器。在该情况下,切换一并执行模式与单独执行模式的寄存器也可以设置在接口芯片fbi及各存储器芯片cp1、cp2中的指令解码器101、115内。

[0076]

另外,在读取用dcc的训练序列sq1中,也可以从各存储器芯片cp1、cp2中被选择的1个存储器芯片向接口芯片fbi输出数据选通信号dqs/dqs-。在该构成中,接口芯片fbi也将数据选通信号dqs/dqs-经由读取用dcc103回传给主机ha。

[0077]

(第2实施方式)

[0078]

接下来,对第2实施方式的半导体装置1进行说明。以下,以与第1实施方式不同的部分为中心进行说明。

[0079]

第1实施方式记载了所有芯片一并执行读取用dcc的调整动作的控制方法,但由于系统整体的负载电流较大,所以存在电源电压因负载电流的影响而发生变动等dcc在不稳定的状态下被锁定的可能性。

[0080]

因此,在第2实施方式中,为了能够选择同时进行训练的芯片,对所有存储器芯片中的每特定数量的芯片(例如8个存储器芯片中的每4个芯片)同时执行(一并执行)读取用dcc的调整动作。同时执行的芯片的选择是在训练执行前通过利用指令输入的设定来进行的。例如,半导体装置1以多个训练序列分批执行各芯片(接口芯片fbi及各存储器芯片cp1、cp2)的读取用dcc的调整动作。即,半导体装置1依次从主机ha接收分别指示分批执行模式下的读取用dcc的调整动作的多个调整指令,依次执行与多个调整指令相应的多个训练序列。

[0081]

具体来说,在读取用dcc的训练序列中,如图4所示,半导体装置1在以下方面进行与第1实施方式不同的动作。图4是表示半导体装置1的动作的波形图。

[0082]

例如,调整指令cm2可以被预先决定为指示分批执行模式下的第1芯片组的读取用dcc的调整动作的指令,调整指令cm3可以被预先决定为指示分批执行模式下的第2芯片组的读取用dcc的调整动作的指令。第1芯片组包含接口芯片fbi及与各通道ch1、ch2连接的第奇数个存储器芯片cp1-1、cp1-3、cp2-1、cp2-3。第2芯片组包含接口芯片fbi及与各通道ch1、ch2连接的第偶数个存储器芯片cp1-2、cp1-4、cp2-2、cp2-4。

[0083]

在训练序列sq2中,接口芯片fbi当从主机ha接收到调整指令cm2时,将调整指令cm2供给到指令解码器101,并且经由通道ch1供给到存储器芯片cp1-1~cp1-4,经由通道ch2供给到存储器芯片cp2-1~cp2-4。

[0084]

接口芯片fbi的指令解码器101对调整指令cm2进行解码。指令解码器101当根据调整指令cm2,解释为被指示分批执行模式下的第1芯片组的读取用dcc的调整动作时,向读取用dcc102及读取用dcc103指示dcc的调整动作的开始。

[0085]

在共有通道ch1、ch2的各存储器芯片cp1-1~cp1-4、cp2-1~cp2-4中,指令解码器115对调整指令cm2进行解码。

[0086]

在第奇数个存储器芯片cp1-1、cp1-3、cp2-1、cp2-3中,指令解码器115当根据调整指令cm2,解释为被指示分批执行模式下的读取用dcc的调整动作时,经由输出控制电路117对读取用dcc118指示dcc的调整动作的开始。读取用dcc118成为能够开始dcc的调整动作的状态。当读取用dcc118接收到图4所示的读取使能信号re-/re(读取用时钟信号)时,使用读取使能信号re/re,开始用于使设定占空比接近目标占空比的反馈动作。此时,通过输出阻断电路116、119使端子组tm1、tm3成为高阻抗状态。即,通过输出阻断电路116、119非活性化端子组tm1、tm3。

[0087]

在第偶数个存储器芯片cp1-2、cp1-4、cp2-2、cp2-4中,指令解码器115当根据调整指令cm2,解释为未被指示分批执行模式下的读取用dcc的调整动作时,不向读取用dcc118指示dcc的调整动作的开始。读取用dcc118不进行调整动作。即,如图4中“未执行(unexecuted)”所示,读取用dcc118未接收读取使能信号re-/re(读取用时钟信号),而不开始用于使设定占空比接近目标占空比的反馈动作。

[0088]

接口芯片fbi将虚拟数据d2(例如全部为“0”)作为数据信号dq[7∶0]经由节点组n1及端子1a1-7、1a1-0回传给主机ha。接口芯片fbi将由读取用dcc103调整后的读取使能信号re-/re作为图4所示的数据选通信号dqs/dqs-经由节点组n3及端子1a3-1、1a3-2回传给主机ha。

[0089]

在训练序列sq3中,除了将第奇数个存储器芯片cp1-1、cp1-3、cp2-1、cp2-3的动作和第偶数个存储器芯片cp1-2、cp1-4、cp2-2、cp2-4的动作相互置换以外,进行与训练序列sq2相同的动作。

[0090]

如上所述,在第2实施方式中,在半导体装置1中,能够选择同时执行(一并执行)dcc的训练的存储器芯片数。例如,各芯片的指令解码器对分批执行模式下的调整指令进行解释,能够解释自身芯片是否应执行dcc的训练。由此,能够任意地选择同时执行的芯片,所以与对所有芯片一并执行相比,能够抑制电源电压的变动等,能够稳定地锁定各芯片的dcc。

[0091]

调整指令cm2、cm3可以与单独执行时的训练指令编号相同,在该情况下,也可以是如下方法:利用设置特征指令预先设定切换一并执行模式与单独执行模式的寄存器、及在

一并执行模式时使哪个芯片组有效。

[0092]

(第3实施方式)

[0093]

接下来,对第3实施方式的半导体装置1i进行说明。以下,以与第1实施方式及第2实施方式不同的部分为中心进行说明。

[0094]

在第1实施方式中,例示了一并执行所有芯片的读取用dcc的控制,但搭载在接口芯片fbi上的写入用dcc必须单独执行。

[0095]

在第3实施方式中,设置用于dcc训练的专用指令,该专用指令能够将来自主机ha的读取使能信号re-/re和数据选通信号dqs/dqs-同时输入到接口芯片fbi。进而,在接口芯片fbi中,追加在接收该专用指令时停止向主机ha输出数据选通信号dqs/dqs-的电路、及停止向各存储器芯片cp1、cp2输出数据选通信号dqs/dqs-的电路。由此,能够一并执行接口芯片fbi用的读取用dcc102、103、写入用dcc104的调整动作。此时,也能够与第1实施方式同样地一并执行各存储器芯片cp1、cp2的读取用dcc118的调整动作。

[0096]

具体来说,如图5所示,在半导体装置1i中,接口芯片fbi还具有输出阻断(输出off)电路305、输出阻断(输出off)电路306及输出阻断(输出off)电路307。图5是表示半导体装置1i的构成的图。

[0097]

输出阻断电路305配置在节点组n4和通道接口109之间。输出阻断电路305从指令解码器101接收指令的解码结果。输出阻断电路305根据指令是指示一并执行模式的读取用dcc、写入用dcc的调整动作的调整指令,向各存储器芯片cp1、cp2传送调整指令,但之后阻断向各存储器芯片cp1、cp2传送从主机ha接收到的写入数据d4。即,输出阻断电路305将通道接口109与端子组1a1-7~1a1-0电阻断。

[0098]

输出阻断电路306配置在读取用dcc103和节点组n3之间。输出阻断电路306从指令解码器101接收指令的解码结果。输出阻断电路306例如根据指令是指示一并执行模式的读取用dcc、写入用dcc的调整动作的调整指令,停止从读取用dcc103向节点组n3输出数据选通信号dqs/dqs-。

[0099]

写入用dcc104以设定占空比调整经由节点组n3接收到的数据选通信号dqs/dqs-的占空比,并将调整后的数据选通信号dqs/dqs-供给到节点组n6。在训练序列中,将该设定占空比调整为目标占空比(例如占空比=50%)。

[0100]

写入用dcc104具有工作周期校正电路104a、工作周期检测电路104b及校正量决定电路104c。在训练序列中,通过工作周期校正电路104a、工作周期检测电路104b及校正量决定电路104c进行比如使设定占空比接近目标占空比的反馈动作。例如,工作周期检测电路104b检测校正后的数据选通信号dqs/dqs-的占空比,如果所检测出的占空比与目标占空比(例如占空比=50%)大致一致,则将校正量固定为当前的校正量,使dcc成为锁定状态。

[0101]

输出阻断电路307配置在节点组n6和通道接口109之间。输出阻断电路307从指令解码器101接收指令的解码结果。例如,输出阻断电路307根据指令是指示一并执行模式的读取用dcc、写入用dcc的调整动作的调整指令,停止从写入用dcc104向各存储器芯片cp1、cp2输出数据选通信号dqs/dqs-。即,输出阻断电路307将通道接口109与写入用dcc104电阻断。

[0102]

另外,在读取用dcc、写入用dcc的训练序列sq4中,如图6所示,半导体装置1i在以下方面进行与第1实施方式不同的动作。图6是表示半导体装置1i的动作的波形图。

[0103]

在接口芯片fbi中,指令解码器101对调整指令cm4进行解码。指令解码器101当根据调整指令cm4,解释为指示一并执行模式下的读取用dcc、写入用dcc的调整动作时,向读取用dcc102、读取用dcc103及写入用dcc104指示dcc的调整动作的开始。

[0104]

读取用dcc102及读取用dcc103当分别从主机ha经由端子1a2-1、1a2-2接收到读取使能信号re-/re(读取用时钟信号)时,使用读取使能信号re-/re,开始用于使设定占空比接近目标占空比的反馈动作。写入用dcc104当经由端子1a3-1、1a3-2从主机ha接收到数据选通信号dqs/dqs-(写入用时钟信号)时,使用数据选通信号dqs/dqs-开始用于使设定占空比接近目标占空比的反馈动作。

[0105]

此时,输出阻断电路305从指令解码器101接收到指令的解码结果,向各存储器芯片cp1、cp2传送调整指令,之后阻断向各存储器芯片cp1、cp2传送从主机ha接收到的写入数据d4。另外,输出阻断电路306从指令解码器101接收到指令的解码结果,停止从读取用dcc103向节点组n3输出数据选通信号dqs/dqs-。输出阻断电路307从指令解码器101接收到指令的解码结果,停止从写入用dcc104向各存储器芯片cp1、cp2输出数据选通信号dqs/dqs-。

[0106]

由此,能够同时执行接口芯片fbi及各存储器芯片cp1、cp2的读取用dcc的调整动作和接口芯片fbi的写入用dcc的调整动作。结果,与第1实施方式相比,能够进一步缩短dcc的总训练时间。

[0107]

如上所述,在第3实施方式中,在半导体装置1i中,一并执行接口芯片fbi的读取用dcc的调整动作、各存储器芯片cp1、cp2的读取用dcc的调整动作及接口芯片fbi的写入用dcc的调整动作。由此,在半导体装置1i中,能够更有效率地进行各芯片的dcc的调整动作,能够进一步缩短总训练时间。

[0108]

调整指令cm4可以与单独执行时的训练指令编号相同,在该情况下,也可以是如下方法:利用设置特征指令预先设定切换一并执行模式与单独执行模式的寄存器、及在一并执行模式时使哪个芯片组有效。

[0109]

(第4实施方式)

[0110]

接下来,对第4实施方式的半导体装置1j进行说明。以下,以与第1实施方式~第3实施方式不同的部分为中心进行说明。

[0111]

在第1实施方式~第3实施方式中,考虑了用于针对多个芯片实现训练时间的缩短的研究,但在第4实施方式中,考虑用于针对1芯片实现训练时间的缩短的研究。

[0112]

在第1实施方式~第3实施方式中,接口芯片fbi将虚拟数据d1~d4(参照图3、图4、图6)回传给主机ha的期间的长度被预先决定为进行调整动作的dcc锁定所需的充分的时间(例如16kb(1页(page)大小)的数据传送时间)。即,数据d1~d4的期间的长度有可能大幅地长于dcc实际锁定为止的时间长度。另外,为了确认dcc实际已锁定,主机ha向半导体装置发出状态读取指令,接收并确认来自半导体装置的该应答。该训练 确认序列的时间与dcc实际锁定为止的时间长度相比,有可能进一步大幅地增长。

[0113]

因此,在第4实施方式中,各芯片将表示dcc的调整动作的进行状况的状态信息转换为可由主机ha识别的密码,将虚拟数据d1~d4的一部分置换为该密码并回传给主机ha,由此实现训练 确认序列的时间的缩短。

[0114]

具体来说,如图7所示,在半导体装置1j中,接口芯片fbi还具有接收器405a、驱动

器406a及锁定状态(lock status)通知电路407a。图7是表示半导体装置1j的构成的图。

[0115]

接收器405a配置在节点组n1和指令解码器101之间。当从主机ha接收到指令时,接收器405a将该指令传送到指令解码器101。

[0116]

锁定状态通知电路407a配置在指令解码器101、驱动器406a、读取用dcc102及读取用dcc103之间。锁定状态通知电路407a具有状态寄存器及产生电路。锁定状态通知电路407a在状态寄存器内确保第1地址及第2地址。第1地址是用于存储表示读取用dcc102的调整动作的进行状况的状态信息的寄存器地址。第2地址是用于存储表示读取用dcc103的调整动作的进行状况的状态信息的寄存器地址。锁定状态通知电路407a例如根据从指令解码器101接收到指示开始调整动作的解码结果,将初始值存储在状态寄存器内的第1地址及第2地址中。该初始值也可以是表示dcc的锁定未完成的值。

[0117]

读取用dcc102能够进行dcc的调整动作,且将该调整动作的进行状况通知给锁定状态通知电路407a。锁定状态通知电路407a当从读取用dcc102接收到调整动作完成的通知时,将状态寄存器内的第1地址中所存储的值从初始值变更为有效值。该有效值可以是表示dcc的锁定完成的值。

[0118]

同样,读取用dcc103能够进行dcc的调整动作,且将该调整动作的进行状况通知给锁定状态通知电路407a。锁定状态通知电路407a当从读取用dcc103接收到调整动作完成的通知时,将状态寄存器内的第2地址中所存储的值从初始值变更为有效值。该有效值可以是表示dcc的锁定完成的值。

[0119]

锁定状态通知电路407a当在状态寄存器内的第1地址及第2地址的任一个中存储着有效值时,通过产生电路产生用于接口芯片fbi的密码并输出到驱动器406a。用于接口芯片fbi的密码也可以是表示接口芯片fbi中的各dcc的锁定完成的代码(即,位模式)。

[0120]

驱动器406a配置在节点组n1和锁定状态通知电路407a之间。驱动器406a当从锁定状态通知电路407a接收到用于接口芯片fbi的密码时,将该密码经由节点组n1及端子1a1-7~1a1-0发送到主机ha。由此,主机ha接收用于接口芯片fbi的密码,根据该密码,能够识别接口芯片fbi中的各dcc的锁定完成。

[0121]

在与通道ch1连接的各存储器芯片cp1中,周边电路112a还具有锁定状态通知电路117a。

[0122]

锁定状态通知电路117a配置在指令解码器115、驱动器114、读取用dcc118之间。锁定状态通知电路117a具有状态寄存器及产生电路。锁定状态通知电路117a在状态寄存器内确保特定的地址。特定的地址是用于存储表示读取用dcc118的调整动作的进行状况的状态信息的寄存器地址。锁定状态通知电路117a例如根据从指令解码器115接收到指示开始调整动作的解码结果,将初始值存储在状态寄存器内的特定的地址。该初始值也可以是表示dcc的锁定未完成的值。

[0123]

读取用dcc118进行dcc的调整动作,且能够将该调整动作的进行状况通知给锁定状态通知电路117a。锁定状态通知电路117a当从读取用dcc118接收到调整动作完成的通知时,将状态寄存器内的特定地址中存储的值从初始值变更为有效值。该有效值可以是表示dcc的锁定完成的值。

[0124]

锁定状态通知电路117a当在状态寄存器内的特定的地址中存储着有效值时,通过产生电路产生用于存储器芯片cp1的密码并输出到驱动器114。用于存储器芯片cp1的密码

也可以是表示存储器芯片cp1中的dcc的锁定完成的代码(即,位模式)。驱动器114当从锁定状态通知电路117a接收到用于存储器芯片cp1的密码时,将该密码经由端子组tm1及通道ch1发送到接口芯片fbi。

[0125]

在锁定状态通知电路407a中,通道接口109当接收到用于存储器芯片cp1的密码时便向锁定状态通知电路407a传送。锁定状态通知电路407a将传送来的密码输出到驱动器406a。驱动器406a经由节点组n1及端子1a1-7~1a1-0向主机ha发送该密码。由此,主机ha接收用于存储器芯片cp1的密码,根据该密码,能够识别存储器芯片cp1中的dcc的锁定完成。

[0126]

此外,对于与通道ch2连接的各存储器芯片cp2,也和与通道ch1连接的各存储器芯片cp1相同。

[0127]

例如,如图8(a)中“固定数据大小(fixed data size)”所示,接口芯片fbi将虚拟数据d1回传给主机ha的期间的长度被预先固定地决定为dcc的锁定所需的充分的时间。图8(a)是表示数据d1的长度被固定地决定时的半导体装置的动作(训练 确认序列sq1')的波形图。在该情况下,数据d1的期间的长度有可能大幅长于dcc实际锁定为止的时间长度。另外,为了确认dcc实际锁定,主机ha向半导体装置发出状态读取指令cm10,接收并确认来自半导体装置的该应答。该训练 确认序列sq1'的时间与dcc实际锁定为止的时间长度相比,有可能进一步大幅度增长。

[0128]

另一方面,在第4实施方式中,如图8(b)所示,各芯片在与调整指令cm5相应的训练 确认序列sq5执行中,进行将表示dcc是否锁定的进行状况(status)的密码(pass code)cd5加入到数据信号dq[7∶0]中的控制。图8(b)是表示第4实施方式的半导体装置1j的动作(训练 确认序列sq5)的波形图。各芯片能够在内部dcc已锁定的时刻通过密码cd5向主机ha通知该锁定状态。例如,数据信号dq[7∶0]上的数据模式如“任意数据大小(arbitrary data size)”所示,在解锁(unlock)状态下,接口芯片fbi将虚拟数据d5回传给主机ha的期间的长度设为任意长度。而且,数据信号dq[7∶0]上的数据模式可以在dcc成为锁定状态时设为表示密码cd5的模式。密码cd5的图案也可以是在各芯片间相互不同的图案。各芯片可以在(例如针对各通道的每个芯片以时分方式输出等)数据信号dq[7∶0]上无其它密码的期间输出自身密码。由此,在比所决定的期间短的期间内dcc锁定的情况下,主机ha能够识别各芯片中的dcc的锁定状态,并对各芯片立即停止训练序列sq5。由此,能够大幅地缩短dcc的训练时间。

[0129]

如上所述,在第4实施方式中,1个芯片将表示dcc的调整动作的进行状况的状态信息转换为可由主机ha识别的密码,将虚拟数据的一部分置换为该密码,回传给主机ha。由此,在比所决定的期间短的期间内dcc锁定的情况下,能够立即停止训练,所以与固定时间的序列相比,能够针对每个芯片缩短dcc的训练 确认序列的时间。

[0130]

调整指令cm5可以与单独执行时的训练指令编号相同,在该情况下,也可以是如下方法:利用设置特征指令预先设定切换一并执行模式与单独执行模式的寄存器、及在一并执行模式时使哪个芯片组有效。

[0131]

(第5实施方式)

[0132]

接下来,对第5实施方式的半导体装置1k进行说明。以下,以与第1实施方式~第4实施方式不同的部分为中心进行说明。

[0133]

第4实施方式关于1芯片例示了在训练执行中立即对主机ha侧进行dcc已锁定的通

知的控制,但在第5实施方式中,对所有芯片一并执行该控制。

[0134]

即,在第5实施方式中,与第1实施方式同样,对各存储器芯片追加停止数据选通信号dqs/dqs-的输出的电路。进而,追加在内部dcc已锁定的时刻对数据信号dq[7∶0]输出中的1比特(bit)设置标记的电路,以针对所积层的每个芯片每次输出1比特的方式进行分配,在各存储器芯片中进行控制以使数据信号dq的输出不短路。

[0135]

具体来说,如图9所示,在半导体装置1k中,各存储器芯片cp1、cp2的周边电路112b还具有输出阻断(输出off)电路119b。图9是表示半导体装置1k的构成的图。

[0136]

输出阻断电路119b配置在端子组tm3和读取用dcc118之间。输出阻断电路119b从读取用dcc118接收调整后的读取使能信号re-/re和禁止信号da。输出阻断电路119b在禁止信号da为非有效电平的期间,将调整后的读取使能信号re-/re作为数据选通信号dqs/dqs-输出到端子组tm3。输出阻断电路119b在禁止信号da处于有效电平的期间,停止向端子组tm3输出数据选通信号dqs/dqs-。

[0137]

数据信号dq[7∶0]中的各比特被分配给与通道ch1连接的各存储器芯片cp1-1~cp1-8的每一个作为所要使用的比特。各存储器芯片cp1-1~cp1-8的锁定状态通知电路407a根据来自读取用dcc118的调整动作完成的通知,产生用于存储器芯片cp1的标记并设定为已分配的比特。例如,存储器芯片cp1-1的锁定状态通知电路407a将标记设定为比特dq[0]。存储器芯片cp1-2的锁定状态通知电路407a将标记设定为比特dq[1]。存储器芯片cp1-8的锁定状态通知电路407a将标记设定为比特dq[7]。锁定状态通知电路407a将设定了标记的比特经由驱动器114、端子组tm1、通道ch1输出到接口芯片fbi。

[0138]

同样,数据信号dq[7∶0]中的各比特被分配给与通道ch2连接的各存储器芯片cp2-1~cp2-8的每一个作为所要使用的比特。各存储器芯片cp2-1~cp2-8的锁定状态通知电路407a根据来自读取用dcc118的调整动作完成的通知,产生用于存储器芯片cp2的标记并设定为已分配的比特。例如,存储器芯片cp2-1的锁定状态通知电路407a将标记设定为比特dq[0]。存储器芯片cp2-2的锁定状态通知电路407a将标记设定为比特dq[1]。存储器芯片cp2-8的锁定状态通知电路407a将标记设定为比特dq[7]。锁定状态通知电路407a将设定了标记的比特经由驱动器114、端子组tm1、通道ch2输出到接口芯片fbi。

[0139]

接口芯片fbi的通道接口109例如能够分时切换通道ch1、ch2和锁定状态通知电路407a的连接。由此,关于是否对数据信号dq[7∶0]中的各比特设置了标记,能够大致实时地通知给锁定状态通知电路407a。锁定状态通知电路407a确认是否对数据信号dq[7∶0]中的各比特设置了标记,如果在所有比特中设置了标记,则利用锁定状态通知电路407a保存表示已对与该通道对应的所有存储器芯片完成了锁定的有效值。锁定状态通知电路407a当内部的dcc、通道ch1的所有存储器芯片cp1的dcc和通道ch2的所有存储器芯片cp2的dcc中的任一个保存有效值时,产生表示在所有芯片中锁定完成的密码,并输出到驱动器406a。驱动器406a经由节点组n1及端子1a1-7~1a1-0向主机ha发送该密码。由此,主机ha接收密码,根据该密码,能够识别所有芯片中的dcc的锁定完成。

[0140]

例如,如图10所示,各芯片在与调整指令cm6相应的训练 确认序列sq6执行中,进行将表示dcc是否锁定(lock)的进行状况的状态信息加入到数据信号dq[7∶0]中的控制。图10是表示第5实施方式的半导体装置1k的动作(训练 确认序列sq6)的波形图。

[0141]

接口芯片fbi根据调整指令cm6,开始dcc的调整动作,并且将虚拟数据d6发送到主

机ha。接口芯片fbi当在内部dcc锁定时,利用锁定状态通知电路407a保存表示内部的dcc已锁定的有效值。

[0142]

存储器芯片cp1-1根据调整指令cm6,开始dcc的调整动作,使标记为初始值(解锁),并设定为比特dq[0],使数据信号dq[7∶0]中的其它比特dq[7∶1]和数据选通信号dqs/dqs-分别为高阻抗状态。存储器芯片cp1-1在内部dcc已锁定的时刻,使标记为有效值(lock),并设定为比特dq[0]。此时,存储器芯片cp1-1将数据信号dq[7∶0]中的其它比特dq[7∶1]维持在高阻抗状态。

[0143]

存储器芯片cp1-8根据调整指令cm6,开始dcc的调整动作,使标记为初始值(解锁),并设定为比特dq[7],使数据信号dq[7∶0]中的其它比特dq[6∶0]和数据选通信号dqs/dqs-分别为高阻抗状态。存储器芯片cp1-8在内部dcc已锁定的时刻,使标记为有效值(lock),并设定为比特dq[7]。此时,存储器芯片cp1-8将数据信号dq[7∶0]中的其它比特dq[6∶0]维持在高阻抗状态。

[0144]

接口芯片fbi当在将通道ch1和锁定状态通知电路407a连接的状态下,对所有比特dq[0]~dq[7]设定标记的有效值(设置标记)时,利用锁定状态通知电路407a保存表示与通道ch1连接的所有存储器芯片cp1-1~cp1-8的dcc锁定的有效值。

[0145]

另外,存储器芯片cp2-1根据调整指令cm6,开始dcc的调整动作,使标记为初始值(解锁),并设定为比特dq[0],使数据信号dq[7∶0]中的其它比特dq[7∶1]和数据选通信号dqs/dqs-分别为高阻抗状态。存储器芯片cp2-1在内部dcc已锁定的时刻,使标记为有效值(lock),并设定为比特dq[0]。此时,存储器芯片cp2-1将数据信号dq[7∶0]中的其它比特dq[7∶1]维持在高阻抗状态。

[0146]

存储器芯片cp2-8根据调整指令cm6,开始dcc的调整动作,使标记为初始值(解锁),并设定为比特dq[7],使数据信号dq[7∶0]中的其它比特dq[6:0]和数据选通信号dqs/dqs-为高阻抗状态。存储器芯片cp2-8在内部dcc已锁定的时刻,使标记为有效值(lock),并设定为比特dq[7]。此时,存储器芯片cp2-8将数据信号dq[7∶0]中的其它比特dq[6∶0]维持在高阻抗状态。

[0147]

接口芯片fbi当在将通道ch2和锁定状态通知电路407a连接的状态下,对所有比特dq[0]~dq[7]设定标记的有效值(设置标记)时,利用锁定状态通知电路407a保存表示与通道ch2连接的所有存储器芯片cp2-1~cp2-8的dcc锁定的有效值。锁定状态通知电路407a当关于内部的dcc、与通道ch1连接的所有存储器芯片cp1-1~cp1-8的dcc、及与通道ch2连接的所有存储器芯片cp2-1~cp2-8的dcc中的任一个,保存表示dcc已锁定的有效值时,产生表示所有dcc已锁定的密码cd6,并发送给主机ha。由此,主机ha接收密码,根据该密码,能够识别所有芯片中的dcc的锁定已完成。

[0148]

这样,在图10所示的训练序列sq6中,在接收到调整指令cm6后,在各存储器芯片中,使数据信号dq[7∶0]的各比特中经分配的比特选择性地输出标记,停止其它比特的输出。标记了以该值表示dcc的调整动作的进行状况,以初始值表示锁定未完成,以有效值表示锁定完成。接口芯片监视数据信号dq[7∶0]中的各比特,在对每个比特设置了标记的时刻,产生与该比特对应的芯片用密码并发送给主机ha。由此,在比所决定的期间短的期间内dcc锁定的情况下,能够大致实时地通知给主机ha,能够利用主机ha对所有芯片一并执行立即停止训练。

[0149]

如上所述,在第5实施方式中,多个芯片相互并行地将表示dcc的调整动作的进行状况的状态信息置换为虚拟数据的一部分并回传给主机ha。由此,能够对多个芯片一并执行dcc的调整动作的执行及确认,能够在比所决定的期间短的期间内dcc锁定的情况下立即停止训练,因此能够进一步缩短dcc的训练 确认序列的时间。

[0150]

此外,与各通道ch1、ch2连接的存储器芯片cp1、cp2的数量可以少于数据信号dq[7∶0]的比特数。在该情况下,也能够针对每个通道ch1、ch2将其所连接的各存储器芯片cp1、cp2分配给数据信号dq[7∶0]中的1比特,且利用各存储器芯片cp1、cp2以数据信号dq的输出不会在通道ch1、ch2上短路的方式进行控制。

[0151]

调整指令cm6可以与单独执行时的训练指令编号相同,在该情况下,也可以是如下方法:利用设置特征指令预先设定切换一并执行模式与单独执行模式的寄存器、及在一并执行模式时使哪个芯片组有效。

[0152]

(第6实施方式)

[0153]

接下来,对第6实施方式的半导体装置1r进行说明。以下,以与第1实施方式~第5实施方式不同的部分为中心进行说明。

[0154]

在第5实施方式中,能够通过1个指令针对每个通道将能够实现dcc的调整动作的指示及确认的芯片数限制在数据信号的比特数以下。例如,在数据信号dq[7∶0]的比特数为8比特的情况下,能够通过1个指令针对每个通道将能够实现dcc的调整动作的指示及确认的芯片数限制在8以下。

[0155]

因此,在第6实施方式中,通过1个指令针对每个通道对多个存储器芯片依次进行dcc锁定完成的状态信息的输出。例如,当某个存储器芯片进行dcc的训练且dcc锁定时,在数据信号dq[7∶0]上输出dcc锁定完成的状态信息(例如芯片id(identifier,识别符))。下一个存储器芯片当识别出在数据信号dq[7∶0]上出现了状态信息时,设为前一个存储器芯片的dcc的训练结束,而进行dcc的训练。此时,某个存储器芯片向数据信号dq[7∶0]输出高阻抗。当dcc锁定时,下一个存储器芯片将状态信息输出到数据信号dq[7∶0]上。针对每个通道对多个存储器芯片依次进行该控制。当从最后的存储器芯片输出状态信息时,接口芯片根据在内部dcc锁定而产生密码,并发送给主机ha。由此,能使能够通过1个指令针对每个通道实现dcc的调整动作的指示及确认的芯片数多于数据信号的比特数。

[0156]

具体来说,如图11所示,在半导体装置1r中,各存储器芯片cp1、cp2的周边电路112c还具有状态监视器(dcc status monitor)电路116c。图11是表示半导体装置1r的构成的图。状态监视电路116c监视通道ch1、ch2中的数据信号dq[7∶0]的状态。

[0157]

将与各通道ch1、ch2连接的存储器芯片数设为n(n为2以上的整数)。例示通道ch1。设为对与通道ch1连接的各存储器芯片cp1-1~cp1-n预先分配芯片编号1-n,按照芯片编号的顺序进行与调整指令相应的dcc的调整动作的进行状况的确认。在存储器芯片cp1中,状态监视电路116c监视前一存储器芯片的密码是否出现在数据信号dq[7∶0]上。当状态监视电路116c监视到前一个存储器芯片的密码出现时,将该监视结果经由指令解码器115通知给锁定状态通知电路117a。锁定状态通知电路117a根据前一个存储器芯片的密码出现在数据信号dq[7∶0]上,在内部dcc锁定后产生密码并输出到驱动器114。驱动器114经由端子组tm1及通道ch1向接口芯片fbi发送该密码。当经过预定时间(例如下一个存储器芯片监视数据信号dq[7∶0]上的密码所需的充分的时间)时,锁定状态通知电路117a将高阻抗输出到驱

动器114。驱动器114将该高阻抗传递到端子组tm1及通道ch1。此外,通道ch2也与通道ch1相同。

[0158]

接口芯片fbi的通道接口109例如能够分时切换通道ch1、ch2和锁定状态通知电路407a的连接。由此,与通道ch1、ch2连接的最后的存储器芯片cp1-n、cp2-n的状态信息能够大致实时地向锁定状态通知电路407a传送。当传送最后的存储器芯片cp1-n、cp2-n的状态信息时,锁定状态通知电路407a根据在内部dcc锁定而产生密码,并输出到驱动器406a。驱动器406a经由节点组n1及端子1a1-7~1a1-0向主机ha发送该密码。由此,主机ha接收到密码,根据该密码,能够识别存储器芯片cp1、cp2及接口芯片fbi中的dcc的锁定完成。

[0159]

例如,执行如图12所示的训练 确认序列sq7-1~sq7-n。图12是表示第6实施方式的半导体装置1r的动作(训练 确认序列sq7)的波形图。以下,关于与通道ch1连接的各存储器芯片cp1-1~cp1-n和接口芯片fbi例示了n=256时的序列,与通道ch2连接的各存储器芯片cp2-1~cp2-n和接口芯片fbi也相同。

[0160]

芯片cp1-1在训练中输出全部为“0”的数据d7-1作为数据信号dq[7∶0],如果训练完成而dcc锁定,则在一定期间内输出芯片id“0x01”作为状态信息cd7-1,之后设为高阻抗(hi-z)。

[0161]

存储器芯片cp1-2在训练中监视数据信号dq[7∶0]的状态,并等待其成为“0x01”(状态信息cd7-1)。

[0162]

存储器芯片cp1-2检测出数据信号dq[7∶0]的“0x00

”→“

0x01”的序列后,如果自身的训练完成,则在一定期间内输出芯片id“0x02”作为状态信息cd7-2,之后设为高阻抗(hi-z)。

[0163]

存储器芯片cp1-2检测出数据信号dq[7∶0]的“0x00

”→“

0x01”的序列后,如果自身的训练未完成,则输出前一个存储器芯片的芯片id“0x01”作为数据d7-2,如果训练完成而dcc锁定,则在一定期间内输出芯片id“0x02”作为状态信息cd7-2,之后设为高阻抗(hi-z)。

[0164]

存储器芯片cp1-3在训练中监视数据信号dq[7∶0]的状态,并等待其成为“0x02”(状态信息cd7-2)。

[0165]

存储器芯片cp1-3检测出数据信号dq[7∶0]的“0x01

”→“

0x02”的序列后,如果自身的训练完成,则在一定期间内输出“0x03”作为状态信息cd7-3,之后设为高阻抗(hi-z)。

[0166]

存储器芯片cp1-3检测出数据信号dq[7∶0]的“0x00

”→“

0x02”的序列后,如果自身的训练未完成,则输出前一个存储器芯片的芯片id“0x02”作为数据d7-3,如果训练完成而dcc锁定,则在一定期间内输出芯片id“0x03”作为状态信息cd7-3,之后设为高阻抗(hi-z)。

[0167]

存储器芯片cp1-256在训练中监视数据信号dq[7∶0]的状态,并等待其成为“0xff”(状态信息cd7-255)。

[0168]

存储器芯片cp1-256检测出数据信号dq[7∶0]的“0xfe

”→“

0xff”的序列后,如果自身的训练完成,则在一定期间内输出“0x00”作为状态信息cd7-256,之后设为高阻抗(hi-z)。

[0169]

存储器芯片cp1-256检测出数据信号dq[7∶0]的“0xfe

”→“

0xff”的序列后,如果自身的训练未完成,则输出前一个存储器芯片的芯片id“0xff”作为数据d7-256,如果训练完成而dcc锁定,则在一定期间内输出芯片id“0x00”作为状态信息cd7-256,之后设为高阻抗(hi-z)。

[0170]

接口芯片fbi在训练中监视数据信号dq[7∶0]的状态,等待其成为“0x00”(状态信息cd7-256)。

[0171]

接口芯片fbi检测出数据信号dq[7∶0]的“0xff

”→“

0x00”的序列后,如果自身的训练完成,则设为通道ch1的所有芯片及自身芯片的dcc的锁定完成,产生密码cd7-all并在一定期间内输出,之后设为高阻抗(hi-z)。

[0172]

存储器芯片cp1-256检测出数据信号dq[7∶0]的“0xff

”→“

0x00”的序列后,如果自身的训练未完成,则继续输出虚拟数据d7-all。关于存储器芯片cp1-256,如果训练完成而dcc锁定,则设为通道ch1的所有芯片及自身芯片的dcc的锁定完成,产生密码cd7-all并在一定期间内输出,之后设为高阻抗(hi-z)。

[0173]

如上所述,在第6实施方式中,通过1个指令针对每个通道对多个存储器芯片依次进行dcc锁定完成的状态信息的输出。由此,能使能够通过1个指令针对每个通道实现dcc的调整动作的指示及确认的芯片数多于数据信号的比特数。

[0174]

此外,接口芯片fbi的通道接口109例如能够分时切换通道ch1、ch2和锁定状态通知电路407a的连接。在该情况下,接口芯片fbi可以针对每个通道ch1、ch2,确认在数据信号dq[7∶0]上是否输出了状态信息cd7-256。接口芯片fbi在将连接切换到通道ch1、ch2的期间,如果在数据信号dq[7∶0]上输出了状态信息cd7-256,则利用锁定状态通知电路407a保存关于与该通道对应的所有存储器芯片表示锁定完成的有效值。锁定状态通知电路407a当内部的dcc、通道ch1的所有存储器芯片cp1的dcc和通道ch2的所有存储器芯片cp2的dcc中的任一个保存有效值时,产生表示在所有芯片中锁定已完成的密码,并输出到驱动器406a。驱动器406a经由节点组n1及端子1a1-7~1a1-0向主机ha发送该密码。由此,主机ha接收密码,根据该密码,能够识别所有芯片中的dcc的锁定已完成。

[0175]

另外,各存储器芯片也可以在自身的序列输出完成的时点停止读取使能信号re-/re的接收等而进入低功耗模式。

[0176]

调整指令cm7也可以与单独执行时的训练指令编号相同,在该情况下,也可以是如下方法:利用设置特征指令预先设定切换一并执行模式与单独执行模式的寄存器、及在一并执行模式时使哪个芯片组有效。

[0177]

虽然说明了本发明的若干个实施方式,但这些实施方式是作为例子而提示的,并不意图限定发明的范围。这些新颖的实施方式能够以其它多种方式实施,能够在不脱离发明的主旨的范围内进行各种省略、置换、变更。这些实施方式及其变化包含在发明的范围和主旨中,并且包含在权利要求书所记载的发明及其均等的范围中。

[0178]

[符号的说明]

[0179]

1、1i、1j、1k、1r

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

半导体装置

[0180]

102、103、118

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

读取用dcc

[0181]

104

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

写入用dcc

[0182]

cp1、cp2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

存储器芯片

[0183]

fbi

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

接口芯片

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。