(一)技术领域:

本发明涉及电力系统自动化领域。尤其涉及一种合并单元用时钟板卡。

(二)

背景技术:

:

随合并单元(mergingunit)为智能电子设备提供一组时间同步(相关)的电流和电压采样值。其主要功能是汇集/或合并多个互感器的输出信号,获取电力系统电流和电压瞬时值,并以确定的数据品质传输到电力系统电气测量仪器和继电保护设备。其每个数据通道可以传送一台或多台的电流和/或电压互感器的采样值数据。

合并单元应能汇集合并电子式电压互感器、电子式电流互感器输出的数字量信号,也可汇集并采样传统电压互感器、电流互感器输出的模拟信号或者电子式互感器输出的模拟小信号,并进行传输。

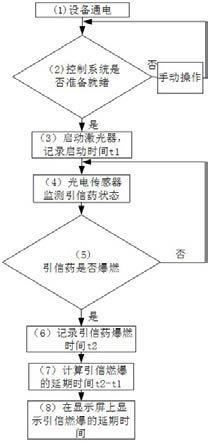

针对电子互感器,较为典型的合并单元及其系统架构如图1所示。由于前端汇集的数据通道较多,因此通道之间的同步问题至关重要。

本板卡可同时接入电力设备常用的同步输入如1pps秒脉冲、irig-b码、1588等方式,同时外挂da和压控晶体振荡器可极大地提高板卡的同步精度和参考消失后的保持时间,提高合并单元运行的稳定性。

(三)

技术实现要素:

:

本实用新型为一种合并单元用时钟板卡,主要由irig-b码/1pps输入接口、以太网1588输入接口、1588phy芯片、fpga、da芯片、压控晶振、cpu、外对时接口、内对时接口等组成,各部分说明如下:

irig-b码/1pps输入接口主要用于接入irig-b码信号;

以太网1588输入接口主要用于接入以太网信号;

1588phy芯片用于保证物理层连接并产生1pps信号。

fpga内部包含四个模块:输入判断选择模块、自计时模块、同步模块、调压模块。其中输入判断选择模块主要用于识别irig-b或外输入的1pps信号以及1588phy产生的1pps信号,判断有效性确认优先级,并输出外接秒脉冲;自计时模块通过外接主时钟产生自计时秒脉冲,并将该脉冲同时输出到fpga的同步模块,外对时接口,内对时接口;同步模块用于将将自计时秒脉冲与输出外接秒脉冲同步;调压模块用于控制外接da芯片以便调节晶振。

da芯片为数模转换芯片,辅助fpga调节压控晶振。

压控晶振可根据调压端的电压微调自身的频率输出范围,主要用于fpga的自计时模块产生自计时秒脉冲。

cpu主要用于管理fpga以及通过mii接口实现以太网连接,以及实现调试串口。

外对时接口的用于输出对时脉冲供其他电力设备同步使用。

内对时接口的用于输出对时脉冲供本合并单元自身使用。

(四)附图说明:

图1典型的合并单元及其系统架构示意图;

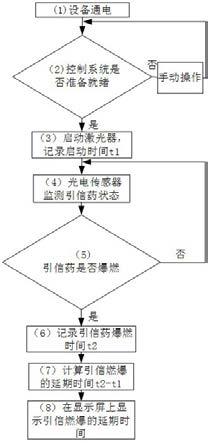

图2板卡结构示意图;

(五)具体实施方式:

为了使本发明的装置、方法、技术方案及优点更加明晰,以下结合附图和实例对本发明作进一步的详细说明。相关领域的技术人员应当理解,此处描述的具体实例仅仅用于理解本发明,并不用于限定本发明。

本实用新型中的板卡结构示意图如图2所示,主要由irig-b码/1pps输入接口、以太网1588输入接口、1588phy芯片、fpga、da芯片、压控晶振、cpu、外对时接口、内对时接口等组成。

其中irig-b码/1pps输入接口直接接入fpga的io连接其内部的输入判断选择模块。

以太网1588输入接口连接板卡的1588phy芯片。

1588phy芯片通过mii接口与cpu的mii接口相连,1588phy产生的1pps信号接入fpga的io连接其内部的输入判断选择模块。

fpga内部分为4个模块,分别为输入判断选择模块、自计时模块、同步模块、调压模块。

其中输入判断选择模块接入irig-b码/1pps输入接口信号和588phy产生的1pps信号,判断有效性确认优先级,并输出外接秒脉冲;本模块能自动识别1pps或irig-b信号,1pps信号则直接输出,irig-b信号则提取其中的ipps信号后再输出,如果两个接口的输入信号同时有效时则需要选择优先使用哪路信号作为外接秒脉冲信号输出。

自计时模块通过外接主时钟产生自计时秒脉冲,并将该脉冲同时输出到fpga的同步模块,外对时接口,内对时接口;输出到同步模块用于将将自计时秒脉冲与输出外接秒脉冲同步,输出到外对时接口的用于其他电力设备同步使用,输出到内对时接口的用于本合并单元自身使用。

同步模块用于将将自计时秒脉冲与输出外接秒脉冲同步,自计时秒脉冲与输出外接秒脉冲进行相位比较,得到正偏差或负偏差传给调压模块。

调压模块利用比较的结果来调节外部da的输入值,从而改变da的输出电压来调节压控晶振;调压模块与da芯片的数字侧接口可以是spi或iic或其他并行接口。

da芯片的数字侧接口与fpga的调压模块相连,模拟侧接口与压控晶振的调压端adj相连。

压控晶振的调压端adj与da芯片的模拟侧相连,时钟输出于fpga的gclk(全局时钟管脚)相连,压控晶振的周边有屏蔽壳体用于防止其周边温度过快变化。

cpu通过l_bus与fpga的mif接口相连,通过mii接口与1588phy芯片通过mii接口相连,通过uart与232phy相连,提供调试串口。

外对时接口的用于输出对时脉冲供其他电力设备同步使用,其为光模块输出与fpga的自计时模块相连。

内对时接口的用于输出对时脉冲供本合并单元自身使用,其为背板接插件输出与fpga的自计时模块相连。

以上所述的仅为本实用新型的较佳实施例,并不用以限制本实用新型,凡在本实用新型的精神和原则之内所作的修改、等同替换和改进等,均应包含在本实用新型的保护范围之内。

技术特征:

1.一种合并单元用时钟板卡,其特征在于:主要由irig-b码/1pps输入接口、以太网1588输入接口、1588phy芯片、fpga、da芯片、压控晶振、cpu、外对时接口、内对时接口等组成;其中irig-b码/1pps输入接口直接接入fpga的io连接;1588phy芯片通过mii接口与cpu的mii接口相连,1588phy产生的1pps信号接入fpga的io连接;da芯片的数字侧接口与fpga的相连,模拟侧接口与压控晶振的调压端adj相连;压控晶振的时钟输出与fpga的全局时钟管脚gclk相连;cpu通过l_bus与fpga的mif接口相连,通过mii接口与1588phy芯片通过mii接口相连,通过uart与232phy相连,提供调试串口。

2.根据权利要求1所述的一种合并单元用时钟板卡,其特征在于:所述的fpga内部包含输入判断选择模块、自计时模块、同步模块、调压模块四个模块。

3.根据权利要求1所述的一种合并单元用时钟板卡,其特征在于:所述的irig-b码/1pps输入接口、以太网1588输入接口、外对时接口均使用光模块作为物理接口。

4.根据权利要求1所述的一种合并单元用时钟板卡,其特征在于:所述的压控晶振可通过调整自身调压端adj的电压微调自身的频率输出范围。

5.根据权利要求1所述的一种合并单元用时钟板卡,其特征在于:所述的压控晶振周边有屏蔽壳体用于防止其周边温度过快变化。

技术总结

本实用新型为一种合并单元用时钟板卡,主要由IRIG‑B码/1PPS输入接口、以太网1588输入接口、1588PHY芯片、FPGA、DA芯片、压控晶振、CPU、外对时接口、内对时接口等组成;其中IRIG‑B码/1PPS输入接口直接接入FPGA的IO连接;1588PHY芯片通过MII接口与CPU的MII接口相连,产生的1PPS信号接入FPGA的IO连接;DA芯片的数字侧接口与FPGA的相连,模拟侧接口与压控晶振的调压端ADJ相连;压控晶振的时钟输出于FPGA的GCLK(全局时钟管脚)相连;CPU通过L_BUS与FPGA的MIF接口相连,通过MII接口与1588PHY芯片通过MII接口相连。本板卡可同时接入电力设备常用的同步输入如1PPS秒脉冲、IRIG‑B码、1588等方式,同时外挂DA和压控晶体振荡器可极大地提高板卡的同步精度和参考消失后的保持时间,提高合并单元运行的稳定性。

技术研发人员:王向东;赵明敬;王杰

受保护的技术使用者:北京贺兰云天科技有限公司

技术研发日:2019.08.28

技术公布日:2020.06.19

本文用于企业家、创业者技术爱好者查询,结果仅供参考。