本发明属于集成电路技术领域,具体涉及时间数字转换器。

背景技术:

时间数字转换器已经使用于许多的混合信号系统中,像是锁相环以及一些进行时间信号处理的电路,这些应用需要时间数字转换器具有高精度、高速以及大的输入范围。目前有许多文献被提出来改进时间数字转换器的性能,在文献[1]中使用的时间数字转换器架构为两步式时间数字转换器,其运作原理为藉由时间数字转换器进行第一次量化后,使用时间放大器将时间余量放大,再使用时间数字转换器进行第二次量化,可以提高整体时间数字转换器的精度,但使用时间放大器会影响整体时间数字转换器的性能。在文献[1]中使用的以锁存器为基础的时间放大器,其增益容易受到制程、温度以及电压(pvt)飘移影响,因此造成时间数字转换器的线性度下降。文献[2]则是使用两条相互依赖的充放电路径作为时间放大器,可以达到比较好的增益控制能力,但他的增益大小以及线性范围仍受到限制。文献[3]提出使用脉冲序列产生器作为时间放大器,但其产生脉冲的过程会产生非线性的特性。文献[1-3]提出不同的时间放大器架构,但仍无法有效的改善时间放大器的非线性问题,因此大多需要设计复杂的校正电路去针对时间放大器造成的增益误差以及非线性特性去改进,此外越复杂的时间放大器或者是校正电路的设计会使电路的延迟越大,导致整体时间数字转换器的转换速度下降。

本发明基于传统的两步式时间数字转换器架构,提出一种简单的动态时间放大器架构去提高整体时间数字转换器的转换速度以及线性度,并降低整体电路消耗功率。本发明的动态时间放大器架构主要使用时间-电压-时间转换过程,其目的是为了藉由转换过程来实现一个放大的效果来达到高线性度,举例来说,当输入时间信号为16ps,且时间放大器增益为16倍,藉由时间电压转换后得到输出电压为850mv,最后由电压时间转换后得到输出时间信号为256ps。此外,动态时间放大器具有采样-保持的特性,因此本发明还可以实现一个流水线的架构,来达到更快的转换速度。

[1]m.leeanda.a.abidi,"a9b,1.25psresolutioncoarse–finetime-to-digitalconverterin90nmcmosthatamplifiesatimeresidue,"inieeejournalofsolid-statecircuits,vol.43,no.4,pp.769-777,april2008.

[2]s.lee,y.seo,h.parkandj.sim,"a1ghzadpllwitha1.25psminimum-resolutionsub-exponenttdcin0.18μmcmos,"inieeejournalofsolid-statecircuits,vol.45,no.12,pp.2874-2881,dec.2010.

[3]k.kim,y.kim,w.yuands.cho,"a7bit,3.75psresolutiontwo-steptime-to-digitalconverterin65nmcmosusingpulse-traintimeamplifier,"inieeejournalofsolid-statecircuits,vol.48,no.4,pp.1009-1017,april2013.。

技术实现要素:

为克服上述现有技术的缺点,本发明提供一种转换速度快、电路功耗低的两步式动态时间数字转换器。

本发明提供的两步式高速动态时间数字转换器,由粗调时间数字转换器(ctdc)、动态时间放大器(dta)、细调时间数字转换器(ftdc)以及解码器(decoder)组成。主要的功能是将时间信号进行两次采样之后得到数字转换结果。当粗调时间数字转换器结束第一次转换后,粗调时间数字转换器中的余量产生器得到第一次转换产生的误差,并由动态时间放大器将误差放大,放大后的误差信号输入至细调时间数字转换器进行第二次的转换,最后将粗调时间数字转换器以及细调时间数字转换器得到的数字结果输入至解码器得到最终数字输出结果。

本发明中,所述的动态时间放大器,由时间电压转换器(tvc)以及电压时间转换器(vtc)组成,它将粗调时间数字转换器产生的余量误差经过时间电压转换器后产生电压信号,最后再将电压信号输入至电压时间转换器,产生一个放大的输出时间信号。动态时间放大器的原理采用时间-电压-时间转换过程产生一个对应的电压以及时间信号来实现时间放大的效果。

本发明中,所述的时间电压转换器,它主要由相位频率侦测器(pfd)以及两条充放电流路径组成,相位频率侦测器包含两个d型触发器以及一个与门,充放电路径包含反相器(inv)、两个开关sw1、sw2和采样电容cs,反相器由p型晶体管mp1和n型晶体管mn1组成。在充放电流路径中,反相器在输入信号up/dn为0,sw1关闭且sw2打开时,电压节点vsp/vsn充电至vdd;输入信号up/dn为1,sw1关闭且sw2打开时,mn1导通,使得电压节点vsp/vsn放电至gnd。在整个转换过程中只有在输入信号up/dn为1,sw1关闭且sw2打开的这个状态下才会产生电流,因此可以节省静态功率的消耗。

本发明中,所述的电压时间转换器,它为一个传统的动态放大器架构,主要由两个p型晶体管(mp2、mp3)和四个n型晶体管(mn2-mn5)以及负载电容(cl)和反相器依序组成。运作原理为根据两输入电压的大小产生两种不同大小的电流分别对两负载电容放电,并由反相器将电压信号转成时间信号。其中mn2用来进行对电压时间转换器的转换增益进行校正,使得动态时间放大器具有稳定的增益。

本发明中,所述的动态时间放大器,除了具有稳定增益以及高线性度的特性以外,还利用采样-保持的功能进行时间-电压-时间转换,所以两步式高速时间数字转换器还可以实现一种流水线架构,以达到更快的转换速度。

本发明中,所述细调数字转换器,使用一位冗余位来降低失调带来的影响,因此校正电路只需要针对时间放大器增益进行一次校正,以简化了校正电路的复杂度。

本发明的技术效果为,该两步式高速时间数字转换器藉由动态时间数字转换器,将粗调时间数字转换器产生的余量误差放大,并由细调时间数字转换器进行第二次转换,以提高整体时间数字转换器的精度。此外动态时间数字转换器的使用使得两步式高速时间数字转换器可以实现流水线的架构来达到更快的转换速度,和降低整体电路的静态消耗功率。

附图说明

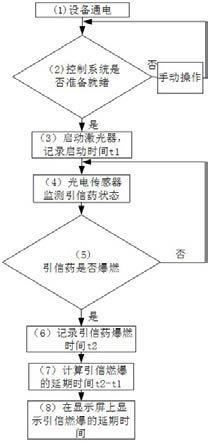

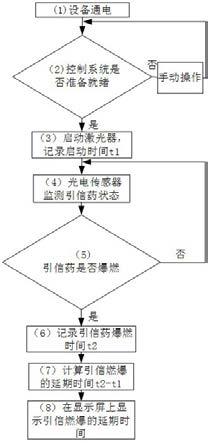

图1是本发明的两步式高速动态时间数字转换器架构以及时序图。

图2是本发明的两步式高速动态时间数字转换器时序图。

图3是本发明的动态时间放大器架构图。

图4是本发明的动态时间放大器时序图。

图中标号:ctdc为粗调时间数字转换器,dta为动态时间放大器,tvc为时间电压转换器,vtc为电压时间转换器,ftdc为细调时间数字转换器,decoder为译码器,start和stop为输入时间信号,f_start和f_stop为ctdc输出余量信号,vop和von为tvc输出电压信号,toutp和toutn为vtc输出时间信号,t[47:0]为ctdc和ftdc输出数字信号,dout[7:0]为整体电路的输出信号,1stcoarseconv.和2ndcoarseconv.分别为第一次以及第二次ctdc转换阶段,1stresidualamp.和2ndresidualamp.分别为第一次以及第二次dta放大时间信号阶段,1stfineconv.和2ndfineconv.分别为第一次以及第二次ftdc转换阶段,1stdigitalcalc.为第一次decoder输出阶段tin为输入信号的时间差,tres为ctdc的余量误差,vd为tvc将余量时间信号转换成的电压差,tamp为放大后的时间差,vdd为电源电压,pfd为相位频率侦测器,inv为反相器,sw1和sw2为充放电控制开关,cs为采样电容,mn1-5为n型晶体管,mp1-3为p型晶体管,cl为负载电容,up和dn为pfd输出信号,cks1和cks2为控制开关的时钟,vsp和vsn为采样电容放电后的电压信号,vop和von为tvc的输出信号,voutp和voutn为负载电容放电后的电压信号,ckp为将voutp和voutn还原至vdd的信号,vgain为控制vtc校正的信号,toutp和toutn为vtc的输出信号,vth为反相器的门槛电压,gnd为接地信号。

具体实施方式

在下文中结合图示在参考实施例中更完全地描述本发明,本发明提供优选实施例,但不应该被认为仅限于在此阐述的实施例。

图1显示了本发明的电路架构图,本发明为一种两步式高速时间数字转换器,主要是由粗调时间数字转换器、动态时间放大器、细调时间数字转换器以及解码器组成。本发明所使用的粗调时间数字转换器以及细调时间数字转换器为传统的闪存时间数字转换器,译码器则是使用verilog代码综合的数字电路,本发明的核心架构在于动态时间放大器,主要由时间电压转换器以及电压时间转换器组成。两步式高速时间数字转换器的运作时序图如图2,在第一次粗调转换阶段,当两个输入时间信号start和stop(时间差为tin)输入至ctdc,经过采样后可以得到输出数字码t[47:32]以及输出余量信号f_start和f_stop(两者时间差为余量时间tres),之后电路工作在第一次余量放大阶段,余量时间tres进行时间电压转换后为余量电压vd,最后vd经过电压时间转换器变为放大后的时间差tamp,本发明的动态时间放大器增益为16,因此放大后的时间差tamp为余量时间差tres的16倍。当余量放大阶段完成后,tamp输入至ftdc进行细调转换得到t[31:0],最后ctdc和ftdc输出数字信号t[47:0]输入至译码器中进行计算得到输出dout[7:0]。本发明可以实现流水线操作,于是当第一个时间差tin在粗调时间数字转换器完成转换后输入至动态时间放大器之后,粗调时间转换器就可以处理下一个tin,不需要等到第一个tin完成细调时间数字转换并得到整体电路的数字输出结果。当一个tin完成从粗调转换、放大、细调转换到输出需要经过四个时钟周期,但由于流水线的实现,本发明只需要两个时钟周期来完成所有的工作,因此可以提高大约两倍的转换速度。

图3为本发明的动态时间放大器架构图,动态时间放大器主要由tvc以及vtc组成,其中tvc由相位频率侦测器(pfd)以及两条充放电流路径组成,相位频率侦测器包含两个d型触发器以及一个与门,充放电路径包含反相器(inv)、两个开关sw1、sw2和采样电容cs,反相器由p型晶体管mp1和n型晶体管mn1组成;而vtc为一个传统的动态放大器架构,主要由两个p型晶体管(mp2-、mp3)、四个n型晶体管(mn2-mn5)以及负载电容(cl)和反相器依序组成。动态时间放大器电路工作流程如图4所示,当两输入时间信号f_start和f_stop(两输入时间信号差为tin)经过pfd时会产生up和dn输出信号,其中dn信号由pfd中的与门延迟产生,用来避免pfd进入死区而导致输出产生误差,up信号包含时间差tin和dn信号的延时,cks1和cks2为非交迭时钟。up和dn进入反相器后,此时控制开关信号cks1为1,cks2为0,控制开关sw1关闭,sw2打开,因此vsp和vsn电压开始以等速率放电至gnd,等到cks2为1,cks1为1,控制开关sw2关闭,sw1打开时,vsp和vsn电压输出至vop和von,得到转换后的余量电压vd。ckp为vtc的控制信号,当ckp为0时,voutp和voutn被还原至vdd,当ckp为1时,vtc根据输入电压信号vop和von产生不同的电流,因此voutp和voutn会以不同的速率放电至gnd。当voutp和voutn的电压低于反相器的门坎电压时,反相器的输出toutp和toutn由0改变至1,而toutp和toutn两信号之间的时间差tamp即为余量时间差放大后的结果。nmos管mn1主要用来进行动态时间放大器的增益校正,当动态时间放大器增益不匹配时,校正电路会检测ftdc输出数字结果的最大值与最小值,并求出ftdc输出的范围,以及和理想输出范围的数字差值,举例来说,ftdc为4位闪存时间数字转换器,于是在理想状况下ftdc最大的输出数字结果为15,最小为0,因此理想输出范围为15。将ctdc输出范围与理想输出范围相减得到差值后,藉由数字模拟转换器将差值转为模拟信号vgain调整vop和von产生的电流大小。

本发明的两步式高速时间数字转换器,主要是藉由动态时间放大器来提高时间数字转换器的线性度以及转换速度,此外,本发明结合一位冗余位来消除数字偏差的产生,因此可以简化校正电路对时间动态放大器的增益进行校正,降低校正电路所需要消耗的功率,以达到低功耗的设计。本发明可应用在数字锁相回路的设计中,提高数字锁相回路的整体性能。

以上通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

本文用于企业家、创业者技术爱好者查询,结果仅供参考。