1.本发明涉及用于调制光辐射的电光调制器和方法。

背景技术:

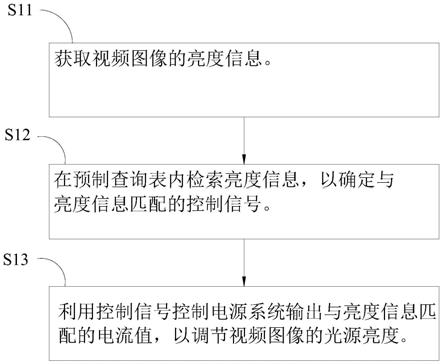

::2.由于数据业务和带宽需求上的不断增长,迫切需要更快的光互连。这进而又导致对低功率高速光收发器的需求不断增加。为了满足这一需求,向诸如多级信令的高级调制格式的转变似乎很有希望。例如,4级脉冲幅度调制(pam4)信号需要典型不归零(nrz)信号的带宽的一半。3.然而,众所周知,多级信令对组件的线性度更敏感。在光学系统中,电光调制器通常是最非线性的元件,因为它的传递函数通常强烈依赖偏置和电压,因此生成干净的pam4眼图经常需要耗电电子数模转换器(dac)或电信号的预失真以产生等距的光电平。4.为了缓解这些问题,可以将调制器布置在2比特光学dac配置中,如w.huang等人的下文中所述:题为“opticaldacforgenerationofpam4usingparallelelectro‑absorptionmodulators(使用并联电吸收调制器生成pam4的光学dac)”ecoc2016;第42届欧洲光通信会议,德国杜塞尔多夫,2016年,第1‑3页)。这种方法——其中采用每个调制器来创建二进制nrz信号——允许绕过调制器的非线性,从而从发射器侧消除线性约束——在电气域和光域中——并使得能够使用更简单的低功耗nrz驱动器拓扑。5.如美国专利第8,320,720b2号中所示,类似的方法可用于除pam4之外的各种高级调制格式。技术实现要素:6.本发明的目的7.本发明的一个目的是提供一种用于调制光辐射的改进的电光调制器。8.本发明的另一个目的是提供一种改进的调制光辐射的方法。9.发明简述10.本发明的示例性实施例涉及一种用于调制光辐射的电光调制器,其包括至少一个上游调制子单元、至少一个下游调制子单元和至少一个相位匹配单元。上游和下游调制子单元光学地串联连接,使得光辐射在通过上游调制子单元之后通过下游调制子单元。上游调制子单元包括上游电极,其中,上游电极的近端适于接收电上游调制信号并且位于其中辐射进入上游调制子单元的光学上游部分中。上游电极的远端位于其中辐射离开上游调制子单元的光学下游部分中。下游调制子单元包括下游电极。下游电极的近端适于接收电下游调制信号并位于其中辐射进入下游调制子单元的光学上游部分中。下游电极的远端位于其中辐射离开下游调制子单元的光学下游部分中。相位匹配单元被配置为延迟下游调制信号,使得在上游电极的远端处的上游调制信号与在下游电极的近端处的下游调制信号之间的相位差最小。11.相位匹配单元优选地包括被配置为响应于控制信号延迟下游调制信号的可调延迟线。12.相位匹配单元的相位检测器优选地连接到上游电极的远端和下游电极的近端。相位检测器可以被配置为产生指示在远端与近端之间的相位差的控制信号。13.第一单稳态电路优选地被布置在上游电极的远端和相位检测器的第一输入端口之间。14.第二单稳态电路优选地被布置在下游电极的远端和相位检测器的第二输入端口之间。15.低通滤波器优选地被布置在相位检测器的输出端口和可调延迟线的输入端口之间。16.可调延迟线可以是数控延迟线。17.模数转换器可以被布置在低通滤波器的输出端口和数控延迟线的输入端口之间。18.调制子单元优选地是相位调制器、幅度调制器、偏振调制器、注入调制器或耗尽调制器。19.调制单元可以提供任何类型的驱动方案(例如分段驱动器、行波电极、分段行波电极等...)。20.电驱动器优选地被分配给下游调制子单元。驱动器可以被配置为接收电输入信号并且生成用于下游调制子单元的电下游调制信号。21.驱动器优选地电气地布置在可调延迟线和下游电极的近端之间。22.驱动器和调制子单元优选地被集成在同一芯片上。可调延迟线也可以被集成在同一芯片上。23.在另一个优选实施例中,驱动器和调制子单元可以被集成在同一个芯片上,并且可调延迟线可以被集成在另一个芯片上。24.驱动器优选地被配置为处理(接收和发送)差分和/或非差分输入信号。25.取决于驱动器的输出接口是单端还是差分端的,分配的调制子单元优选地包括单个电极(在非差分输入信号的情况下)或两个电极(在差分输入信号的情况下)。26.控制器可以被配置为间歇地激活和停用相位匹配单元并且以补偿周期操作相位匹配单元。27.在后一实施例中,模数转换器优选地被布置在低通滤波器的输出端口和可调延迟线的输入端口之间。可调延迟线优选地是数控延迟线。模数转换器优选地被配置为在相位匹配单元的停用期间存储其数字值并输出所存储的值,直到在下一个补偿周期中由低通滤波器提供新的模拟值。28.电光调制器可以包括串联布置的多个调制子单元,以及多个相位匹配单元。除了调制子单元系列中的最后一个之外,每个调制子单元优选地是由后一调制子单元和连续的下游调制子单元形成的一对调制子单元中的上游调制子单元。相位匹配单元优选地被分配给每对调制子单元。每个相位匹配单元优选地被配置为延迟施加到各个下游调制子单元的下游调制信号,使得在上游调制子单元的上游电极的远端处的上游调制信号与在下游调制子单元的下游电极的近端处的下游调制信号之间的相位差最小。29.可以为每个调制子单元分配一个电驱动器。每个驱动器可以被配置为接收电输入信号并且生成用于各个调制子单元电调制信号。30.对于除了调制子单元系列中的第一个之外的每个调制子单元,驱动器优选地电气地被设置在各个调制子单元的电极的近端与所分配的相位匹配单元的可调延迟线之间。31.本发明的另一实施例涉及一种基于光输入辐射生成调制光输出辐射的方法,该方法包括下述步骤:在至少一个上游调制子单元处接收输入辐射,在至少一个上游调制子单元中调制辐射,然后在连续的下游调制子单元中再次调制辐射,32.其中,至少一个上游调制子单元包括上游电极,其中,上游电极的近端接收电上游调制信号并且位于其中辐射进入上游调制子单元的光学上游部分中,并且其中,上游电极的远端位于其中辐射离开上游调制子单元的上游调制子单元的光学下游部分中,33.其中,连续下游调制子单元包括下游电极,其中,下游电极的近端接收电下游调制信号并且位于其中辐射进入下游调制子单元的光学上游部分中,并且其中,下游电极的远端位于其中辐射离开下游调制子单元的下游调制子单元的光学下游部分中,并且34.其中,下游调制信号被延迟,使得上游电极的远端处的上游调制信号和下游相应电极的近端处的下游调制信号之间的相位差最小。附图说明35.为了容易理解获得本发明的上述和其他优点的方式,将通过参考附图中示出的本发明的具体实施例来对以上简要描述的本发明进行更具体的描述。要理解,这些附图仅描绘了本发明的典型实施例并且因此不应被认为是对其范围的限制,将通过使用附图以额外的具体性和细节来描述和解释本发明,在附图中,36.图1示出了根据本发明的电光调制器的第一示例性实施例,其中,可调延迟线是模拟延迟线;37.图2示出了根据本发明的电光调制器的第二示例性实施例,其中,可调延迟线是数控延迟线。38.图3示出了根据本发明的电光调制器的第三示例性实施例,其中,数字控制器提供节能模式;39.图4示出了根据本发明的电光调制器的第四示例性实施例,其中,可调延迟线集成在单独的芯片上。40.图5示出了根据本发明的电光调制器的第五示例性实施例,其中,调制器包括多个级联调制子单元;以及41.图6图示了根据本发明的电光调制器的第六示例性实施例,其中,驱动器和调制子单元基于差分信号操作。具体实施方式42.参考附图将最好地理解本发明的优选实施例。将容易理解的是,如本文附图中一般描述和图示的,本发明可以在较宽的范围内变化。因此,如附图中所表示的本发明的示例性实施例的以下更详细描述并非旨在限制所要求保护的本发明的范围,而仅代表本发明的当前优选实施例。43.图1示出了根据本发明的电光调制器eom的第一示例性实施例。电光调制器eom被配置为调制光辐射r,包括第一调制子单元mod1、第二调制子单元mod2和相位匹配单元pmu。44.第一和第二调制子单元光学地串联连接,使得光辐射r在通过第一调制子单元之后通过第二调制子单元。因此,第一调制子单元在下文中被称为上游调制子单元mod1,第二调制子单元在下文中被称为下游调制子单元mod2。45.上游调制子单元mod1包括上游电极e1。上游电极e1的近端11适于接收电上游调制信号sm1并且位于其中辐射r进入上游调制子单元mod1的光上游部分21中。上游电极e1的远端12位于其中辐射r离开上游调制子单元mod1的光学下游部分22中。46.下游调制子单元mod2包括下游电极e2。下游电极e2的近端11适于接收电下游调制信号sm2。近端11位于其中辐射r进入下游调制子单元mod2的光上游部分21中。下游电极e2的远端12位于其中辐射r离开下游调制子单元mod2的光学下游部分22中。47.相位匹配单元pmu被配置为延迟下游调制信号sm2,使得上游电极e1的远端12处的上游调制信号sm1与下游电极e2的近端11处的下游调制信号sm2之间的相位差最小。48.在图1的示例性实施例中,相位匹配单元pmu包括第一单稳态电路(monostable)mst1、第二单稳态电路mst2、相位检测器phd、低通滤波器lpf和可调延迟线dl。49.第一单稳态电路mst1布置在上游电极e1的远端12与相位检测器phd的第一输入端口之间。第二单稳态电路mst2布置在下游电极e2的远端12和相位检测器phd的第二输入端口之间。50.由于相位匹配单元pmu的相位检测器phd(经由单稳态电路mst1、mst2)连接到上游电极e1的远端12和下游电极e2的近端11,相位检测器phd可以产生输出信号,其指示远端和近端11、12处的信号之间的相位差。相位检测器phd的输出信号控制可调延迟线dl并且在下文中被称为控制信号cs。51.如图1所示,低通滤波器lpf优选地布置在相位检测器phd的输出端口和可调延迟线dl的输入端口之间。优选地选择低通滤波器lpf的截止频率使得闭环极点比数据速率慢至少四个数量级。52.在图1的示例性实施例中,电驱动器dr1、dr2被分配给上游调制子单元mod1和下游调制子单元mod2。第一驱动器dr1被配置为接收第一电输入信号s1并产生用于上游调制子单元mod1的电上游调制信号sm1。第二驱动器dr2被配置为接收第二电输入信号s2并且产生用于下游调制子单元mod2的电下游调制信号sm2。53.在图1的示例性实施例中,第二驱动器dr2电气地布置在可调延迟线dl和下游电极e2的近端之间。因此,可调延迟线dl可以补偿由第一驱动器dr1和第二驱动器dr2引起的不等延迟。54.可以操作图1的电光调制器eom以基于两个比特生成pam4信号,该两个比特此后称为最高有效位(msb)和最低有效位(lsb)。上游调制信号sm1可用于输入msb,下游信号可用于输入lsb,或反之亦然。55.产生pam4信号的一个关键问题是上游调制信号sm1和下游调制信号sm2之间的差分偏斜控制。在图1的示例性实施例中,上游调制子单元mod1中光的有限传播速度可以引入与其长度成比例的延迟,使得——为了产生理想的pam4信号——电下游调制信号sm2优选地偏斜等于由上游调制子单元mod1引入的延迟的量。这种偏斜可以由可调延迟线dl产生。与理想偏斜的任何偏差都可能导致pam4信号的严重劣化。这对于高速信号——例如,对于pam456g串行链路——非常明显。56.更一般地,如果我们用td1、tm1、tdelay、td2指示第一驱动器dr1、上游调制子单元mod1、延迟线dl和第二驱动器dr2分别引入的延迟,为了产生理想的pam4信号,则以下等式必须成立:57.td1 tm1=td2 tdelayꢀꢀꢀꢀꢀꢀꢀ(1)58.在理想情况下,驱动器延迟是相等的,等式(1)变为:59.tm1=tdelayꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ(2)60.实际上,虽然光学延迟在工艺、温度和操作条件下是稳定的,但由于工艺不匹配——其引起静态差分偏斜——和工作条件(诸如电压、温度、设置)——其可能会不断变化——这两者导致第一和第二驱动器dr1、dr2引入的延迟可能不同,从而导致动态差分偏斜。61.即使通过适当校准延迟线dl可以消除静态差分偏斜,动态偏斜仍然没有得到补偿,因此基本上可以将等式(2)重写为:62.tm1=tdelay δtd(t)ꢀꢀꢀꢀ(3)63.其中,δtd(t)表示驱动器dr1、dr2之间的时间相关偏斜。64.在图1的示例性实施例中,由相位检测器phd和可调延迟线dl提供的延迟补偿回路可以自动补偿静态和动态差分偏斜两者,为多电平信号提供最佳性能。为此,电下游链路调制信号可以与光信号相位匹配。更具体地,由上游调制子单元mod1引入的光延迟在电平处——在上游调制子单元mod1的电极的远端12处和在下游调制子单元mod2的电极的近端11处——被感测。线性相位检测器phd比较两端处的电信号之间的偏斜,产生对应的控制信号cs。该信号优选地被低通滤波,然后用于控制可调延迟线dl,以便对齐电下行链路和上行链路调制信号sm1、sm2。由于所提出的延迟补偿回路使用随机数据流工作,所以单稳态电路mst1、mst2优选地存在于相位检测器phd的前方以便产生有限持续时间的脉冲。65.可调延迟线dl优选地在路径中生成可变偏斜δtdelay(t),以便:66.tm1=tdelay δtdelay(t) δtd(t)ꢀꢀꢀ(4)67.换句话说,延迟补偿环路的目的是修改可变偏斜以便消除信号路径中的任何延迟差异,使得:68.δtdelay(t) δtd(t)=0ꢀꢀꢀꢀ(5)69.延迟补偿回路可以仅由模拟块组成,如图1的示例性实施例所示,或者另外或替代地包括数字电路。图2、3和4中示出了还包括数字电路的示例性实施方式。70.在图2的示例性实施例中,相位检测器phd的低通滤波的输出信号由模数转换器adc数字化,模数转换器adc的输出控制数控延迟线dl。71.由于典型的动态变化发生非常缓慢,因此可以在低占空比模式下周期性地启用补偿回路,以便降低电流消耗,对芯片功耗具有可忽略不计的影响。例如,控制器(如图3所示)可以被配置为间歇地激活和停用相位匹配单元pmu(例如单稳态电路mst1、mst2、相位检测器phd和/或低通滤波器lpf)并且在补偿周期中运行相位匹配单元pmu。模数转换器优选地被配置为在相位匹配单元pmu停用期间存储其数字值并输出所存储的值,直到在下一个补偿周期中由低通滤波器lpf提供新的模拟值。72.在图1、2和3的示例性实施例中,驱动器dr1、dr2和调制子单元以及可调延迟线dl优选地集成在同一芯片上。73.替代地,如图4所示,驱动器dr1、dr2和调制子单元mod1、mod2可以集成在同一芯片上,而可调延迟线dl可以集成在另一芯片上。这里,低通滤波器lpf输出由模数转换器adc数字化,并经由数字接口传递到外部数控延迟线dl。74.通过进一步的示例,图5示出了上面参考图1‑4描述的操作的原理也可以扩展到任何其他调制方案,其中,不同比特或信道之间的精确延迟是有利的。例如,如图5所示,该方法可以在pam‑16调制方案中实现。75.在图5的示例性实施例中,电光调制器eom包括串联布置的多个调制子单元和多个相位匹配单元。除了调制子单元系列中的最后一个之外的每个调制子单元都是由后一调制子单元和连续的下游调制子单元形成的一对调制子单元中的上游调制子单元。相位匹配单元被分配给每对调制子单元。每个相位匹配单元优选地被配置为延迟施加到各个下游调制子单元的下游调制信号,使得在上游调制子单元的上游电极的远端处的上游调制信号与在下游调制子单元的下游电极的近端处的下游调制信号之间的相位差是最小的。76.关于延迟,上面参考图1的解释对应地适用于每对调制子单元。77.在图5的示例性实施例中,电驱动器被分配给每个调制子单元。每个驱动器被配置为接收电输入信号并且为相应的调制子单元生成电调制信号。对于除了调制子单元系列中的第一个之外的每个调制子单元,驱动器电气地布置在各个调制子单元的电极的近端与分配的相位匹配单元的可调延迟线之间。78.上面通过示例描述的操作原理可以应用于任何类型的光调制器(例如相位调制器、幅度调制器、偏振调制器、注入调制器、耗尽调制器等...)和任何类型的驱动方案(例如分段驱动器、行波电极、分段行波电极等...)。79.如果不存在额外的寄生元件,诸如焊盘/导线杂散电容和电感——其否则会降低调制器电极上的rf信号并干扰在到延迟补偿回路电路的高速连接上的传播延迟,则驱动器和光电调制器的协同集成通常可以提供最佳性能。80.出于说明的目的,图1‑5的示例性实施例示出了基于非差分信号运行的驱动器和调制子单元。当然,驱动器也可以被配置为接收和处理差分信号。在这种情况下,调制子单元优选地被配置为接收差分信号并基于差分调制信号调制辐射。为此,调制子单元可以包括优选地并联布置的两个电极。上述相位匹配单元可以连接到上述两个电极中的任何一个并与其一起操作。图6示出了基于差分信号的电光调制器eom的示例性实施例。81.本文公开的本发明的实施例的各种实施例和方面不仅应在本说明书中具体描述的顺序和上下文中被理解,而且包括任何顺序及其任何组合。每当上下文需要时,所有以单数形式使用的词语均应视为包括复数形式,反之亦然。没当上下文需要时,所有带有“和”字样的选项都应被视为包括词“或”(反之亦然)以及它们的任何组合。82.在附图和说明书中,已经公开了本发明的多个实施例。申请人想强调的是,每个实施例的每个特征都可以与任何其他实施例组合或添加到任何其他实施例中,以便修改相应实施例并创建附加实施例。这些附加实施例构成本公开的一部分,因此,申请人可以在审查的后期阶段提交关于这些附加实施例的另外的专利权利要求。83.此外,申请人想强调的是,每个所附从属权利要求的每个特征可以与任何当前独立权利要求以及任何其他(一个或多个)当前从属权利要求组合(无论本权利要求结构如何)。84.因此,申请人可以在审查的后期将进一步的专利权利要求引向其他权利要求组合。当前第1页12当前第1页12

背景技术:

::2.由于数据业务和带宽需求上的不断增长,迫切需要更快的光互连。这进而又导致对低功率高速光收发器的需求不断增加。为了满足这一需求,向诸如多级信令的高级调制格式的转变似乎很有希望。例如,4级脉冲幅度调制(pam4)信号需要典型不归零(nrz)信号的带宽的一半。3.然而,众所周知,多级信令对组件的线性度更敏感。在光学系统中,电光调制器通常是最非线性的元件,因为它的传递函数通常强烈依赖偏置和电压,因此生成干净的pam4眼图经常需要耗电电子数模转换器(dac)或电信号的预失真以产生等距的光电平。4.为了缓解这些问题,可以将调制器布置在2比特光学dac配置中,如w.huang等人的下文中所述:题为“opticaldacforgenerationofpam4usingparallelelectro‑absorptionmodulators(使用并联电吸收调制器生成pam4的光学dac)”ecoc2016;第42届欧洲光通信会议,德国杜塞尔多夫,2016年,第1‑3页)。这种方法——其中采用每个调制器来创建二进制nrz信号——允许绕过调制器的非线性,从而从发射器侧消除线性约束——在电气域和光域中——并使得能够使用更简单的低功耗nrz驱动器拓扑。5.如美国专利第8,320,720b2号中所示,类似的方法可用于除pam4之外的各种高级调制格式。技术实现要素:6.本发明的目的7.本发明的一个目的是提供一种用于调制光辐射的改进的电光调制器。8.本发明的另一个目的是提供一种改进的调制光辐射的方法。9.发明简述10.本发明的示例性实施例涉及一种用于调制光辐射的电光调制器,其包括至少一个上游调制子单元、至少一个下游调制子单元和至少一个相位匹配单元。上游和下游调制子单元光学地串联连接,使得光辐射在通过上游调制子单元之后通过下游调制子单元。上游调制子单元包括上游电极,其中,上游电极的近端适于接收电上游调制信号并且位于其中辐射进入上游调制子单元的光学上游部分中。上游电极的远端位于其中辐射离开上游调制子单元的光学下游部分中。下游调制子单元包括下游电极。下游电极的近端适于接收电下游调制信号并位于其中辐射进入下游调制子单元的光学上游部分中。下游电极的远端位于其中辐射离开下游调制子单元的光学下游部分中。相位匹配单元被配置为延迟下游调制信号,使得在上游电极的远端处的上游调制信号与在下游电极的近端处的下游调制信号之间的相位差最小。11.相位匹配单元优选地包括被配置为响应于控制信号延迟下游调制信号的可调延迟线。12.相位匹配单元的相位检测器优选地连接到上游电极的远端和下游电极的近端。相位检测器可以被配置为产生指示在远端与近端之间的相位差的控制信号。13.第一单稳态电路优选地被布置在上游电极的远端和相位检测器的第一输入端口之间。14.第二单稳态电路优选地被布置在下游电极的远端和相位检测器的第二输入端口之间。15.低通滤波器优选地被布置在相位检测器的输出端口和可调延迟线的输入端口之间。16.可调延迟线可以是数控延迟线。17.模数转换器可以被布置在低通滤波器的输出端口和数控延迟线的输入端口之间。18.调制子单元优选地是相位调制器、幅度调制器、偏振调制器、注入调制器或耗尽调制器。19.调制单元可以提供任何类型的驱动方案(例如分段驱动器、行波电极、分段行波电极等...)。20.电驱动器优选地被分配给下游调制子单元。驱动器可以被配置为接收电输入信号并且生成用于下游调制子单元的电下游调制信号。21.驱动器优选地电气地布置在可调延迟线和下游电极的近端之间。22.驱动器和调制子单元优选地被集成在同一芯片上。可调延迟线也可以被集成在同一芯片上。23.在另一个优选实施例中,驱动器和调制子单元可以被集成在同一个芯片上,并且可调延迟线可以被集成在另一个芯片上。24.驱动器优选地被配置为处理(接收和发送)差分和/或非差分输入信号。25.取决于驱动器的输出接口是单端还是差分端的,分配的调制子单元优选地包括单个电极(在非差分输入信号的情况下)或两个电极(在差分输入信号的情况下)。26.控制器可以被配置为间歇地激活和停用相位匹配单元并且以补偿周期操作相位匹配单元。27.在后一实施例中,模数转换器优选地被布置在低通滤波器的输出端口和可调延迟线的输入端口之间。可调延迟线优选地是数控延迟线。模数转换器优选地被配置为在相位匹配单元的停用期间存储其数字值并输出所存储的值,直到在下一个补偿周期中由低通滤波器提供新的模拟值。28.电光调制器可以包括串联布置的多个调制子单元,以及多个相位匹配单元。除了调制子单元系列中的最后一个之外,每个调制子单元优选地是由后一调制子单元和连续的下游调制子单元形成的一对调制子单元中的上游调制子单元。相位匹配单元优选地被分配给每对调制子单元。每个相位匹配单元优选地被配置为延迟施加到各个下游调制子单元的下游调制信号,使得在上游调制子单元的上游电极的远端处的上游调制信号与在下游调制子单元的下游电极的近端处的下游调制信号之间的相位差最小。29.可以为每个调制子单元分配一个电驱动器。每个驱动器可以被配置为接收电输入信号并且生成用于各个调制子单元电调制信号。30.对于除了调制子单元系列中的第一个之外的每个调制子单元,驱动器优选地电气地被设置在各个调制子单元的电极的近端与所分配的相位匹配单元的可调延迟线之间。31.本发明的另一实施例涉及一种基于光输入辐射生成调制光输出辐射的方法,该方法包括下述步骤:在至少一个上游调制子单元处接收输入辐射,在至少一个上游调制子单元中调制辐射,然后在连续的下游调制子单元中再次调制辐射,32.其中,至少一个上游调制子单元包括上游电极,其中,上游电极的近端接收电上游调制信号并且位于其中辐射进入上游调制子单元的光学上游部分中,并且其中,上游电极的远端位于其中辐射离开上游调制子单元的上游调制子单元的光学下游部分中,33.其中,连续下游调制子单元包括下游电极,其中,下游电极的近端接收电下游调制信号并且位于其中辐射进入下游调制子单元的光学上游部分中,并且其中,下游电极的远端位于其中辐射离开下游调制子单元的下游调制子单元的光学下游部分中,并且34.其中,下游调制信号被延迟,使得上游电极的远端处的上游调制信号和下游相应电极的近端处的下游调制信号之间的相位差最小。附图说明35.为了容易理解获得本发明的上述和其他优点的方式,将通过参考附图中示出的本发明的具体实施例来对以上简要描述的本发明进行更具体的描述。要理解,这些附图仅描绘了本发明的典型实施例并且因此不应被认为是对其范围的限制,将通过使用附图以额外的具体性和细节来描述和解释本发明,在附图中,36.图1示出了根据本发明的电光调制器的第一示例性实施例,其中,可调延迟线是模拟延迟线;37.图2示出了根据本发明的电光调制器的第二示例性实施例,其中,可调延迟线是数控延迟线。38.图3示出了根据本发明的电光调制器的第三示例性实施例,其中,数字控制器提供节能模式;39.图4示出了根据本发明的电光调制器的第四示例性实施例,其中,可调延迟线集成在单独的芯片上。40.图5示出了根据本发明的电光调制器的第五示例性实施例,其中,调制器包括多个级联调制子单元;以及41.图6图示了根据本发明的电光调制器的第六示例性实施例,其中,驱动器和调制子单元基于差分信号操作。具体实施方式42.参考附图将最好地理解本发明的优选实施例。将容易理解的是,如本文附图中一般描述和图示的,本发明可以在较宽的范围内变化。因此,如附图中所表示的本发明的示例性实施例的以下更详细描述并非旨在限制所要求保护的本发明的范围,而仅代表本发明的当前优选实施例。43.图1示出了根据本发明的电光调制器eom的第一示例性实施例。电光调制器eom被配置为调制光辐射r,包括第一调制子单元mod1、第二调制子单元mod2和相位匹配单元pmu。44.第一和第二调制子单元光学地串联连接,使得光辐射r在通过第一调制子单元之后通过第二调制子单元。因此,第一调制子单元在下文中被称为上游调制子单元mod1,第二调制子单元在下文中被称为下游调制子单元mod2。45.上游调制子单元mod1包括上游电极e1。上游电极e1的近端11适于接收电上游调制信号sm1并且位于其中辐射r进入上游调制子单元mod1的光上游部分21中。上游电极e1的远端12位于其中辐射r离开上游调制子单元mod1的光学下游部分22中。46.下游调制子单元mod2包括下游电极e2。下游电极e2的近端11适于接收电下游调制信号sm2。近端11位于其中辐射r进入下游调制子单元mod2的光上游部分21中。下游电极e2的远端12位于其中辐射r离开下游调制子单元mod2的光学下游部分22中。47.相位匹配单元pmu被配置为延迟下游调制信号sm2,使得上游电极e1的远端12处的上游调制信号sm1与下游电极e2的近端11处的下游调制信号sm2之间的相位差最小。48.在图1的示例性实施例中,相位匹配单元pmu包括第一单稳态电路(monostable)mst1、第二单稳态电路mst2、相位检测器phd、低通滤波器lpf和可调延迟线dl。49.第一单稳态电路mst1布置在上游电极e1的远端12与相位检测器phd的第一输入端口之间。第二单稳态电路mst2布置在下游电极e2的远端12和相位检测器phd的第二输入端口之间。50.由于相位匹配单元pmu的相位检测器phd(经由单稳态电路mst1、mst2)连接到上游电极e1的远端12和下游电极e2的近端11,相位检测器phd可以产生输出信号,其指示远端和近端11、12处的信号之间的相位差。相位检测器phd的输出信号控制可调延迟线dl并且在下文中被称为控制信号cs。51.如图1所示,低通滤波器lpf优选地布置在相位检测器phd的输出端口和可调延迟线dl的输入端口之间。优选地选择低通滤波器lpf的截止频率使得闭环极点比数据速率慢至少四个数量级。52.在图1的示例性实施例中,电驱动器dr1、dr2被分配给上游调制子单元mod1和下游调制子单元mod2。第一驱动器dr1被配置为接收第一电输入信号s1并产生用于上游调制子单元mod1的电上游调制信号sm1。第二驱动器dr2被配置为接收第二电输入信号s2并且产生用于下游调制子单元mod2的电下游调制信号sm2。53.在图1的示例性实施例中,第二驱动器dr2电气地布置在可调延迟线dl和下游电极e2的近端之间。因此,可调延迟线dl可以补偿由第一驱动器dr1和第二驱动器dr2引起的不等延迟。54.可以操作图1的电光调制器eom以基于两个比特生成pam4信号,该两个比特此后称为最高有效位(msb)和最低有效位(lsb)。上游调制信号sm1可用于输入msb,下游信号可用于输入lsb,或反之亦然。55.产生pam4信号的一个关键问题是上游调制信号sm1和下游调制信号sm2之间的差分偏斜控制。在图1的示例性实施例中,上游调制子单元mod1中光的有限传播速度可以引入与其长度成比例的延迟,使得——为了产生理想的pam4信号——电下游调制信号sm2优选地偏斜等于由上游调制子单元mod1引入的延迟的量。这种偏斜可以由可调延迟线dl产生。与理想偏斜的任何偏差都可能导致pam4信号的严重劣化。这对于高速信号——例如,对于pam456g串行链路——非常明显。56.更一般地,如果我们用td1、tm1、tdelay、td2指示第一驱动器dr1、上游调制子单元mod1、延迟线dl和第二驱动器dr2分别引入的延迟,为了产生理想的pam4信号,则以下等式必须成立:57.td1 tm1=td2 tdelayꢀꢀꢀꢀꢀꢀꢀ(1)58.在理想情况下,驱动器延迟是相等的,等式(1)变为:59.tm1=tdelayꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ(2)60.实际上,虽然光学延迟在工艺、温度和操作条件下是稳定的,但由于工艺不匹配——其引起静态差分偏斜——和工作条件(诸如电压、温度、设置)——其可能会不断变化——这两者导致第一和第二驱动器dr1、dr2引入的延迟可能不同,从而导致动态差分偏斜。61.即使通过适当校准延迟线dl可以消除静态差分偏斜,动态偏斜仍然没有得到补偿,因此基本上可以将等式(2)重写为:62.tm1=tdelay δtd(t)ꢀꢀꢀꢀ(3)63.其中,δtd(t)表示驱动器dr1、dr2之间的时间相关偏斜。64.在图1的示例性实施例中,由相位检测器phd和可调延迟线dl提供的延迟补偿回路可以自动补偿静态和动态差分偏斜两者,为多电平信号提供最佳性能。为此,电下游链路调制信号可以与光信号相位匹配。更具体地,由上游调制子单元mod1引入的光延迟在电平处——在上游调制子单元mod1的电极的远端12处和在下游调制子单元mod2的电极的近端11处——被感测。线性相位检测器phd比较两端处的电信号之间的偏斜,产生对应的控制信号cs。该信号优选地被低通滤波,然后用于控制可调延迟线dl,以便对齐电下行链路和上行链路调制信号sm1、sm2。由于所提出的延迟补偿回路使用随机数据流工作,所以单稳态电路mst1、mst2优选地存在于相位检测器phd的前方以便产生有限持续时间的脉冲。65.可调延迟线dl优选地在路径中生成可变偏斜δtdelay(t),以便:66.tm1=tdelay δtdelay(t) δtd(t)ꢀꢀꢀ(4)67.换句话说,延迟补偿环路的目的是修改可变偏斜以便消除信号路径中的任何延迟差异,使得:68.δtdelay(t) δtd(t)=0ꢀꢀꢀꢀ(5)69.延迟补偿回路可以仅由模拟块组成,如图1的示例性实施例所示,或者另外或替代地包括数字电路。图2、3和4中示出了还包括数字电路的示例性实施方式。70.在图2的示例性实施例中,相位检测器phd的低通滤波的输出信号由模数转换器adc数字化,模数转换器adc的输出控制数控延迟线dl。71.由于典型的动态变化发生非常缓慢,因此可以在低占空比模式下周期性地启用补偿回路,以便降低电流消耗,对芯片功耗具有可忽略不计的影响。例如,控制器(如图3所示)可以被配置为间歇地激活和停用相位匹配单元pmu(例如单稳态电路mst1、mst2、相位检测器phd和/或低通滤波器lpf)并且在补偿周期中运行相位匹配单元pmu。模数转换器优选地被配置为在相位匹配单元pmu停用期间存储其数字值并输出所存储的值,直到在下一个补偿周期中由低通滤波器lpf提供新的模拟值。72.在图1、2和3的示例性实施例中,驱动器dr1、dr2和调制子单元以及可调延迟线dl优选地集成在同一芯片上。73.替代地,如图4所示,驱动器dr1、dr2和调制子单元mod1、mod2可以集成在同一芯片上,而可调延迟线dl可以集成在另一芯片上。这里,低通滤波器lpf输出由模数转换器adc数字化,并经由数字接口传递到外部数控延迟线dl。74.通过进一步的示例,图5示出了上面参考图1‑4描述的操作的原理也可以扩展到任何其他调制方案,其中,不同比特或信道之间的精确延迟是有利的。例如,如图5所示,该方法可以在pam‑16调制方案中实现。75.在图5的示例性实施例中,电光调制器eom包括串联布置的多个调制子单元和多个相位匹配单元。除了调制子单元系列中的最后一个之外的每个调制子单元都是由后一调制子单元和连续的下游调制子单元形成的一对调制子单元中的上游调制子单元。相位匹配单元被分配给每对调制子单元。每个相位匹配单元优选地被配置为延迟施加到各个下游调制子单元的下游调制信号,使得在上游调制子单元的上游电极的远端处的上游调制信号与在下游调制子单元的下游电极的近端处的下游调制信号之间的相位差是最小的。76.关于延迟,上面参考图1的解释对应地适用于每对调制子单元。77.在图5的示例性实施例中,电驱动器被分配给每个调制子单元。每个驱动器被配置为接收电输入信号并且为相应的调制子单元生成电调制信号。对于除了调制子单元系列中的第一个之外的每个调制子单元,驱动器电气地布置在各个调制子单元的电极的近端与分配的相位匹配单元的可调延迟线之间。78.上面通过示例描述的操作原理可以应用于任何类型的光调制器(例如相位调制器、幅度调制器、偏振调制器、注入调制器、耗尽调制器等...)和任何类型的驱动方案(例如分段驱动器、行波电极、分段行波电极等...)。79.如果不存在额外的寄生元件,诸如焊盘/导线杂散电容和电感——其否则会降低调制器电极上的rf信号并干扰在到延迟补偿回路电路的高速连接上的传播延迟,则驱动器和光电调制器的协同集成通常可以提供最佳性能。80.出于说明的目的,图1‑5的示例性实施例示出了基于非差分信号运行的驱动器和调制子单元。当然,驱动器也可以被配置为接收和处理差分信号。在这种情况下,调制子单元优选地被配置为接收差分信号并基于差分调制信号调制辐射。为此,调制子单元可以包括优选地并联布置的两个电极。上述相位匹配单元可以连接到上述两个电极中的任何一个并与其一起操作。图6示出了基于差分信号的电光调制器eom的示例性实施例。81.本文公开的本发明的实施例的各种实施例和方面不仅应在本说明书中具体描述的顺序和上下文中被理解,而且包括任何顺序及其任何组合。每当上下文需要时,所有以单数形式使用的词语均应视为包括复数形式,反之亦然。没当上下文需要时,所有带有“和”字样的选项都应被视为包括词“或”(反之亦然)以及它们的任何组合。82.在附图和说明书中,已经公开了本发明的多个实施例。申请人想强调的是,每个实施例的每个特征都可以与任何其他实施例组合或添加到任何其他实施例中,以便修改相应实施例并创建附加实施例。这些附加实施例构成本公开的一部分,因此,申请人可以在审查的后期阶段提交关于这些附加实施例的另外的专利权利要求。83.此外,申请人想强调的是,每个所附从属权利要求的每个特征可以与任何当前独立权利要求以及任何其他(一个或多个)当前从属权利要求组合(无论本权利要求结构如何)。84.因此,申请人可以在审查的后期将进一步的专利权利要求引向其他权利要求组合。当前第1页12当前第1页12

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。