数位

‑

类比转换器及源极驱动器

技术领域

1.本发明涉及数模转换技术领域,尤其涉及一种具备较低rc延迟的数位

‑

类比转换器及源极驱动器。

背景技术:

2.随着液晶显示(liquid crystal display,lcd)面板技术的进步,消费市场对高阶lcd面板的需求也随之增加。目前的高阶lcd面板指的是可支援高帧率(frame rate)、高色彩深度及具备高解析度的大尺寸面板;例如,帧率(frame rate)为120hz、色彩深度为10位元(即可显示1024种灰阶的色彩)及解析度为8k(即7680*4320平方像素)的超高画质电视(ultra high definition television,uhdtv)。

3.然而,为了满足上述应用需求,用来对输入讯号进行处理的数位

‑

类比转换器(digital

‑

to

‑

analog, dac)的处理速度也必须相对应地提高。因此,如何提高数位

‑

类比转换器的处理速度,实乃本领域的重要课题之一。

技术实现要素:

4.本发明要解决的技术问题是:为了解决现有技术中的数位

‑

类比转换器处理速度较慢,导致lcd面板性能无法提高的技术问题。本发明提供一种数位

‑

类比转换器及源极驱动器,其具备较低rc延迟,能够提升数位

‑

类比转换器的处理速度。

5.本发明解决其技术问题所采用的技术方案是:一种数位

‑

类比转换器,用于根据一数位输入讯号,选择多个类比电压中的一者,以将所述数位输入讯号转换为一类比输出讯号,所述数位

‑

类比转换器包含:一第一转换电路,用来根据所述数位输入讯号,产生多个中继讯号;以及一第二转换电路,耦接于所述第一转换电路,用于根据所述数位输入讯号及所述多个中继讯号,产生所述类比输出讯号,其中,所述第二转换电路包含:一解码器,用于根据所述数位输入讯号,产生一选择讯号;以及多个开关,耦接于所述解码器,用于根据所述选择讯号,选择所述多个中继讯号中的一者,以做为所述类比输出讯号。

6.进一步地,所述多个类比电压与所述类比输出讯号之间形成多个讯号路径,所述多个讯号路径不通过所述第二转换电路的解码器。

7.进一步地,所述数位输入讯号包含n个位元,所述解码器为一m输入对2

m

输出的解码器,m、n为正整数,且2≦m≦n

‑

1。也就是说,当解码器的输入讯号数量为m时,输出讯号数量为2

m

。

8.进一步地,所述多个开关的数量为2

m

个。

9.进一步地,所述多个讯号路径中的每一者通过(n

‑

m 1)个开关传递所述多个类比电压中的一者和所述多个中继讯号中的一者。

10.进一步地,所述数位输入讯号包含(n

‑

m)个最低效位元和m个最高效位元,所述第

一转换电路用于根据所述(n

‑

m)个最低效位元,产生所述多个中继讯号,且所述第二转换电路用于根据所述m个最高效位元及所述多个中继讯号,选择所述多个中继讯号中的一者,以做为所述类比输出讯号。

11.进一步地,当m为3时,所述数位输入讯号包含一第一高效位元、一第二高效位元以及一第三高效位元,选择号包含一第零选择位元、一第一选择位元、一第二选择位元、一第三选择位元、一第四选择位元、一第五选择位元、一第六选择位元和一第七选择位元,且所述解码器包含:一第一反向器、一第二反向器和一第三反向器,所述第一反向器、所述第二反向器和所述第三反向器分别用于接收所述第三高效位元、所述第二高效位元和所述第一高效位元,据以产生所述第三高效位元的反向位元、所述第二高效位元的反向位元和所述第一高效位元的反向位元;以及一第一及闸、一第二及闸、一第三及闸、一第四及闸、一第五及闸、一第六及闸、一第七及闸和一第八及闸,耦接于所述第一反向器、所述第二反向器和所述第三反向器,用于分别产生所述第零选择位元、所述第一选择位元、所述第二选择位元、所述第三选择位元、所述第四选择位元、所述第五选择位元、所述第六选择位元和所述第七选择位元。

12.进一步地,所述第一及闸根据所述第三高效位元的反向位元、所述第二高效位元的反向位元和所述第一高效位元的反向位元,产生所述第零选择位元;所述第二及闸根据所述第三高效位元的反向位元、所述第二高效位元的反向位元和所述第一高效位元,产生所述第一选择位元;所述第三及闸根据所述第三高效位元的反向位元、所述第二高效位元和所述第一高效位元的反向位元,产生所述第二选择位元;所述第四及闸根据所述第三高效位元的反向位元、所述第二高效位元和所述第一高效位元,产生所述第三选择位元;所述第五及闸根据所述第三高效位元、所述第二高效位元的反向位元和所述第一高效位元的反向位元,产生所述第四选择位元;所述第六及闸根据所述第三高效位元、所述第二高效位元的反向位元和所述第一高效位元,产生所述第五选择位元;所述第七及闸根据所述第三高效位元、所述第二高效位元和所述第一高效位元的反向位元,产生所述第六选择位元;以及所述第八及闸根据所述第三高效位元、所述第二高效位元和所述第一高效位元,产生所述第七选择位元。

13.一种源极驱动器,包含如上所述的数位

‑

类比转换器,用于根据一数位输入讯号,选择多个类比电压中的一者,以将所述数位输入讯号转换为一类比输出讯号;一运算放大器,耦接于所述数位

‑

类比转换器,用来根据所述类比输出讯号,产生一通道输出讯号;以及一通道开关,耦接于所述运算放大器,用来根据一通道控制讯号,输出所述通道输出讯号,以作为一源极输出讯号。

14.进一步地,所述运算放大器包含:一正输入端,耦接于所述数位

‑

类比转换器,用于接收所述类比输出讯号;一负输入端;以及一输出端,耦接于所述负输入端,用于输出所述通道输出讯号。

15.本发明的有益效果如下:相比于现有技术,本发明的数位

‑

类比转换器及源极驱动器利用解码器来对数位

输入讯号中的部份位元进行解码,能够减少讯号路径上遭遇到的开关数量。当数位

‑

类比转换器中的讯号路径上遭遇到的开关数量越少,则讯号路径的rc延迟越短,能够提高数位

‑

类比转换器的处理速度。

附图说明

16.下面结合附图和实施例对本发明进一步说明。

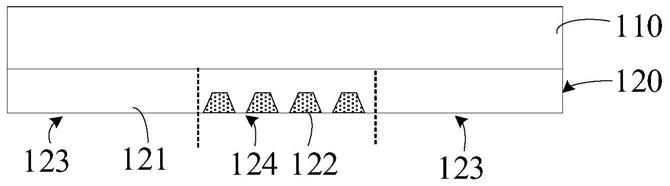

17.图1为根据本发明实施例的源极驱动器的示意图。

18.图2为数位

‑

类比转换器的逻辑电路示意图。

19.图3为图2的开关的等效电路示意图。

20.图4为根据本发明实施例的通道控制讯号、目标电压、类比输出讯号、通道输出讯号及源极输出讯号的电压对时间的示意图。

21.图5为另一通道控制讯号、目标电压、另一类比输出讯号、另一通道输出讯号及另一源极输出讯号的电压对时间的示意图。

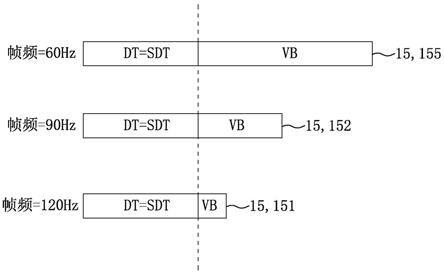

22.图6为另一通道控制讯号、目标电压及另一类比输出讯号的电压对时间的示意图。

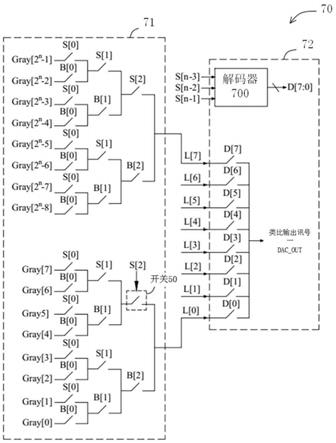

23.图7为根据本发明实施例的数位

‑

类比转换器的示意图。

24.图8为根据本发明实施例图7的解码器的逻辑电路示意图。

25.图中:1: 源极驱动器10:数位

‑

类比转换器一20:数位

‑

类比转换器二70: 数位

‑

类比转换器三700: 解码器22: 转换电路,71:第一转换电路,72:第二转换电路91:第一反向器,92:第二反向器,93:第三反向器901: 第一及闸,902:第二及闸,903:第三及闸,904:第四及闸,905:第五及闸,906:第六及闸,907:第七及闸,908:第八及闸b[n

‑

1]

…

b[0]: 反向位元ch_ctr:通道控制讯号一ch_ctr5: 通道控制讯号二40: 通道开关ch_out:通道输出讯号一ch_out5: 通道输出讯号二cp: 寄生电容d[7:0]: 选择讯号d[7]

…

d[0]: 第七

‑

第零选择位元dac_out:类比输出讯号一dac_out5:类比输出讯号二gray[2

n

‑

1]

…

gray[0]: 类比电压l[7]

…

l[0]: 中继讯号

in: 数位输入讯号30: 运算放大器ron: 电阻sd_out:源极输出讯号一sd_out5: 源极输出讯号二s[n

‑

1]

…

s[0]: 输入位元50: 开关ta: 数位

‑

类比转换时间tb:驱动时间一tb6: 驱动时间二vh:目标电压一vl: 目标电压二vth: 临限电压。

具体实施方式

[0026]

现在结合附图对本发明作进一步详细的说明。这些附图均为简化的示意图,仅以示意方式说明本发明的基本结构,因此其仅显示与本发明有关的构成。

[0027]

如图1所示,源极驱动器1可应用于色彩深度为n位元的显示器,用于提供源极输出讯号给一条源极线(source line)或一条源极通道(source channel)。在结构上,源极驱动器1包含一数位

‑

类比转换器一10、一运算放大器30以及一通道开关40。数位

‑

类比转换器一10耦接于多个类比电压gray[2

n

‑

1]

…

gray[0],用于根据一数位输入讯号in,选择多个类比电压gray[2

n

‑

1]

…

gray[0]中的一者,以将数位输入讯号in转换为一类比输出讯号一dac_out。数位输入讯号in包含n个输入位元s[n

‑

1]

…

s[0]。运算放大器30耦接于数位

‑

类比转换器一10,用于根据类比输出讯号一dac_out,产生一通道输出讯号一ch_ctr。通道开关40耦接于运算放大器30,用于根据一通道控制讯号一ch_ctr,输出通道输出讯号一ch_ctr,以作为一源极输出讯号一sd_out。运算放大器30包含一正输入端,耦接于数位

‑

类比转换器一10,用于接收类比输出讯号一dac_out;一负输入端;以及一输出端,耦接于负输入端,用于输出通道输出讯号一ch_ctr。于一实施例中,源极驱动器1可用于一液晶显示器,该液晶显示器的像素解析度为8k、色彩深度为10位元且帧率(frame rate)或更新率(refresh rate)为120赫兹。

[0028]

当源极驱动器1应用于色彩深度为10个二进制位元(n=10)的显示器时,数位输入讯号in包含十个输入位元s[9]

…

s[0],以表示单一像素的色彩的灰阶值(grayscale)。因此,色彩深度为10位元的显示器可分辨并显示1024种灰阶的色彩。在实际应用中,数位

‑

类比转换器一10根据数位输入讯号s[9]

…

s[0],从1024个类比电压gray[1023]

…

gray[0]中选择一者来作为类比输出讯号一dac_out,使得显示器的特定显示像素可呈现具有特定灰阶的色彩。

[0029]

如图2所示,数位

‑

类比转换器二20为图1的数位

‑

类比转换器一10的一种具体结构。数位

‑

类比转换器二20为树状架构,透过串联的多个电阻对系统电压进行分压,以产生多个类比电压gray[2

n

‑

1]

…

gray[0]。接着,透过多个输入位元s[n

‑

1]

…

s[0](及其反向位

元b[n

‑

1]

…

b[0])来导通某些开关50,以在类比电压与类比输出讯号一dac_out之间形成讯号路径。如此一来,数位

‑

类比转换器二20可根据多个输入位元s[n

‑

1]

…

s[0] (及其反向位元b[n

‑

1]

…

b[0]),选择多个类比电压gray[2

n

‑

1]

…

gray[0]中的一者,以将多个输入位元s[n

‑

1]

…

s[0]转换为类比输出讯号一dac_out。转换电路22为数位

‑

类比转换器二20的一部分,用于根据多个输入位元s[n

‑

1]、s[n

‑

2]和s[n

‑

3],导通某些开关50来形成讯号路径。举例来说,当输入位元s[n

‑

1]、s[n

‑

2]和s[n

‑

3]为二进制位元“111”时,其b[n

‑

1]、b[n

‑

2]和b[n

‑

3]为二进制位元“000”,则输入位元s[n

‑

1]可导通两个并联开关中的一者,输入位元s[n

‑

2]可导通四个并联开关中的两者,且输入位元s[n

‑

3]可导通八个并联开关中的四者,以形成通过三个串联开关的讯号路径。

[0030]

图3为图2的开关50的等效电路示意图。如图3所示,开关50可以是一电晶体,其电阻值为ron且寄生电容值为cp。经由实验或模拟可知,数位

‑

类比转换器二20的开关50的电阻ron与寄生电容cp的大小决定了rc延迟的大小,对数位

‑

类比转换器二20的处理速度的影响最为显著。当数位

‑

类比转换器二20的讯号路径通过的开关50数量越多,rc延迟也越长。

[0031]

传统上,提高数位

‑

类比转换器二20的处理速度的作法大多为增加开关50的电晶体的纵横比(w/l ratio)来降低电阻ron,然而此作法会导致寄生电容cp上升。另一种作法是在数位

‑

类比转换器二20的电路架构下使用低临界电压vth(threshold voltage)的电晶体,由于低临界电压vth的电晶体的电阻ron较小,因此所占的面积也较小,进而具备较低的寄生电容cp,然而此作法的代价是昂贵的制造成本。

[0032]

如图4所示,本实施例的通道控制讯号一ch_ctr、目标电压一vh和vl、类比输出讯号一dac_out、通道输出讯号一ch_ctr及源极输出讯号一sd_out的电压随时间而变化。在图1的源极驱动器1的单一通道驱动期间(包含数位

‑

类比转换时间ta和驱动时间一tb)中,当通道开关40侦测到控制讯号ch_ctr的上升边缘(rising edge)时,数位

‑

类比转换时间ta开始,通道开关40关闭而断开源极通道,数位

‑

类比转换器一10进行数位

‑

类比转换,使得类比输出讯号一dac_out逐渐上升。运算放大器30产生的通道输出讯号一ch_ctr随着类比输出讯号一dac_out上升而上升。通道开关40输出的源极输出讯号一sd_out在数位

‑

类比转换时间ta内保持在目标电压二vl。

[0033]

当通道开关40侦测到控制讯号ch_ctr的下降边缘(falling edge)时,驱动时间一tb开始,通道开关40导通而连接源极通道,运算放大器30的输出端的通道输出讯号一ch_ctr的电压略为下降。然而,由于类比输出讯号一dac_out已达目标电压一vh并大于通道输出讯号一ch_ctr,故运算放大器30将通道输出讯号一ch_ctr逐渐提高到目标电压一vh。通道开关40将通道输出讯号一ch_ctr作为源极输出讯号一sd_out而输出到源极通道。

[0034]

周而复始地,当通道开关40再次侦测到控制讯号ch_ctr的上升边缘时,数位

‑

类比转换时间ta再次开始;接着,当通道开关40再次侦测到控制讯号ch_ctr的下降边缘时,驱动时间一tb再次开始。由于显示器的线反转(line inversion)操作,故类比输出讯号一dac_out、通道输出讯号一ch_ctr和源极输出讯号一sd_out由目标电压一vh下降到目标电压二vl。

[0035]

如图5所示,本实施例的另一通道控制讯号二ch_ctr5、目标电压一vh和vl、另一类比输出讯号二dac_out5、另一通道输出讯号二ch_ctr5及另一源极输出讯号二sd_out5的电压随时间而变化。在图1的源极驱动器1使用图2的数位

‑

类比转换器二20的前提下,由于rc

延迟太长,导致数位

‑

类比转换器二20无法在数位

‑

类比转换时间ta内将类比输出讯号二dac_out5提高到目标电压一vh,造成显示器的画面黯淡、用户观感不佳的问题。

[0036]

如图6所示,当显示器的帧率提高使得单一通道驱动期间的长度缩短,例如图6的驱动时间二tb6短于图4和图5的驱动时间一tb。在图1的源极驱动器1使用图2的数位

‑

类比转换器二20的前提下,由于rc延迟太长,导致数位

‑

类比转换器二20无法在数位

‑

类比转换时间ta以及驱动时间二tb6内将类比输出讯号二dac_out5提高到目标电压一vh,造成显示器的画面黯淡、用户观感不佳的问题。

[0037]

由图4、图5和图6可看出,倘若数位

‑

类比转换器一10可在数位

‑

类比转换时间ta内,将类比输出讯号一dac_out提高到目标电压一vh或vl,即可确保显示像素的亮度足够,进而改善显示器的画面黯淡、用户观感不佳的问题。据此,本发明提出了一种数位

‑

类比转换器,其可使用较少的开关来传递类比电压,降低开关导致的rc延迟,进而提高数位

‑

类比转换器一10的处理速度。

[0038]

如图7至图8所示,数位

‑

类比转换器三70为图1的数位

‑

类比转换器一10的另一种结构,用于根据包含n个输入位元s[n

‑

1]

…

s[0]的数位输入讯号,选择多个类比电压gray[2

n

‑

1]

…

gray[0]中的一者,以将数位输入讯号转换为一类比输出讯号一dac_out。

[0039]

在结构上,数位

‑

类比转换器三70包含第一转换电路71和第二转换电路72。第一转换电路71用于根据包含n个输入位元s[n

‑

1]

…

s[0]的数位输入讯号,产生多个中继讯号l[7]

…

l[0]。第二转换电路72耦接于第一转换电路71,用于根据包含n个输入位元s[n

‑

1]

…

s[0]的数位输入讯号及多个中继讯号l[7]

…

l[0],产生类比输出讯号一dac_out。第二转换电路72包含一解码器700以及多个开关。解码器700用于根据包含n个输入位元s[n

‑

1]

…

s[0]的数位输入讯号,产生一选择讯号d[7:0],其中选择讯号d[7:0]包含多个选择位元d[7]

…

d[0]。多个开关用于根据选择讯号d[7:0],选择多个中继讯号l[7]

…

l[0]中的一者,以做为类比输出讯号一dac_out。多个类比电压gray[2n

‑

1]

…

gray[0]与类比输出讯号一dac_out之间形成多个讯号路径,该多个讯号路径不通过(pass through)第二转换电路72的解码器700。

[0040]

在操作上,在第一转换电路71中,当输入位元s[0]导通开关时,可选择多个类比电压gray[2

n

‑

1]

…

gray[0]中的奇数位(odd ordered)类比电压如gray[2

n

‑

1]、gray[2

n

‑

3]

…

及gray[1];或者,当输入位元s[0]的反向位元b[0] 导通开关时,可选择偶数位的(even ordered)类比电压如gray[2

n

‑

2]、gray[2

n

‑

4]

…

gray[0]。当输入位元s[1] 导通开关时,可选择多个类比电压gray[2

n

‑1‑

1]

…

gray[0]中的奇数位的类比电压如gray[2

n

‑1‑

1]、gray[2

n

‑1‑

3]

…

及gray[1];或者,当输入位元s[1]的反向位元b[1] 导通开关时,可选择偶数位的类比电压如gray[2

n

‑1‑

2]、gray[2

n

‑1‑

4]

…

及gray[0]。依此类推,当多个输入位元s[0]

…

输入位元s[n

‑

4]或反向位元b[0]

…

位元b[n

‑

4]分别导通开关时,可选择多个类比电压来作为多个中继讯号l[7]

…

l[0],并将之传递到第二转换电路72。接着,在第二转换电路72中,在解码器700产生多个选择位元d[7]

…

d[0]之后,当多个选择位元d[7]

…

d[0]中的一者导通开关时,可选择多个中继讯号l[7]

…

l[0]中的一者来做为类比输出讯号一dac_out,并将之传递到运算放大器30(绘于图1)。

[0041]

换言之,根据上述第一转换电路71和第二转换电路72的操作方式可知,第一转换电路71及多个开关形成多个讯号路径,用于传递多个类比电压gray[2

n

‑

1]

…

gray[0]和多

个中继讯号l[7]

…

l[0]。

[0042]

在本发明实施例中,数位输入讯号in包含n个位元,解码器700为一m输入对2

m

输出的解码器,m、n为正整数,且2≦m≦n

‑

1。除此之外,多个开关的数量为2

m

个。在此情况下,多个讯号路径中的每一者通过(n

‑

m 1)个开关传递多个类比电压gray[2

n

‑

1]

…

gray[0]中的一者和多个中继讯号l[7]...l[0]中的一者。再者,多个中继讯号l[2

m

‑

1]...l[0]的数量为2

m

个,以分别对应解码器700的2

m

输出讯号。

[0043]

举例来说,在图7的实施例中,假设数位输入讯号in包含10个输入位元s[9]

…

s[0],数位输入讯号s[9]为最高效位元(most significant bit,msb),而数位输入讯号s[0]为最低效位元(least significant bit,lsb)。解码器700为3输入对8输出的解码器,即n=10、m=3。并且,多个开关的数量为8个,且多个中继讯号l[7]...l[0]的数量为8个。在此情况下,多个讯号路径中的每一者通过10

‑

3 1=8个开关传递多个类比电压gray[1023]

…

gray[0]中的一者和多个中继讯号l[7]...l[0]中的一者。相较之下,图2的数位

‑

类比转换器二20的多个讯号路径中的每一者须通过10个开关来传递多个类比电压gray[1023]

…

gray[0]中的一者,以产生类比输出讯号一dac_out。可见,本发明利用解码器700来对数位输入讯号in中的部份位元进行解码,如此减少讯号路径上遭遇到的开关数量;意即于本发明的数位

‑

类比转换器三70中,讯号路径上遭遇到的开关数量可减少(m

‑

1)个。当讯号路径上遭遇到的开关数量越少,则讯号路径的rc延迟越短,借此提高数位

‑

类比转换器三70的处理速度。

[0044]

在一实施例中,解码器700为2输入对4输出的解码器,即m=2。并且,多个开关的数量为4个,且多个中继讯号的数量为4个。在此情况下,多个讯号路径中的每一者通过10

‑

2 1=9个开关传递多个类比电压和多个中继讯号;意即于本发明的数位

‑

类比转换器三70中,讯号路径上遭遇到的开关数量可减少1个。

[0045]

在一实施例中,解码器700为4输入对16输出的解码器,即m=4。并且,多个开关的数量为16个,且多个中继讯号的数量为16个。在此情况下,多个讯号路径中的每一者通过10

‑

4 1=7个开关传递多个类比电压和多个中继讯号;意即于本发明的数位

‑

类比转换器三70中,讯号路径上遭遇到的开关数量可减少3个。

[0046]

在其他实施例中,电路设计者应当衡量第一转换电路71和第二转换电路72的处理速度,判断适当的m值。详细来说,m值决定了第二转换电路72的m输入对2

m

输出的解码器和m个开关的处理速度或时间,第二转换电路72的处理速度不应比第一转换电路71的处理速度慢,或第二转换电路72的处理时间不应比第一转换电路71的处理时间长。

[0047]

在一实施例中,数位输入讯号in包含(n

‑

m)个最低效位元和m个最高效位元,第一转换电路71用来根据(n

‑

m)个最低效位元,产生多个中继讯号l[7]

…

l[0],且第二转换电路72用来根据m个最高效位元及多个中继讯号l[7]

…

l[0],选择多个中继讯号l[7]

…

l[0]中的一者,以做为类比输出讯号一dac_out。

[0048]

在一实施例中,当m为3时,数位输入讯号in包含一第一高效输入位元s[n

‑

1]、一第二高效输入位元s[n

‑

2]以及一第三高效输入位元s[n

‑

3],选择号包含一选择位元d[0]

…

d[7]。在结构上,解码器700包含多个反向器(inverter)例如,第一反向器91、第二反向器92和第三反向器93,以及多个及闸(and gate)例如,第一及闸901、第二及闸902、第三及闸903、第四及闸904、第五及闸905、第六及闸906、第七及闸907和第八及闸908。第一反向器91、第二反向器92和第三反向器93分别用于接收第三高效输入位元s[n

‑

3]、第二高效输入

位元s[n

‑

2]和第一高效输入位元s[n

‑

1],据以产生反向位元b[n

‑

3]、b[n

‑

2]和b[n

‑

1]。第一及闸901、第二及闸902、第三及闸903、第四及闸904、第五及闸905、第六及闸906、第七及闸907和第八及闸908耦接于第一反向器91、第二反向器92和第三反向器93,分别用来产生第零选择位元d[0]、第一选择位元d[1]、第二选择位元d[2]、第三选择位元d[3]、第四选择位元d[4]、第五选择位元d[5]、第六选择位元d[6]和第七选择位元d[7]。

[0049]

在操作上,第一及闸901根据反向位元b[n

‑

3]、反向位元b[n

‑

2]和反向位元b[n

‑

1],产生第零选择位元d[0]。第二及闸902根据反向位元b[n

‑

3]、反向位元b[n

‑

2]和第一高效输入位元s[n

‑

1],产生第一选择位元d[1]。第三及闸903根据反向位元b[n

‑

3]、第二高效输入位元s[n

‑

2]和反向位元b[n

‑

1],产生第二选择位元d[2]。第四及闸904根据反向位元b[n

‑

3]、第二高效输入位元s[n

‑

2]和第一高效输入位元s[n

‑

1],产生第三选择位元d[3]。第五及闸905根据第三高效输入位元s[n

‑

3]、反向位元b[n

‑

2]和反向位元b[n

‑

1],产生第四选择位元d[4]。第六及闸906根据第三高效输入位元s[n

‑

3]、反向位元b[n

‑

2]和第一高效输入位元s[n

‑

1],产生第五选择位元d[5]。第七及闸907根据第三高效输入位元s[n

‑

3]、第二高效输入位元s[n

‑

2]和反向位元b[n

‑

1],产生第六选择位元d[6]。第八及闸908根据第三高效输入位元s[n

‑

3]、第二高效输入位元s[n

‑

2]和第一高效输入位元s[n

‑

1],产生第七选择位元d[7]。表1为根据本发明实施例图7的解码器真值表。

[0050]

表1综上所述,本发明的数位

‑

类比转换器及源极驱动器利用解码器来对数位输入讯号中的部份位元进行解码,如此可减少讯号路径上遭遇到的开关数量。当数位

‑

类比转换器中的讯号路径上遭遇到的开关数量越少,则讯号路径的rc延迟越短,借此提高数位

‑

类比转换器的处理速度。

[0051]

以上述依据本发明的理想实施例为启示,通过上述的说明内容,相关工作人员完全可以在不偏离本项发明技术思想的范围内,进行多样的变更以及修改。本项发明的技术性范围并不局限于说明书上的内容,必须要如权利要求范围来确定其技术性范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。