1.本公开涉及一种用于显示设备的驱动电路,更具体地,涉及一种提供用于选择源信号的具有全范围的控制信号的反相器,以及一种通过使用该反相器来选择和输出源信号的源信号输出电路。

背景技术:

2.显示设备包括用于驱动诸如lcd面板或led面板的显示面板的驱动电路。驱动电路可以被制造为集成电路并安装在显示设备上。

3.驱动电路用于接收表示屏幕的显示数据,产生对应于显示数据的源信号,并将源信号提供至显示面板。

4.为了减小驱动电路的面积并改善其操作特性,已经对驱动电路进行了各种改进。

5.例如,驱动电路包括产生源信号的输出缓冲器。输出缓冲器可以设计成通过使用驱动电压和接地电压的中间电压来产生具有全范围的源信号。在这种情况下,全范围可以理解为表示驱动电压和接地电压之间的电压。

6.此外,驱动电路包括用于将输出缓冲器的源信号传输至显示面板的多路转接器。多路转接器配置为响应于控制信号来选择和输出具有全范围的源信号。

7.在驱动电路中,可以使用在低电压范围内操作的晶体管来配置输出缓冲器,以减小驱动电路的面积和工艺成本。在这种情况下,低电压范围可以被理解为表示从驱动电压至中间电压的电压范围,或者从中间电压至接地电压的电压范围。

8.与在全范围内操作的晶体管相比,在低电压范围内操作的晶体管占用小的面积并且可以降低工艺成本。

9.驱动电路包括用于向多路转接器提供具有全范围的控制信号的反相器。反相器配置为向多路转接器提供控制信号。

10.通常,反相器通过使用驱动电压和接地电压来提供具有全范围的控制信号,并使用在全范围内操作的晶体管来配置。

11.在驱动电路中,不仅需要使用在低电压范围内操作的晶体管来配置输出缓冲器,而且还需要使用在低电压范围内操作的晶体管来配置反相器,使得可以以低工艺成本制造具有小面积的驱动电路。

技术实现要素:

12.各种实施方式涉及提供源信号输出电路的反相器,该反相器包括在低电压范围内操作并且可以输出用于选择和输出源信号的具有全范围的控制信号的元件。

13.此外,各种实施方式涉及提供能够通过使用反相器来控制多路转接器的源信号输出电路。

14.在一个实施方式中,源信号输出电路可以包括多路转接器和反相器,多路转接器配置为响应于控制信号选择具有从第一电压至第二电压的第一电压范围的源信号,反相器

配置为通过使用第一电压和第二电压之间的中间电压来输出控制信号。反相器包括:第一反相单元,配置为响应于第一输入信号提供具有从第一电压至中间电压的第二电压范围的第一反相信号;第二反相单元,配置为响应于第二输入信号提供具有从中间电压至第二电压的第三电压范围的第二反相信号;以及输出单元,配置为通过输出第一反相信号和第二反相信号中的一个来提供具有第一电压范围的控制信号。

15.此外,源信号输出电路的反相器可以包括:第一反相单元,配置为响应于第一输入信号而提供第一反相信号;第二反相单元,配置为响应于第二输入信号而提供第二反相信号;以及输出单元,配置为选择第一反相信号和第二反相信号中的一个,并输出所选择的信号以作为控制信号。控制信号属于从第一电压至第二电压的第一电压范围。第一反相单元使用第一电压和第二电压之间的中间电压,并输出具有从第一电压至中间电压的第二电压范围的第一反相信号。第二反相单元使用中间电压并输出具有从中间电压至第二电压的第三电压范围的第二反相信号。第一反相单元、第二反相单元和输出单元配置为在小于第一电压范围的低电压范围内操作。

16.本公开的优点在于,其能够以低工艺成本制造具有小面积的驱动电路,因为用于向多路转接器提供具有全范围的控制信号的反相器使用在低电压范围内操作的元件来配置。

附图说明

17.图1是示出根据本公开的源信号输出电路的优选实施方式的电路图。

18.图2是示出图1的反相器的实施方式的电路图。

19.图3是示出图2的反相器输出具有从驱动电压至中间电压的电压范围的控制信号的电路图。

20.图4是示出图2的反相器输出具有从中间电压至接地电压的电压范围的控制信号的电路图。

具体实施方式

21.以下将参照附图更详细地描述示例性实施方式。然而,本公开可以以不同形式来实施,并且不应被构造为限于本文中所阐述的实施方式。相反,提供这些实施方式使得本公开将是彻底和完整的,并且将本公开的范围完全传达给本领域技术人员。在本公开通篇,在本公开的所有附图和实施方式中,相同的参考标号表示相同的部件。

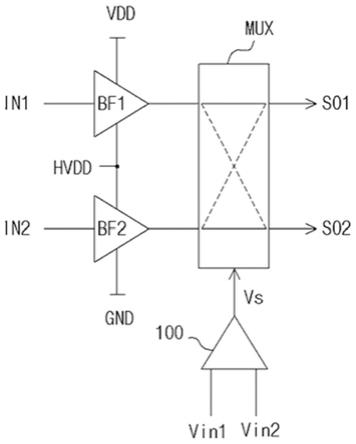

22.可以参照图1描述本公开的源信号输出电路。

23.源信号输出电路形成作为集成电路制造的驱动电路的一部分,并且可以示出为包括输出缓冲器bf1和bf2、多路转接器mux和反相器100。

24.源信号输出电路示出为使用驱动电压vdd作为第一电压,使用接地电压gnd作为第二电压,以及使用半驱动电压hvdd作为中间电压。在这种情况下,例如,中间电压可以理解为具有驱动电压vdd和接地电压gnd之间的中间电平。

25.对于本公开的描述,全范围表示为第一电压范围,并且可以理解为是在驱动电压vdd(即,第一电压)和接地电压gnd(即,第二电压)之间。第二电压范围可以理解为是在驱动电压vdd(即,第一电压)和半驱动电压hvdd(即,中间电压)之间。第三电压范围可以理解为

是在半驱动电压hvdd(即,中间电压)和接地电压gnd(即,第二电压)之间。

26.为了便于描述,vdd表示为第一电压,gnd表示为第二电压,而hvdd表示为中间电压。

27.输出缓冲器bf1配置为接收第一输入电压in1并通过使用第一电压vdd和中间电压hvdd输出与第一输入电压in1对应的源信号so1。

28.输出缓冲器bf2配置为接收第二输入电压in2并通过使用中间电压hvdd和第二电压gnd输出与第二输入电压in2对应的源信号so2。

29.即,输出缓冲器bf1输出具有第一电压范围的源信号so1。输出缓冲器bf2输出具有第二电压范围的源信号so2。

30.多路转接器mux响应于控制信号vs选择输出缓冲器bf1的源信号so1和输出缓冲器bf2的源信号so2的输出方向,并输出源信号so1和源信号so2。在图1中,多路转接器mux示出为相对于两个输出通道直接输出源信号so1和源信号so2。另一方面,多路转接器mux可以通过两个输出通道之间以及输出缓冲器bf1和bf2之间的交叉连接(如虚线所示)来从输出源信号so1和源信号so2的通道中改变。

31.即,多路转接器mux配置为针对每个输出端输出在第一电压范围(即,全范围)内的源信号。为此,还需要提供具有第一电压范围(即,全范围)的控制信号vs。如果控制信号vs具有第一电压范围,则可以理解,控制信号vs具有在第一电压vdd(即,第一电压范围的最高电平)和第二电压gnd(即,第一电压范围的最低电平)之间摆动的电平。

32.第二电压范围和第三电压范围可以理解为属于第一电压范围。具有第二电压范围的控制信号vs可以理解为具有对应于第一电压vdd的高电平。具有第三电压范围的控制信号vs可以理解为具有对应于第二电压gnd的低电平。

33.即,例如,当控制信号vs提供为具有高电平的第一电压vdd时,多路转接器mux可以直接输出源信号so1和源信号so2,并且当控制信号vs提供为具有低电平的第二电压gnd时,多路转接器mux可以通过使源信号so1和源信号so2交叉来输出源信号so1和源信号so2。

34.反相器100配置为接收第一输入信号vin1和第二输入信号vin2,并基于第一输入信号vin1和第二输入信号vin2的值输出控制信号vs。

35.参照图2,反相器100配置为通过使用第一电压vdd和第二电压gnd之间的中间电压hvdd来输出控制信号vs。

36.为此,反相器100可以配置为包括第一反相单元10、第二反相单元20和输出单元30。

37.第一反相单元10配置为响应于第一输入信号vin1提供具有从第一电压vdd至中间电压hvdd的第二电压范围的第一反相信号。

38.此外,第二反相单元20配置为响应于第二输入信号vin2提供具有从中间电压hvdd至第二电压gnd的第三电压范围的第二反相信号。

39.更具体地,第一反相单元10配置为包括第一上拉元件和第一下拉元件,第一上拉元件和第一下拉元件接收第一输入信号vin1并通过使用第一电压vdd和中间电压hvdd输出第一反相信号。在这种情况下,第一上拉元件对应于pmos晶体管q1,而第一下拉元件对应于nmos晶体管q2。

40.pmos晶体管q1配置为具有施加第一电压vdd的源极和施加第一输入信号vin1的栅

极,并通过其漏极输出第一反相信号。nmos晶体管q2配置为具有施加中间电压hvdd的源极,施加第一输入信号vin1的栅极,以及与pmos晶体管q1的漏极共同联接的漏极。

41.根据该配置,第一反相单元10可以理解为具有配置为cmos晶体管结构的pmos晶体管q1(即,第一上拉元件)和nmos晶体管q2(即,第一下拉元件),并且响应于第一输入信号vin1,通过公共漏极输出在第二电压范围内(即,在第一电压vdd和中间电压hvdd之间)摆动的第一反相信号。

42.此外,第二反相单元20配置为包括第二上拉元件和第二下拉元件,第二上拉元件和第二下拉元件接收第二输入信号vin2并通过使用中间电压hvdd和第二电压gnd输出第二反相信号。在这种情况下,第二上拉元件对应于pmos晶体管q3,而第二下拉元件对应于nmos晶体管q4。

43.pmos晶体管q3配置为具有施加中间电压hvdd的源极,施加第二输入信号vin2的栅极,以及与nmos晶体管q4的漏极共同联接的漏极。nmos晶体管q4配置为具有施加第二电压gnd的源极和施加第二输入信号vin2的栅极,并通过其漏极输出第二反相信号。

44.根据该配置,第二反相单元20可以理解为具有配置为cmos晶体管结构的pmos晶体管q3(即,第二上拉元件)和nmos晶体管q4(即,第二下拉元件),并且响应于第二输入信号vin2通过公共漏极输出在第三电压范围(即,在中间电压hvdd和第二电压gnd之间)内摆动的第二反相信号。

45.输出单元30配置为通过选择第一反相单元10的第一反相信号和第二反相单元20的第二反相信号中的一个并输出所选择的信号来提供具有第一电压范围的控制信号vs。

46.为此,输出单元30包括第一开关单元31和第二开关单元32。

47.当第一反相单元10的第一反相信号属于第一电压范围时,第一开关单元31配置为将第一反相信号输出为控制信号vs。

48.为此,当栅极电压由中间电压hvdd固定并且第一反相单元10的第一反相信号与栅极电压之间的电势差等于或高于预设电平时,第一开关单元31输出第一反相信号以作为控制信号vs。即,第一开关单元31可以理解为包括pmos二极管,当中间电压hvdd施加至pmos二极管的栅极,并且等于或高于中间电压hvdd预设电平的第一反相信号施加至pmos二极管的源极和pmos二极管的反向偏置时,该pmos二极管通过其漏极输出控制信号vs。

49.更具体地,第一开关单元31包括配置为用作pmos二极管的pmos晶体管m1。pmos晶体管m1配置为具有施加中间电压hvdd的栅极,施加第一反相单元10的第一反相信号的源极,以及联接至源极的反向偏置,并通过其漏极输出控制信号vs。

50.此外,当第二反相单元20的第二反相信号属于第二电压范围时,第二开关单元32配置为将第二反相信号输出为控制信号vs。

51.为此,当栅极电压由中间电压hvdd固定并且第二反相单元20的第二反相信号与栅极电压之间的电势差等于或高于预设电平时,第二开关单元32输出第二反相信号以作为控制信号vs。即,第二开关单元32可以理解为包括nmos二极管,当中间电压hvdd施加至nmos二极管的栅极,并且等于或低于中间电压hvdd预设电平的第二反相信号施加至nmos二极管的源极和nmos二极管的反向偏置时,该nmos二极管通过其漏极输出控制信号vs。

52.更具体地,第二开关单元32包括配置为用作nmos二极管的nmos晶体管m2。nmos晶体管m2配置为具有施加中间电压hvdd的栅极,施加第二反相单元20的第二反相信号的源

极,以及联接至源极的反向偏置,并通过其漏极输出控制信号vs。

53.包括在第一开关单元31中的pmos晶体管m1和包括在第二开关单元32中的nmos晶体管m2形成公共漏极,并且配置为通过公共漏极输出控制信号vs。

54.如图2中配置的反相器100可以如图3所示响应于具有第二电压范围的第一输入信号vin1而输出控制信号vs,或者可以如图4所示响应于具有第三电压范围的第二输入信号vin2而输出控制信号vs。

55.首先,参照图3,当第一输入信号vin1施加为中间电压hvdd的电平时,第二输入信号vin2施加为第二电压gnd的电平。

56.当第二输入信号vin2施加为第二电压gnd的电平时,pmos晶体管q3导通。然而,nmos晶体管m2保持截止,因为中间电压hvdd施加至nmos晶体管m2的源极和栅极,并且在nmos晶体管m2的栅极和源极之间没有形成用于导通nmos晶体管m2的足够的电压。即,第二开关单元32不运行。

57.然而,当第一输入信号vin1施加为中间电压hvdd的电平时,pmos晶体管q1导通。通过pmos晶体管q1的上拉操作将具有第一电压vdd的电平的第一反相信号施加至第一开关单元31的pmos晶体管m1的源极。

58.第一开关单元31的pmos晶体管m1导通,因为第一电压vdd施加至pmos晶体管m1的源极,并且在pmos晶体管m1的栅极和源极之间形成用于导通pmos晶体管m1的足够的电压。即,第一开关单元31导通,并输出具有第一电压vdd的电平的控制信号vs,即,第一反相单元10的第一反相信号。

59.即,通过pmos晶体管q1和pmos晶体管m1的导通,控制信号vs输出为具有第二电压范围的第一电压vdd的电平。

60.参照图4,当第一输入信号vin1施加为第一电压vdd的电平时,第二输入信号vin2施加为中间电压hvdd的电平。

61.当第一输入信号vin1施加为第一电压vdd的电平时,nmos晶体管q2导通。然而,pmos晶体管m1保持截止,因为中间电压hvdd施加至pmos晶体管m1的源极和栅极,并且在pmos晶体管m1的栅极和源极之间没有形成用于导通pmos晶体管m1的足够的电压。即,第一开关单元31不运行。

62.然而,当第二输入信号vin2施加为中间电压hvdd的电平时,nmos晶体管q4导通。通过nmos晶体管q4的下拉操作将具有第二电压gnd的电平的第二反相信号施加至第二开关单元32的nmos晶体管m2的源极。

63.第二开关单元32的nmos晶体管m2导通,因为第二电压gnd施加至nmos晶体管m2的源极,并且在nmos晶体管m2的栅极和源极之间形成用于导通nmos晶体管m2的足够的电压。即,第二开关单元32导通,并输出具有第二电压gnd的电平的控制信号vs,即,第二反相单元20的第二反相信号。

64.即,通过nmos晶体管q4和nmos晶体管m2的导通,控制信号vs输出为具有第三电压范围的第二电压gnd的电平。

65.如上所述,可以将控制信号vs输出为第一电压vdd的电平或第二电压gnd的电平。即,可以向多路转接器mux提供具有第一电压范围的控制信号vs。

66.可以将从第一电压vdd至中间电压hvdd的第二电压范围和从中间电压hvdd至第二

电压gnd的第三电压范围中的每个理解为小于从第一电压vdd至第二电压gnd的第一电压范围的低电压范围。

67.因此,第一反相单元10的pmos晶体管q1和nmos晶体管q2,第二反相单元20的pmos晶体管q3和nmos晶体管q4,以及输出单元30的pmos晶体管m1和nmos晶体管m2可以配置为在低电压范围内操作。

68.反相器100包括在低电压范围内操作的元件,并且可以提供具有第一电压范围(即,全范围)的控制信号vs。即,通过使用在低电压范围内操作的元件,反相器100可以获得与具有全范围的元件相同的效果。

69.因此,本公开可以通过不仅使用对应于输出缓冲器的缓冲器bf1和bf2,而且使用作为在低电压范围内操作的元件的反相器100来实现源信号输出电路。

70.因此,本公开的优点在于,其能够以低工艺成本制造具有小面积的驱动电路。

71.尽管以上已经描述了各种实施方式,但是本领域技术人员将理解,所描述的实施方式仅是示例性的。因此,不应基于所描述的实施方式来限制本文中所描述的公开内容。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。