1.本发明涉及一种驱动方法,特别是涉及一种显示器的背光驱动方法。

背景技术:

2.现有显示器的图像显示是以数据线(data line)传输图像信号控制对应的液晶分子扭转,并配合彩色滤光层提供滤光效果,以实现图像的全彩显示。其中,液晶分子扭转响应时间有其限制,且在该显示器显示图像期间,该显示器的一个背光模块所具有的多个发光二极管皆一起持续发光,导致在动态图像显示时,容易造成该显示器的显示荧幕具有残影问题。

3.为解决此问题,将现有显示器的背光驱动方法调整为于每一次换帧(frame)时就关闭该背光模块(即,使该显示荧幕逐帧插黑),以降低图像显示时间,进而改善该显示器的残影问题。然而,此方法会使该背光模块处于开启的时间较短,造成该背光模块的发光强度要够强才符合人眼所能感受到的亮度。此外,该背光模块的每一个发光二极管是受控制而一起导通,使得该显示器具有较大的电磁干扰(electromagnetic interference,emi)。另外,若将该背光模块的所述发光二极管分为多组发光二极管,每一组发光二极管都有自己的驱动单元,且每一个驱动单元仅根据一个同步控制信号同时对所对应的一组发光二极管进行各自的亮度控制,如此,将导致该显示器上的互调干扰,造成观察者可以看到条纹形式的画面。因此,现有显示器的背光驱动方法仍有改进的空间。

技术实现要素:

4.本发明的目的在于提供一种能够克服先前技术缺点的显示器的背光驱动方法。

5.本发明的显示器的背光驱动方法,由该显示器的一个具有一个预定频率信号的驱动模块所执行,以驱动该显示器的一个包括一个发光二极管阵列的背光模块逐行发光,该显示器的背光驱动方法包含以下步骤:

6.(a)根据一个相关于该显示器所显示的图像更新的内部同步控制信号、该预定频率信号,及一个具有多个延迟指令及一个图像串流的串行输入信号中的所述延迟指令,产生依序延迟的多个切换信号;

7.(b)根据该串行输入信号及该内部同步控制信号,产生延迟的一个驱动信号输出;及

8.(c)将所述切换信号及该驱动信号输出传输至该背光模块,以致该背光模块逐行发光。

9.本发明的显示器的背光驱动方法,每一个所述延迟指令指示一个延迟值,在步骤(b)中,根据该串行输入信号的所述延迟指令中具有最小延迟值的延迟指令及该图像串流、该内部同步控制信号,产生该驱动信号输出。

10.本发明的显示器的背光驱动方法,每一个所述延迟指令指示一个延迟值,所述延迟指令中任两个相邻延迟指令的延迟值的差值为一个固定值。

11.本发明的显示器的背光驱动方法,所述切换信号及该内部同步控制信号各自为一个具有多个方波的脉波信号,每一个所述切换信号的所述方波中的一个方波的上升缘与该内部同步控制信号的所述方波中的一个对应方波的下降缘的时间间隔相关于所述延迟指令中其所对应的一个延迟指令。

12.本发明的显示器的背光驱动方法,该驱动模块包括各自具有该预定频率信号的一个第一驱动单元及至少一第二驱动单元,所述延迟指令分成多组延迟指令,所述切换信号分成多组切换信号,步骤(a)包括以下子步骤,

13.(a1)利用该第一驱动单元根据该内部同步控制信号、该预定频率信号,及该多组延迟指令中对应的一组,产生该多组切换信号中对应的一组切换信号,及

14.(a2)利用该至少一个第二驱动单元中的每一个第二驱动单元根据该内部同步控制信号、该预定频率信号,及该多组延迟指令中对应的一组延迟指令,产生该多组切换信号中对应的一组切换信号。

15.本发明的显示器的背光驱动方法,该驱动模块包括各自具有该预定频率信号的一个第一驱动单元及至少一第二驱动单元,该驱动信号输出包括多组驱动信号,步骤(b)包括以下子步骤,

16.(b1)利用该第一驱动单元根据该串行输入信号及该内部同步控制信号,产生该多组驱动信号中对应的一组驱动信号,及

17.(b2)利用该至少一个第二驱动单元中的每一个第二驱动单元根据该串行输入信号及该内部同步控制信号,产生该多组驱动信号中对应的一组驱动信号。

18.本发明的显示器的背光驱动方法,该驱动模块包括各自具有该预定频率信号的一个第一驱动单元及至少一第二驱动单元,该背光模块还包括多组开关,该发光二极管阵列包括多组部分发光二极管阵列,所述切换信号分成多组切换信号,该驱动信号输出包括多组驱动信号,步骤(c)包括以下子步骤,

19.(c1)利用该第一驱动单元将该多组切换信号中对应的一组切换信号输出至该多组开关中对应的一组开关,及将该多组驱动信号中对应的一组驱动信号传输至该多组部分发光二极管阵列中对应的一组部分发光二极管阵列,及

20.(c2)利用该至少一个第二驱动单元中的每一个第二驱动单元将该多组切换信号中对应的一组切换信号输出至该多组开关中对应的一组开关,及将该多组驱动信号中对应的一组驱动信号传输至该多组部分发光二极管阵列中对应的一组部分发光二极管阵列。

21.本发明的显示器的背光驱动方法,在步骤(a)前,还包含以下步骤:

22.(d)接收来自一个控制模块的该串行输入信号及一个同步控制信号;及

23.(e)将该同步控制信号进行延迟,以产生该内部同步控制信号。

24.本发明的显示器的背光驱动方法,所述切换信号、该同步控制信号及该内部同步控制信号各自为一个具有多个方波的脉波信号,该内部同步控制信号的每一个方波的上升缘落后该同步控制信号的所述方波中的一个对应方波的上升缘,且该内部同步控制信号的每一个方波的该上升缘与所述切换信号中的最后一个切换信号的所述方波中的一个对应方波的下降缘相对应。

25.本发明的有益效果在于:通过根据该内部同步控制信号、该预定频率信号,及所述延迟指令来产生所述切换信号,以使该背光模块逐行发光,以改善该显示器具有残影的问

题,且由于该背光模块是逐行发光,其并非如现有背光模块是操作在全亮或全灭,所以该发光二极管阵列所发出的背光不需要很强。

附图说明

26.本发明的其他的特征及功效,将于参照附图的实施方式中清楚地呈现:

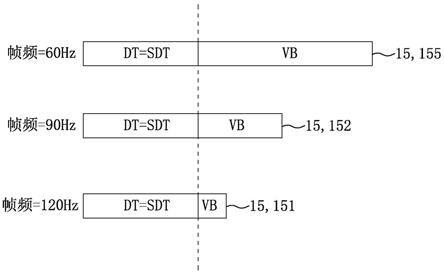

27.图1是一个电路方块图,示出一个用来实施本发明显示器的背光驱动方法的一个实施例的驱动模块;

28.图2是一个流程图,说明该实施例的该显示器的背光驱动方法;及

29.图3是一个时序图,说明该实施例的一个同步控制信号、一个内部同步控制信号、一个预定频率信号、多个切换信号,及一个驱动信号输出。

具体实施方式

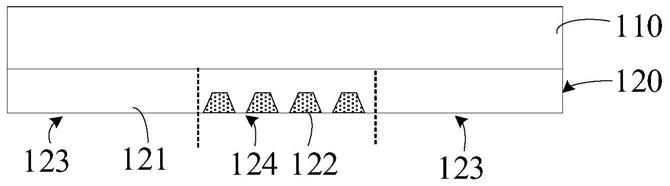

30.参阅图1,绘示了一个显示器的部分元件。该显示器为一个扫描式显示器,且用于动态图像显示(即,支持一个动态讯源dynamic frame rate)。该显示器包括一个背光模块1、一个控制模块2、一个驱动模块3、一个液晶显示面板(图未示)及其它必要元件(图未示)。该驱动模块3被用来实施本发明显示器的背光驱动方法的一个实施例,以驱动该背光模块1进行逐行发光。

31.该背光模块1包括八个开关11~18(此为本实施例举例说明,但开关的数量不限于此)及一个包括多个发光二极管190的发光二极管(light emitting diode,led)阵列19。在此实施例中,所述开关11~18分成第一组开关11~14,及第二组开关15~18。该发光二极管阵列19分成第一组部分发光二极管阵列191,及第二组部分发光二极管阵列192。该第一组开关11~14中的每一者具有一个用于接收一个输入电压v

led

的第一端、一个电连接该第一组部分发光二极管阵列191的第二端,及一个控制端。该第二组开关15~18中的每一者具有一个用于接收该输入电压v

led

的第一端、一个电连接该第二组部分发光二极管阵列192的第二端,及一个控制端。

32.需说明的是,该背光模块1逐行发光中的每一行是定义为该发光二极管阵列19中的每一行(即,每一横排)发光二极管190,也就是说,该背光模块1逐行发光是指该发光二极管阵列19中的每一行发光二极管190依序发光。图1是将所述开关11~18绘于该背光模块1内,但并非表示在制作时所述开关11~18一定要设置于该背光模块1内。实际上在制作时,所述开关11~18也可设置于该驱动模块3内,或独立设置在该背光模块1及该驱动模块3外。

33.该控制模块2产生一个相关于该液晶显示面板的图像显示频率的同步控制信号vsync,及一个具有多个延迟指令及一个图像串流的串行输入信号sdi。该图像串流是由该控制模块2内的一个图形处理单元(graphic processing unit,gpu,图未示)所产生,且其相关于该液晶显示面板所欲显示的画面。需说明的是,在此实施例中,举该串行输入信号sdi所具有的所述延迟指令的数量为八个为例,但不限于此。所述延迟指令的数量与该背光模块1的所述开关的数量相对应。每一个延迟指令指示一个延迟值,且所述延迟指令中任两个相邻者的所述延迟值的一个差值为一个固定值。在此实施例中,将所述延迟指令中的第一至第四个延迟指令分成第一组延迟指令,及将所述延迟指令中的第五至第八个延迟指令分成第二组延迟指令。

34.该驱动模块3电连接该背光模块1的所述开关11~18与该发光二极管阵列19,及该控制模块2,接收来自该控制模块2的该同步控制信号vsync及该串行输入信号sdi,并据以产生依序延迟的多个切换信号sw1~sw4、sw1’~sw4’,及延迟的一个驱动信号输出。在此实施例中,将所述切换信号sw1~sw4、sw1’~sw4’分成第一组切换信号sw1~sw4,及第二组切换信号sw1’~sw4’。该驱动信号输出包括第一组驱动信号d1~dn及第二组驱动信号d1’~dn’。该驱动模块3包括一个第一驱动单元31及至少一第二驱动单元32(为便于说明,本实施例举一个第二驱动单元32为例,但不限于此)。该第一及第二驱动单元31、32各自包括一个用来产生一个预定频率信号pll的锁相回路电路311。需说明的是,图1是将该第一及第二驱动单元31、32皆绘于该驱动模块3内,但并非表示在制作时该第一及第二驱动单元31、32共同组成单一个驱动芯片。实际上在制作时,该第一及第二驱动单元31、32为两个独立的驱动芯片。

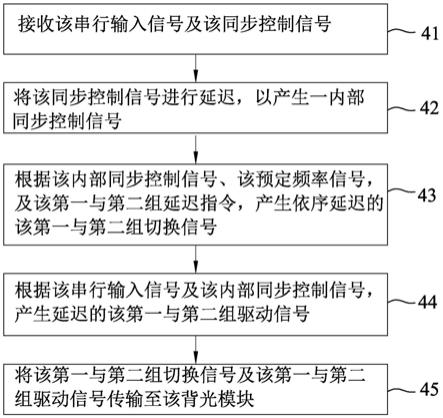

35.进一步参阅图2、图3,详细来说,该驱动模块3执行一个包括以下步骤41~45的本发明显示器的背光驱动方法,以驱动该背光模块1的该发光二极管阵列19依序逐行发光。

36.在步骤41中,该第一及第二驱动单元31、32中的每一者接收来自该控制模块2的该串行输入信号sdi及该同步控制信号vsync。

37.在步骤42中,该第一及第二驱动单元31、32中的每一者将该同步控制信号vsync进行延迟,以产生一个相关于该显示器所显示的图像更新的内部同步控制信号ivsync。

38.在此实施例中,所述切换信号sw1~sw4、sw1’~sw4’、该同步控制信号vsync及该内部同步控制信号ivsync各自为一个具有多个方波的脉波信号。该第一及第二驱动单元31、32中的每一者以一个方式来产生该内部同步控制信号ivsync,使得该内部同步控制信号ivsync的每一个方波的一上升缘落后该同步控制信号vsync的所述方波中的一对应者的一上升缘,且该内部同步控制信号ivsync的每一个方波的该上升缘与该切换信号sw4’的所述方波中的一对应者的一下降缘相对应。

39.此外,该驱动模块3会根据该内部同步控制信号ivsync及该图像串流,产生并输出另一个驱动信号输出至该显示器的该液晶显示面板,以驱动该液晶显示面板根据该另一个驱动信号输出来以一个方式进行图像显示及更新,使得该液晶显示面板追随该内部同步控制信号ivsync的变化而更新其所显示的图像。如此一来,该液晶显示面板所显示中的画面会在该第二组部分发光二极管阵列192的最后一个行扫结束后(即,对应该切换信号sw4’的所述方波中的一对应者的一下降缘)才会更新其所显示的画面。换句话说,该液晶显示面板所显示中的画面不是根据该同步控制信号vsync进行更新,进而可避免该液晶显示面板根据该同步控制信号vsync进行更新会存在该第一组部分发光二极管阵列191或该第二组部分发光二极管阵列192对应的行扫未结束,而导致其所显示的画面突然遭截断而有影像撕裂或中断的情况出现。

40.在步骤43中,该驱动模块3根据该内部同步控制信号ivsync、该预定频率信号pll,及该第一与第二组延迟指令,产生依序延迟的该第一与第二组切换信号sw1~sw4、sw1’~sw4’。

41.详细来说,该第一驱动单元31根据该内部同步控制信号ivsync、该预定频率信号pll,及该第一与第二组延迟指令中对应的一组(即,该第一组延迟指令),产生该第一与第二组切换信号sw1~sw4、sw1’~sw4’中对应的一组(即,该第一组切换信号sw1~sw4)。该第

二驱动单元32根据该内部同步控制信号ivsync、该预定频率信号pll,及该第一与第二组延迟指令中对应的一组(即,该第二组延迟指令),产生该第一与第二组切换信号sw1~sw4、sw1’~sw4’中对应的一组(即,该第二组切换信号sw1’~sw4’)。需说明的是,所述延迟指令各自指示的该延迟值相关于一个方波计数值。图3为该同步控制信号vsync、该内部同步控制信号ivsync、该预定频率信号pll、该第一与第二组切换信号sw1~sw4、sw1’~sw4’,及该第一与第二组驱动信号d1~dn、d1’~dn’各自的一部分波形的时序示意图。参数t

d1

~t

d8

为延迟时间且分别相关于所述延迟指令中的第一至第八个延迟指令的所述延迟值。所述切换信号sw1~sw4、sw1’~sw4’的产生方式相似,所以以下仅举例说明如何产生该切换信号sw1。该第一驱动单元31于该内部同步控制信号ivsync从高逻辑准位转变成低逻辑准位时,其内部的一个计数器(图未示)开始根据该第一个延迟指令指示的该延迟值对该预定频率信号pll的方波进行计数而取得该延迟时间t

d1

,并于该延迟时间t

d1

结束后(即,该计数器的一个计数结果等于该第一个延迟指令的该延迟值时),将该切换信号sw1从低逻辑准位转变成高逻辑准位一个预定持续时间。在此实施例中,每一个切换信号sw1~sw4、sw1’~sw4’的所述方波中的一者的一上升缘与该内部同步控制信号ivsync的所述方波中的一对应者的一下降缘的一个时间间隔(即,所述延迟时间t

d1

~t

d8

中其所对应的一者)相关于该第一至第八个延迟指令中其所对应的一个延迟指令。

42.在步骤44中,该驱动模块3根据该串行输入信号sdi及该内部同步控制信号ivsync,产生延迟的该第一与第二组驱动信号d1~dn、d1’~dn’。

43.详细来说,该第一驱动单元31根据该串行输入信号sdi的所述延迟指令中具有最小延迟值的一者(即,该第一个延迟指令)及该图像串流、该内部同步控制信号ivsync,产生该第一与第二组驱动信号d1~dn、d1’~dn’中对应的一组(即,该第一组驱动信号d1~dn)。该第二驱动单元32根据该串行输入信号sdi的该第一个延迟指令及该图像串流,产生该第一与第二组驱动信号d1~dn、d1’~dn’中对应的一组(即,该第二组驱动信号d1’~dn’)。需说明的是,图3中,参数d1~d8分别相关于该发光二极管阵列19的第一行至第八行的亮度信息。

44.在步骤45中,该驱动模块3将该第一与第二组切换信号sw1~sw4、sw1’~sw4’及该第一与第二组驱动信号d1~dn、d1’~dn’传输至该背光模块1,以驱动该背光模块1逐行发光。

45.详细来说,该第一驱动单元31将该第一与第二组切换信号sw1~sw4、sw1’~sw4’中对应的一组(即,该第一组切换信号sw1~sw4)输出至该第一与第二组开关11~14、15~18中对应的一组(即,该第一组开关11~14),及将该第一与第二组驱动信号d1~dn、d1’~dn’中对应的一组(即,该第一组驱动信号d1~dn)传输至该第一与第二组部分发光二极管阵列191、192中对应的一组(即,该第一组部分发光二极管阵列191)。该第二驱动单元32将该第一与第二组切换信号sw1~sw4、sw1’~sw4’中对应的一组(即,该第二组切换信号sw1’~sw4’)输出至该第一与第二组开关11~14、15~18中对应的一组(即,该第二组开关15~18),及将该第一与第二组驱动信号d1~dn、d1’~dn’中对应的一组(即,该第二组驱动信号d1’~dn’)传输至该第一与第二组部分发光二极管阵列191、192中对应的一组(即,该第二组部分发光二极管阵列192)。

46.综上所述,本发明显示器的背光驱动方法是使所述第一及第二驱动单元31、32根

据该内部同步控制信号ivsync、该预定频率信号pll,及所述延迟指令中各自的对应者,产生对应的所述切换信号sw1~sw4、sw1’~sw4’来分别切换所述开关11~14、15~18,以致所述开关11~18依序导通,并使该背光模块1逐行发光(即,使该液晶显示面板逐行插黑),以改善该显示器的残影问题。如此一来,由于所述第一及第二驱动单元31、32并非同时对所对应的第一组及第二组部分发光二极管阵列191、192进行各自的亮度控制,可避免该显示器上的互调干扰,且由于该背光模块1是逐行发光,其并非如现有背光模块的多个发光二极管是全亮或全灭而需要很强的背光,因此该背光模块1的每一个发光二极管190发光强度较低,可延长每一个发光二极管190的使用寿命。此外,该背光模块1的每一个发光二极管190并非受控制而一起导通,使得该显示器具有较低的电磁干扰。

47.以上所述者,仅为本发明的实施例而已,当不能以此限定本发明实施的范围,即凡依本发明权利要求书及说明书内容所作的简单的等效变化与修饰,皆仍属本发明的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。