1.本发明涉及一种图像处理装置以及图像处理方法,尤其涉及一种可提升省电效率的图像处理装置以及图像处理方法。

背景技术:

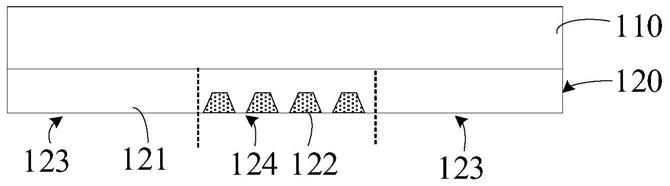

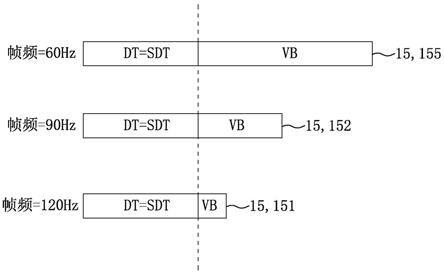

2.随着显示科技的迅速发展,目前平面显示器具有更大的尺寸与更高的分辨率。随之而来的是,显示设备的运作将需要可观的耗电量。面板自动刷新(panel self-refresh,psr)功能可用在显示静态图像(still image)时以降低显示设备的耗电量。请参考图1,图1为一现有显示系统1的示意图。显示系统1包括一处理器电路10、一图像处理装置12及一显示面板14。图像处理装置12包括一接收电路120、图像处理电路ip_1-ip_n、一抖动电路(dithering circuit)122、一输出电路124以及一内存126。如图1所示,在正常操作(normal operation mode)模式中,接收电路120接续地由处理器电路10接收输入帧fin,每一输入帧可依序为图像处理装置12的所有图像处理电路进行处理。处理器电路10可为用于提供视频源的电视处理器,且图像处理装置12可为时序控制器(timing controller)。图像处理装置12产生输出帧至显示驱动电路,进而产生用来驱动显示面板14的数据电压。

3.进一步地,如图1所示,当处理器电路10提供了视频数据而且是静态图像时,图像处理装置12可进入一psr模式。在此情况下,接收电路120接收并提供输入帧fin(此时为静态图像)至图像处理电路ip_1,同时也将输入帧fin存储至内存126。如图2所示,在psr模式期间,处理器电路10停止提供输入帧至图像处理装置12,且图像处理装置12通过图像处理电路ip_1-ip_n及抖动电路122重复地处理存储在内存126中的输入帧fin来产生输出帧。只要没有图像更新,图像处理装置12即不再由接收电路112接收输入帧,因而可以节省接收电路112的耗电量。更具体而言,由内存126所读取到的输入帧fin可依序地为图像处理电路ip_1-ip_n所处理,进而使图像处理电路ip_n产生并输出中间帧fn至抖动电路122。接着,抖动电路122对中间帧fn执行抖动操作后产生输出帧fout,以传送至输出电路124。输出电路124将输出帧fout输出至显示面板14,以进行显示。尽管处理器电路10停止输出视频数据而可节省耗电量,但是图像处理装置12中的图像处理电路ip_1-ip_n依然需重复地执行图像处理操作因而仍会耗费大量的耗电量。因此,现有技术实有改进的必要。

技术实现要素:

4.因此,本发明的主要目的之一即在于提供一种可提升省电效率的图像处理装置以及图像处理方法,以解决上述问题。

5.本发明提供一种图像处理装置,用来产生图像帧以显示在一显示面板上,包括︰一第一内存,用来存储一输入帧;复数个图像处理电路,用来依序对所述输入帧执行相应图像处理操作以产生一第一中间帧;一第一图像处理电路,耦接于所述第一内存以及所述复数个图像处理电路的最后一级,用来对所述第一中间帧执行一第一图像处理操作以产生一第二中间帧以及将所述第二中间帧写入所述第一内存以将所述输入帧置换成所述第二中间

帧;以及一抖动电路,耦接于所述第一图像处理电路以及所述第一内存,用来对由所述第一图像处理电路所传送的所述第二中间帧执行一抖动操作以产生一第一输出帧以及对从所述第一内存所读取出的所述第二中间帧执行所述抖动操作以产生接续在所述第一输出帧之后的一第二输出帧。

6.本发明还提供一种用于图像处理装置的图像处理方法,用来产生图像帧以显示在一显示面板上,所述图像处理方法包括︰将一输入帧存储至一第一内存;由复数个图像处理电路依序对所述输入帧执行相应图像处理操作以产生一第一中间帧;由一第一图像处理电路对所述第一中间帧执行一第一图像处理操作以产生一第二中间帧以及将所述第二中间帧写入所述第一内存以将所述输入帧置换成所述第二中间帧;以及由一抖动电路对由所述第一图像处理电路所传送的所述第二中间帧执行一抖动操作以产生一第一输出帧以及对从所述第一内存所读取出的所述第二中间帧执行所述抖动操作以产生接续在所述第一输出帧之后的一第二输出帧。

附图说明

7.图1为现有显示系统的示意图。

8.图2为现有显示系统操作在面板自动刷新模式时的示意图。

9.图3为本发明实施例的一显示系统的示意图。

10.图4为本发明实施例的一流程的示意图。

11.图5至图8为本发明实施例的显示系统操作在面板自动刷新模式时的示意图。

12.其中,附图标记说明如下:

13.1、3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

显示系统

14.10、30

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

处理器电路

15.12、32

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

图像处理装置

16.120、320

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

接收电路

17.122、322

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

抖动电路

18.124、324

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

输出电路

19.126、326、328

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

内存

20.14、34

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

显示面板

[0021]4ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

流程

[0022]

fin、fin1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

输入帧

[0023]

f1-fn

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

中间帧

[0024]

fout、fout1、fout2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

输出帧

[0025]

ip_1-ip_n

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

图像处理电路

[0026]

s400、s402、s404、s406、s408、s410步骤

[0027]

具体实施方式

[0028]

在说明书及后续的权利要求书当中使用了某些词汇来指称特定的组件。本领域技术人员应可理解,制造商可能会用不同的名词来称呼同样的组件。本说明书及后续的权利

要求书并不以名称的差异来做为区分组件的方式,而是以组件在功能上的差异来做为区分的基准。在通篇说明书及后续的权利要求书当中所提及的“包含”或“包括”为一开放式的用语,故应解释成“包括但不限定于”。另外,“耦接”一词在此包含任何直接及间接的电气连接手段。因此,若文中描述一第一装置耦接于一第二装置,则代表该第一装置可直接电气连接于该第二装置,或通过其他装置或连接手段间接地电气连接至该第二装置。

[0029]

请参考图3,图3为本发明实施例的一显示系统3的示意图。显示系统3包含有一处理器电路30、一图像处理装置32以及一显示面板34。处理器电路30可依序提供输入帧至图像处理装置32。输入帧可为视频图像(video image)或静态图像(still image)。处理器电路30可为图形处理器(graphics processing unit,gpu)、视觉处理单元(vision processing unit,vpu)、电视处理器或其他任何视频内容提供的视频源装置。图像处理装置32经配置成用以根据输入帧产生输出帧,以提供至显示面板34进行显示。图像处理装置32可为一时序控制器(timing controller),但不以此为限。显示面板34可用以显示输出帧。例如,显示面板34可为一有机发光二极管面板(organic light-emitting diode panel)或一液晶显示面板(liquid crystal display panel,lcd panel),但不以此为限。显示系统3还包括一显示驱动电路(未绘示于图中),其可电连接至图像处理装置32,显示驱动电路可根据来自图像处理装置32的输出帧产生数据电压,以驱动显示面板34。图像处理装置32及显示驱动电路可各自设置在不同半导体芯片中或者设置在同一电路半导体芯片中。

[0030]

图像处理装置32包括一接收电路320、图像处理电路ip_1-ip_n、一抖动电路322、一输出电路324以及内存326、328。处理器电路30与图像处理装置32可通过基于如嵌入式显示端口(embedded display port,edp)传输协议或其他任何用于图像传输的传输协议的传输接口来进行通信。接收电路320经配置成用来接收来自处理器电路30的输入帧。并且,接收电路320经配置成用以将所接收到的输入帧输出至内存326进行存储。接收电路320经配置成用以在一正常操作模式(normal operation mode)时将输入帧提供至图像处理电路ip_1-ip_n。接收电路320也可接收相关指令。

[0031]

图像处理电路ip_1-ip_n经配置成用以依序地对输入帧执行相应图像处理操作以产生一中间帧。图像处理电路ip_1耦接于接收电路320及内存326。图像处理电路ip_2耦接于图像处理电路ip_1,图像处理电路ip_3耦接于图像处理电路ip_2,依此类推,图像处理电路ip_1-ip_n串联连接在一起,图像处理电路ip_n耦接于图像处理电路ip_n-1、抖动电路322及内存326。图像处理电路ip_1-ip_n可具有不同功能,例如颜色管理(color management,cm)、高动态范围(high dynamic range,hdr)、子像素渲染(sub-pixel rendering,spr)、自动电流侦测(auto current detection,acd)、电压降转换(voltage drop conversation,vdc)、伽马校正(gamma correction)、mura补偿(mura compensation),或其他任何可对图帧进行处理以供显示的图像处理功能,其中具不同功能的该些图像处理电路可一依预定的操作顺序进行排列。例如,图像处理电路ip_1可为一hdr功能电路、图像处理电路ip_2可为一伽马校正功能电路、图像处理电路ip_3可为一mura补偿功能电路,依此类推。

[0032]

抖动电路322耦接于图像处理电路ip_n及内存326。抖动电路经配置成用以对图像处理电路ip_n所传送的中间帧或是从内存326之中所读取到的中间帧执行可增加颜色深度

的抖动操作以产生输出帧。输出电路324再将输出帧传送至显示面板34。例如,输出电路324可为一传输接口电路或一输出缓冲电路,但不以此为限。例如,输出电路324可支持一集成数据流协议(integrated stream protocol,isp)接口标准、一点对点高速(point-to-point high speed interface,phi)接口标准或其他任何传输接口标准。显示面板34可显示输出帧。内存326、328可为嵌入式动态随机存取存储器(embedded dynamic random access,edram)或动态随机存取存储器(dram),但不以此为限。

[0033]

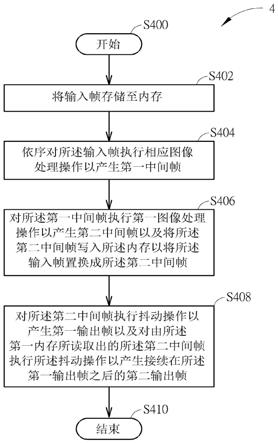

关于显示系统3的运作方式,请参考图4,图4为本发明实施例的一流程4的示意图。第4图中的流程4可被应用于第3图中所示的显示系统3的实施例。流程4包含下列步骤:

[0034]

步骤s400:开始。

[0035]

步骤s402:将输入帧存储至内存。

[0036]

步骤s404:依序对所述输入帧执行相应图像处理操作以产生第一中间帧。

[0037]

步骤s406:对所述第一中间帧执行第一图像处理操作以产生第二中间帧以及将所述第二中间帧写入所述内存以将所述输入帧置换成所述第二中间帧。

[0038]

步骤s408:对所述第二中间帧执行抖动操作以产生第一输出帧以及对从所述第一内存所读取出的所述第二中间帧执行所述抖动操作以产生接续在所述第一输出帧之后的第二输出帧。

[0039]

步骤s410:结束。

[0040]

根据流程4,在步骤s402中,于图像处理装置32运作在一正常操作模式期间,接收电路320接收从处理器电路30发送的输入帧。接收电路320将输入帧提供至图像处理电路ip_1并且将输入帧存储至内存326。当图像处理装置32进入一面板自动刷新(panel self-refresh,psr)模式,接收电路320接收从处理器电路30发送的一输入帧fin并且将输入帧fin存储至内存326。例如,接收电路320自处理器电路30接收一psr模式指令。当接收到psr模式指令时,图像处理装置32进入psr模式。因应接收到所述psr指令,接收电路320可从处理器电路30接收到一输入帧fin,并且输入帧fin可被写入内存326。如图5所示,内存326中存储着输入帧fin。输入帧fin可为静态图像(still image或称static image)。接着,在psr模式时,处理器电路30可停止提供输入帧至接收电路320。

[0041]

在步骤s404中,于psr模式下,图像处理电路ip_1-ip_n-1依序对输入帧fin执行相应图像处理操作以产生一中间帧fn-1(称第一中间帧)。如图5及图6所示,图像处理电路ip_1读取出存储在内存326中的输入帧fin。如图6所示,图像处理电路ip_1对输入帧fin执行一相应图像处理操作以产生一中间帧f1。图像处理电路ip_1将中间帧f1传送至图像处理电路ip_2。图像处理电路ip_2对中间帧f1执行一相图像处理操作以产生一中间帧f2。同样地,图像处理电路ip_2将中间帧f传送至图像处理电路ip_3以进行类似地后续操作。依此类推,图像处理电路ip_n-1对自图像处理电路ip_n-2所输出的中间帧fn-2执行一相应图像处理操作以产生一中间帧fn-1。图像处理电路ip_n-1再将中间帧fn-1传送至图像处理电路ip_n。换言之,图像处理电路ip_1读取存储在内存326中的输入帧fin,并且输入帧fin再依序为图像处理电路ip_1-ip_n-1所处理。

[0042]

例如,若n为4,图像处理电路ip_1为一hdr功能电路。图像处理电路ip_2为一spr功能电路。图像处理电路ip_3为一伽马校正功能电路。图像处理电路ip_4为一mura补偿功能电路。图像处理电路ip_4耦接于抖动电路322。在psr模式期间,图像处理电路ip_1读取出存

储在内存326中的输入帧fin并对输入帧fin执行一hdr图像处理操作以产生一中间帧f1。图像处理电路ip_1将中间帧f1传送至图像处理电路ip_2。图像处理电路ip_2对中间帧f1执行一spr图像处理操作以产生一中间帧f2,并且将中间帧f2传送至图像处理电路ip_3。图像处理电路ip_3对中间帧f2执行一伽马校正图像处理操作以产生一中间帧f3,并且将中间帧f3传送至图像处理电路ip_4。

[0043]

在步骤s406中,图像处理电路ip_n对由图像处理电路ip_n-1所输出的中间帧fn-1执行一相应图像处理操作(称第一图像处理操作)以产生一中间帧fn(称第二中间帧),并且将中间帧fn写入至内存326,以将内存326中之输入帧fin置换成中间帧fn。如图6所示,图像处理电路ip_n产生中间帧fn并将中间帧fn传送至抖动电路322以及内存326。中间帧fn被写入内存326,原先存储在内存326的输入帧fin已被置换成中间帧fn。例如,原先存储在内存326的输入帧fin被移除或是删除,而图像处理电路ip_n所产生的中间帧fn被写入至内存326以取代输入帧fin。此外,中间帧fn也可被存储至不同于内存326的内存中。请继续参考图6,抖动电路322接收到由图像处理电路ip_n所传送的中间帧fn并对中间帧fn执行一抖动操作以产生一输出帧fout1(称第一输出帧)。抖动电路322再将输出帧fout1传送至输出电路324。输出电路324将输出帧fout1传送至显示面板34。显示面板34显示输出帧fout1。

[0044]

在步骤s408中,在步骤s406中通过图像处理电路ip_n对中间帧fn-1执行相应图像处理操作而产生中间帧fn并且将中间帧fn写入内存326之后(如图6所示),图像处理电路ip_1-ip_n可进入一低功耗(low power consumption)状态,例如可称为睡眠状态(sleep state)、深度睡眠状态(deep-sleep state)或空闲状态(idle state),以降低电力功率消耗。在低功耗状态中,图像处理电路ip_1-ip_n可停止处理图像(即停止在正常操作状态下的图像处理操作)。当图像处理装置32离开psr模式时,图像处理电路ip_1-ip_n可被切换至一待命状态(stand-by state)。如图7所示,在接收到由图像处理电路ip_n所传送的中间帧fn并对中间帧fn执行抖动操作以产生输出帧fout1之后,抖动电路322可读取出存储在内存326中的中间帧fn,并对从内存326中所读取出的中间帧fn执行抖动操作以产生一输出帧fout2(称第二输出帧)。同样地,抖动电路322将输出帧fout2传送至输出电路324。输出电路324将输出帧fout2传送至显示面板34。显示面板34显示输出帧fout2。其中输出帧fout2在输出帧fout1之后。

[0045]

换言之,在产生输出帧fout2以及其后续输出帧的期间,图像处理电路ip_1-ip_n处于睡眠(低功耗)状态。因此,相较于现有的psr方法,本发明实施例在产生输出帧fout2以及其后续输出帧的期间将可消耗较少的电力,本发明实施例图像处理装置32将可大幅地降低功耗并有效地提高省电效率。

[0046]

在输出帧fout2之后,抖动电路322可周期性地由内存326中读取出中间帧fn并对从内存326中所读取出的中间帧fn执行抖动操作以产生后续输出帧,直到图像处理电路ip_1-ip_n离开睡眠状态。当操作在psr模式期间,处理器电路30可传送作为一更新输入帧的新静态图像至图像处理装置32,在此情况下,图像处理电路ip_1-ip_n可依据一垂直同步信号(vsync)从睡眠状态当中被启动或唤醒进而处理所述更新输入帧。如图8所示,处理器电路30可提供一新输入帧fin1至接收电路320。接收电路320接收输入帧fin1并将输入帧fin1内存326以取代原本用来产生先前的输出帧的中间帧fn。接着,类似于图6所示的操作,图像处理电路ip_1-ip_n再次执行步骤s404与s406。如图8所示,图像处理电路ip_1-ip_n可依序地

对输入帧fin1执行相应图像处理操作而产生中间帧f1'-fn',图像处理电路ip_n可将中间帧fn'存储至内存326以取代输入帧fin1。抖动电路322可再次执行步骤s408以产生一更新输出帧以及其后续输出帧。

[0047]

要注意的是,在操作于psr模式之下,本发明实施例的图像处理电路ip_1-ip_n可以更早或是更晚进入低功耗状态,而不限于此。图像处理电路ip_1-ip_n越早进入低功耗状态,则可节省越多功耗。在前述图5至图7的实施例中,在psr模式下的第一个输出帧是通过图像处理电路ip_1-ip_n所产生的。接着,在psr模式下的第二个输出帧是通过处理存储在内存326的中间帧所产生,而非通过图像处理电路ip_1-ip_n所产生的。在一变化实施例中,在步骤s408中,在图像处理电路ip_n对中间帧fn-1执行相应图像处理操作而产生中间帧fn之后,中间帧fn可以不被写入内存326且输入帧fin仍被保留在内存326之中。图像处理电路ip_1可周期性地重复自内存326中读取输入帧fin,而图像处理电路ip_1-ip_n可对输入帧fin执行相应图像处理操作以产生后续中间帧,抖动电路322可对后续中间帧执行抖动操作以产生输出帧。在几次反复迭代执行自内存326中重复读取输入帧fin与依序执行相应图像处理操作的程序后,图像处理电路ip_n产生相应于最后次迭代处理之一相应中间帧并将所述相应中间帧写入内存326以置换输入帧fin。接着,抖动电路322开始周期性地读取出存储在内存326之中的中间帧并对自内存326所读取出的中间帧执行抖动操作以产生后续输出帧。因此,图像处理电路ip_n越早将中间帧存储至内存326,则抖动电路322可越早开始周期性地读取出存储在内存326之中的中间帧,而可实现更低的功耗。

[0048]

此外,在一实施例中,图像处理电路ip_1-ip_n当中至少之一个图像处理电路包括一mura补偿电路。包含有所述mura补偿电路的图像处理电路可被耦接至内存328。内存328存储有de-mura查找表。包含有所述mura补偿电路的图像处理电路可读取内存328中的de-mura查找表。例如,当图像处理电路ip_1包含有一mura补偿电路时,图像处理电路ip_1的mura补偿电路可读取内存328中的de-mura查找表并且依据de-mura查找表对输入帧fin执行一mura补偿操作以产生一中间帧f1。当图像处理电路ip_2-ip_n当中之一包含有一mura补偿电路时,相应图像处理电路的mura补偿电路可读取内存328中的de-mura查找表并且依据de-mura查找表对前一级图像处理电路所传送来的中间帧执行一mura补偿操作以产生一相应中间帧。由于存取内存会消耗较大的电力,图像处理电路ip_1-ip_n当中包含有mura补偿电路的图像处理电路越早进入低功耗状态则可节省越多的电力功耗。

[0049]

综上所述,相较于现有的psr方法,本发明实施例提供了在产生输出帧期间不需经由图像处理电路来处理而能更节省电力功耗的方式,因而大幅地降低在psr模式期间的电力功耗并有效地提高省电效率。

[0050]

以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。