包括第一存储器和第二存储器的流体喷射设备

背景技术:

1.作为流体喷射系统的一个示例的喷墨打印系统可以包括打印头、向打印头供应液体墨水的墨水供应器和控制打印头的电子控制器。作为流体喷射设备的一个示例的打印头通过多个喷嘴或孔口并向打印介质(诸如一张纸)喷射墨滴,以在打印介质上进行打印。在一些示例中,孔口被布置成至少一个列或阵列,使得当打印头和打印介质相对于彼此移动时,来自孔口的适当顺序的墨水喷射使得字符或其他图像被打印在打印介质上。

附图说明

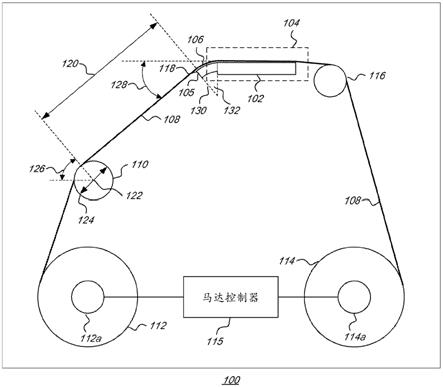

2.图1是示出了流体喷射系统的一个示例的框图。

3.图2是示出了流体喷射设备的一个示例的示意图。

4.图3是示出了包括流体喷射设备的第一存储器和第二存储器的电路的一个示例的框图。

5.图4是示出了包括流体喷射设备的第一存储器和第二存储器的电路的另一个示例的框图。

6.图5是示出了包括流体喷射设备的存储器元件的电路的一个示例的示意图。

7.图6是示出了包括流体喷射设备的存储器元件的电路的另一个示例的示意图。

8.图7a是示出了包括流体喷射设备的多个存储器元件的电路的一个示例的示意图。

9.图7b是示出了包括流体喷射设备的多个存储器元件的电路的另一个示例的示意图。

10.图8a至图8b是示出了包括流体喷射设备的多个存储器元件和多个流体致动设备的电路的一个示例的示意图。

11.图9a是示出了包括第一存储器、第二存储器和流体致动设备的电路的一个示例的示意图。

12.图9b是示出了包括第一存储器、第二存储器和流体致动设备的电路的另一个示例的示意图。

13.图10a和图10b是示出了图9b的电路的操作的一个示例的时序图。

14.图11a和图11b是示出了图9b的电路的操作的另一个示例的时序图。

15.图12是示出了流体喷射系统的一个示例的框图。

16.图13a至图13d是示出了用于对流体喷射设备的第一存储器和第二存储器进行访问的方法的一个示例的流程图。

17.图14a至图14b是示出了用于对流体喷射设备的存储器进行访问的方法的一个示例的流程图。

18.图15a至图15b是示出了用于对流体喷射设备的存储器进行访问的方法的另一个示例的流程图。

具体实施方式

19.在以下具体实施方式中,对附图进行了参考,这些附图形成具体实施方式的一部分,并且在附图中通过说明的方式示出了可以实践本公开的具体示例。应当理解的是,在不脱离本公开的范围的情况下,可以利用其他示例并且可以做出结构或逻辑变化。因此以下具体实施方式不应当被理解为限制性的意义,并且本公开的范围由所附权利要求限定。应当理解的是,除非另外特别指出,否则本文所描述的各种示例的特征可以部分地或全部地彼此组合。

20.如本文所使用的,“逻辑高”信号是逻辑“1”或“导通”信号或具有约等于供应到集成电路的逻辑电力的电压(例如,在约1.8v与15v之间,如5.6v)的信号。如本文所使用的,“逻辑低”信号是逻辑“0”或“关断”信号或具有约等于供应到集成电路的逻辑电力的逻辑电力接地回路的电压(例如,约0v)的信号。

21.打印系统中使用的打印头可以包括被激活以使打印流体微滴从对应的喷嘴中喷射的喷嘴。每个喷嘴包括流体致动设备。流体致动设备在被激活时使打印流体微滴被对应的喷嘴喷射。在一个示例中,每个流体致动设备包括加热元件(例如,热敏电阻),加热元件在被激活时产生热量,以使喷嘴的激发室中的打印流体汽化。打印流体的汽化使得打印流体的微滴从喷嘴中排出。在其他示例中,每个流体致动设备包括压电元件。在被激活时,压电元件施加力以使打印流体微滴从喷嘴中喷射。在其他示例中,其他类型的流体致动设备可以用于从喷嘴喷射流体。

22.打印系统可以是二维(2d)打印系统或三维(3d)打印系统。2d打印系统分配如墨水等打印流体,以在如纸质介质或其他类型的打印介质等打印介质上形成图像。3d打印系统通过沉积连续的构建材料层来形成3d对象。从3d打印系统分配的打印流体可以包括墨水以及用于熔化构建材料层的粉末、详细描绘构建材料层(如通过限定构建材料层的边缘或形状)等的试剂。

23.如本文所使用的,术语“打印头”通常指打印头模具或包括安装在支撑结构上的多个模具的组件。模具(还被称为“集成电路模具”)包括衬底,该衬底上设置有用于形成喷嘴和/或用于控制喷嘴进行的流体喷射的控制电路系统的各种层。

24.尽管在一些示例中参考了打印系统中使用的打印头,但应注意,本公开的技术或机制适用于在能够通过喷嘴分配流体的非打印应用中使用的其他类型的流体喷射设备。这样的其他类型的流体喷射设备的示例包括在流体感测系统、医疗系统、车辆、流体流动控制系统等中使用的那些。

25.在包括打印头模具或其他类型的流体喷射模具的设备的尺寸不断缩小时,用于控制设备的电路系统的信号线的数量可能影响设备的总尺寸。大量的信号线可能导致使用大量的信号焊盘(被称为“接合焊盘”)来将信号线电连接到外部线路。向流体喷射设备添加特征可能导致使用增加数量的信号线(和对应的接合焊盘),这可能会占用宝贵的模具空间。可以添加到流体喷射设备的附加特征的示例包括存储器设备。

26.因此,本文公开了流体喷射设备(其包括一个模具或多个模具)的各种示例电路,这些示例电路可以共享控制线和数据线以允许减少流体喷射设备的信号线的数量。如本文所使用的,术语“线路”是指可以用于承载信号(或多个信号)的电导体(或替代性地,多个电导体)。

27.图1是示出了流体喷射系统100的一个示例的框图。流体喷射系统100包括流体喷射控制器102和流体喷射设备106。流体喷射控制器102通过多个控制线104通信地耦接到流体喷射设备106。流体喷射设备106可以包括控制电路108、流体致动设备110、第一存储器112和第二存储器114。控制电路108电耦接到流体致动设备110、第一存储器112和第二存储器114。

28.流体喷射控制器102与流体喷射设备106分开。流体喷射控制器102可以包括处理器、专用集成电路(asic)或用于通过控制线104来控制流体喷射设备106的其他合适的逻辑电路系统。例如,在打印系统中,流体喷射控制器102可以是作为打印系统的一部分的打印头驱动控制器,而流体喷射设备106可以是作为(包括墨水或另一种试剂的)打印墨盒的一部分或另一个结构的一部分的打印头集成电路模具。

29.流体喷射设备106的流体致动设备110可以包括可选择性地控制以分配流体的喷嘴阵列。第一存储器112可以包括用于存储标识数据和/或关于流体喷射设备106的其他信息(如用于唯一地标识流体喷射设备106)的id存储器。第二存储器114可以包括用于存储与流体致动设备110有关的数据的激发存储器,其中,该数据可以包括以下各项中的任一项或某种组合,如示例:模具位置、区域信息、落重编码信息、认证信息、用于启用或禁用所选流体致动设备的数据等等。

30.第一存储器112和第二存储器114可以用不同类型的存储器实施,以形成混合存储器布置。第一存储器112可以用非易失性存储器(如电可编程只读存储器(eprom))实施。第二存储器114可以用非易失性存储器(如熔丝存储器)来实施,其中,熔丝存储器包括可以选择性地熔断(或不熔断)以将数据编程到第二存储器114中的熔丝阵列。尽管上文列出了存储器的类型的具体示例,但是应当注意的是,在其他示例中,可以用其他类型的存储器来实施第一存储器112和第二存储器114。在一些示例中,可以用同一类型的存储器来实施第一存储器112和第二存储器114。

31.在一个示例中,流体喷射设备106的流体致动设备110、第一存储器112和第二存储器114可以形成在公共模具(即,流体喷射模具)上。在另一个示例中,流体致动设备110可以在一个模具(即,流体喷射模具)上实施,而第一存储器112和第二存储器114可以在单独的模具(或相应的单独模具)上实施。例如,第一存储器112和第二存储器114可以形成于与流体喷射模具分开的第二模具上,或者替代性地,第一存储器112和第二存储器114可以形成于与流体喷射模具分开的相应的不同模具上。在其他示例中,第一存储器112的一部分可以处于一个模具上,并且第一存储器112的另一部分可以处于另一个模具上。同样,第二存储器114的一部分可以处于一个模具上,并且第二存储器114的另一部分可以处于另一个模具上。

32.控制电路108基于通过控制线104接收的控制信号来控制流体致动设备110、第一存储器112和第二存储器114的操作。控制线104包括激发线、csync线、选择线、地址数据线、id线、时钟线和其他线路。在其他示例中,可以存在多条激发线和/或多条选择线和/或多条地址数据线。控制电路108可以基于id线上的id信号选择流体致动设备110或第二存储器114。id线还可以用于对第一存储器112进行访问以进行读取和/或写入操作。可以基于选择线和地址数据线上的选择信号和数据信号来寻址第一存储器112的存储器元件。

33.激发线用于在流体致动设备110响应于id线上的第一逻辑电平而被控制电路108

选择时控制流体致动设备110的激活。如果这种流体致动设备(或多个流体致动设备)是基于选择线和地址数据线上的选择信号和数据信号而被寻址的,则激发线上的激发信号在被设置为第一逻辑电平时使相应的流体致动设备(或多个流体致动设备)被激活。如果激发信号被设置为与第一逻辑电平不同的第二逻辑电平,则流体致动设备(或多个流体致动设备)不会被激活。激发线还可以用于在第二存储器114响应于id线上的第二逻辑电平而被控制电路108选择时对第二存储器114进行访问以进行读取和/或写入操作。可以基于选择线和地址数据线上的选择信号和数据信号来寻址第二存储器114的存储器元件。

34.csync信号用于在流体喷射设备106中发起地址(被称为ax和ay)。选择线可以用于选择某些流体致动设备或存储器元件。地址数据线可以用于承载地址位(或多个地址位),以对特定的流体致动设备或存储器元件(或特定的流体致动设备组或存储器元件组)进行寻址。时钟线可以用于承载用于控制电路108的时钟信号。

35.根据本公开的一些实施方式,为了提高流体喷射设备106上必须设置的输入/输出(i/o)焊盘的灵活性并减少其数量,每条激发线和id线执行主要任务和次要任务两者。如上所述,激发线的主要任务是激活所选(多个)流体致动设备110。激发线的次要任务是传送第二存储器114的数据。以此方式,可以在流体喷射控制器102与第二存储器114之间设置数据路径(通过激发线),而无需在流体喷射控制器102与流体喷射设备106之间设置单独的数据线。

36.id线的主要任务是传送第一存储器112的数据。id线的次要任务是使控制电路108启用流体致动设备110或者第二存储器114。以此方式,可以使用公共激发线来控制流体致动设备110的激活并传送第二存储器114的数据,其中,id线可以用于选择流体致动设备110何时由激发线控制以及激发线何时可以被用来传送第二存储器114的数据。

37.图2是更详细地示出了图1的流体喷射设备106的一个示例的示意图。流体喷射设备106包括流体致动设备110、第一存储器112、第二存储器114、锁存器130和132、移位寄存器解码器134、地址生成器136、激发线140、id线142以及开关144、146、148和150。在一个示例中,激发线140和id线142是图1的控制线104的一部分。锁存器130和132、移位寄存器解码器134、地址生成器136以及开关144、146、148和150可以是图1的控制电路108的一部分。

38.id线142电耦接到锁存器130的输入、锁存器132的输入和第一存储器112。激发线140电耦接到开关146的一侧并且电耦接到流体致动设备110。锁存器130的输出电耦接到开关146的控制输入。开关146的另一侧电耦接到第二存储器114。锁存器132的输出电耦接到开关148的控制输入。开关148电耦接在第二存储器114与公共或接地节点152之间。开关150电耦接在流体致动设备110与公共或接地节点152之间。地址生成器136的输出电耦接到开关148的控制输入和开关150的控制输入。移位寄存器134的输出电耦接到开关144的控制输入。开关144电耦接在第一存储器112与公共或接地节点152之间。

39.第一存储器112可以包括多个存储器元件。开关144可以包括多个开关,其中,每个开关对应于第一存储器112的存储器元件之一。移位寄存器解码器134通过闭合与所选存储器元件相对应的开关144来选择第一存储器112的存储器元件进行读取和/或写入访问。移位寄存器解码器134通过断开与被禁用的存储器元件相对应的开关144来禁用第一存储器112的存储器元件。在第一存储器112的存储器元件由移位寄存器解码器134选择的情况下,可以通过id线142对存储器元件进行访问以进行读取和/或写入操作。

40.锁存器130接收id线142上的id信号,锁存id信号的逻辑电平,并且基于已锁存的值来控制开关146。响应于已锁存的值的第一逻辑电平(例如,逻辑高),锁存器130导通开关146。响应于已锁存的值的第二逻辑电平(例如,逻辑低),锁存器130关断开关146。在开关146闭合的情况下,启用第二存储器114以通过激发线140进行读取和/或写入访问。在开关146断开的情况下,第二存储器114被禁用。

41.第二存储器114可以包括多个存储器元件。开关148可以包括多个开关,其中,每个开关对应于第二存储器114的存储器元件之一。开关150可以包括多个开关,其中,每个开关对应于流体致动设备110之一。锁存器132接收id线142上的id信号,锁存id信号的反相逻辑电平,并且基于已锁存的值来控制开关148。响应于已锁存的值的第一逻辑电平(例如,逻辑高),锁存器132禁用开关148(即,阻止开关148导通)。响应于已锁存的值的第二逻辑电平(例如,逻辑低),锁存器132启用开关148(即,允许开关148导通)。

42.地址生成器136生成用于选择第二存储器114的存储器元件或流体致动设备110的地址信号ax和ay。第二存储器114的存储器元件或流体致动设备110的选择也可以基于地址数据线上的数据信号(d2)。因此,如图2所示并且在下文更详细地描述的,可以基于id

×

d2

×

axay来控制开关148,并且可以基于id

’×

d2

×

axay来控制开关150。在开关150断开、开关146闭合和开关148闭合的情况下,可以通过激发线140对第二存储器114进行访问以进行读取和/或写入操作。在开关146断开、开关148断开和开关150闭合的情况下,可以通过激发线140激活流体致动设备110。

43.图3是示出了包括流体喷射设备的第一存储器和第二存储器的电路200的一个示例的框图。在一个示例中,电路200是用于驱动多个流体致动设备的集成电路的一部分。电路200包括第一存储器112和第二存储器114。第一存储器112包括多个第一存储器元件2121到212

m

,其中,“m”是任何合适的存储器元件数量。第二存储器114包括多个第二存储器元件2141到214

n

,其中,“n”是任何合适的存储器元件数量。第一存储器112和第二存储器114可以包括相同数量的存储器元件或不同数量的存储器元件。

44.电路200还包括多条第一数据(d11到d13)线2161到2163和第二数据(d2)线218。第一数据线2161到2163电耦接到第一存储器112,并且第二数据线218电耦接到第二存储器114。在一个示例中,第一数据线2161到2163和第二数据线218是图1的控制线104的地址数据线的一部分。在此示例中,第一存储器112的存储器元件212响应于多条第一数据线2161到2163上的第一数据而被启用,并且第二存储器114的存储器元件214响应于第二数据线218上的第二数据而被启用。

45.图4是示出了包括流体喷射设备的第一存储器和第二存储器的电路230的另一个示例的框图。在一个示例中,电路230是用于驱动多个流体致动设备的集成电路的一部分。电路230包括如先前参考图3所描述和图示的第一存储器112和第二存储器114。电路230还包括id线142、第一选择(s4)线236和第二选择(s5)线238。第一选择线236电耦接到第一存储器112,并且第二选择线238和id线142电耦接到第二存储器114。在此示例中,第一存储器112的存储器元件212响应于第一选择线236上的第一逻辑电平而被启用,并且第二存储器114的存储器元件214响应于第二选择线238上的第一逻辑电平和id线上的第一逻辑电平而被启用。

46.在一个示例中,图3的电路200可以与图4的电路230组合。因此,第一存储器112可

以基于通过第一数据d11、d12和d13生成的地址(例如,经由图1的移位寄存器解码器134)被访问,而第二存储器114可以基于通过第二数据d2生成的地址被访问。第一数据和第二数据可以完全彼此独立。另外,第一存储器112可以响应于s4选择信号而被启用,而第二存储器114可以响应于s5选择信号而被启用。s4选择信号和s5选择信号可以交错。以此方式,可以避免由于移位寄存器(例如,图1的移位寄存器解码器134)造成的id信号损坏。

47.图5是示出了包括流体喷射设备的存储器元件的电路250的一个示例的示意图。在一个示例中,电路250是用于驱动多个流体致动设备的集成电路的一部分。电路250包括激发线140、id线142、存储器元件252、锁存器254和放电路径256。激发线140电耦接到存储器元件252。id线142电耦接到锁存器254的输入。锁存器254的输出电耦接到放电路径256的输入。放电路径256电耦接在存储器元件252与公共或接地节点152之间。

48.放电路径256在存储器元件252未被启用以进行读取和/或写入访问时防止存储器元件252浮动。在此示例中,锁存器254响应于id线142上的第一逻辑电平(例如,逻辑高)而禁用放电路径并且响应于id线上的第二逻辑电平(例如,逻辑低)而启用放电路径。当存储器元件252被启用时,放电路径256被禁用并且存储器元件252可以通过激发线140被访问以进行读取和/或写入操作。在一个示例中,锁存器254提供图2的锁存器132,放电路径256是到开关148的控制输入的一部分,并且存储器元件252是图2的第二存储器114的存储器元件。

49.图6是示出了包括流体喷射设备的存储器元件的电路270的另一个示例的示意图。在一个示例中,电路270是用于驱动多个流体致动设备的集成电路的一部分。电路270包括激发线140、id线142、存储器元件252、锁存器272和开关274。开关274电耦接在激发线140与存储器元件252之间。锁存器272的输入电耦接到id线142。锁存器272的输出电耦接到开关274的控制输入。存储器元件252电耦接到公共或接地节点152。

50.在此示例中,锁存器272响应于id线142上的第一逻辑电平(例如,逻辑高)而启用(即,导通)开关274,并且响应于id线上的第二逻辑电平(例如,逻辑低)而禁用(即,关断)开关274。在开关274被启用的情况下,激发线140电连接到存储器元件252。在开关274被禁用的情况下,激发线140与存储器元件252断开电连接。在开关274被启用的情况下,存储器元件252可以通过激发线140被访问以进行读取和/或写入操作。在一个示例中,锁存器272提供图2的锁存器130,开关274提供图2的开关146,并且,存储器元件252提供图2的第二存储器114的存储器元件。

51.图7a是示出了包括流体喷射设备的多个存储器元件的电路300的一个示例的示意图。在一个示例中,电路300是用于驱动多个流体致动设备的集成电路的一部分。电路300包括激发线140、多个存储器元件2141到214

n

、第一开关304和多个第二开关3081到308

n

。开关304电耦接在激发线140与每个存储器元件2141到214

n

的第一侧之间。开关304的控制输入电耦接到控制(vy)信号线302。每个第二开关3081到308

n

的一侧电耦接到相应存储器元件2141到214

n

的第二侧。每个第二开关3081到308

n

的另一侧电耦接到公共或接地节点152。每个第二开关3081到308

n

的控制输入分别电耦接到控制(x1到x

n

)信号线3061到306

n

。

52.vy控制信号可以基于(例如,id线142上的)id信号。控制信号x1到x

n

可以基于(例如,id线142上的)id信号、(例如,d2数据线218上的)d2数据信号以及(例如,来自地址生成器136的)ax和ay地址信号。在此示例中,可以通过响应于vy信号而导通开关304并且响应于

相应的x1到x

n

信号而导通至少一个相应的第二开关3081到308

n

,启用存储器元件2141到214

n

。在存储器元件2141到214

n

被启用的情况下,可以通过激发线140对启用的存储器元件进行访问以进行读取和/或写入操作。在一个示例中,第一开关304提供图2的开关146,并且每个第二开关3081到308

n

提供图2的开关148。

53.图7b是示出了包括流体喷射设备的多个存储器元件的电路320的另一个示例的示意图。在一个示例中,电路320是用于驱动多个流体致动设备的集成电路的一部分。电路320类似于先前参考图7a所描述和示出的电路300,除了在电路320中使用第一晶体管324代替第一开关304并且使用多个第二晶体管3281到328

n

代替第二开关3081到308

n

。第一晶体管324具有电耦接在激发线140与每个存储器元件2141到214

n

的第一侧之间的源极

‑

漏极路径。每个第二晶体管3281到328

n

具有电耦接在相应存储器元件2141到214

n

与公共或接地节点152之间的源极

‑

漏极路径。每个第二晶体管3281到328

n

的栅极分别电耦接到控制信号线3061到306

n

。

54.在此示例中,可以通过响应于逻辑高vy信号而导通第一晶体管324并且响应于相应的逻辑高x1到x

n

信号而导通至少一个相应的第二晶体管3281到328

n

来启用存储器元件2141到214

n

。在存储器元件2141到214

n

被启用的情况下,可以通过激发线140对启用的存储器元件进行访问以进行读取和/或写入操作。在一个示例中,第一晶体管324提供图2的开关146,并且每个第二晶体管3281到328

n

提供图2的开关148。

55.图8a至图8b是示出了包括流体喷射设备的多个存储器元件和多个流体致动设备的电路350的一个示例的示意图。在一个示例中,电路350是用于驱动多个流体致动设备的集成电路的一部分。电路350包括先前参考图7b所描述和图示的电路320。另外,如图8a所图示的,电路350包括多个流体致动设备3521到352

n

和多个第三开关(例如,第三晶体管)3581到358

n

。每个流体致动设备3521到352

n

电耦接在激发线140与相应第三晶体管3581到358

n

的源极

‑

漏极路径的一侧之间。每个第三晶体管3581到358

n

的源极

‑

漏极路径的另一侧电耦接到公共或接地节点152。每个第三晶体管3581到358

n

的栅极分别电耦接到控制(y1到y

n

)信号线3561到356

n

。

56.如图8b所图示的,电路350还包括地址生成器136和解码器360。地址生成器136的输出通过ax地址信号线362和ay地址信号线364电耦接到解码器360的输入。解码器360的其他输入电耦接到id线142和第二数据线218。解码器360的第一输出分别通过控制信号线3061到306

n

电耦接到第二晶体管3281到328

n

的栅极。解码器360的第二输出分别通过控制信号线3561到356

n

电耦接到第三晶体管3581到358

n

的栅极。

57.ax和ay是通过地址生成器136所输出的,诸如响应于选择线上的选择信号和csync线上的csync信号。在一个示例中,解码器360接收地址(例如,d2、ax、ay),以响应于该地址而导通相应的第二晶体管3281到328

n

或相应的第三晶体管3581到358

n

。在另一个示例中,响应于id线142上的第一逻辑电平(例如,逻辑高),解码器360响应于地址而导通相应的第二晶体管3281到328

n

,并且响应于id线142上的第二逻辑电平(例如,逻辑低),解码器360响应于地址而导通相应的第三晶体管3581到358

n

以启用相应的流体致动设备3521到352

n

。在流体致动设备3521到352

n

被启用的情况下,启用的流体致动设备可以通过激发线140被激活。在一个示例中,每个第三晶体管3581到358

n

提供图2的开关150。

58.图9a是更详细地示出了包括第一存储器112、第二存储器114和流体致动设备110

的电路400的一个示例的示意图。在一个示例中,电路400是用于驱动多个流体致动设备的集成电路的一部分。尽管第一存储器112包括多个存储器元件,但图9a中仅示出了一个存储器元件212。同样,尽管第二存储器114包括多个存储器元件,但图9a中仅示出了一个存储器元件214,并且尽管流体致动设备110包括多个流体致动设备,但图9a中仅示出了一个流体致动设备352。

59.电路400包括激发线140、id线142、第一数据线2161到2163、第二数据线218、选择线236和238、ax地址信号线362、ay地址信号线364、移位寄存器解码器134以及晶体管324、328和358,如先前所描述的。另外,电路400包括缓冲器408、反相器(inverter)410和晶体管402、404、406、412、414、416、418、420、422、432、434、436、438、440和442。在一个示例中,晶体管402、404和406可以提供图2的开关144。缓冲器408可以提供图2的锁存器130或图6的锁存器272。反相器410可以提供图2的锁存器132或图5的锁存器254。晶体管416可以为第一存储器114提供图5的放电路径256的一部分。晶体管436可以为流体致动设备110提供放电路径。晶体管412、414、418、420、422、432、434、438、440和442可以提供图8b的解码器360的一部分。

60.移位寄存器解码器134的第一输入电耦接到第一数据线2161到2163。移位寄存器解码器134的第二输入电耦接到第一选择(s4)线236。移位寄存器解码器134的输出电耦接到晶体管402、404和406的栅极。晶体管402、404和406串联电耦接在存储器元件212与公共或接地节点152之间。当晶体管402、404和406导通时,存储器元件212被寻址,使得存储器元件212的数据可以经由id线142被访问。

61.移位寄存器解码器134包括移位寄存器,移位寄存器连接到第一数据线2161到2163中的每一条以将地址数据位输入到移位寄存器解码器134。每个移位寄存器包括一串移位寄存器单元,这一串移位寄存器单元可以被实施为触发器、其他存储元件或可以维持其值直至下次选择存储元件的任何采样和保持电路(如用于对地址数据位进行预充电和评估的电路)。这一串中一个移位寄存器单元的输出可以提供至下一个移位寄存器单元的输入,以通过移位寄存器执行数据移位。通过每个移位寄存器提供的地址数据位连接到晶体管402、404和406中的相应晶体管的栅极。

62.通过使用移位寄存器解码器134中的移位寄存器,可以使用少量的数据线2161到2163来选择较大的地址空间。例如,每个移位寄存器可以包括八个(或任何其他数量的)移位寄存器单元。在将三个地址数据位(d11、d12和d13)输入到包括三个移位寄存器的移位寄存器解码器134的情况下(每个的长度为八),则可以由移位寄存器解码器134寻址的地址空间是512位(代替在不使用移位寄存器解码器134的移位寄存器的情况下使用这三个地址位时的仅八位)。移位寄存器解码器134的输出可以响应于第一选择(s4)线236上的第一逻辑电平而被启用,并且响应于第一选择(s4)线236上的第二逻辑电平而被禁用。

63.缓冲器408通过vy节点409电耦接在id线142与晶体管324的栅极之间。反相器410通过vx节点411电耦接在id线142与晶体管416的栅极之间。晶体管416的源极

‑

漏极路径的一侧电耦接到公共或接地节点152。晶体管416的源极

‑

漏极路径的另一侧电耦接到晶体管414的源极

‑

漏极路径的一侧、晶体管418的源极

‑

漏极路径的一侧、晶体管420的源极

‑

漏极路径的一侧以及晶体管422的源极

‑

漏极路径的一侧。每个晶体管418、420和422的源极

‑

漏极路径的另一侧电耦接到公共或接地节点152。晶体管418的栅极电耦接到第二数据线218。

晶体管420的栅极电耦接到ax地址信号线362。晶体管422的栅极电耦接到ay地址信号线364。晶体管414的栅极电耦接到第二选择(s5)线238。晶体管414的源极

‑

漏极路径的另一侧电耦接到晶体管412的源极

‑

漏极路径的一侧和晶体管328的栅极。晶体管412的源极

‑

漏极路径的另一侧和栅极电耦接到第一选择(s4)线236。

64.晶体管436的栅极电耦接到id线142。晶体管436的源极

‑

漏极路径的一侧电耦接到公共或接地节点152。晶体管436的源极

‑

漏极路径的另一侧电耦接到晶体管434的源极

‑

漏极路径的一侧、晶体管438的源极

‑

漏极路径的一侧、晶体管440的源极

‑

漏极路径的一侧以及晶体管442的源极

‑

漏极路径的一侧。每个晶体管438、440和442的源极

‑

漏极路径的另一侧电耦接到公共或接地节点152。晶体管438的栅极电耦接到第二数据线218。晶体管440的栅极电耦接到ax地址信号线362。晶体管442的栅极电耦接到ay地址信号线364。晶体管434的栅极电耦接到第二选择(s5)线238。晶体管434的源极

‑

漏极路径的另一侧电耦接到晶体管432的源极

‑

漏极路径的一侧和晶体管358的栅极。晶体管432的源极

‑

漏极路径的另一侧和栅极电耦接到第一选择(s4)线236。

65.使用两个单独的解码器来分别控制连接到存储器元件214和流体致动设备352的相应的晶体管328和358。晶体管328的栅极连接到包括晶体管412、414、418、420和422的第一解码器。晶体管358的栅极连接到包括晶体管432、434、438、440和442的第二解码器。s4选择信号可以比s5选择信号在时间上更早地被激活。ax、ay、d2、s4和s5的组合形成了到第一解码器和第二解码器的地址输入。

66.当id线142上的id信号处于第一逻辑电平(例如,逻辑高)时,晶体管436导通并且使晶体管358的栅极保持放电(即,禁用晶体管358的栅极),使得流体致动设备352保持停用。另外,当id信号处于第一逻辑电平(例如,逻辑高)时,晶体管324由缓冲器408导通并且晶体管416由反相器410关断,使得当晶体管328基于到第一解码器的地址输入而导通时,存储器元件214可以通过激发线140被访问以进行读取和/或写入操作。

67.当id线142上的id信号处于第二逻辑电平(例如,逻辑低)时,晶体管436关断,使得当晶体管358基于到第二解码器的地址输入而导通时,流体致动设备352可以通过激发线140而被激活。另外,当id信号处于第二逻辑电平(例如,逻辑低)时,晶体管324由缓冲器408关断并且晶体管416由反相器410导通。在晶体管416导通的情况下,晶体管328的栅极保持放电(即,晶体管328的栅极被禁用),使得存储器元件214保持取消选择。

68.图9b是示出了包括第一存储器112、第二存储器114和流体致动设备110的电路450的另一个示例的示意图。在一个示例中,电路450是用于驱动多个流体致动设备的集成电路的一部分。电路450类似于先前参考图9a所描述和示出的电路400,除了在电路450中,使用晶体管452、454、456、458、460和462代替缓冲器408;并且使用晶体管468、470和472代替反相器410。

69.晶体管460和462串联电耦接在节点459与公共或接地节点152之间。晶体管462的栅极电耦接到id线142,并且晶体管460的栅极电耦接到s4选择线236。晶体管458具有电耦接在s3选择线234与节点459之间的源极

‑

漏极路径。晶体管458的栅极电耦接到s3选择线234。晶体管454和晶体管456串联电耦接在晶体管324的栅极与公共或接地节点152之间。晶体管456的栅极电耦接到节点459。晶体管454的栅极电耦接到s5选择线238。晶体管452具有电耦接在s4选择线236与晶体管324的栅极之间的源极

‑

漏极路径。晶体管452的栅极电耦接

到s4选择线236。

70.晶体管470和晶体管472串联电耦接在晶体管416的栅极与公共或接地节点152之间。晶体管472的栅极电耦接到id线142。晶体管470的栅极电耦接到s4选择线236。晶体管468具有电耦接在s3选择线234与晶体管416的栅极之间的源极

‑

漏极路径。晶体管468的栅极电耦接到s3选择线234。

71.s3选择信号可以比s4选择信号在时间上更早地被激活。s4选择信号可以比s5选择信号在时间上更早地被激活。在id线142上的id信号处于第一逻辑电平(例如,逻辑高)的情况下,第二逻辑电平(例如,逻辑低)响应于s3选择信号和s4选择信号而被锁存在vx节点411上。在id信号处于第二逻辑电平(例如,逻辑低)的情况下,第一逻辑电平(例如,逻辑高)响应于s3选择信号和s4选择信号而被锁存在vx节点411上。

72.在id线142上的id信号处于第一逻辑电平(例如,逻辑高)的情况下,第二逻辑电平(例如,逻辑低)响应于s3选择信号和s4选择信号而被锁存在节点459上。在id信号处于第二逻辑电平(例如,逻辑低)的情况下,第一逻辑电平(例如,逻辑高)响应于s3选择信号和s4选择信号而被锁存在节点459上。在节点459上的第一逻辑电平(例如,逻辑高)的情况下,第二逻辑电平(例如,逻辑低)响应于s4选择信号和s5选择信号而被锁存在vy节点409上。在节点459上的第二逻辑电平(例如,逻辑低)的情况下,第一逻辑电平(例如,逻辑高)响应于s4选择信号和s5选择信号而被锁存在vy节点409上。因此,在id线142上的id信号处于第一逻辑电平(例如,逻辑高)的情况下,第一逻辑电平(例如,逻辑高)响应于s3选择信号、s4选择信号和s5选择信号而被锁存在vy节点409上。在id信号处于第二逻辑电平(例如,逻辑低)的情况下,第二逻辑电平(例如,逻辑低)响应于s3选择信号、s4选择信号和s5选择信号而被锁存在vy节点409上。

73.图10a和图10b是示出了图9b的电路450的操作的一个示例的时序图。图10a示出了当存储器元件214被启用时的时序图500a,并且图10b示出了当流体致动设备352被启用时的时序图500b。时序图500a和500b包括csync信号、s1选择信号、s2选择信号、s3选择线234上的s3选择信号、s4选择线236上的s4选择信号、s5选择线238上的s5选择信号、时钟信号、d11数据线2161上的d11数据信号、d12数据线2162上的d12数据信号、d2数据线218上的d2数据信号、id线142上的id信号、vx节点411上的vx信号以及激发线140上的激发信号。

74.s1至s5选择信号被依次激活。s1和s2选择信号可以由第一存储器112使用,如用于控制移位寄存器解码器134。如图10a所示,在502处,当s4信号为逻辑高、id信号为逻辑高时,vx为逻辑低。因此,当s5信号为逻辑高时,存储器元件214的放电路径断开并且存储器元件214被启用以经由激发信号进行读取和/或写入访问,如504处所指示的。如图10b所示,在506处,当s4信号为逻辑高、id信号为逻辑低时,vx为逻辑高。因此,当s5信号为逻辑高时,存储器元件214的放电路径接通并且存储器元件214被禁用。在存储器元件214被禁用的情况下,流体致动设备352可以被启用并且可以经由激发信号被激活,如508处指示的。

75.在一个示例中,如图10a和图10b所示,id信号和激发信号可以不同时导通(即,逻辑高)。因此,当s4信号为逻辑高时,id信号被锁存以提供vx,以在s5为逻辑高时为激发信号做准备。这还确保用于存储器元件214的晶体管328的栅极或者用于流体致动设备352的晶体管358的栅极具有放电路径以避免未选择时的浮动状况。应避免浮动状况以防止存储在第二存储器114中的数据损坏。

76.图11a和图11b是示出了图9b的电路的操作的另一个示例的时序图。图11a示出了当存储器元件214被启用时的时序图550a,并且图11b示出了当流体致动设备352被启用时的时序图550b。时序图550a和550b包括csync信号、s1选择信号、s2选择信号、s3选择线234上的s3选择信号、s4选择线236上的s4选择信号、s5选择线238上的s5选择信号、时钟信号、d11数据线2161上的d11数据信号、d12数据线2162上的d12数据信号、d2数据线218上的d2数据信号、id线142上的id信号、vy节点409上的vy信号以及激发线140上的激发信号。

77.如图11a所示,在552处,当s4信号为逻辑高、id信号为逻辑高时,vy在s5信号为逻辑高时为逻辑高。在vy逻辑高的情况下,存储器元件214被启用以经由激发信号进行读取和/或写入访问,如554处所指示的。如图11b所示,在556处,当s4信号为逻辑高、id信号为逻辑低时,vy在s5信号为逻辑高时为逻辑低。在vy逻辑低的情况下,存储器元件214被禁用并且与激发信号隔离。在存储器元件214被禁用的情况下,流体致动设备352可以被启用并且可以经由激发信号被激活,如558处指示的。

78.在一个示例中,如图11a和图11b所示,id信号和激发信号可以不同时导通(即,逻辑高)。因此,当s4信号为逻辑高时,id信号被锁存以提供vy,以在s5为逻辑高时为激发信号做准备。当流体致动设备352被激活时,晶体管324还用作激发信号与存储器元件214之间的隔离器。这可以防止存储器元件214在高频下经受高电压,这可以提高存储器元件214的可靠性。

79.图12是示出了流体喷射系统600的一个示例的框图。流体喷射系统600包括流体喷射组件(如打印头组件602),以及流体供应组件(如墨水供应组件610)。在所示出的示例中,流体喷射系统600还包括服务站组件604、托架组件616、打印介质传输组件618和电子控制器620。尽管以下描述提供了用于关于墨水进行流体处理的系统和组件的示例,但是所公开的系统和组件也适用于处理除墨水之外的流体。

80.打印头组件602包括至少一个打印头或流体喷射模具606(如图1的流体喷射设备106),至少一个打印头或流体喷射模具通过多个孔口或喷嘴608喷射墨滴或液滴。在一个示例中,液滴被引导朝向介质,如打印介质624,以打印到打印介质624上。在一个示例中,打印介质624包括任何类型的合适的片材,如纸、卡片纸、透明胶片、聚酯薄膜、织物等。在另一个示例中,打印介质624包括用于三维(3d)打印的介质,如粉末床,或用于生物打印和/或药物发现测试的介质,如贮存器或容器。在一个示例中,喷嘴608布置成至少一个列或阵列,使得当打印头组件602和打印介质624相对于彼此移动时,墨水从喷嘴608进行的适当排序的喷射导致字符、符号和/或其他图形或图像被打印在打印介质624上。

81.墨水供应组件610向打印头组件602供应墨水并且包括用于储存墨水的贮存器612。因此,在一个示例中,墨水从贮存器612流动到打印头组件602。在一个示例中,打印头组件602和墨水供应组件610被一起容纳在喷墨或流体喷射打印墨盒或笔中。在另一个示例中,墨水供应组件610与打印头组件602分开并且通过接口连接613(如供应管和/或阀)将墨水供应到打印头组件602。

82.托架组件616相对于打印介质传输组件618定位打印头组件602,并且打印介质传输组件618相对于打印头组件602定位打印介质624。因此,打印区626被限定成在打印头组件602与打印介质624之间的区域中与喷嘴608相邻。在一个示例中,打印头组件602是扫描型打印头组件,使得托架组件616相对于打印介质传输组件618移动打印头组件602。在另一

个示例中,打印头组件602是非扫描型打印头组件,使得托架组件616相对于打印介质传输组件618将打印头组件602固定在规定的位置处。

83.服务站组件604提供打印头组件602的喷射、擦拭、加盖和/或灌注以维持打印头组件602、并且更具体地喷嘴608的功能。例如,服务站组件604可以包括橡胶叶片或擦拭器,橡胶叶片或擦拭器周期性地经过打印头组件602以擦拭和清洁喷嘴608上的过量墨水。另外,服务站组件604可以包括覆盖打印头组件602的盖,用于在不使用时段期间保护喷嘴608免于变干。另外,服务站组件604可以包括墨盂,打印头组件602在吐出期间将墨水喷射到墨盂中以确保贮存器612维持适当水平的压力和流动性,并且确保喷嘴608不会堵塞或渗漏。服务站组件604的功能可以包括服务站组件604与打印头组件602之间的相对运动。

84.电子控制器620通过通信路径603与打印头组件602通信,通过通信路径605与服务站组件604通信,通过通信路径617与托架组件616通信,并且通过通信路径619与打印介质传输组件618通信。在一个示例中,当打印头组件602安装在托架组件616中时,电子控制器620和打印头组件602可以通过通信路径601经由托架组件616进行通信。电子控制器620还可以与墨水供应组件610通信,使得在一种实施方式中,可以检测到新的(或使用过的)墨水供应器。

85.电子控制器620从主机系统(如计算机)接收数据628,并且可以包括用于临时存储数据628的存储器。数据628可以沿电子、红外线、光学或其他信息输送路径发送到流体喷射系统600。数据628表示例如要打印的文档和/或文件。因此,数据628形成流体喷射系统600的打印作业并且包括至少一个打印作业命令和/或命令参数。

86.在一个示例中,电子控制器620提供对打印头组件602的控制,包括用于从喷嘴608喷射墨滴的时序控制。因此,电子控制器620限定喷射的墨滴的图案,喷射的墨滴在打印介质624上形成字符、符号和/或其他图形或图像。时序控制以及因此喷射的墨滴的图案由打印作业命令和/或命令参数确定。在一个示例中,形成电子控制器620的一部分的逻辑和驱动电路系统定位于打印头组件602上。在另一个示例中,形成电子控制器620的一部分的逻辑和驱动电路系统定位于打印头组件602之外。

87.图13a至图13d是示出了用于对流体喷射设备的第一存储器和第二存储器进行访问的方法700的一个示例的流程图。在一个示例中,方法700可以由图1的流体喷射系统100实施。如图13a所图示的,在702处,方法700包括顺序地生成第一选择信号和第二选择信号。在704处,方法700包括响应于第一选择信号和多条第一数据线上的第一数据而启用第一存储器元件。在706处,方法700包括响应于第二选择信号和第二数据线上的第二数据而启用第二存储器元件。

88.如图13b所图示的,在708处,方法700可以还包括生成地址信号。在这种情况下,启用第二存储器元件可以包括响应于第二选择信号、第二数据线上的第二数据和地址信号而启用第二存储器元件。

89.如图13c所图示的,在710处,方法700可以还包括生成id线上的信号。在712处,方法700可以还包括响应于第二选择信号和id线上的第一逻辑电平而启用流体致动设备。在这种情况下,启用第二存储器元件可以包括响应于第二选择信号和id线上的第二逻辑电平而启用第二存储器元件。

90.如图13d所图示的,在714处,方法700可以还包括在第一存储器元件被启用的情况

下经由id线对第一存储器元件进行访问。在716处,方法700可以还包括在第二存储器元件被启用的情况下经由激发线对第二存储器元件进行访问。

91.图14a至图14b是示出了用于对流体喷射设备的存储器进行访问的方法800的一个示例的流程图。在一个示例中,方法800可以由图1的流体喷射系统100实施。如图14a所图示的,在802处,方法800包括:响应于id线上的第一逻辑电平,经由第一开关将多个存储器元件中的每个存储器元件的第一侧电连接到激发线,并且,响应于id线上的第二逻辑电平,经由第一开关将多个存储器元件中的每个存储器元件的第一侧与激发线断开电连接。在804处,方法800包括:响应于地址信号,经由多个第二开关中的相应第二开关将多个存储器元件中的相应存储器元件的第二侧电连接到公共节点。

92.在一个示例中,第一开关包括第一晶体管并且多个第二开关包括多个第二晶体管。如图14b所图示的,在806处,方法800可以还包括:在相应存储器元件电连接在激发线与公共节点之间的情况下,经由激发线对多个存储器元件中的相应存储器元件进行访问。

93.图15a至图15b是示出了用于对流体喷射设备的存储器进行访问的方法900的另一个示例的流程图。在一个示例中,方法900可以由图1的流体喷射系统100实施。如图15a所图示的,在902处,方法900包括:生成id线上的id信号。在904处,方法900包括:顺序地生成第一选择信号和第二选择信号。在906处,方法900包括:响应于第一选择信号而锁存id信号。在908处,方法900包括:响应于已锁存的id信号具有第一逻辑电平而启用存储器元件。在910处,方法900包括:在存储器元件被启用的情况下,响应于第二选择信号经由激发线对存储器元件进行访问。

94.在一个示例中,启用存储器元件包括:响应于已锁存的id信号具有第一逻辑电平,将存储器元件电连接到激发线。在另一个示例中,锁存id信号包括:将id信号反相,并且,响应于第一选择信号,锁存经反相的id信号;并且,启用存储器元件包括:响应于已锁存的经反相id的信号具有第二逻辑电平,关断耦接到存储器元件的放电路径。

95.如图15b所图示的,在912处,方法900可以还包括:响应于id信号具有第二逻辑电平,启用流体致动设备。在914处,方法900可以还包括:在流体致动设备被启用的情况下,响应于第二选择信号,经由激发线激活流体致动设备。

96.尽管本文已经示出和描述了特定示例,但是在不脱离本公开的范围的情况下,各种各样的替代和/或等效实施方式可以代替所示出和描述的特定示例。本技术旨在覆盖本文所讨论的特定示例的任何修改或变化。因此,本公开旨在仅由权利要求及其等同所限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。