数字滤波器、a/d转换器、传感器处理电路及传感器系统

技术领域

1.本公开总体涉及数字滤波器、a/d转换器、传感器处理电路及传感器系统,更具体地涉及用于对a/d转换单元(其对模拟信号进行数字转换)的输出执行滤波处理的数字滤波器、a/d转换器、传感器处理电路及传感器系统。

背景技术:

2.已经从相关技术(参见例如专利文献1)中了解了包括数字滤波器的a/d转换器。专利文献1公开了设计为实现与δ∑a/d转换器的分辨率一样高的分辨率同时又保持与逐次逼近寄存器(sar)a/d转换器的功耗一样低的功耗的噪声整形a/d转换器。

3.专利文献1的噪声整形sar a/d转换器具有将集成电路设置为用于正常的sar a/d转换器的附加组成元件的配置。在对最低有效位(lsb)执行逐次比较操作之后,电容式模数转换器(dac)的残留电压经历积分操作,并且如此获得的积分值在下次执行采样时被反馈,因此获得噪声整形特性。

4.为了提高a/d转换器的输出数据的精度,要使数字转换处理完成要花费很长时间,因此引起延迟的增加。

5.引用列表

6.专利文献

7.专利文献1:jp 2017

‑

147712 a

技术实现要素:

8.结合上述背景,本公开的目标因此是提供数字滤波器、a/d转换器、传感器处理电路及传感器系统,它们均对使输出数据具有较高精度和较低延迟做出贡献。

9.根据本公开的一个方面的数字滤波器用于a/d转换器中并且包括第一滤波器和第二滤波器。所述第一滤波器通过对所述a/d转换器中包括的a/d转换单元的输出执行滤波处理而输出第一数字数据。所述第二滤波器通过对所述a/d转换单元的输出执行滤波处理而输出第二数字数据。所述第二数字数据具有比所述第一数字数据更低的分辨率或更少的有效位数。所述第二滤波器在所述第一滤波器输出所述第一数字数据之前输出所述第二数字数据。

10.根据本公开的另一方面的a/d转换器包括:上述数字滤波器;以及所述a/d转换单元。

11.根据本公开的又一方面的传感器处理电路包括上述a/d转换器。所述a/d转换器将来自传感器的模拟信号转换成数字数据并且向控制电路输出所述数字数据。

12.根据本公开的另一方面的传感器系统包括:上述传感器处理电路;以及所述传感器。

附图说明

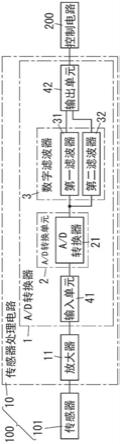

13.图1是包括根据本公开的示例性实施例的数字滤波器和a/d转换器的传感器系统的框图;

14.图2示出了a/d转换器如何操作;

15.图3是包括根据本公开的示例性实施例的第一种变型的数字滤波器的传感器系统的框图;

16.图4是包括根据本公开的示例性实施例的另一变型的数字滤波器的传感器系统的框图;

17.图5是包括根据本公开的示例性实施例的又一变型的数字滤波器的传感器系统的框图;以及

18.图6是包括根据本公开的示例性实施例的另一变型的a/d转换器的传感器系统的框图。

具体实施方式

19.要注意,要在下面描述的实施例及其变型仅是本公开的示例并且不应该被解释为限制。相反,示例性实施例及其变型可以根据设计选择或任何其他因素,在不背离本公开的真实精神和范围的情况下容易地以各种方式修改。

20.[实施例]

[0021]

(1)配置

[0022]

图1是包括根据示例性实施例的数字滤波器3和a/d(模数)转换器1的传感器系统100的框图。

[0023]

根据该实施例的a/d转换器1用在传感器系统100的模拟前端(传感器处理电路10)中,并且配置为将由传感器101提供的模拟信号转换成数字数据。

[0024]

传感器处理电路10包括a/d转换器1和放大器11,对由传感器101提供的信号执行信号处理,并且向控制电路200输出如此处理的信号。

[0025]

传感器系统100包括传感器101和传感器处理电路10。

[0026]

传感器101配置为检测测量对象的物理量或其变化的幅度。传感器101向传感器处理电路10输出模拟信号,该模拟信号的幅度由基于检测结果的电压值表示。也就是说,传感器101用作用于输出模拟信号的信号输出单元。传感器处理电路10将由传感器101提供的模拟信号转换成数字数据并且向控制电路200输出数字数据。

[0027]

在该实施例中,传感器系统100例如可应用于诸如汽车之类的移动载具。在这种情况下,传感器101可以被实现为用于检测作为测量对象的移动载具的加速度的加速度传感器。接收由传感器101检测的结果的控制电路200可以被实现为作为安装在汽车上的一个车载设备的电子控制单元(ecu)。然而,这仅是示例并且不应该被解释为限制。传感器101不一定是加速度传感器,而是例如也可以是陀螺仪传感器、压力传感器或运动传感器。此外,传感器系统100也可应用于不同类型的设备,而不是诸如汽车之类的移动载具。

[0028]

传感器处理电路10是用于对由传感器101提供的模拟信号执行信号处理并且向控制电路200输出所产生的数据的模拟前端。

[0029]

传感器处理电路10包括a/d转换器1和放大器11。

[0030]

放大器11配置为放大由传感器101提供的模拟信号。放大器11接收作为传感器101的输出信号的模拟信号。放大器11根据预定的放大系数放大输入模拟信号的幅度,并且向连接到放大器11之后的a/d转换器1输出具有经放大的幅度的信号。

[0031]

a/d转换器1包括a/d转换单元2、数字滤波器3、输入单元41和输出单元42。a/d转换器1将模拟信号的幅度转换成具有规定的位(bit)数的数字数据并向控制电路200输出如此获得的数字数据。在该实施例中,a/d转换器1可以配置为例如输出21位数字数据。要注意,由a/d转换器1输出的数字数据的位数不一定是21位。

[0032]

输入单元41电连接到放大器11。输入单元41经由放大器11接收作为传感器101的输出信号的模拟信号。

[0033]

a/d转换单元2包括a/d转换器21。

[0034]

a/d转换器21被实现为δ∑a/d转换器。a/d转换器21包括减法器、积分器、量化器和d/a转换器并且执行δ∑调制。减法器被实现为差分放大器。减法器接收由传感器101提供的模拟信号和参考信号。减法器从模拟信号中减去参考信号。积分器通过将由减法器获得的计算结果加在一起来计算累积值。量化器通过将由积分器获得的结果与参考信号进行比较来确定1位数字值。由量化器如此获得的结果输出到在a/d转换器21之后布置的数字滤波器3并且输出到d/a转换器。d/a转换器被实现为1位d/a转换器,并且基于由量化器获得的结果来确定要反馈到减法器的参考信号。

[0035]

可选地,a/d转换器21也可以被实现为包括多个减法器和多个积分器的高阶δ∑a/d转换器。a/d转换器21的阶数越高,则生成量化噪声的频率范围可能越高。这使转换精度提高。

[0036]

数字滤波器3对a/d转换单元2的输出执行滤波处理。数字滤波器3包括第一滤波器31和第二滤波器32。

[0037]

第一滤波器31和第二滤波器32并联连接。第一滤波器31和第二滤波器32均接收作为a/d转换单元2的输出数据的1位数字数据。

[0038]

第一滤波器31和第二滤波器32均对a/d转换单元2的输出执行滤波处理。第一滤波器31和第二滤波器32均将带宽限制功能和抽取(decimation)功能作为其用于滤波处理的功能。换言之,第一滤波器31和第二滤波器32均包括低通滤波器和抽取滤波器。被实现为δ∑a/d转换器的a/d转换器21的输出包括由量化噪声的噪声整形生成的rf噪声,并且因为过采样而具有比其原始采样速率更高的数据速率。因此,第一滤波器31和第二滤波器32通过使用带宽限制功能而减小rf噪声,并且还通过使用抽取功能而降低数据速率。

[0039]

第一滤波器31和第二滤波器32均通过对a/d转换单元2的输出执行滤波处理而生成多位数字数据。第二滤波器32具有比第一滤波器31更低的分辨率。在该实施例中,第一滤波器31通过对a/d转换单元2的输出执行滤波处理而生成21位数字数据(第一数字数据)。第二滤波器32通过对a/d转换单元2的输出执行滤波处理而生成3位数字数据(第二数字数据)。由第二滤波器32生成的第二数字数据对应于由第一滤波器31生成的第一数字数据的高位。

[0040]

输出单元42具有多个输出端口,并且向控制电路200输出第一数字数据和第二数字数据。输出单元42具有针对21位的数字数据分别设置的21个输出端口。当输出21位的第一数字数据时,输出单元42通过使用全部21个输出端口来输出第一数字数据。此外,第二数

字数据对应于第一数字数据的3个最高有效位。因此,当输出3位的第二数字数据时,输出单元42通过使用21个输出端口中与第一数字数据的3个最高有效位相对应的3个输出端口来输出第二数字数据。

[0041]

在此情况下,第二滤波器32生成具有比由第一滤波器31生成的数字数据更低的分辨率的数字数据。因此,由第二滤波器32执行的滤波处理需要比由第一滤波器31执行的滤波处理更短的时间。因此,在第一滤波器31生成第一数字数据之前,第二滤波器32生成第二数字数据。输出单元42输出更早生成的第二数字数据,然后输出第一数字数据。也就是说,第二数字数据的延迟(时延)低于第一数字数据的延迟。同时,比第二数字数据更晚输出的第一数字数据具有比第二数字数据更高的分辨率。

[0042]

(示例性操作)

[0043]

将参考图2描述根据该实施例的a/d转换器1的示例性操作。

[0044]

在以下描述中,将描述如何对提供给输入单元41的模拟信号的幅度执行a/d转换处理。

[0045]

第一滤波器31和第二滤波器32并联连接,并且基本同时开始执行滤波处理。第二滤波器32生成分辨率低于由第一滤波器31生成的数字数据的分辨率的数字数据。因此,在时刻t1,第二滤波器32比第一滤波器31更早地结束生成第二数字数据。输出单元42向控制电路200输出由第二滤波器32生成的第二数字数据。要注意,严格而言,例如,在第二滤波器32生成了第二数字数据时的时刻和输出单元42输出第二数字数据时的时刻之间由输出单元42执行的信号处理引起了时间滞后。然而,该时间滞后不明显,因此在该示例中忽略。

[0046]

然后,在时刻t2处,第一滤波器31结束生成第一数字数据。输出单元42向控制电路200输出由第一滤波器31生成的第一数字数据。要注意,严格而言,例如,在第一滤波器31生成了第一数字数据时的时刻和输出单元42输出第一数字数据时的时刻之间由输出单元42执行的信号处理引起了时间滞后。然而,该时间滞后不明显,因此在该示例中忽略。

[0047]

如可以看到的,根据该实施例的a/d转换器1在输出具有较高分辨率的第一数字数据之前输出具有较低分辨率的第二数字数据。也就是说,与第一数字数据相比,第二数字数据具有较低的分辨率,但是引起更低的延迟。这允许根据该实施例的a/d转换器1输出具有较高分辨率的第一数字数据和引起较低延迟的第二数字数据,因此对使输出数据具有较高分辨率和较低延迟做出贡献。

[0048]

此外,控制电路200可以在接收具有较高分辨率的第一数字数据之前接收具有较低分辨率的第二数字数据。这允许控制电路200快速地检测由传感器101提供的模拟信号具有大于门限值的幅度的异常状态。因此,控制电路200可以更快速地执行在出现任何异常状态时要执行的操作。也就是说,这对提高从异常状态出现时的时刻到控制电路200开始执行其应对异常的操作时的时刻的控制电路200的响应能力做出了贡献。

[0049]

此外,控制电路200可以独立于第二数字数据而接收具有较高分辨率的第一数字数据,因此,可以基于第一数字数据对控制对象进行准确的控制。

[0050]

(变型)

[0051]

接着,将描述根据示例性实施例的a/d转换器1的变型。

[0052]

(第一变型)

[0053]

将参考图3描述根据第一变型的a/d转换器1。

[0054]

第一变型的具有与上述实施例的a/d转换器1的对应组成元件具有相同功能的任意组成元件将通过与该对应组成元件相同的附图标记指定,并且在本文中在适当时省略了其描述。

[0055]

根据该变型的a/d转换器1包括:包括第一滤波器31a和第二滤波器32a的数字滤波器3a。

[0056]

第一滤波器31a和第二滤波器32a串联连接。第二滤波器32a布置在第一滤波器31a之前,并且从a/d转换单元2接收1位数字数据。

[0057]

第二滤波器32a通过对a/d转换单元2的输出执行滤波处理而生成3位的第二数字数据。第二滤波器32a向第一滤波器31a和输出单元42输出3位的第二数字数据。

[0058]

输出单元42向控制电路200输出由第二滤波器32a生成的第二数字数据。

[0059]

此外,第一滤波器31a通过对由第二滤波器32a提供的3位的第二数字数据执行滤波处理而生成21位的第一数字数据。也就是说,在该变型中,第二滤波器32a对a/d转换单元2的输出执行初级滤波处理,并且第一滤波器31a对a/d转换单元2的输出执行次级滤波处理。作为通过第二滤波器32a的初级滤波处理的结果,生成了由3个高位组成的数字数据。作为通过第一滤波器31a的次级滤波处理的结果,生成了由18个低位组成的数字数据。第一滤波器31a向输出单元42输出21位的第一数字数据,该21位的第一数字数据是通过初级滤波处理生成的3个高位的数字数据和通过次级滤波处理生成的18个低位的数字数据的组合。

[0060]

输出单元42向控制电路200输出由第一滤波器31a生成的第一数字数据。

[0061]

如可以看到的,在该变型中,a/d转换单元2的输出经历通过第二滤波器32a的初级滤波处理,然后经历通过第一滤波器31a的次级滤波处理。因此,第二数字数据比第一数字数据更早地生成并且向控制电路200输出。也就是说,与第一数字数据相比,第二数字数据具有较低的分辨率,但是引起了更低的延迟。这允许根据该变型的a/d转换器1输出具有较高分辨率的第一数字数据和引起较低延迟的第二数字数据,因此同时对使输出数据具有较高分辨率和较低延迟做出贡献。

[0062]

此外,根据该变型,第一滤波器31a和第二滤波器32a串联连接,以使第二滤波器32a执行初级滤波处理并且使第一滤波器31a执行次级滤波处理。与第一滤波器31和第二滤波器32并联连接的配置(参见图1)相比,这减小了第一滤波器31a的尺寸。

[0063]

(其他变型)

[0064]

在上述示例中,由第二滤波器32(32a)生成的第二数字数据具有比由第一滤波器31(31a)生成的第一数字数据更低的分辨率。然而,这仅是示例并且不应该被解释为限制。

[0065]

可选地,第一滤波器31(31a)和第二滤波器32(32a)可以配置为,使由第二滤波器32(32a)生成的第二数字数据具有比由第一滤波器31(31a)生成的第一数字数据更少的有效位数。如本文中使用的,“有效位数”根据被实现为δ∑a/d转换器的a/d转换器21的过采样速率与第一滤波器31(31a)或第二滤波器32(32a)的输出数据速率之间的比率(即,抽取比率)来获得。由第二滤波器32(32a)生成的数字数据具有比由第一滤波器31(31a)生成的数字数据更少的有效位数。因此,第二滤波器32(32a)需要比第一滤波器31(31a)更短的滤波处理时间。因此,第二数字数据比第一数字数据更早地生成并且向控制电路200输出。也就是说,第二数字数据的延迟低于第一数字数据的延迟。

[0066]

此外,虽然在上述示例中数字滤波器3包括第一滤波器31(31a)和第二滤波器32

(32a),但是数字滤波器3可以包括大量的滤波器。

[0067]

如图4所示,数字滤波器3还可以包括第三滤波器33。在图4所示的示例中,数字滤波器3包括并联连接的第一滤波器31、第二滤波器32和第三滤波器33。第三滤波器33通过对a/d转换单元2的输出执行滤波处理而生成多位数字数据。例如,由第三滤波器33输出的第三数字数据可以具有比由第一滤波器31生成的第一数字数据更低的分辨率以及比由第二滤波器32生成的第二数字数据更高的分辨率。此外,由第三滤波器33输出的第三数字数据可以引起比由第一滤波器31生成的第一数字数据更低的延迟以及比由第二滤波器32输出的第二数字数据更高的延迟。

[0068]

如图5所示,数字滤波器3a还可以包括第三滤波器33a。在图5所示的示例中,数字滤波器3a包括串联连接的第一滤波器31a、第二滤波器32a和第三滤波器33a。第三滤波器33a设置在第二滤波器32a之后和第一滤波器31a之前。a/d转换单元2的输出经历通过第二滤波器32a的初级滤波处理、通过第三滤波器33a的次级滤波处理、以及之后通过第一滤波器31a的第三级滤波处理。因此,由第三滤波器33a输出的第三数字数据可以具有比由第一滤波器31a生成的第一数字数据更低的分辨率以及比由第二滤波器32a生成的第二数字数据更高的分辨率。此外,由第三滤波器33a输出的第三数字数据可以引起比由第一滤波器31a生成的第一数字数据更低的延迟以及比由第二滤波器32a输出的第二数字数据更高的延迟。

[0069]

此外,在上述示例中,a/d转换单元2被配置为仅包括被实现为δ∑a/d转换器的a/d转换器21。然而,这仅是示例并且不应该被解释为限制。

[0070]

如图6所示,a/d转换单元2可以包括a/d转换器21(在下文中称为“第一a/d转换器21”)和在第一a/d转换器21之前设置的第二a/d转换器22。第二a/d转换器22被实现为逐次逼近寄存器(sar)a/d转换器。也就是说,a/d转换器1可以被实现为具有多个a/d转换结构的混合a/d转换器。

[0071]

第二a/d转换器22包括电容式数模(d/a)转换器。电容式d/a转换器包括多个电容器(电容元件)。每个电容器具有电连接到输入单元41的一端和选择性地电连接到第一电压源或第二电压源中的一个的另一端。第一电压源和第二电压源具有相互不同的输出电压。

[0072]

第二a/d转换器22逐次且重复地执行将模拟信号的幅度电压与由电容式d/a转换器生成的电压进行比较的操作,由此生成多位数字数据。具体地,a/d转换单元2包括比较器和逐次逼近寄存器控制电路。比较器将由输入单元41接收的输入电压(即,模拟信号的幅度)与由电容式d/a转换器生成的电压(用于比较的参考电压)进行比较。然后,逐次逼近寄存器控制电路基于由比较器做出的比较的结果来生成下一位的逐次比较控制信号,并且向电容式d/a转换器输出该控制信号。根据逐次比较控制信号,电容式d/a转换器的每个电容器使其另一端选择性地电连接到第一电压源或第二电压源中的一个。第二a/d转换器22重复地执行这种逐次比较操作,由此生成多位数字数据。

[0073]

在由第二a/d转换器22执行逐次比较操作之后,第一a/d转换器21接收电容式d/a转换器的残留电压(与量化噪声相对应)。

[0074]

在该变型中,从输出单元42向控制电路200输出数字数据,该数字数据的高位是由第二a/d转换器22生成的数字数据并且低位是由第一a/d转换器21和数字滤波器3生成的数字数据。

[0075]

第二a/d转换器22不一定被实现为逐次逼近寄存器a/d转换器,而是也可以被实现为具有任何其他a/d转换结构的a/d转换器(例如,快速a/d转换器)。

[0076]

此外,在上述示例中,数字滤波器3是a/d转换器1的组成元件中的一个。然而,数字滤波器3可以是设置在a/d转换器1外部的组成元件。

[0077]

(概括)

[0078]

一种根据第一方面的数字滤波器(3),用于a/d转换器(1)中并且包括第一滤波器(31,31a)和第二滤波器(32,32a)。第一滤波器(31,31a)通过对a/d转换器(1)中包括的a/d转换单元(2)的输出执行滤波处理而输出第一数字数据。第二滤波器(32,32a)通过对a/d转换单元(2)的输出执行滤波处理而输出第二数字数据。所述第二数字数据具有比所述第一数字数据更低的分辨率或更少的有效位数。在第一滤波器(31,31a)输出第一数字数据之前,第二滤波器(32,32a)输出第二数字数据。

[0079]

该方面使数字滤波器(3)输出具有较高分辨率或较多有效位数的第一数字数据以及具有较低分辨率或较少有效位数的第二数字数据,因此对使输出数据具有较高精度和较低延迟做出贡献。

[0080]

在根据可以结合第一方面实现的第二方面的数字滤波器(3)中,a/d转换单元(2)包括δ∑a/d转换器(a/d转换器21)。第一滤波器(31,31a)和第二滤波器(32,32a)中的每一个包括抽取滤波器。

[0081]

该方面对提高数字转换的精度做出贡献。

[0082]

在根据可以结合第一方面或第二方面实现的第三方面的数字滤波器(3)中,第一滤波器(31a)和第二滤波器(32a)串联连接,并且第二滤波器(32a)布置在第一滤波器(31a)之前。

[0083]

根据该方面,第二滤波器(32a)执行初级滤波处理并且第一滤波器(31a)执行次级滤波处理,因此对减小第一滤波器(31a)的尺寸做出贡献。

[0084]

在根据可以结合第三方面实现的第四方面的数字滤波器(3)中,第一滤波器(31a)还对第二滤波器(32a)输出的第二数字数据执行滤波处理。

[0085]

根据该方面,第二滤波器(32a)执行初级滤波处理并且第一滤波器(31a)执行次级滤波处理,因此对减小第一滤波器(31a)的尺寸做出贡献。

[0086]

在根据可以结合第一方面至第四方面中的任一方面实现的第五方面的数字滤波器(3)中,所述第二数字数据是所述第一数字数据的高位。

[0087]

该方面允许输出具有不同的精度的第一数字数据和第二数字数据。

[0088]

根据可以结合第一方面至第五方面中的任一方面实现的第六方面的数字滤波器(3)还包括:用于对a/d转换单元(2)的输出执行滤波处理的第三滤波器(33,33a)。

[0089]

该方面允许独立于第一数字数据和第二数字数据而生成第三数字数据。

[0090]

一种根据第七方面的a/d转换器(1),包括:根据第一至第六方面中任一方面的数字滤波器(3);以及a/d转换单元(2)。

[0091]

该方面使数字滤波器(3)提供具有较高精度和较低延迟的输出数据。

[0092]

在根据可以结合第七方面实现的第八方面的a/d转换器(1)中,a/d转换单元(2)包括:δ∑a/d转换器;以及布置在δ∑a/d转换器之前的逐次逼近寄存器a/d转换器(第a/d转换器22)。

[0093]

该方面使a/d转换器(1)的输出数据具有较低延迟。

[0094]

一种根据第九方面的传感器处理电路(10)包括:根据第七方面或第八方面的a/d转换器(1)。a/d转换器(1)将传感器(101)的输出转换成数字数据并且向控制电路(200)输出数字数据。

[0095]

该方面使a/d转换器(1)中包括的数字滤波器(3)提供具有较高精度和较低延迟的输出数据。

[0096]

一种根据第十方面的传感器系统(100)包括:根据第九方面的传感器处理电路(10);以及传感器(101)。

[0097]

该方面使传感器处理电路(10)的a/d转换器(1)中包括的数字滤波器(3)提供具有较高精度和较低延迟的输出数据。

[0098]

附图标记列表

[0099]1ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

a/d转换器

[0100]2ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

a/d转换单元

[0101]

21

ꢀꢀꢀꢀꢀꢀꢀꢀ

(第一)a/d转换器(δ∑a/d转换器)

[0102]

22

ꢀꢀꢀꢀꢀꢀꢀꢀ

第a/d转换器(逐次逼近寄存器a/d转换器)

[0103]3ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

数字滤波器

[0104]

31,31a

ꢀꢀꢀ

第一滤波器

[0105]

32,32a

ꢀꢀꢀ

第二滤波器

[0106]

33,33a

ꢀꢀꢀ

第三滤波器

[0107]

42

ꢀꢀꢀꢀꢀꢀꢀꢀ

输出单元

[0108]

10

ꢀꢀꢀꢀꢀꢀꢀꢀ

传感器处理电路

[0109]

100

ꢀꢀꢀꢀꢀꢀꢀ

传感器系统

[0110]

101

ꢀꢀꢀꢀꢀꢀꢀ

传感器

[0111]

200

ꢀꢀꢀꢀꢀꢀꢀ

控制电路。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。