1.本发明属于全息存储技术领域,更具体地,涉及一种相位调制型全息存储系统的编码/译码方法、设备及系统。

背景技术:

2.由于具有大存储容量和高数据传输速率的优点,全息存储成为下一代主流存储技术的有力竞争者。全息存储是一种以光进行数据存取的存储技术。按照携带用户信息的特征载体不同,常见的全息存储技术有振幅调制型全息存储和相位调制型全息存储。相比于振幅调制型全息存储,相位调制型全息存储具有较高的抗干扰性能,因此得到了较为广泛的应用。

3.由于环境中各种复杂噪声的存在,相位调制型全息存储的可靠性仍面临严重挑战。为了提升数据存储的可靠性,采用基于迭代译码方法的ldpc(low density parity check code,低密度奇偶校验码)纠错码因为具有较强的纠错能力而被广泛使用在全息存储系统中。

4.然而,传统的ldpc码会因为其纠错能力的上限而难以保证系统的数据可靠性,降低了全息存储系统的数据可靠性。

技术实现要素:

5.针对现有技术的缺陷和改进需求,本发明提供了一种相位调制型全息存储系统的编码/译码方法、设备及系统,旨在解决ldpc等传统的纠错编码的纠错能力有限引起数据可靠性下降的技术问题。

6.为实现上述目的,按照本发明的一个方面,提供了一种相位调制型全息存储系统的编码方法,包括:

7.记录数据时,对待记录的用户数据依次进行1级编码~n级编码后,对用户数据连同各级编码产生的校验数据以及部分嵌入式数据进行相位编码并组织成数据页,之后将数据页记录进相位调制型全息存储系统中的全息存储材料中;n为正整数,且n≥2;

8.1级编码包括:将用户数据作为码字进行纠错编码,产生相应的校验数据;

9.i级编码包括:选取部分用户数据和部分嵌入式数据组成码字,并对该码字进行纠错编码,产生相应的校验数据;i∈{2,3,

……

,n};

10.其中,各级编码所使用的用户数据互不相同。

11.进一步地,n=2。

12.进一步地,各级编码中的纠错码编码均为ldpc编码。

13.进一步地,任意两级编码中的纠错编码相同或者不同。

14.按照本发明的另一个方面,提供了一种相位调制型全息存储系统的译码方法,该相位调制型全息存储中的数据在记录时,采用本发明提供的相位调制型全息存储系统的编码方法进行编码;

15.该译码方法包括:从相位调制型全息存储系统中的全息存储材料中读取出数据页后,按照如下步骤进行译码:

16.(s1)从数据页中提取用户数据、嵌入式数据和各级编码产生校验数据,将提取的用户数据作为待译码数据,并初始化译码级数j=1;

17.(s2)将待译码数据作为码字,利用1级编码产生的校验数据对该码字进行1级译码,若译码成功,则返回译码后的用户数据,译码结束;否则,转入步骤(s3);

18.(s3)若j≥n,则返回译码失败的信息,译码结束;否则,按照j=j 1更新译码级数后,转入步骤(s4);

19.(s4)按照j级编码中码字的组成,相应提取出部分用户数据和部分嵌入式数据组成码字,并利用j级编码产生的校验数据对该码字进行j级译码,利用译码得到的用户数据替换待译码数据中的相应内容以对待译码码字进行更新,之后转入步骤(s2);

20.其中,各级译码的译码方法与对应级编码中的纠错编码相对应。

21.按照本发明的又一个方面,提供了一种相位调制型全息存储系统中的编码设备,包括:编码模块、相位编码模块以及记录模块;

22.编码模块,用于在记录数据时,对待记录的用户数据依次进行1级编码~n级编码;n为正整数,且n≥2;

23.相位编码模块,用于对用户数据连同各级编码产生的校验数据以及部分嵌入式数据进行相位编码并组织成数据页;

24.记录模块,用于将数据页记录进相位调制型全息存储系统中的全息存储材料中;

25.1级编码包括:将用户数据作为码字进行纠错编码,产生相应的校验数据;

26.i级编码包括:选取部分用户数据和部分嵌入式数据组成码字,并对该码字进行纠错编码,产生相应的校验数据;i∈{2,3,

……

,n};

27.其中,各级编码所使用的用户数据互不相同。

28.按照本发明的又一个方面,提供了一种相位调制型全息存储系统中的译码设备,该相位调制型全息存储中的数据在记录时,采用本发明提供的相位调制型全息存储系统的编码方法进行编码;

29.该译码设备包括:初始化模块、第一译码模块第二译码模块和译码控制模块;

30.初始化模块,用于在从相位调制型全息存储系统中的全息存储材料中读取出数据页后,从数据页中提取用户数据、嵌入式数据和各级编码产生校验数据,将提取的用户数据作为待译码数据,并初始化译码级数j=1;

31.第一译码模块,用于将待译码数据作为码字,并利用1级编码产生的校验数据对该码字进行1级译码,并在译码成功时,返回译码后的用户数据,以结束译码;在译码失败时,触发译码控制模块;

32.译码控制模块,用于在j≥n时,返回译码失败的信息,以结束译码;并在j<n,按照j=j 1更新译码级数后,触发第二译码模块;

33.第二译码模块,用于按照j级编码中码字元的组成,相应提取出部分用户数据和部分嵌入式数据组成码字,并利用j级编码产生的校验数据对该码字进行j级译码,利用译码得到的用户数据替换待译码数据中的相应内容以对待译码码字进行更新,之后触发第一译码模块;

34.其中,各级译码的译码方法与对应级编码中的纠错编码相对应。

35.按照本发明的又一个方面,提供了一种相位调制型全息存储系统,包括:本发明提供的相位调制型全息存储系统中的编码设备,和本发明提供的相位调制型全息存储系统中的译码设备。

36.总体而言,通过本发明所构思的以上技术方案,能够取得以下有益效果:

37.(1)本发明在相位调制型全息存储系统记录数据时,会对待记录的用户数据进行多级编码,其中的1级编码为传统的纠错编码,即直接对用户数据进行纠错编码;后续的编码为借助于系统中已知的嵌入式数据对部分用户数据进行的纠错编码,为常规编码基础上的增强编码。通过增强编码,能够提供更多的校验信息,增强对用户数据的保护,提高数据可靠性,并且借助于已知的嵌入式数据能够减少后续译码码字的的原始比特误码率,加快译码迭代。

38.(2)本发明在相位调制型全息存储系统读取数据时,优先尝试对读取出的数据进行常规译码,在译码失败时,会逐级启动下一级译码,获得部分已知的用户数据,以逐步降低译码码字的原始误码率,促进迭代,增加译码成功的可能性;由于下一级译码仅在前一级译码失败的情况下才会启动,可以最大限度的利用纠错编码的纠错能力,避免不必要的计算,在增加译码成功可能性的同时提高译码效率。

附图说明

39.图1为本发明实施例提供的相位调制型全息存储系统的编码方法流程图;

40.图2为本发明实施例提供的相位调制型全息存储系统的译码方法流程图;

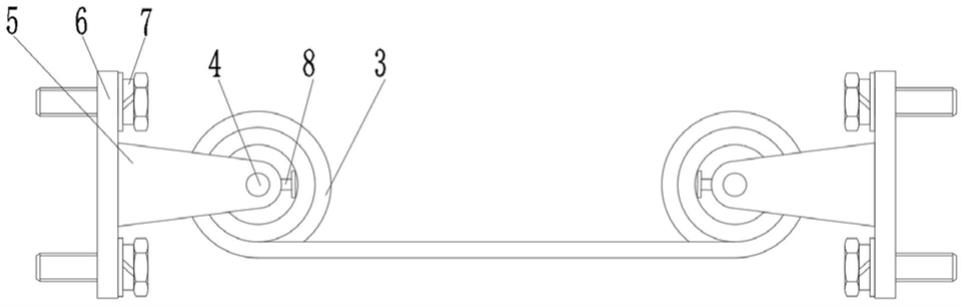

41.图3为本发明实施例提供的相位调制型全息存储系统的编码方法示意图;

42.图4为本发明实施例提供的相位调制型全息存储系统的译码方法示意图。

具体实施方式

43.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。此外,下面所描述的本发明各个实施方式中所涉及到的技术特征只要彼此之间未构成冲突就可以相互组合。

44.在本发明中,本发明及附图中的术语“第一”、“第二”等(如果存在)是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。

45.在详细解释本发明的技术方案之前,先对全息存储系统中的嵌入式数据进行如下简要说明:

46.嵌入式数据是指一些相位信息已知的数据,它的相位类型和用户数据的相位类型一致。嵌入式数据不携带任何的有效信息,仅仅为了协助或者加快数据页中相位信息未知的用户数据的恢复过程。

47.为了解决现有的ldpc等传统的纠错编码的纠错能力有限导致相位调制型全息存储系统的数据可靠性下降的技术问题,本发明提供了一种相位调制型全息存储系统的编码/译码方法、设备及系统,其整体思路在于:在记录数据时,在对待记录的用户数据进行常规编码的基础上,借助相位调制型全息存储系统中已知的嵌入式数据,对部分用户数据进

行增强编码,以提供更多的校验信息,由此增强对用户数据的保护,提高数据可靠性;相应地,在读取数据时,优先尝试对读取出的数据进行常规译码,在译码失败时,会逐级启动下一级译码,获得部分已知的用户数据,以逐步降低译码码字的原始误码率,促进迭代,增加译码成功的可能性。

48.为解决上述技术问题,本发明提供的相位调制型全息存储系统的编码方法,如图1,包括:

49.记录数据时,对待记录的用户数据依次进行1级编码~n级编码后,对用户数据连同各级编码产生的校验数据以及部分嵌入式数据进行相位编码并组织成数据页,之后将数据页记录进相位调制型全息存储系统中的全息存储材料中;n为正整数,且n≥2;

50.1级编码包括:将用户数据作为码字进行纠错编码,产生相应的校验数据;1级编码为常规编码;

51.i级编码包括:选取部分用户数据和部分嵌入式数据组成码字,并对该码字进行纠错编码,产生相应的校验数据;i∈{2,3,

……

,n};i级编码为增强编码,可以在常规编码的基础上,提供更多的校验信息,增强对用户数据的保护;

52.其中,各级编码所使用的用户数据互不相同,也即是说,在i级编码中,所选取的用户数据的数量和/或位置会发生变化,由此能够保证在译码过程中,能够获得用户数据中不同部分的内容。

53.在实际应用中,编码级数n的具体取值,可根据具体的误码率要求相应设定;更多的译码级数将产生的更多的校验信息,由于相位调制型全息存储系统中数据页的大小是固定的,为了在记录数据时将校验信息均记录到全息存储材料中,相应地会减少数据页中嵌入式数据的数据量,n的设定,只要保证采用多级编码后,相比于传统的纠错编码,数据页中的误码率有所下降即可;为在提高系统可靠性的同时简化编码过程,在本发明可选的一些实施例中,n=2。

54.考虑到ldpc编码的纠错能力较强,在本发明可选的一些实施例中,1级编码和i级编码均采用ldpc编码;应当说明的是,ldpc编码仅为本发明可选的一种纠错编码,在本发明其他的一些实施例中,在保证纠错能力满足系统要求的情况下,各级编码也可以采用bch码(bose

–

chaudhuri

–

hocquenghem codes),rs码(reed

‑

solomon codes),ra码(repeat

‑

accumulate codes)等其他的纠错编码,并且各级编码中采用的纠错编码可以相同也可以不同。

55.在上述的相位调制型全息存储系统的编码方法的基础上,本发明还提供了一种相位调制型全息存储系统的译码方法,该相位调制型全息存储中的数据在记录时,采用上述相位调制型全息存储系统的编码方法进行编码;

56.如图2所示,本发明提供的相位调制型全息存储系统的译码方法包括:从相位调制型全息存储系统中的全息存储材料中读取出数据页后,按照如下步骤进行译码:

57.(s1)从数据页中提取用户数据、嵌入式数据和各级编码产生校验数据,将提取的用户数据作为待译码数据,并初始化译码级数j=1;

58.(s2)将待译码数据作为码字,利用1级编码产生的校验数据对该码字进行1级译码,若译码成功,则返回译码后的用户数据,译码结束;否则,转入步骤(s3);

59.(s3)若j≥n,则返回译码失败的信息,译码结束;否则,按照j=j 1更新译码级数

后,转入步骤(s4);

60.(s4)按照j级编码中码字的组成,相应提取出部分用户数据和部分嵌入式数据组成码字,并利用j级编码产生的校验数据对该码字进行j级译码,利用译码得到的用户数据替换待译码数据中的相应内容以对待译码码字进行更新,之后转入步骤(s2);

61.其中,各级译码的译码方法与对应级编码中的纠错编码相对应;例如,若相位调制型全息存储系统的译码方法中,1级编码采用的纠错编码为ldpc编码,则相应地,1级译码中采用的译码方法为ldpc译码。

62.本发明还提供了一种相位调制型全息存储系统中的编码设备,包括:编码模块、相位编码模块以及记录模块;

63.编码模块,用于在记录数据时,对待记录的用户数据依次进行1级编码~n级编码;n为正整数,且n≥2;

64.相位编码模块,用于对用户数据连同各级编码产生的校验数据以及部分嵌入式数据进行相位编码并组织成数据页;

65.记录模块,用于将数据页记录进相位调制型全息存储系统中的全息存储材料中;

66.1级编码包括:将用户数据作为码字进行纠错编码,产生相应的校验数据;

67.i级编码包括:选取部分用户数据和部分嵌入式数据组成码字,并对该码字进行纠错编码,产生相应的校验数据;i∈{2,3,

……

,n};

68.其中,各级编码所使用的用户数据互不相同;

69.各模块的具体实施方式,可参考上述相位调制型全息存储系统的编码方法中的描述,在此将不作复述。

70.本发明还提供了一种相位调制型全息存储系统中的译码设备,该相位调制型全息存储中的数据在记录时,采用上述相位调制型全息存储系统的编码方法进行编码;

71.该译码设备包括:初始化模块、第一译码模块第二译码模块和译码控制模块;

72.初始化模块,用于在从相位调制型全息存储系统中的全息存储材料中读取出数据页后,从数据页中提取用户数据、嵌入式数据和各级编码产生校验数据,将提取的用户数据作为待译码数据,并初始化译码级数j=1;

73.第一译码模块,用于将待译码数据作为码字,并利用1级编码产生的校验数据对该码字进行1级译码,并在译码成功时,返回译码后的用户数据,以结束译码;在译码失败时,触发译码控制模块;

74.译码控制模块,用于在j≥n时,返回译码失败的信息,以结束译码;并在j<n,按照j=j 1更新译码级数后,触发第二译码模块;

75.第二译码模块,用于按照j级编码中码字元的组成,相应提取出部分用户数据和部分嵌入式数据组成码字,并利用j级编码产生的校验数据对该码字进行j级译码,利用译码得到的用户数据替换待译码数据中的相应内容以对待译码码字进行更新,之后触发第一译码模块;

76.其中,各级译码的译码方法与对应级编码中的纠错编码相对应;

77.各模块的具体实施方式,可参考上述相位调制型全息存储系统的译码方法中的描述,在此将不作复述。

78.本发明还提供了一种相位调制型全息存储系统,包括:本发明提供的上述相位调

制型全息存储系统中的编码设备,和本发明提供的上述相位调制型全息存储系统中的译码设备。

79.以下结合1个具体的应用实例,对本发明做进一步的解释说明。

80.相位调制型全息存储系统的一个数据页中包括用户数据d1~d18,对该用户数据进行相位编码时,所使用的嵌入式数据包括e1~e18;在记录该用户数据时,使用本发明提供的上述相位调制型全息存储系统的编码方法对该用户数据进行编码,编码时,设置n=2,1级编码和2级编码均采用ldpc编码作为纠错编码;相应地,译码时,1级译码和2级译码均采用ldpc译码方法。

81.如图3所示,编码过程具体包括如下步骤:

82.(w1)记录数据时,先进行1级编码,具体地,将一个数据页上的全部用户数据,即d1~d18,作为一个码字,进行纠错编码产生校验数据p1~p2,记为校验数据ec1;

83.利用校验数据ec1可以对用户数据进行保护;

84.(w2)进行2级编码,具体地,将数据页的前一半用户数据和前一半嵌入式数据,即d1~d9和e1~e9组成码字,进行纠错编码,产生校验数据p3~p4,记为校验数据ec2;

85.校验数据ec2可以对用户数据进行双重保护,并且通过这种编码方式可以减少译码码字的原始比特误码率,加快译码迭代;

86.(w3)将用户数据d1~d18、嵌入式数据以及校验数据ec1和ec2进行相位编码并组成数据页,相位编码的具体方式以及组成数据页的具体排布规则,为相位调制型全息存储系统中现有的,在此将不再赘述;

87.通过减少一定的嵌入式数据保存了两份校验信息ec1和ec2;校验数据ec1和ec2为用户数据提供了双重保护,其中ec1是提供的一级保护是常规保护,ec2提供的二级保护是增强保护;

88.(w4)将数据页记录进全息存储材料中。

89.如图4所示,译码过程包括如下步骤:

90.(r1)读取数据时,首先进行1级译码,将用户数据d1~d18作为一个码子,利用校验数据ec1进行译码,由此可以最大限度地充分利用纠错码的纠错能力;

91.(r2)若译码成功,则返回正确的用户数据,译码结束;否则,转入步骤(r3)以进行2级译码;

92.在1级译码失败时启动2级译码,可以对数据的可靠性进行双重保护;

93.(r3)将前一半用户数据和前一半嵌入式数据组成码字,利用校验数据ec2对该码字进行译码,若译码成功,得到正确的前一半用户数据,转入步骤(r4);若译码失败,则返回译码失败的信息,译码结束;

94.通过2级译码时,码字中有一半已知的用户数据,已知的用户数据使得译码码字的原始误码率降低,同时促进了译码迭代;

95.(r4)将正确的前一半用户数据和后一半待纠正的用户数据组成码字,利用校验数据ec1组成的码字进行1级译码,若译码成功,输出正确的用户数据;若译码不成功,则返回译码失败的信息,译码结束;

96.步骤(r4)中,前一半正确的已知用户数据使得码字的原始误码率降低,2级译码的性能大大增强。

97.本领域的技术人员容易理解,以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。