[0001]

本发明涉及一种内存测试装置以及内存测试方法,特别是一种用于在主板处于内存满载状态下对内存进行测试的内存测试装置以及内存测试方法。

背景技术:

[0002]

现行的内存的满载测试是将待测内存插在主板的插槽上,其余空余的插槽则会插满正常的内存模块(一般被称为golden module)。如此,满载测试可以测试出待测内存在主板的插槽满载的情况下的实际表现。

[0003]

然而,所使用的测试程序对待测内存以及正常的内存模块的所有地址范围进行测试。由于测试的范围包含了正常的内存模块的地址范围,所以测试时间中的大部分时间是花在测试正常的内存模块上。这样测试效率会大大降低。

技术实现要素:

[0004]

本发明是针对一种内存测试装置以及内存测试方法,能够大幅提高对待测内存进行满载测试的测试效率。

[0005]

根据本发明的实施例,内存测试装置包括测试板、主板以及处理器。测试板经配置以搭载至少一待测内存芯片。主板具有多个内存插槽。至少一内存模块以及测试板分别被插在所述多个内存插槽中,以使所述多个内存插槽呈现满载状况。处理器被设置在主板上。处理器经配置以关闭交错访问模式以进入依序访问模式,确定所述测试板的测试地址范围,并且基于所述测试板的测试地址范围对至少一待测内存芯片进行测试,以获得对应于所述至少一待测内存芯片的第一测试结果。

[0006]

根据本发明的实施例,内存测试方法包括:使测试板搭载至少一待测内存芯片,并将至少一内存模块以及测试板分别插在主板的多个内存插槽中,以使所述多个内存插槽呈现满载状况;关闭交错访问模式以进入依序访问模式;确定所述测试板的测试地址范围;以及基于所述测试板的测试地址范围对至少一待测内存芯片进行测试,以获得对应于所述至少一待测内存芯片的第一测试结果。

[0007]

基于上述,在所述多个内存插槽呈现满载状况下,本发明的内存测试装置以及内存测试方法会关闭交错访问模式以进入依序访问模式,确定出测试板的测试地址范围,并且对至少一待测内存芯片进行测试。本发明的内存测试装置以及内存测试方法能够在依序访问模式中仅仅对搭载于测试板上的待测内存芯片进行测试。如此一来,本发明能够大幅提高对待测内存进行满载测试的测试效率。

附图说明

[0008]

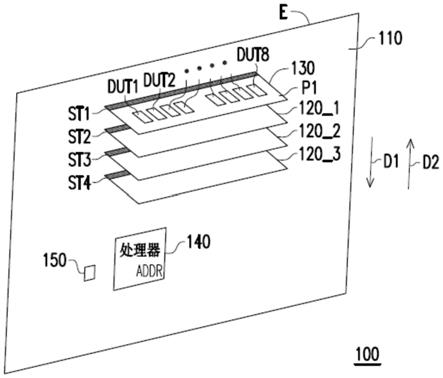

图1是依据本发明一实施例所绘示的内存测试装置的示意图;

[0009]

图2是依据本发明一实施例所绘示的测试板以及内存模块的载板的示意图;

[0010]

图3是依据本发明一实施例所绘示的内存测试方法的方法流程图;

[0011]

图4是依据本发明一实施例所绘示的地址范围的示意图。

[0012]

附图标记说明

[0013]

100:内存测试装置;

[0014]

110:主板;

[0015]

120_1、120_2、120_3:内存模块;

[0016]

121:载板;

[0017]

130:测试板;

[0018]

140:处理器;

[0019]

150:作业单元;

[0020]

d1:第一方向;

[0021]

d2:第二方向;

[0022]

d3:第三方向;

[0023]

dut1~dut8:待测内存芯片;

[0024]

e:边缘;

[0025]

st1~st4:内存插槽;

[0026]

p1:第一面;

[0027]

addr:测试地址范围;

[0028]

addr1~addr4:地址范围;

[0029]

s110、s120、s130、s140:步骤。

具体实施方式

[0030]

现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同符号在图式和描述中用来表示相同或相似部分。

[0031]

请参考图1,图1是依据本发明一实施例所绘示的内存测试装置的示意图。在本实施例中,内存测试装置100包括主板110、测试板130以及处理器140。主板110具有4个内存插槽st1~st4。测试板130搭载8个待测内存芯片dut1~dut8。本发明并不以本实施例的内存插槽st1~st4的数量以及测试板130所能搭载的待测内存芯片dut1~dut8的数量为限。本发明的测试板130所能搭载的待测内存芯片的数量可以是一个或是多个。本发明的内存插槽的数量可以是多个。在本实施例中,内存模块120_1、120_2、120_3以及测试板130分别被插在内存插槽st1~st4中,以使内存插槽st1~st4呈现满载状况。举例来说,测试板130被插在内存插槽st1中。内存模块120_1被插在内存插槽st2中,依此类推。在内存插槽st1~st4呈现满载状况的情况下,内存测试装置100可进行满载测试。

[0032]

在本实施例中,处理器140被设置在主板110上。在进行满载测试时,处理器140关闭内存的交错(interleave)访问模式以进入依序(sequence)访问模式。在本实施例中,处理器140可被控制以选用依序访问模式,因此交错动作被关闭,并使内存测试装置100进入依序访问模式。在一些实施例中,处理器140可被控制以关闭交错访问模式,以使内存测试装置100进入依序访问模式。在本实施例中,处理器140确定测试板130的测试地址范围addr。测试板130的测试地址范围addr等同于搭载在测试板130上的待测内存芯片dut1~dut8的测试地址范围addr。也就是说,处理器140确定待测内存芯片dut1~dut8的测试地址

范围addr,并且基于测试地址范围addr对待测内存芯片dut1~dut8进行测试,以获得对应于待测内存芯片dut1~dut8的测试结果。处理器140例如是中央处理单元(central processing unit,cpu),或是其他可程序化之一般用途或特殊用途的微处理器(microprocessor)、数字信号处理器(digital signal processor,dsp)、可程序化的控制器、特殊应用集成电路(application specific integrated circuits,asic)、可程序化逻辑设备(programmable logic device,pld)或其他类似装置或这些装置的组合,其可加载并执行计算机程序。

[0033]

在此值得一提的是,在内存插槽st1~st4呈现满载状况下,处理器140会使内存测试装置100进入依序访问模式,并且基于测试地址范围addr对待测内存芯片dut1~dut8进行测试。处理器140能够仅仅对搭载于测试板130上的待测内存芯片dut1~dut8进行满载测试。如此一来,相较于现行的内存的满载测试(请参考「背景技术」),本实施例能够大幅缩短满载测试的测试时间,并大幅提高满载测试的测试效率。

[0034]

进一步举例说明的测试板130的实施方式。在本实施例中,测试板130以及内存模块120_1、120_2、120_3沿第一方向d1被排列设置。进一步来说,测试板130以及内存模块120_1、120_2、120_3是依据第一方向d1依序平行排列。因此,相较于内存模块120_1、120_2、120_3,测试板130较接近于主板110的边缘e。此外,如图1所示,主板110被直立设置。因此,测试板130会位于内存模块120_1、120_2、120_3的上方。

[0035]

在本实施例中,测试板130具有第一面p1以及第二面。第二面相对于第一面p1。第一面p1的面方向大致上等于第二方向d2。第二方向d2与第一方向d1相反。第二面则会面向内存模块120_1、120_2、120_3。在本实施例中,待测内存芯片dut1~dut8被装载在第一面p1上。因此,基于上述的设置,内存测试装置100可以沿第一方向d1将待测内存芯片dut1~dut8装载在第一面p1上,并且沿第二方向d2卸载待测内存芯片dut1~dut8。举例来说,内存测试装置100还包括芯片移动机构。芯片移动机构会将待测内存芯片dut1~dut8依序地或同时地装载到第一面p1上。此外,芯片移动机构还会沿第二方向d2卸载待测内存芯片dut1~dut8。

[0036]

在本实施例中,测试板130的布线配置不同于内存模块120_1、120_2、120_3的布线配置。请同时参考图1以及图2,图2是依据本发明一实施例所绘示的测试板以及内存模块的载板的示意图。在本实施例中,内存模块120_1、120_2、120_3的载板121可以是常规的载板。因此,在内存模块120_1、120_2、120_3被插在内存插槽st2~st4中时,设置内存模块120_1、120_2、120_3上的内存芯片会面向处理器140,并背对于主板110的边缘e。测试板130在第三方向d3上的布线配置相反于载板121在第三方向d3上的布线配置。第三方向d3等于测试板130的长边延伸方向。举例来说,测试板130在第三方向d3上的金属连线的布线配置会相反于载板121在第三方向d3上的金属连线的布线配置。测试板130在第三方向d3上的引脚的布线配置会相反于载板121在第三方向d3上的引脚的布线配置。此外,测试板130在第三方向d3上的引脚缺口的布线配置会相反于载板121在第三方向d3上的引脚缺口的布线配置。因此,在测试板130被插在内存插槽st1中时,第一面p1会面向主板110的边缘e。如此一来,内存测试装置100能够沿第一方向d1将待测内存芯片dut1~dut8装载在第一面p1上,并且沿第二方向d2卸载待测内存芯片dut1~dut8。

[0037]

请同时参考图1以及图3,图3是依据本发明一实施例所绘示的内存测试方法的方

法流程图。本实施例的内存测试方法可适用于内存测试装置100。在本实施例中,在步骤s110中,使测试板130搭载待测内存芯片dut1~dut8,并将内存模块120_1、120_2、120_3以及测试板130分别插在主板110的内存插槽st1~st4中,以使内存插槽st1~st4呈现满载状况。步骤s110的实施细节可以在先前的实施例中获得足够的教示或说明,因此恕不在此重述。

[0038]

在步骤s120中,交错访问模式被关闭以进入依序访问模式。内存的访问(access)的模式例如是包括交错访问模式以及依序访问模式。在交错访问模式中,内存的多个内存区块会以交错方式被访问。交错访问模式是内存正常使用的访问模式。在依序访问模式中,内存的多个内存区块则会基于多个内存区块的地址顺序依序被访问。

[0039]

在本实施例中,内存测试装置100还包括作业单元150。作业单元150可以是实现基本输入输出系统(bios)的功能的组件。作业单元150纪录了交错访问模式以及依序访问模式的访问方式以及测试流程。处理器140在步骤s120中会控制作业单元150关闭交错访问模式以进入依序访问模式。在依序访问模式下。处理器140能够基于内存模块120_1、120_2、120_3以及待测内存芯片dut1~dut8的地址顺序依序对内存模块120_1、120_2、120_3以及待测内存芯片dut1~dut8进行测试。

[0040]

在本实施例中,处理器140在步骤s130中确定出测试板130的测试地址范围addr(也就是,待测内存芯片dut1~dut8的测试地址范围)。由于测试板130被指定插在内存插槽st1中。因此,处理器140可例如是由内存插槽st1确定出测试板130的测试地址范围addr。步骤s140中,处理器140基于测试地址范围addr对待测内存芯片dut1~dut8进行测试,以获得待测内存芯片dut1~dut8的测试结果。步骤s140中,在内存插槽st1~st4处于满载状况下,处理器140能够基于测试地址范围addr以及待测内存芯片dut1~dut8的地址顺序依序对待测内存芯片dut1~dut8的地址进行测试,以获得待测内存芯片dut1~dut8的测试结果。处理器140并不会对内存模块120_1、120_2、120_3的地址进行测试。也就是说,在满载测试中,内存测试装置100可仅仅对待测内存芯片dut1~dut8进行测试。相较于一并对待测内存以及正常的内存模块进行测试的现行满载测试方式,本实施例的测试时间可以大幅被缩短。如此一来,内存测试装置100可能够大幅提高对待测内存芯片dut1~dut8进行满载测试的测试效率。

[0041]

举例来说明步骤s130、s140的实施细节,请同时参考图1、图3以及图4。图4是依据本发明一实施例所绘示的地址范围的示意图。在本实施例中,图4示出了地址范围addr1~addr4。在本实施例中,地址范围addr1被表示为内存模块120_1的地址范围。地址范围addr2被表示为待测内存芯片dut1~dut8的测试地址范围(即,图1所示的测试地址范围addr)。地址范围addr3被表示为内存模块120_2的地址范围。地址范围addr4被表示为内存模块120_3的地址范围。

[0042]

在步骤s130中,处理器140例如可以通过内存插槽st1确定出待测内存芯片dut1~dut8的测试地址范围addr2。同理可推,处理器140也可以通过内存插槽st2~st4确定出内存模块120_1~120_3的地址范围addr1、addr3、addr4。在确定出待测内存芯片dut1~dut8的地址范围addr2之后,处理器140会在步骤s140中基于地址范围addr2以及待测内存芯片dut1~dut8的地址顺序依序对待测内存芯片dut1~dut8的地址进行测试,以获得待测内存芯片dut1~dut8的测试结果。

[0043]

在一些实施例中,内存模块120_1~120_3中的至少其中一者可以是待测内存模块。在内存插槽st1~st4处于满载状况下,处理器140还可以在待测内存模块进行测试。举例来说,内存模块120_1是待测内存模块。处理器140能够在满载状况下确定出内存模块120_1的地址范围addr1,并基于内存模块120_1的地址范围addr1对内存模块120_1进行测试,以获得对应于内存模块120_1的测试结果。此外,在满载状况下,处理器140也能够基于内存模块120_1的地址范围addr1以及待测内存芯片dut1~dut8的地址范围addr2对内存模块120_1以及待测内存芯片dut1~dut8进行测试,以获得内存模块120_1的测试结果以及待测内存芯片dut1~dut8的测试结果。

[0044]

综上所述,在满载状况下,本发明的内存测试装置以及内存测试方法会被控制以进入依序访问模式,确定出至少一待测内存芯片的测试地址范围,并且对至少一待测内存芯片进行测试。本发明的内存测试装置以及内存测试方法能够在依序访问模式中仅仅对搭载于测试板上的待测内存芯片进行测试。如此一来,本发明能够大幅提高对待测内存进行满载测试的测试效率。除此之外,本发明使测试板较接近于主板的边缘,并且使主板被直立设置。测试板的布线配置相反于常规载板的布线配置。因此,本发明能够沿第一方向将待测内存芯片装载测试板上,并且自测试板上卸除待测内存芯片。

[0045]

最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。