[0001]

本发明的一个方式涉及一种半导体装置。特别是本发明的一个方式涉及一种能够模仿人脑中的信息记忆的半导体装置。

[0002]

注意,在本说明书等中,半导体装置是指能够通过利用半导体特性而工作的所有装置。

背景技术:

[0003]

用于人工智能(ai:artificial intelligence)开发的诺依曼型计算机的计算机在计算速度方面胜过人类。

[0004]

相对于此,人脑可以通过将片段的输入信息与记忆进行对比并补充而做出正确的判断。或者,具有通过根据大范围的领域的记忆进行联想或发挥创造性或预见性能够解决计算机难以解决的问题的能力。

[0005]

近年来,随着计算机性能的提高,可以使用神经网络进行学习及推论等的大规模计算。另外,在机械学习的领域中,报告了通过使用深度学习(深层学习)的方法,计算机的识别精度得到了显著的提高(例如参照专利文献1)。即使在象棋、围棋等需要创造性或预见性的领域,计算机难以解决的问题也正在得到解决。

[0006]

[先行技术文献]

[0007]

[专利文献]

[0008]

[专利文献1]美国专利申请公开第2016/0110642号说明书

技术实现要素:

[0009]

发明所要解决的技术问题

[0010]

现有的人工智能装置的功能在电力效率方面远不及人脑。在cpu或gpu等硬件中,使用由si晶体管构成的sram或dram等存储元件来储存数据并进行运算处理。由si晶体管构成的存储元件随着精细化而导致泄漏电流增大,并且由于计算机的高性能化导致电路规模增大,功耗也变得更大。

[0011]

此外,现有的人工智能装置的存储元件所包括的储存信息的功能是单一的。例如,其中大多数为sram、dram等存储元件写入/读出0或1等信息。相对于此,人脑的信息记忆具有多样性,例如长期记忆或短期记忆等的信息保存方法,以及大脑新皮质中的记忆或海马体中的记忆等的信息保存位置的移动。

[0012]

本发明的一个方式的目的之一是提供一种具有新颖结构的半导体装置。另外,本发明的一个方式的目的之一是提供一种能够以低功耗工作的半导体装置。此外,本发明的一个方式的目的之一是提供一种能够模仿人脑中的信息记忆的半导体装置。

[0013]

注意,这些目的的记载不妨碍其他目的的存在。另外,本发明的一个方式并不需要实现所有上述目的。此外,上述以外的目的从说明书、附图、权利要求书等的记载中自然得知,可以从说明书、附图、权利要求书等的记载提炼上述以外的目的。

[0014]

解决技术问题的手段

[0015]

本发明的一个方式是一种包括控制部、存储部以及传感器部的半导体装置。存储部包括存储电路和切换电路,存储电路包括第一晶体管及电容器,切换电路包括第二晶体管及第三晶体管,第一晶体管及第二晶体管包括在沟道形成区域中包含氧化物半导体的半导体层,控制部具有根据在传感器部得到的信号而切换供应到第一晶体管及第二晶体管的信号的功能。

[0016]

本发明的一个方式是一种包括控制部、存储部以及传感器部的半导体装置。存储部包括存储电路和切换电路,存储电路包括第一晶体管及电容器,切换电路包括第二晶体管及第三晶体管,第一晶体管及第二晶体管包括在沟道形成区域中包含氧化物半导体的半导体层和背栅电极,控制部具有根据在传感器部得到的信号而切换供应到背栅电极的信号的功能。

[0017]

本发明的一个方式是一种包括控制部、存储部以及传感器部的半导体装置。存储部包括存储电路和切换电路,存储电路包括第一晶体管及电容器,第一晶体管的源极和漏极中的一个与电容器的一个电极电连接,切换电路包括第二晶体管及第三晶体管,第二晶体管的源极和漏极中的一个与第三晶体管的栅极电连接,第一晶体管及第二晶体管包括在沟道形成区域中包含氧化物半导体的半导体层和背栅电极,控制部具有根据在传感器部得到的信号而切换供应到背栅电极的信号的功能。

[0018]

本发明的一个方式是一种包括控制部、存储部以及传感器部的半导体装置。存储部包括存储电路和切换电路,存储电路包括第一晶体管及电容器,切换电路包括第二晶体管及第三晶体管,第一晶体管及第二晶体管包括在沟道形成区域中包含氧化物半导体的半导体层和栅电极,控制部具有根据在传感器部得到信号而切换供应到栅电极的信号的功能。

[0019]

本发明的一个方式是一种包括控制部、存储部以及传感器部的半导体装置。存储部包括存储电路和切换电路,存储电路包括第一晶体管及电容器,第一晶体管的源极和漏极中的一个与电容器的一个电极电连接,切换电路包括第二晶体管及第三晶体管,第二晶体管的源极和漏极中的一个与第三晶体管的栅极电连接,第一晶体管及第二晶体管包括在沟道形成区域中包含氧化物半导体的半导体层和栅电极,控制部具有根据在传感器部得到信号而切换供应到栅电极的信号的功能。

[0020]

在本发明的一个方式中优选为一种半导体装置,该半导体装置的存储电路包括第四晶体管,第二晶体管的源极和漏极中的一个与第四晶体管的栅极电连接。

[0021]

发明效果

[0022]

本发明的一个方式可以提供一种具有新颖结构的半导体装置。另外,本发明的一个方式可以提供一种能够以低功耗工作的半导体装置。此外,本发明的一个方式的目的之一是提供一种能够模仿人脑中的信息记忆的半导体装置。

[0023]

注意,这些效果的记载不妨碍其他效果的存在。另外,本发明的一个方式并不需要具有所有上述效果。此外,说明书、附图以及权利要求书等的记载中显然存在上述效果以外的效果,可以从说明书、附图以及权利要求书等的记载中获得上述效果以外的效果。

附图说明

[0024]

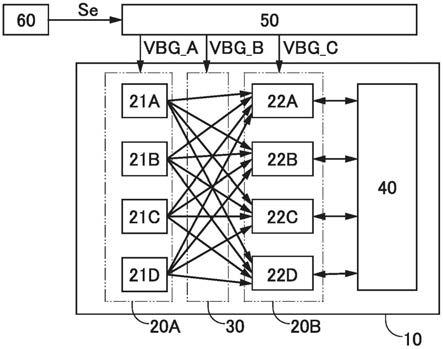

[图1]是示出半导体装置的结构例子的方框图。

[0025]

[图2]是用来说明半导体装置的示意图。

[0026]

[图3](a)至(c)是示出半导体装置的结构例子的电路图、图表及流程图。

[0027]

[图4](a)至(c)是示出半导体装置的结构例子的电路图、图表及流程图。

[0028]

[图5](a)至(c)是示出半导体装置的结构例子的电路图、图表及流程图。

[0029]

[图6](a)至(d)是示出半导体装置的结构例子的示意图。

[0030]

[图7](a)、(b)是示出半导体装置的结构例子的方框图。

[0031]

[图8]是示出半导体装置的结构例子的方框图。

[0032]

[图9](a)至(d)是示出半导体装置的结构例子的电路图、波形图、图表及流程图。

[0033]

[图10](a)至(d)是示出半导体装置的结构例子的电路图、波形图、图表及流程图。

[0034]

[图11](a)至(c)是示出半导体装置的结构例子的电路图、波形图及流程图。

[0035]

[图12]是示出半导体装置的结构例子的波形图。

[0036]

[图13](a)至(d)是示出半导体装置的结构例子的示意图。

[0037]

[图14](a)、(b)是示出半导体装置的结构例子的方框图。

[0038]

[图15](a)至(d)是示出半导体装置的应用例子的图。

[0039]

[图16]是示出半导体装置的结构例子的截面图。

[0040]

[图17]是示出半导体装置的结构例子的截面图。

[0041]

[图18](a)至(c)是示出晶体管的结构例子的截面图。

具体实施方式

[0042]

以下,参照附图对实施方式进行说明。注意,实施方式可以以多个不同模式来实现,并且所属技术领域的普通技术人员可以很容易地理解一个事实就是其方式及详细内容在不脱离本发明的宗旨及其范围的情况下可以被变换为各种各样的形式。因此,本发明不应该被解释为仅限定在以下所示的实施方式所记载的内容中。

[0043]

另外,在附图中,为便于清楚地说明,有时夸大表示大小、层的厚度或区域。因此,本发明并不局限于附图中的尺寸。注意,在附图中,示意性地示出理想的例子,而不局限于附图所示的形状或数值等。

[0044]

另外,本说明书中的以下实施方式可以适当地组合。另外,当在一个实施方式中示出多个结构例子时,可以适当地组合结构例子。

[0045]

以下对本发明的一个方式的半导体装置进行说明。在本实施方式中,特别对能够实现接近人脑的存储能力的半导体装置进行说明。

[0046]

<半导体制造的结构例子1>

[0047]

图1是用来说明半导体装置的结构的方框图的一个例子。图1所示的半导体装置包括传感器部60、控制部50以及存储部10。作为一个例子,存储部10包括存储电路20a、存储电路20b、切换电路30以及输入输出电路40。

[0048]

注意,虽然在图1中示出传感器部60、控制部50以及存储部10各为一个,但是也可以各为多个。另外,存储电路20a、存储电路20b、切换电路30以及输入输出电路40也不局限于图1所示,可以各为多个。

[0049]

存储电路20a包括多个存储电路(图1示出存储电路21a至存储电路21d)。存储电路21a至存储电路21d各自包括多个存储元件。虽未图示,存储电路21a至存储电路21d包括用来驱动多个存储元件的驱动电路。驱动电路具有可以根据控制部50的控制而切换施加到晶体管的背栅电极的背栅级电压的功能。存储电路21a至存储电路21d具有可以根据从传感器部60得到的信号se而改变信息存储能力的功能。注意,有时将信息换称为数据。另外,信息作为与数据对应的电压值或电荷量储存在存储电路中。

[0050]

例如,存储电路21a至存储电路21d包括存储元件,该存储元件可以根据施加到晶体管的背栅级电压而改变信息存储能力。例如,可以由控制部50控制存储电路21a及存储电路21b,使其分别成为能够长期储存信息的存储元件和能够短期储存信息的存储元件。

[0051]

存储电路20b与存储电路20a相同,包括多个存储电路(图1示出存储电路22a至存储电路22d)。存储电路22a至存储电路22d分别包括多个存储元件。虽未图示,存储电路22a至存储电路22d包括用来驱动多个存储元件的驱动电路。驱动电路具有可以根据控制部50的控制而切换施加到晶体管的背栅电极的背栅级电压的功能。存储电路22a至存储电路22d具有可以根据从传感器部60得到的信号se而改变信息存储能力的功能。

[0052]

例如,存储电路21a至存储电路21d包括存储元件,该存储元件可以根据施加到晶体管的背栅级电压而改变信息存储能力。例如,可以由控制部50控制存储电路21a及存储电路21b,使其分别成为能够长期储存信息的存储元件和能够短期储存信息的存储元件。

[0053]

作为适用于存储电路20a及存储电路20b的存储电路,dosram或nosram是优选的。dosram(注册商标)是“dynamic oxide semiconductor random access memory(ram)(动态氧化物半导体随机存取存储器)”的简称,并是指包括1t(晶体管)1c(电容器)型存储单元的ram。此外,nosram(注册商标)是“nonvolatile oxide semiconductor ram(氧化物半导体非易失性随机存取存储器)”的简称,指包括增益单元型(2t型、3t型)存储单元的ram。dosram、nosram是利用了os晶体管(在沟道形成区域包含氧化物半导体的晶体管)的关态电流(off-state current)低的特征的存储器。

[0054]

dosram是使用os晶体管形成的dram,且是暂时储存从外部发送的信息的存储器。dosram包括具有os晶体管的存储单元和具有si晶体管(在沟道形成区域包含硅的晶体管)的读出电路部。由于上述存储单元和读出电路部可以设置在被层叠的不同层上,所以可以缩小dosram的整体电路面积。此外,dosram可以细分存储单元阵列并有效地配置。

[0055]

nosram是使用os晶体管的非易失性存储器。与快闪存储器、reram(resistive random access memory:电阻随机存取存储器)、mram(magnetoresistive random access memory:磁阻随机存取存储器)等其他的非易失性存储器相比,nosram写入数据时的功耗小。另外,nosram不会像快闪存储器或reram那样在写入数据时发生元件劣化,在数据写入次数上没有限制。此外,nosram不仅可以储存1位的2值数据还可以储存2位以上的多值数据。nosram通过储存多值数据可以缩小每1位的存储单元面积。

[0056]

另外,nosram除了可以储存数字数据之外还可以储存模拟数据。由此,存储电路20a及存储电路20b也可以用作模拟存储器。由于nosram可以以模拟数据的方式进行储存,所以不需要d/a转换电路或a/d转换电路。因此,可以缩小nosram的外围电路的面积。

[0057]

注意,在本发明的一个方式中,对将nosram或dosram应用于存储电路20a及存储电路20b所包括的各电路的结构进行说明,但是本发明的一个方式不局限于此。例如,随着今

后的技术革新,在使用reram、mram等非易失性存储器时的功耗充分变小的情况等下,根据情况也可以将其应用于存储电路20a及存储电路20b所包括的各电路。

[0058]

切换电路30具有可以根据控制部50的控制而控制存储电路20a与存储电路20b间的电连接的功能。例如,具有控制流过存储电路21a至存储电路21d与存储电路22a至存储电路22d间的电流量的功能。也就是说,具有可以切换多个存储电路间的信息传输的功能。切换电路30具有可以根据从传感器部60得到的信号se及施加到晶体管的背栅极电压而改变流过存储电路21a至存储电路21d与存储电路22a至存储电路22d间的电流量的功能。有时将切换电路30称为能够重配置的电路(可重配置电路)。

[0059]

切换电路30包括控制流过存储电路间的电流量的存储元件及根据储存于存储元件的信息使电流流过的半导体元件。在切换电路30中,控制部50具有可以通过控制施加到晶体管的背栅级电压而改变储存于存储元件的信息的功能。注意,在图1中,虽然示出存储电路20a与存储电路20b间的箭头指向一个方向,但是也可以根据信息的流动以双向箭头表示。

[0060]

切换电路30为存储元件包括os晶体管的可编程装置(programmable device)。注意,在本说明书及附图中将包含os晶体管的可编程装置称为os-fpga。此外,将储存于os-fpga的存储元件的信息称为配置数据。

[0061]

os-fpga的存储器面积可以比存储元件由sram构成的fpga更小。因此,即便对其附加上下文切换功能,面积增加也较少。另外,os-fpga通过升压(boosting)可以高速地传送数据和参数。

[0062]

作为一个例子,传感器部60是用来取得脑波、脉搏、血压及体温等生物信息的脑波传感器、脈波传感器、血压传感器及温度传感器等各种传感器。在图1中,虽然示出从一个传感器输出信号se的样子,但是也可以将从多个传感器得到的信号输入到控制部50。

[0063]

控制部50包括cpu(central processing unit:中央处理器)及gpu(graphics processing unit:图形处理器)等的运算电路及sram(static random access memory:静态随机存取存储器)等的存储电路。控制部50具有根据从传感器部60输出的信号se而输出电压vbg_a至电压vbg_c的功能。例如,控制部50可以利用根据人工神经网络的运算处理等而进行与输入相应的输出。

[0064]

电压vbg_a至电压vbg_c是能够切换施加到存储电路20a、存储电路20b及切换电路30所包括的晶体管的背栅电极的电压或者施加到该背栅极的电压的信号。图1示出将电压vbg_a输出到存储电路20a的样子。在图1中,电压vbg_a不局限于一个值的电压,可以将存储电路20a所包括的存储电路21a至存储电路21d控制为施加到不同的背栅电极的电压。同样地,也可以将存储电路20b及切换电路30控制为在不同的存储电路中施加到不同的背栅电极的电压。

[0065]

注意,控制部50可以根据从传感器部60输出的信号se而切换对电压vbg_a至电压vbg_c的控制。例如,可以根据是重复输入相同的信号se还是输入具有高或低强度的信号se来切换对电压vbg_a至电压vbg_c的控制。

[0066]

输入输出电路40是用来控制向存储电路20a、存储电路20b及切换电路30输入输出信息的电路。也可以将输入输出电路40设置于存储部10的外部。

[0067]

图2是示意性地示出使用包括os晶体管的存储电路及切换电路来模仿人脑

(brain)的功能的图。

[0068]

如图2所示,在本发明的一个方式中,为了模仿人脑(brain)的功能,使用包含氧化物半导体的晶体管(也称为os晶体管)的技术(osfettechnology(os晶体管技术))。作为os晶体管技术,例如可以举出晶体管(也称为fet)以及与该晶体管电连接的电容器(也称为condenser、cs)等。此外,通过使用一个或者多个由上述fet及cs等构成的存储器(memory),可以形成运算装置、寄存器或外围电路等,从而能够用作处理器。

[0069]

此外,在本说明书等中,可以将上述处理器用作脑型处理器(也称为脑子形性处理器(brain-morphicprocessor)、bm处理器(bmprocessor)或脑处理器(brainprocessor))。注意,关于图2示出的dosram、nosram及os-fpga,将在后面进行说明。注意,os-fpga中的os存储器(也称为osmem.)为包括os晶体管的存储器并储存os-fpga的配置数据(configurationdata)。

[0070]

注意,在图2所示的nosram中,以虚线示出电容器。作为该电容器,例如可以使用在布线和与该布线形成于不同层的布线之间有可能形成的寄生电容。在此,由于图2所示的nosram的电容器不是意图性地形成的电容器,所以以虚线示出。

[0071]

在本发明的一个方式的结构中,通过采用包括os晶体管的存储电路及切换电路的结构,可以利用关闭时源极与漏极间流过的泄漏电流(以下,关态电流)极低的特征,从而储存信息(数据)。通过在包括存储电容及寄生电容的节点中保持与数据相应的电荷,可以实现信息的存储。

[0072]

在使用os晶体管的存储电路中,通过电荷的充电或放电,可以进行信息的改写,因此在实际上能够进行无限次的数据的写入及读出。在使用os晶体管的存储电路中,没有如磁存储器或阻变式存储器等的原子级的结构变化,因此具有优良的改写耐性。此外,与快闪存储器不同,即使在反复改写工作中,在使用os晶体管的存储电路中也观察不到电子俘获中心的增加所导致的不稳定性。

[0073]

另外,使用os晶体管的存储电路可以在使用si晶体管的电路上等进行自由地配置,因此容易进行集成化。另外,可以使用与si晶体管相同的制造装置制造os晶体管,因此能够以低成本制造。

[0074]

另外,os晶体管在除了栅电极、源电极及漏电极之外还加有背栅电极的情况下,可以成为4端子的半导体元件。根据供应给栅电极或背栅电极的电压,可以由独立地控制源极与漏极之间的信号的输入输出的电路网络构成。因此,可以与lsi相同地进行电路设计。再者,os晶体管具有在高温环境下比si晶体管优越的电特性。具体而言,即使在125℃以上且150℃以下的高温下,通态电流与关态电流的比率也大,因此可以进行良好的开关工作。

[0075]

通过采用本实施方式中公开的的半导体装置结构,可以使用包括os晶体管的半导体装置实现人脑中长期记忆的形成及其过程和短期记忆的形成及其过程。因此,与以往相比,可以以更接近人脑的功能来储存数据。另外,可以用极小的功率来实现数据的保持。也就是说,可以和人脑一样,用极低的功耗来驱动脑型处理器。

[0076]

<nosram、dosram的结构例子1>

[0077]

存储电路21a至存储电路21d或存储电路22a至存储电路22d是包括os晶体管的电路结构。参照图3a至图3c及图4a至图4c对电路结构及工作的一个例子进行说明。

[0078]

图3a示出包括dosram的电路结构的存储元件的电路图。图3a示出晶体管mt1、电容

器c1、字线wl、位线bl及背栅级电位线bgl。

[0079]

晶体管mt1是os晶体管,也是包括背栅电极的4端子元件。背栅电极通过与背栅级电极线bgl连接,被供应电位vbg。晶体管mt1的关态电流图示为ioff。在图3a中,将保持电荷的节点示为节点fn,该节点也是与晶体管mt1和电容器c1连接的布线的节点。

[0080]

位线bl具有向存储元件传输写入信息(数据、数据电位)的功能。另外,字线wl具有传输控制晶体管mt1开关的信号的功能。背栅级电位线bgl具有向晶体管mt1的背栅电极传输电位vbg的功能。有时将位线bl、字线wl及背栅级电位线bgl都简称为布线。

[0081]

例如,电位vbg被控制部50控制为与存储电路21a至存储电路21d所包括的每个存储元件的电位不同。例如,如果将信息储存在存储电路21a中时的背栅级电位设为v1,将信息储存在存储电路21b中时的背栅级电位设为v0(<v1),将信息储存在存储电路21c中时的背栅级电位设为v2(>v1),晶体管mt1的关态电流ioff则如图3b所示。也就是说,与背栅级电位的大小关系相对应,关态电流也是ioff_2为最大,其次为ioff_1、ioff_0。关态电流越大,节点fn所保持的电荷越容易发生变化,关态电流越小,节点fn所保持的电荷越难以发生变化。其结果是,可以使每个存储电路的信息的保持期间都产生差。

[0082]

通过采用该结构,存储电路21a至存储电路21d或存储电路22a至存储电路22d可以实现根据从传感器部60得到的信号se而储存存储能力不同的信息的功能。

[0083]

图3c示出用来说明上述dosram的工作的流程图。

[0084]

在步骤s01中,将作为背栅级电位供应的电位vbg设为v1,并将信息储存到存储电路中。

[0085]

在步骤s02中,判断从传感器部60输出的信号se是否发生变动。优选设定多个阈值并根据该阈值与传感器输出之间的大小关系来控制作为背栅级电位供应的电位vbg,以便判断是否存在传感器信号。

[0086]

如果在步骤s02中发生变动,则进入步骤s03,将作为背栅级电位供应的电位vbg设为小于v1的v0,并且将信息储存到存储电路中。也就是说,切换电位vbg,使得存储电路中的信息的保持时间变长。

[0087]

如果在步骤s03中没有变动或变动小,则进入步骤s04,将作为背栅级电位供应的电位vbg设为大于v1的v2,并且将信息储存到存储电路中。也就是说,切换电位vbg,使得存储电路中的信息的保持时间变短。

[0088]

通过采用该结构,可以实现根据传感器部的输出而储存存储能力不同的信息的功能。例如,如果传感器部是温度传感器,则可以实现在高温或低温下长期储存信息而在室温下一段期间后忘记信息的功能。

[0089]

图4a示出包括nosram的电路结构的存储元件的电路图。图4a示出晶体管mt2、晶体管mt3、字线wl、位线bl以及背栅级电位线bgl。

[0090]

晶体管mt2是os晶体管,也是包括背栅电极的4端子元件。背栅电极通过与背栅级电极线bgl连接,被供应电位vbg。晶体管mt2的关态电流图示为ioff。在图4a中,将保持电荷的节点示为节点fn,该节点也是与晶体管mt2及晶体管mt3的栅极连接的布线的节点。

[0091]

注意,虽然在图4a中将晶体管mt3示为p沟道型晶体管,但是晶体管mt3也可以是n沟道型晶体管。另外,虽然在图4a中示出包括两个晶体管的2t型,但是也可以采用添加了电容器的2t1c型或与其他晶体管组合的3t型。注意,通过将晶体管mt3的栅极电容等的寄生电

容增大,可以省略与节点fn连接的电容器。此外,如图2所示,也可以将上述寄生电容积极地用作电容器。

[0092]

例如,电位vbg被控制部50控制为与存储电路21a至存储电路21d所包括的每个存储元件的电位不同。例如,如果将信息储存在存储电路21a中时的作为背栅级电位供应的电位vbg设为v1,将信息储存在存储电路21b中时的作为背栅级电位供应的电位vbg设为v0(<v1),将信息储存在存储电路21c中时的作为背栅级电位供应的电位vbg设为v2(>v1),晶体管mt2的关态电流ioff则如图4b的图表所示。也就是说,与电位vbg的大小关系相对应,关态电流也是ioff_2为最大,其次是ioff_1、ioff_0。关态电流越大,节点fn所保持的电荷就越容易发生变化,关态电流越小,节点fn所保持的电荷就越不容易发生变化。其结果是,可以使每个存储电路的信息的保持期间都产生差。

[0093]

通过采用该结构,存储电路21a至存储电路21d或存储电路22a至存储电路22d可以实现根据从传感器部60得到的信号se而储存存储能力不同的信息的功能。

[0094]

图4c示出用来说明上述nosram的工作的流程图。

[0095]

在步骤s11中,将作为背栅级电位供应的电位vbg设为v1,并将信息储存到存储电路中。

[0096]

在步骤s12中,判断从传感器部60输出的信号se是否发生变动。优选设定多个阈值并根据该阈值与传感器输出之间的大小关系来控制作为背栅级电位供应的电位vbg,以便判断是否存在传感器信号。

[0097]

如果在步骤s12中发生变动,则进入步骤s13,将作为背栅级电位供应的电位vbg设为小于v1的v0,并且将信息储存到存储电路中。也就是说,切换电位vbg,使得存储电路中的信息保持时间变长。

[0098]

如果在步骤s13中没有变动或变动小,则进入步骤s14,将作为背栅级电位供应的电位vbg设为大于v1的v2,并且将信息储存到存储电路中。也就是说,切换电位vbg,使得存储电路中的信息保持时间变短。

[0099]

通过采用该结构,可以实现根据传感器部的输出而储存存储能力不同的信息的功能。例如,如果传感器部是温度传感器,则可以实现在高温或低温下长期存储信息而在室温下一段期间后忘记信息的功能。

[0100]

<切换电路的结构例子1>

[0101]

切换电路30是包括os晶体管的电路结构。参照图5a至图5c及图6a至图6d对电路结构及工作的一个例子进行说明。

[0102]

图5a示出包括设置在一对存储电路间的切换电路30的电路结构的存储元件的电路图。图5a示出晶体管mt4、晶体管mt5、字线wl、位线bl、背栅级电位线bgl、输入端子in及输出端子out。

[0103]

晶体管mt4是os晶体管,也是包括背栅电极的4端子元件。背栅电极通过与背栅级电极线bgl连接,被供应电位vbg。晶体管mt4的关态电流图示为ioff。在图5a中,将保持电荷的节点示为节点fn,该节点也是与晶体管mt4及晶体管mt5连接的布线的节点。

[0104]

晶体管mt5是si晶体管或os晶体管。根据节点fn的电位流过晶体管mt5的电流图示为idata,该电流流过输入端子in与输出端子out间。

[0105]

注意,虽然在图5a中将晶体管mt5示为p沟道型晶体管,但是晶体管mt5也可以是n

沟道型晶体管。另外,虽然在图5a中示出包括两个晶体管的2t型,但是也可以采用添加了电容器的2t1c型或与其他晶体管组合的3t型。注意,通过将晶体管mt5的栅极电容等的寄生电容增大,可以省略与节点fn连接的电容器。

[0106]

例如,电位vbg被控制部50控制为与设置于存储电路21a至存储电路21d的其中之一和存储电路22a至存储电路22d的其中之一之间的布线间的每个切换电路的电位不同。例如,如果将设置于存储电路21a与存储电路22a之间的切换电路所包括的晶体管mt4的背栅级电位设为v1,将设置于存储电路21b与存储电路22b之间的切换电路所包括的晶体管m4的背栅级电位设为v0(<v1),将设置于存储电路21c与存储电路22c之间的切换电路所包括的晶体管m4的背栅级电位设为v2(>v1),晶体管mt4的关态电流ioff则在关态电流的大小上产生差。此时,如果在节点fn保持h电平的电位,节点fn的电位(v

fn

)根据关态电流的大小产生差。因此,根据节点fn的电位流过的电流idata产生差。也就是说,如图5b所示,随着时间经过(t)而变化的电流idata根据背栅级电位的大小关系产生差。其结果是,可以使流过每个存储电路的电流量产生差。

[0107]

通过采用该结构,设置于存储电路21a至存储电路21d的其中之一和存储电路22a至存储电路22d的其中之一之间的布线间的切换电路可以实现根据从传感器部60得到的信号se而使流过每个存储电路的电流量产生差的功能。

[0108]

图5c示出用来说明上述切换电路的工作的流程图。

[0109]

在步骤s21中,将作为节点fn供应的电位vbg设为h电平,即不流过电流idata的数据。

[0110]

在步骤s22中,将作为背栅级电位供应的电位vbg设为v0,并将晶体管mt4的关态电流ioff设为极低的状态。

[0111]

在步骤s23中,判断从传感器部60输出的信号se是否发生变动。优选设定多个阈值并根据该阈值与传感器输出之间的大小关系来控制电位vbg,以便判断是否存在传感器信号。

[0112]

如果在步骤s23中发生变动,则进入步骤s24,将作为背栅级电位供应的电位vbg设为大于v0的v1。也就是说,控制晶体管mt4的关态电流ioff使其增大并切换电位vbg,使得流过存储电路间的电流idata增大。当在步骤s23中没有变动或变动小时,继续进行步骤s22。

[0113]

在步骤s25中,判断从传感器部60输出的信号se是否发生变动。优选设定多个阈值并根据该阈值与传感器输出之间的大小关系来控制作为背栅级电位供应的电位vbg,以便判断是否存在传感器信号。

[0114]

如果在步骤s25中发生变动,则进入步骤s26,将作为背栅级电位供应的电位vbg设为大于v1的v2。也就是说,控制晶体管mt4的关态电流ioff使其增大并切换电位vbg,使得流过存储电路间的电流idata增大。当在步骤s25中没有变动或变动小时,继续进行步骤s24。

[0115]

通过采用该结构,可以实现根据传感器部的输出而使流过存储电路间的电流量不同的功能。例如,如果传感器部是温度传感器,则可以实现使信息传输在高温或低温下变活跃而在室温下的信息传输变得不活跃的功能。

[0116]

另外,图6a至图6d是模仿人脑并用来说明本发明的一个方式的半导体装置中的信息存储的图。

[0117]

图6a示出以下状态:作为初始状态在存储电路21a保持信息(以实线表示),切换电

路30的信息传输不活跃(流过存储电路间的电流量少的状态;以虚线箭头表示),并且在存储电路22a至存储电路22c没有保持信息(以虚线表示)。

[0118]

在本发明的一个方式的半导体装置中,可以根据传感器部的信号se而将切换电路30的信息传输切换为活跃的状态(流过存储电路间的电流量大的状态;以实线箭头表示)。因此,如图6b所示,可以将保持在存储电路21a的信息保持在存储电路22a至存储电路22c中(以实线表示)。

[0119]

另外,在本发明的一个方式的半导体装置中,可以根据传感器部的信号se而使存储电路22a至存储电路22c中的信息消失(使保持期间变短)。因此,如图6c所示,可以将从切换电路31向存储电路28b及存储电路28c的信息传输切换为不活跃的状态,并将保持在存储电路28b及存储电路28c的信息切换为短期存储(以细虚线表示)。

[0120]

此外,在本发明的一个方式的半导体装置中,除了可以根据传感器部的信号se而使存储电路22a至存储电路22c中的信息消失(使保持期间变短),也可以使其强化(使保持期间变长)。因此,如图6d所示,可以将从切换电路30向存储电路22b及存储电路22c的信息传输切换为更活跃的状态(流过存储电路间的电流量更大的状态;以粗线箭头表示),可以将向存储电路22b及存储电路22c的信息传输切换为不活跃的状态,可以将保持在存储电路22a的信息切换为长期存储(以粗实线表示),或者也可以将保持在存储电路22b及存储电路22c的信息切换为短期存储。

[0121]

<传感器部及外围电路的组合1>

[0122]

如图7a所示,可以将上述说明的结构用于与外围电路70间进行收发信息。另外,如图7a所示,可以将上述说明的结构用于从传感器部60输入信息的结构。外围电路70也可以被用于向显示装置或执行器等输出信息。

[0123]

通过采用图7a的结构,可以处理在外部的传感器等得到的信号(信息)。例如,可以利用脑波传感器、脈波传感器、血压传感器、温度传感器等各种传感器取得脑波、脉搏、血压、体温等生物信息并储存该信息。可以期待能够通过得到的信息而瞬时统一地把握不规则变化的生物信息的变化。

[0124]

图7b是用来将图7a所示的半导体装置可实现的功能和人脑周边的功能进行比较的示意图。

[0125]

在传感器部60,传感器元件(例如光电变换元件)相当于人的眼睛。从光电变换元件输出的信息被输入到包括os晶体管的存储部。存储部包括由os晶体管所形成的存储电路及由os晶体管所形成的切换电路。

[0126]

存储部10为存储元件,相当于大脑新皮质或海马体等的控制记忆的部位。切换电路相当于视神经或轴索等传输信息的部位。输入输出电路40可以被用于根据存储部10中储存的信息来与外围电路进行信息的输入输出。

[0127]

<半导体装置的结构例子2>

[0128]

图8是用来说明半导体装置的结构的方框图的一个例子。图8所示的半导体装置包括传感器部60、控制部50a及存储部10a。作为一个例子,存储部10a包括存储电路26a、存储电路26b、切换电路31及输入输出电路40。

[0129]

注意,虽然在图8中示出传感器部60、控制部50a以及存储部10a各为一个,但是也可以各为多个。另外,存储电路26a、存储电路26b、切换电路31以及输入输出电路40也不局

限于图8所示,可以各为多个。

[0130]

存储电路26a包括多个存储电路(图8示出存储电路27a至存储电路27d)。存储电路27a至存储电路27d各自包括多个存储元件。虽未图示,存储电路27a至存储电路27d包括用来驱动多个存储元件的驱动电路。驱动电路具有可以根据控制部50a的控制而切换字信号的信号波形的功能。存储电路27a至存储电路27d具有可以根据从传感器部60得到的信号se而改变信息存储能力的功能。注意,有时将信息换称为数据。另外,信息作为与数据对应的电压值或电荷量储存在存储电路中。

[0131]

例如,存储电路27a至存储电路27d包括存储元件,该存储元件可以根据字信号的信号波形而改变信息存储能力。例如,可以由控制部50a控制存储电路27a及存储电路27b,使其分别成为能够长期储存信息的存储元件和能够短期储存信息的存储元件。

[0132]

存储电路26b与存储电路26a相同,包括多个存储电路(图8示出存储电路28a至存储电路28d)。存储电路28a至存储电路28d分别包括多个存储元件。虽未图示,存储电路28a至存储电路28d包括用来驱动多个存储元件的驱动电路。驱动电路具有可以根据控制部50a的控制而切换字信号的信号波形的功能。存储电路28a至存储电路28d具有可以根据从传感器部60得到的信号se而改变信息存储能力的功能。

[0133]

例如,存储电路28a至存储电路28d包括存储元件,该存储元件具有根据字信号的信号波形而改变信息存储能力的功能。例如,可以由控制部50a控制存储电路28a及存储电路28b,使其分别成为能够长期储存信息的存储元件和能够短期储存信息的存储元件。

[0134]

作为适用于存储电路26a及存储电路26b的存储电路,dosram或nosram是优选的。

[0135]

注意,在本发明的一个方式中,对将nosram或dosram应用于存储电路26a及存储电路26b所包括的各电路的结构进行说明,但是本发明的一个方式不局限于此。例如,随着今后的技术革新,在使用reram、mram等非易失性存储器时的功耗充分变小的情况等下,根据情况也可以将其应用于存储电路26a及存储电路26b所包括的各电路。

[0136]

切换电路31具有可以根据控制部50a的控制而控制存储电路26a及26b间的电连接的功能。例如,具有控制流过存储电路27a至存储电路27d与存储电路28a至存储电路28d间的电流量的功能。也就是说,具有可以切换多个存储电路间的信息传输的功能。切换电路31具有可以根据从传感器部60得到的信号se及字信号的信号波形而改变流过存储电路27a至存储电路27d与存储电路28a至存储电路28d间的电流量的功能。有时将切换电路31称为能够重配置的电路(重配置电路)。

[0137]

切换电路31包括控制流过存储电路间的电流量的存储元件及根据储存于存储元件的信息而使电流流过的半导体元件。在切换电路31中,控制部50a具有可以通过控制字信号的信号波形而改变储存在存储元件的信息的功能。注意,在图8中,虽然示出存储电路26a和存储电路26b之间的箭头指向一个方向,但是也可以根据信息的流动表示为双向箭头。

[0138]

切换电路31是包括os晶体管的可编程装置。注意,在本说明书及附图中,将包含os晶体管的可编程装置称为os-fpga。此外,将os-fpga的存储元件所储存的信息称为配置数据。

[0139]

os-fpga的存储器面积可以比存储元件由sram构成的fpga更小。因此,即便对其附加上下文切换功能,面积增加也较少。另外,os-fpga通过升压可以高速地传送数据和参数。

[0140]

作为一个例子,传感器部60是用来取得脑波、脉搏、血压、体温等生物信息的脑波

传感器、脈波传感器、血压传感器、温度传感器等各种传感器。在图8中,虽然示出从一个传感器输出信号se的状态,但是也可以将从多个传感器得到的信号输入到控制部50a。

[0141]

控制部50a包括cpu(central processing unit:中央处理器)及gpu(graphics processing unit:图形处理器)等的运算电路及sram(static random access memory:静态随机存取存储器)等的存储电路。控制部50a具有根据从传感器部60输出的信号se而输出信号wl_a至信号wl_c的功能。例如,控制部50a可以利用根据人工神经网络的运算处理等而进行与输入相应的输出。

[0142]

信号wl_a至信号wl_c是供应到存储电路26a、存储电路26b及切换电路31所包括的晶体管的栅电极的信号(字信号)或能够切换该字信号的信号。注意,虽然图8示出将信号wl_a输出到存储电路26a的样子,但是信号wl_a使用不同的字信号对存储电路26a所包括的存储电路27a至存储电路27d或存储元件进行控制。存储电路26b及切换电路31也可以同样使用不同的字信号对不同的存储电路进行控制。

[0143]

注意,控制部50a可以根据从传感器部60输出的信号se而切换对信号wl_a至信号wl_c的控制。例如,可以根据是重复输入相同的信号se还是输入具有高或低强度的信号se来切换对信号wl_a至信号wl_c的控制。

[0144]

输入输出电路40是用来控制向存储电路26a、存储电路26b及切换电路31输入或输出信息的电路。输入输出电路40也可以设置于存储部10a的外部。

[0145]

通过采用本实施方式中公开的的半导体装置结构,可以使用包括os晶体管的半导体装置实现人脑中长期记忆的形成及其过程和短期记忆的形成及其过程。因此,与以往相比,可以以更接近人脑的功能来储存数据。另外,可以用极小的功率来实现数据的保持。也就是说,可以和人脑一样,用极低的功耗来驱动脑型处理器。

[0146]

<nosram、dosram的结构例子2>

[0147]

存储电路27a至存储电路27d或存储电路28a至存储电路28d是包括os晶体管的电路结构。参照图9a至图9d及图10a及图10d对电路结构及工作的一个例子进行说明。

[0148]

图9a示出包括dosram的电路结构的存储元件的电路图。图9a示出晶体管mt6、电容器c1、字线wl及位线bl。

[0149]

晶体管mt6是os晶体管,也是包括背栅电极的3端子元件。晶体管mt6也可以是包括背栅电极的4端子元件。晶体管mt6的关态电流图示为ioff。在图9a中,将保持电荷的节点示为节点fn,该节点也是与晶体管mt6及电容器c1连接的布线的节点。

[0150]

位线bl具有向存储元件传输写入信息(数据、数据电位)的功能。另外,字线wl具有根据控制部50a的控制,传输用来控制晶体管mt6的开启/关闭的比例(相当于开启时间的长度)的信号(字信号)的功能。有时将位线bl及字线wl都简称为布线。

[0151]

例如,供应到字线wl的字信号被控制部50a控制为与存储电路27a至存储电路27d所包括的每个存储元件不同的电位。例如,可以将在存储电路27a储存信息时的字信号设为wl_0,将在存储电路26b储存信息时的字信号设为wl_1,并将在存储电路27c储存信息时的字信号设为wl_2。如图9b所示,可以将信号wl_0至信号wl_2示为开启时间t0至开启时间t2不同的信号。

[0152]

根据图9b示出的开启时间t0至开启时间t2,节点fn所保持的电位发生变化。例如,如果将位于开启时间t0的节点fn的电位设为电位vfn_0,将位于开启时间t1的节点fn的电

位设为电位vfn_1,将位于开启时间t2的节点fn的电位设为电位vfn_2,那么将呈现图9c所示图表的大小关系。节点fn的电位随着时间推移发生变化,在达到任意电位(v0)之前的时间产生差(参照图9c的时刻t0至时刻t2)。也就是说,开启时间越短在节点fn保持的电位越容易在短期内发生变化,开启时间越长在节点fn保持的电位越难以发生变化。其结果是,可以使每个存储电路的信息的保持期间都产生差。

[0153]

通过采用该结构,存储电路27a至存储电路27d或存储电路28a至存储电路28d可以实现根据从传感器部60得到的信号se而储存存储能力不同的信息的功能。

[0154]

图9d示出用来说明上述dosram的工作的流程图。

[0155]

在步骤s31中,将供应到字线wl的字信号设为wl_1,并将信息储存到存储电路中。

[0156]

在步骤s32中,将供应到字线wl的字信号设为wl_1,定期地刷新信息(datarefresh)。注意,当关态电流充分低时,可以省略刷新信息。

[0157]

在步骤s33中,判断从传感器部60输出的信号se是否发生变动。优选设定多个阈值并根据该阈值与传感器输出之间的大小关系来控制字信号的开启时间,以便判断是否存在传感器信号。

[0158]

在步骤s33中如果发生变动,则进入步骤s34,将开启时间较长的信号设为wl_2,并将信息储存到存储电路中。也就是说,切换字信号,使得存储电路中的信息保持时间变长。

[0159]

如果在步骤s33中没有变动或变动小,则进入步骤s35,将供应到字线wl的字信号设为开启时间短的wl_0,并且将信息储存到存储电路中。也就是说,切换字信号,使得存储电路中的信息保持时间变短。

[0160]

通过采用该结构,可以实现根据传感器部的输出而储存存储能力不同的信息的功能。例如,如果传感器部是温度传感器,则可以实现在高温或低温下长期储存信息而在室温下一段期间后忘记信息的功能。

[0161]

图10a示出包括nosram的电路结构的存储元件的电路图。图10a示出晶体管mt7、晶体管mt8、字线wl及位线bl。

[0162]

晶体管mt7是os晶体管,也是包括背栅电极的3端子元件。晶体管mt7也可以是包括背栅电极的4端子元件。晶体管mt7的关态电流图示为ioff。在图10a中,将保持电荷的节点示为节点fn,该节点也是与晶体管mt7及晶体管mt8的栅极连接的布线的节点。

[0163]

注意,虽然在图10a中将晶体管mt8示为p沟道型晶体管,但是晶体管mt8也可以是n沟道型晶体管。另外,虽然图10a示出包括两个晶体管的2t型,但是也可以采用添加了电容器的2t1c型或与其他晶体管组合的3t型。注意,通过将晶体管mt3的栅极电容等的寄生电容增大,可以省略与节点fn连接的电容器。

[0164]

例如,供应到字线wl的字信号被控制部50a控制为与存储电路27a至存储电路27d所包括的每个存储元件的电位不同。例如,可以将在存储电路27a储存信息时的字信号设为wl_0,将在存储电路27b储存信息时的字信号设为wl_1,并将在存储电路27c储存信息时的字信号设为wl_2。如图10b所示,可以将信号wl_0至信号wl_2示为开启时间t0至开启时间t2不同的信号。

[0165]

根据图10b示出的开启时间t0至开启时间t2,节点fn所保持的电位发生变化。例如,如果将位于开启时间t0的节点fn的电位设为电位vfn_0,将位于开启时间t1的节点fn的电位设为电位vfn_1,将位于开启时间t2的节点fn的电位设为电位vfn_2,那么将呈现图10c

所示图表的大小关系。节点fn的电位随着时间推移发生变化,在达到任意电位(v0)之前的时间产生差(参照图10c的时刻t0至时刻t2)。也就是说,开启时间越短在节点fn保持的电位越容易在短期内发生变化,开启时间越长在节点fn保持的电位越难以发生变化。其结果是,可以使每个存储电路的信息的保持期间都产生差。

[0166]

通过采用该结构,存储电路27a至存储电路27d或存储电路28a至存储电路28d可以实现根据从传感器部60得到的信号se而储存存储能力不同的信息的功能。

[0167]

图10d示出用来说明上述nosram的工作的流程图。

[0168]

在步骤s41中,将供应到字线wl的字信号设为wl_1,并将信息储存到存储电路中。

[0169]

在步骤s42中,将供应到字线wl的字信号设为wl_1,定期地刷新信息(datarefresh)。注意,当关态电流充分低时,可以省略刷新信息。

[0170]

在步骤s43中,判断从传感器部60输出的信号se是否发生变动。优选设定多个阈值并根据该阈值与传感器输出之间的大小关系来控制字信号的开启时间,以便判断是否存在传感器信号。

[0171]

在步骤s43中如果发生变动,则进入步骤s44,将供应到字线wl的信号设为开启时间较长的wl_2,并将信息储存到存储电路中。也就是说,切换字信号,使得存储电路中的信息保持时间变长。

[0172]

如果在步骤s43中没有变动或变动小,则进入步骤s45,将供应到字线wl的字信号设为开启时间短的wl_0,并且将信息储存到存储电路中。也就是说,切换字信号,使得存储电路的信息的保持时间变短。

[0173]

通过采用该结构,可以实现根据传感器部的输出而储存存储能力不同的信息的功能。例如,如果传感器部是温度传感器,则可以实现在高温或低温下长期储存信息而在室温下一段期间后忘记信息的功能。

[0174]

<切换电路的结构例子2>

[0175]

切换电路31是包括os晶体管的电路结构。参照图11a至图11c、图12及图13a至图13d对电路结构及工作的一个例子进行说明。

[0176]

图11a示出包括设置在一对存储电路间的切换电路31的电路结构的存储元件的电路图。图11a示出晶体管mt9、晶体管mt10、字线wl、位线bl、输入端子in及输出端子out。

[0177]

晶体管mt9是os晶体管,也是包括背栅电极的3端子元件。晶体管mt9也可以是包括背栅电极的4端子元件。晶体管mt9的关态电流图示为ioff。在图11a中,将保持电荷的节点示为节点fn,该节点也是与晶体管mt9及晶体管mt10的栅极连接的布线的节点。

[0178]

晶体管mt10是si晶体管或os晶体管。根据节点fn的电位流过晶体管mt10的电流图示为idata,该电流流过输入端子in与输出端子out间。

[0179]

注意,在图11a中,晶体管mt10可以为p沟道型晶体管或n沟道型晶体管。另外,虽然图11a示出包括两个晶体管的2t型,但是也可以采用添加了电容器的2t1c型或与其他晶体管组合的3t型。注意,通过将晶体管mt10的栅极电容等的寄生电容增大,可以省略与节点fn连接的电容器。

[0180]

例如,供应到字线wl的字信号被控制部50a控制为与设置于存储电路27a至存储电路27d的其中之一和存储电路28a至存储电路28d的其中之一之间的布线间的每个切换电路的电位不同。例如,如果将设置于存储电路27a与存储电路28a之间的切换电路所包括的晶

体管mt9的字信号设为wl_0,将设置于存储电路27b与存储电路28b之间的切换电路所包括的晶体管mt9的字信号设为wl_1,并将设置于存储电路27c与存储电路28c之间的切换电路所包括的晶体管mt9的字信号设为wl_2。如图11b所示,可以将信号wl_0至信号wl_2示为开启时间t0至开启时间t2不同的信号。

[0181]

根据图11b示出的开启时间t0至开启时间t2,节点fn所保持的电位发生变化。开启时间越长,节点fn所保持的电位越容易在短期内发生变化,开启时间越短,节点fn所保持的电位越难以发生变化。此时,如果在节点fn保持l电平的电位,节点fn的电位(v

fn

)根据开启时间的长短产生差。因此,根据节点fn的电位流过的电流idata产生差。其结果是,可以使流过每个存储电路的电流量产生差。

[0182]

通过采用该结构,设置于存储电路27a至存储电路27d的其中之一和存储电路28a至存储电路28d的其中之一之间的布线间的切换电路可以实现根据从传感器部60得到的信号se而使流过每个存储电路的电流量产生差的功能。

[0183]

图11c示出用来说明上述切换电路的工作的流程图。

[0184]

在步骤s51中,将节点fn设为l电平,即电流idata不流过的数据。注意,将位线bl设为h电平。

[0185]

在步骤52中,将供应到字线wl的字信号设为wl_0,并减少节点fn所保持的电位的变动。

[0186]

在步骤s53中,判断从传感器部60输出的信号se是否发生变动。优选设定多个阈值并根据该阈值与传感器输出之间的大小关系来控制字信号的开启时间,以便判断是否存在传感器信号。

[0187]

如果在步骤s53中发生变动,则进入步骤s54,将供应到字线wl的字信号设为wl_1。也就是说,使保持在节点fn的电位的变动增大,并控制开启时间,使得流过存储电路间的电流idata变大。在步骤s53中如果没有变动或变动小,则继续进行步骤s52。

[0188]

在步骤s55中,判断从传感器部60输出的信号se是否发生变动。优选设定多个阈值并根据该阈值与传感器输出之间的大小关系来控制字信号的开启时间,以便判断是否存在传感器信号。

[0189]

如果在步骤s55中发生变动,则进入步骤s56,将字信号设为wl_2。也就是说,使保持在节点fn的电位的变动继续增大,并控制开启时间,使得流过存储电路间的电流idata继续变大。在步骤s55中如果没有变动或变动小,则继续进行步骤s54。

[0190]

注意,在图11a至图11c中,示出控制字信号的开启时间的一个例子,但是也可以采用其他结构。例如,如图12所示,也可以改变字信号的刷新率(refreshrate)。对图12所示的例子进行说明,当减小电流idata时,减少作为字信号供应的信号的频率。即,如图12所示,信号wl_0在每个期间t11为h电平。另外,当增大电流idata时,增加作为字信号供应的信号的频率。即,如图12所示,信号wl_1在每个期间t12为h电平。此外,当电流idata进一步增大时,进一步增加作为字信号供应的信号的频率。即,如图12所示,信号wl_2在每个期间t13为h电平。

[0191]

通过采用该结构,可以实现根据传感器部的输出而使流过存储电路间的电流量不同的功能。例如,如果传感器部是温度传感器,则可以实现使信息传输在高温或低温下变活跃而在室温下的信息传输变得不活跃的功能。

[0192]

另外,图13a至图13d是模仿人脑并用来说明本发明的一个方式的半导体装置中的信息存储的图。

[0193]

图13a示出以下状态:作为初始状态在存储电路27a保持信息(以实线表示),切换电路31的信息传输不活跃(流过存储电路间的电流量少的状态;以虚线箭头表示),并且在存储电路28a至存储电路28c没有保持信息的状态(以虚线表示)。

[0194]

在本发明的一个方式的半导体装置中,可以根据传感器部的信号se而将切换电路31的信息传输切换为活跃的状态(流过存储电路间的电流量大的状态;以实线箭头表示)。因此,如图13b所示,可以将保持在存储电路27a的信息保持在存储电路28a至存储电路28c中(以实线表示)。

[0195]

此外,在本发明的一个方式的半导体装置中,可以根据传感器部的信号se而使存储电路28a至存储电路28c中的信息消失(使保持期间变短)。因此,如图13c所示,可以将从切换电路31向存储电路28b及存储电路28c的信息传输切换为不活跃的状态,并将保持在存储电路28b及存储电路28c的信息切换为短期存储(以细虚线表示)。

[0196]

此外,在本发明的一个方式的半导体装置中,除了可以根据传感器部的信号se而使存储电路28a至存储电路28c中的信息消失(使保持期间变短),也可以使其强化(使保持期间变长)。因此,如图13d所示,可以将从切换电路31向存储电路28b及存储电路28c的信息传输切换为更活跃的状态(流过存储电路间的电流量更大的状态;以粗线箭头表示),可以将向存储电路28b及存储电路28c的信息传输切换为不活跃的状态,可以将保持在存储电路28a的信息切换为长期存储(以粗实线表示),或者也可以将保持在存储电路28b及存储电路28c的信息切换为短期存储。

[0197]

<传感器部及外围电路的组合2>

[0198]

如图14a所示,可以将上述说明的结构用于与外围电路70间进行收发信息。另外,如图14a所示,可以将上述说明的结构用于从传感器部60输入信息的结构。外围电路70可以被用于向显示装置或执行器等输出信息。

[0199]

通过采用图14a的结构,可以处理在外部的传感器等得到的信号(信息)。例如,可以利用脑波传感器、脈波传感器、血压传感器、温度传感器等各种传感器取得脑波、脉搏、血压、体温等生物信息并储存该信息。可以期待能够通过得到的信息而瞬时统一地把握不规则变化的生物信息的变化。

[0200]

图14b是用来将图14a所示的半导体装置可实现的功能和人脑周边的功能进行比较的示意图。

[0201]

在传感器部60,传感器元件(例如光电变换元件)相当于人的眼睛。从光电变换元件输出的信息被输入到包括os晶体管的存储部。存储部包括由os晶体管所形成的存储电路及由os晶体管所形成的切换电路。

[0202]

存储部10为存储元件,相当于大脑新皮质或海马体等的控制存储的部位。切换电路相当于视神经或轴索等传输信息的部位。输入输出电路40可以被用于根据存储部10中储存的信息来与外围电路进行信息的输入输出。

[0203]

<半导体装置的应用实例>

[0204]

参照图15a至图15d对上述实施方式中说明的半导体装置的电子装置的应用实例进行说明。本发明的一个实施方式可以适用于便携式电子设备,例如智能手机等的信息终

端或笔记本型个人计算机。

[0205]

图15a所示的便携式信息终端2910包括外壳2911、显示部2912、麦克风2917、扬声器部2914、照相机2913、外部连接部2916及操作开关2915等。显示部2912包括使用柔性衬底的显示面板及触摸屏。另外,信息终端2910在外壳2911的内侧具有天线、电池等。信息终端2910例如可以被用作智能手机、移动电话、平板信息终端、平板电脑或电子书阅读器终端等。

[0206]

注意,本发明的一个方式可以适用于便携式信息终端,也可以适用于汽车或机器人等的自主型移动体。

[0207]

图15b所示的扫地机器人2920包括外壳2921、显示部2922、操作按钮2923、多个设置于侧面的照相机2924及刷子2925等。虽然未图示,但是扫地机器人2920的底面设置有轮胎和吸入口等。另外,扫地机器人2920还包括红外线传感器、超音波传感器、加速度传感器、压电传感器、光传感器、陀螺仪传感器等各种传感器。此外,扫地机器人2920包括无线通信单元。

[0208]

另外,扫地机器人2920对照相机2924所拍摄的图像进行分析,可以判断墙壁、家具或台阶等障碍物的有无。另外,在通过图像分析检测布线等可能会绕在刷子2925上的物体的情况下,可以停止刷子5103的旋转。

[0209]

可以在显示器5101上显示电池的剩余电量和所吸引的垃圾的量等。也可以在显示部2922显示扫地机器人2920走过的路线。

[0210]

图15c所示的机器人2100包括运算装置2110、照度传感器2101、麦克风2102、上部照相机2103、扬声器2104、显示器2105、下部照相机2106、障碍物传感器2107及移动机构2108。

[0211]

上述半导体装置可以用于机器人2100中的运算装置2110、照度传感器2101、上部照相机2103、显示器2105、下部照相机2106及障碍物传感器2107等。

[0212]

麦克风2102具有检测使用者的声音及周围的声音等的功能。另外,扬声器2104具有发出声音的功能。机器人2100可以使用麦克风2102及扬声器2104与使用者交流。

[0213]

显示器2105具有显示各种信息的功能。机器人2100可以将使用者所希望的信息显示在显示器2105上。显示器2105可以安装有触摸面板。

[0214]

上部照相机2103及下部照相机2106具有对机器人2100的周围环境进行摄像的功能。另外,障碍物传感器2107可以检测机器人2100使用移动机构2108移动时的前方的障碍物的有无。机器人2100可以使用上部照相机2103、下部照相机2106及障碍物传感器2107认知周囲环境而安全地移动。

[0215]

图15d所示的飞行物2120包括运算装置2121、螺旋桨2123及照相机2122,具有自主飞行功能。

[0216]

在飞行物2120中可以将上述半导体装置用于运算装置2121及照相机2122。

[0217]

图15d是示出汽车的一个例子的外观图。汽车2980包括照相机2981等。另外,汽车2980包括红外线雷达、毫米波雷达、激光雷达等各种传感器等。汽车2980对照相机2981所拍摄的图像进行分析,判断护栏1201或行人的有无等周囲的交通状况,由此可以进行自动驾驶。

[0218]

<os晶体管的结构例子>

[0219]

图16所示的半导体装置包括晶体管300、晶体管500及电容器600。图18a是晶体管500的沟道长度方向上的截面图,图18b是晶体管500的沟道宽度方向上的截面图,图18c是晶体管300的沟道宽度方向上的截面图。

[0220]

晶体管500是在沟道形成区域中包含金属氧化物的晶体管(os晶体管)。由于晶体管500的关态电流小,所以通过将晶体管500用于半导体装置所包括的os晶体管,可以长期保持写入的数据。换言之,刷新工作的频率低或者不需要刷新工作,所以可以降低半导体装置的功耗。

[0221]

在本实施方式中说明的半导体装置包括图16示出的晶体管300、晶体管500及电容器600。晶体管500设置在晶体管300的上方,电容器600设置在晶体管300及晶体管500的上方。

[0222]

晶体管300设置在衬底311上,并包括:导电体316、绝缘体315、由衬底311的一部分构成的半导体区域313;以及被用作源区域和漏区域的低电阻区域314a及低电阻区域314b。另外,晶体管300例如可以应用于上述实施方式的晶体管。

[0223]

如图18c所示,在晶体管300中,导电体316隔着绝缘体315覆盖半导体区域313的顶面及沟道宽度方向的侧面。如此,通过使晶体管300具有fin型结构,实效上的沟道宽度增加,所以可以改善晶体管300的通态特性。此外,由于可以增加栅电极的电场的影响,所以可以改善晶体管300的关闭特性。

[0224]

另外,晶体管300可以为p沟道型晶体管或n沟道型晶体管。

[0225]

半导体区域313的沟道形成区域、其附近的区域、被用作源区域或漏区域的低电阻区域314a及低电阻区域314b等优选包含硅类半导体等半导体,更优选包含单晶硅。此外,也可以使用包含ge(锗)、sige(硅锗)、gaas(砷化镓)、gaalas(镓铝砷)等的材料形成。可以使用对晶格施加应力,改变晶面间距而控制有效质量的硅。此外,晶体管300也可以是使用gaas和gaalas等的hemt(high electron mobility transistor:高电子迁移率晶体管)。

[0226]

在低电阻区域314a及低电阻区域314b中,除了应用于半导体区域313的半导体材料之外,还包含砷、磷等赋予n型导电性的元素或硼等赋予p型导电性的元素。

[0227]

作为被用作栅电极的导电体316,可以使用包含砷、磷等赋予n型导电性的元素或硼等赋予p型导电性的元素的硅等半导体材料、金属材料、合金材料或金属氧化物材料等导电材料。

[0228]

此外,由于导电体的材料决定功函数,所以通过选择该导电体的材料,可以调整晶体管的阈值电压。具体而言,作为导电体优选使用氮化钛或氮化钽等材料。为了兼具导电性和埋入性,作为导电体优选使用钨或铝等金属材料的叠层,尤其在耐热性方面上优选使用钨。

[0229]

注意,图16所示的晶体管300的结构只是一个例子,不局限于上述结构,根据电路结构或驱动方法使用适当的晶体管即可。例如,当在半导体装置中使用只有os晶体管的单极性电路时,如图17所示,作为晶体管300的结构采用与使用氧化物半导体的晶体管500相同的结构即可。注意,在后面说明晶体管500的结构。

[0230]

以覆盖晶体管300的方式依次层叠有绝缘体320、绝缘体322、绝缘体324及绝缘体326。

[0231]

作为绝缘体320、绝缘体322、绝缘体324及绝缘体326,例如可以使用氧化硅、氧氮

化硅、氮氧化硅、氮化硅、氧化铝、氧氮化铝、氮氧化铝及氮化铝等。

[0232]

注意,在本说明书中,“氧氮化硅”是指在其组成中氧含量多于氮含量的材料,而“氮氧化硅”是指在其组成中氮含量多于氧含量的材料。注意,在本说明书中,“氧氮化铝”是指氧含量多于氮含量的材料,“氮氧化铝”是指氮含量多于氧含量的材料。

[0233]

绝缘体322也可以被用作对因设置在其下方的晶体管300等而产生的台阶进行平坦化的平坦化膜。例如,为了提高绝缘体322的顶面的平坦性,其顶面也可以通过利用化学机械抛光(cmp)法等的平坦化处理被平坦化。

[0234]

作为绝缘体324,优选使用能够防止氢或杂质从衬底311或晶体管300等扩散到设置有晶体管500的区域中的具有阻挡性的膜。

[0235]

作为对氢具有阻挡性的膜的一个例子,例如可以使用通过cvd法形成的氮化硅。在此,有时氢扩散到晶体管500等具有氧化物半导体的半导体元件中,导致该半导体元件的特性下降。因此,优选在晶体管500与晶体管300之间设置抑制氢的扩散的膜。具体而言,抑制氢的扩散的膜是指氢的脱离量少的膜。

[0236]

氢的脱离量例如可以利用热脱附谱分析法(tds)等测量。例如,在tds分析中的膜表面温度为50℃至500℃的范围内,当将换算为氢原子的脱离量换算为绝缘体324的每单位面积的量时,绝缘体324中的氢的脱离量为10

×

10

15

atoms/cm2以下,优选为5

×

10

15

atoms/cm2以下,即可。

[0237]

注意,绝缘体326的介电常数优选比绝缘体324低。例如,绝缘体326的相对介电常数优选低于4,更优选低于3。例如,绝缘体326的相对介电常数优选为绝缘体324的相对介电常数的0.7倍以下,更优选为0.6倍以下。通过将介电常数低的材料用于层间膜,可以减少产生在布线之间的寄生电容。

[0238]

此外,在绝缘体320、绝缘体322、绝缘体324及绝缘体326中埋入与电容器600或晶体管500连接的导电体328、导电体330等。此外,导电体328及导电体330具有插头或布线的功能。注意,有时使用同一附图标记表示具有插头或布线的功能的多个导电体。此外,在本说明书等中,布线、与布线连接的插头也可以是一个构成要素。就是说,导电体的一部分有时被用作布线,并且导电体的一部分有时被用作插头。

[0239]

作为各插头及布线(导电体328及导电体330等)的材料,可以使用金属材料、合金材料、金属氮化物材料或金属氧化物材料等导电材料的单层或叠层。优选使用兼具耐热性和导电性的钨或钼等高熔点材料,优选使用钨。或者,优选使用铝或铜等低电阻导电材料。通过使用低电阻导电材料可以降低布线电阻。

[0240]

也可以在绝缘体326及导电体330上形成布线层。例如,在图16中,依次层叠有绝缘体350、绝缘体352及绝缘体354。此外,在绝缘体350、绝缘体352及绝缘体354中形成有导电体356。导电体356具有与晶体管300连接的插头或布线的功能。此外,导电体356可以使用与导电体328及导电体330同样的材料形成。

[0241]

此外,与绝缘体324同样,绝缘体350例如优选使用对氢具有阻挡性的绝缘体。此外,导电体356优选包含对氢具有阻挡性的导电体。尤其是,在对氢具有阻挡性的绝缘体350所包括的开口中形成对氢具有阻挡性的导电体。通过采用该结构,可以使用阻挡层将晶体管300与晶体管500分离,从而可以抑制氢从晶体管300扩散到晶体管500中。

[0242]

注意,作为对氢具有阻挡性的导电体,例如优选使用氮化钽等。此外,通过层叠氮

化钽和导电性高的钨,不但可以保持作为布线的导电性而且可以抑制氢从晶体管300扩散。此时,对氢具有阻挡性的氮化钽层优选与对氢具有阻挡性的绝缘体350接触。

[0243]

此外,也可以在绝缘体354及导电体356上形成布线层。例如,在图16中,依次层叠有绝缘体360、绝缘体362及绝缘体364。此外,在绝缘体360、绝缘体362及绝缘体364中形成有导电体366。导电体366具有插头或布线的功能。此外,导电体366可以使用与导电体328及导电体330同样的材料形成。

[0244]

此外,与绝缘体324同样,绝缘体360例如优选使用对氢具有阻挡性的绝缘体。此外,导电体366优选包含对氢具有阻挡性的导电体。尤其在对氢具有阻挡性的绝缘体360所包括的开口中形成对氢具有阻挡性的导电体。通过采用该结构,可以使用阻挡层将晶体管300与晶体管500分离,从而可以抑制氢从晶体管300扩散到晶体管500中。

[0245]

此外,也可以在绝缘体364及导电体366上形成布线层。例如,在图16中,依次层叠有绝缘体370、绝缘体372及绝缘体374。此外,在绝缘体370、绝缘体372及绝缘体374中形成有导电体376。导电体376具有插头或布线的功能。此外,导电体376可以使用与导电体328及导电体330同样的材料形成。

[0246]

此外,与绝缘体324同样,绝缘体370例如优选使用对氢具有阻挡性的绝缘体。此外,导电体376优选包含对氢具有阻挡性的导电体。尤其在对氢具有阻挡性的绝缘体370所包括的开口中形成对氢具有阻挡性的导电体。通过采用该结构,可以使用阻挡层将晶体管300与晶体管500分离,从而可以抑制氢从晶体管300扩散到晶体管500中。

[0247]

此外,也可以在绝缘体374及导电体376上形成布线层。例如,在图16中,依次层叠有绝缘体380、绝缘体382及绝缘体384。此外,在绝缘体380、绝缘体382及绝缘体384中形成有导电体386。导电体386具有插头或布线的功能。此外,导电体386可以使用与导电体328及导电体330同样的材料形成。

[0248]

此外,与绝缘体324同样,绝缘体380例如优选使用对氢具有阻挡性的绝缘体。此外,导电体386优选包含对氢具有阻挡性的导电体。尤其在对氢具有阻挡性的绝缘体380所包括的开口中形成对氢具有阻挡性的导电体。通过采用该结构,可以使用阻挡层将晶体管300与晶体管500分离,从而可以抑制氢从晶体管300扩散到晶体管500中。

[0249]

在上面说明包括导电体356的布线层、包括导电体366的布线层、包括导电体376的布线层及包括导电体386的布线层,但是本实施方式的半导体装置不局限于此。与包括导电体356的布线层同样的布线层可以为三层以下,与包括导电体356的布线层同样的布线层可以为五层以上。

[0250]

在绝缘体384上依次层叠有绝缘体510、绝缘体512、绝缘体514及绝缘体516。作为绝缘体510、绝缘体512、绝缘体514及绝缘体516中的一个,优选使用对氧或氢具有阻挡性的物质。

[0251]

例如,作为绝缘体510及绝缘体514,优选使用能够防止氢或杂质从衬底311或设置有晶体管300的区域等扩散到设置有晶体管500的区域中的具有阻挡性的膜。因此,绝缘体510及绝缘体514可以使用与绝缘体324同样的材料。

[0252]

作为对氢具有阻挡性的膜的一个例子,可以使用通过cvd法形成的氮化硅。在此,有时氢扩散到晶体管500等具有氧化物半导体的半导体元件中,导致该半导体元件的特性下降。因此,优选在晶体管300与晶体管500之间设置抑制氢的扩散的膜。具体而言,抑制氢

的扩散的膜是指氢的脱离量少的膜。

[0253]

例如,作为对氢具有阻挡性的膜,绝缘体510及绝缘体514优选使用氧化铝、氧化铪、氧化钽等金属氧化物。

[0254]

尤其是,氧化铝的不使氧及导致晶体管的电特性变动的氢、水分等杂质透过的阻挡效果高。因此,在晶体管的制造工序中及制造工序之后,氧化铝可以防止氢、水分等杂质进入晶体管500中。此外,氧化铝可以抑制氧从构成晶体管500的氧化物释放。因此,氧化铝适合用于晶体管500的保护膜。

[0255]

例如,作为绝缘体512及绝缘体516,可以使用与绝缘体320同样的材料。此外,通过作为上述绝缘体使用介电常数较低的材料,可以减少产生在布线之间的寄生电容。例如,作为绝缘体512及绝缘体516,可以使用氧化硅膜和氧氮化硅膜等。

[0256]

此外,在绝缘体510、绝缘体512、绝缘体514及绝缘体516中例如埋入有导电体518、构成晶体管500的导电体(例如,导电体503)等。此外,导电体518被用作与电容器600或晶体管300连接的插头或布线。导电体518可以使用与导电体328及导电体330同样的材料形成。

[0257]

尤其是,与绝缘体510及绝缘体514接触的区域的导电体518优选为对氧、氢及水具有阻挡性的导电体。通过采用该结构,可以利用对氧、氢及水具有阻挡性的层将晶体管300与晶体管500分离,从而可以抑制氢从晶体管300扩散到晶体管500中。

[0258]

在绝缘体516的上方设置有晶体管500。

[0259]

如图18a和图18b所示,晶体管500包括:嵌入在绝缘体514及绝缘体516中的导电体503;配置在绝缘体516及导电体503上的绝缘体520;配置在绝缘体520上的绝缘体522;配置在绝缘体522上的绝缘体524;配置在绝缘体524上的氧化物530a;配置在氧化物530a上的氧化物530b;配置在氧化物530b上且彼此隔开的导电体542a及导电体542b;配置在导电体542a及导电体542b上且形成有与导电体542a和导电体542b之间重叠的开口的绝缘体580;配置在开口的底面及侧面上的氧化物530c;配置在氧化物530c的形成面的绝缘体550;以及配置在绝缘体550的形成面上的导电体560。

[0260]

另外,如图18a和图18b所示,优选在氧化物530a、氧化物530b、导电体542a及导电体542b与绝缘体580之间配置有绝缘体544。此外,如图18a和图18b所示,导电体560优选包括设置在绝缘体550的内侧的导电体560a及嵌入在导电体560a的内侧的导电体560b。此外,如图18a和图18b所示,优选在绝缘体580、导电体560及绝缘体550上配置有绝缘体574。

[0261]

注意,下面有时将氧化物530a、氧化物530b及氧化物530c总称为氧化物530。

[0262]

在晶体管500中,在形成沟道的区域及其附近层叠有氧化物530a、氧化物530b及氧化物530c的三层,但是本发明不局限于此。例如,可以设置氧化物530b的单层、氧化物530b与氧化物530a的两层结构、氧化物530b与氧化物530c的两层结构或者四层以上的叠层结构。另外,在晶体管500中,导电体560具有两层结构,但是本发明不局限于此。例如,导电体560也可以具有单层结构或三层以上的叠层结构。注意,图16、图18a所示的晶体管500的结构只是一个例子而不局限于上述结构,可以根据电路结构或驱动方法使用适当的晶体管。

[0263]

在此,导电体560被用作晶体管的栅电极,导电体542a及导电体542b被用作源电极或漏电极。如上所述,导电体560填埋于绝缘体580的开口中及夹在导电体542a与导电体542b之间的区域。导电体560、导电体542a及导电体542b相对于绝缘体580的开口的配置是自对准地被选择。换言之,在晶体管500中,可以在源电极与漏电极之间自对准地配置栅电

极。由此,可以在不设置用于对准的余地的方式形成导电体560,所以可以实现晶体管500的占有面积的缩小。由此,可以实现半导体装置的微型化及高集成化。

[0264]

再者,导电体560自对准地形成在导电体542a与导电体542b之间的区域,所以导电体560不包括与导电体542a及导电体542b重叠的区域。由此,可以降低形成在导电体560与导电体542a及导电体542b之间的寄生电容。因此,可以提高晶体管500的开关速度,从而晶体管500可以具有高频率特性。

[0265]

导电体560有时被用作第一栅(也称为顶栅极)电极。导电体503有时被用作第二栅(也称为底栅极)电极。在此情况下,通过独立地改变供应到导电体503的电位而不使其与供应到导电体560的电位联动,可以控制晶体管500的阈值电压。尤其是,通过对导电体503供应负电位,可以使晶体管500的阈值电压大于0v且可以减小关态电流。因此,与不对导电体503施加负电位时相比,在对导电体503施加负电位的情况下,可以减小对导电体560供应的电位为0v时的漏极电流。导电体503以与氧化物530及导电体560重叠的方式配置。由此,在对导电体560及导电体503供应电位的情况下,从导电体560产生的电场和从导电体503产生的电场连接,可以覆盖形成在氧化物530中的沟道形成区域。在本说明书等中,将由第一栅电极的电场和第二栅电极的电场电围绕沟道形成区域的晶体管的结构称为surrounded channel(s-channel:围绕沟道)结构。

[0266]

另外,导电体503与导电体518具有相同的结构,以与绝缘体514及绝缘体516的开口的内壁接触的方式形成有导电体503a,其内侧形成有导电体503b。在此,在晶体管500中,叠层有导电体503a与导电体503b,但是本发明不局限于此。例如,导电体503可以具有单层结构,也可以具有三层以上的叠层结构。

[0267]

在此,作为导电体503a优选使用具有抑制氢原子、氢分子、水分子、铜原子等杂质的扩散的功能(不容易使上述杂质透过)的导电材料。另外,优选使用具有抑制氧(例如,氧原子、氧分子等中的至少一个)的扩散的功能(不容易使上述氧透过)的导电材料。在本说明书中,“抑制杂质或氧的扩散的功能”是指抑制上述杂质和上述氧中的任一个或全部的扩散的功能。

[0268]

例如,通过使导电体503a具有抑制氧的扩散的功能,可以抑制因导电体503b氧化而导致导电率的下降。

[0269]

另外,在导电体503还具有布线的功能的情况下,作为导电体503b,优选使用以钨、铜或铝为主要成分的导电性高的导电材料。在此情况下,不一定需要设置导电体505。在附图中,导电体503b具有单层结构,但是也可以具有叠层结构,例如,可以采用钛、氮化钛和上述导电材料的叠层结构。

[0270]

绝缘体520、绝缘体522、绝缘体524及绝缘体550被用作第二栅极绝缘膜。

[0271]

在此,与氧化物530接触的绝缘体524优选使用包含超过化学计量组成的氧的绝缘体。换言之,优选在绝缘体524中形成有过剩氧区域。通过以与氧化物530接触的方式设置上述包含过剩氧的绝缘体,可以减少氧化物530中的氧缺陷,从而可以提高晶体管500的可靠性。

[0272]

具体而言,作为具有过剩氧区域的绝缘体,优选使用通过加热使一部分的氧脱离的氧化物材料。通过加热使氧脱离的氧化物是指在tds(thermal desorption spectroscopy:热脱附谱)分析中换算为氧原子的氧的脱离量为1.0

×

10

18

atoms/cm3以上,

优选为1.0

×

10

19

atoms/cm3以上,进一步优选为2.0

×

10

19

atoms/cm3以上,或者3.0

×

10

20

atoms/cm3以上的氧化物膜。另外,进行上述tds分析时的膜的表面温度优选在100℃以上且700℃以下,或者100℃以上且400℃以下的范围内。

[0273]

当绝缘体524具有过剩氧区域时,绝缘体522优选具有抑制氧(例如,氧原子、氧分子等)的扩散的功能(不容易使上述氧透过)。

[0274]

当绝缘体522具有抑制氧或杂质的扩散的功能时,氧化物530所包含的氧不扩散到绝缘体520一侧,所以是优选的。另外,可以抑制导电体503与绝缘体524或氧化物530所包含的氧起反应。

[0275]

作为绝缘体522,例如优选使用包含氧化铝、氧化铪、含有铝及铪的氧化物(铝酸铪)、氧化钽、氧化锆、锆钛酸铅(pzt)、钛酸锶(srtio3)或(ba,sr)tio3(bst)等所谓的high-k材料的绝缘体的单层或叠层。当进行晶体管的微型化及高集成化时,由于栅极绝缘膜的薄膜化,有时发生泄漏电流等问题。通过作为被用作栅极绝缘膜的绝缘体使用high-k材料,可以在保持物理厚度的同时降低晶体管工作时的栅极电位。

[0276]

尤其是,优选使用作为具有抑制杂质及氧等的扩散的功能(不容易使上述氧透过)的绝缘材料的包含铝和铪中的一方或双方的氧化物的绝缘体。作为包含铝和铪中的一方或双方的氧化物的绝缘体,优选使用氧化铝、氧化铪、包含铝及铪的氧化物(铝酸铪)等。当使用这种材料形成绝缘体522时,绝缘体522被用作抑制氧从氧化物530释放或氢等杂质从晶体管500的周围部进入氧化物530的层。

[0277]

或者,例如也可以对上述绝缘体添加氧化铝、氧化铋、氧化锗、氧化铌、氧化硅、氧化钛、氧化钨、氧化钇、氧化锆。此外,也可以对上述绝缘体进行氮化处理。还可以在上述绝缘体上层叠氧化硅、氧氮化硅或氮化硅。

[0278]

绝缘体520优选具有热稳定性。例如,因为氧化硅及氧氮化硅具有热稳定性,所以是优选的。另外,通过组合high-k材料的绝缘体与氧化硅或氧氮化硅,可以形成具有热稳定性且相对介电常数高的叠层结构的绝缘体520。

[0279]

另外,在图18a及图18b中的晶体管500中,作为三层叠层结构的第二栅极绝缘膜使用绝缘体520、绝缘体522及绝缘体524,但是第二栅极绝缘膜也可以采用单层、两层或四层以上的叠层结构。此时,不局限于使用相同材料构成的叠层结构,也可以是使用不同材料形成的叠层结构。

[0280]

在晶体管500中,优选将被用作氧化物半导体的金属氧化物用于包含沟道形成区域的氧化物530。例如,作为氧化物530优选使用in-m-zn氧化物(元素m为选自铝、镓、钇、铜、钒、铍、硼、钛、铁、镍、锗、锆、钼、镧、铈、钕、铪、钽、钨和镁等中的一种或多种)等金属氧化物。尤其是,能够应用于氧化物530的in-m-zn氧化物优选为caac-os或cac-os。此外,作为氧化物530,也可以使用in-ga氧化物、in-zn氧化物。

[0281]

作为在氧化物530中被用作沟道形成区域的金属氧化物,优选使用其带隙为2ev以上,优选为2.5ev以上的金属氧化物。如此,通过使用带隙较宽的金属氧化物,可以减小晶体管的关态电流。

[0282]

在氧化物530中,当在氧化物530b之下设置有氧化物530a时,可以防止杂质从形成在氧化物530a下的结构物扩散到氧化物530b。当在氧化物530b之上设置有氧化物530c时,可以防止杂质从形成在氧化物530c的上方的结构物扩散到氧化物530b。

[0283]

另外,氧化物530优选具有各金属原子的原子个数比互不相同的氧化物的叠层结构。具体而言,用于氧化物530a的金属氧化物的构成元素中的元素m的原子个数比优选大于用于氧化物530b的金属氧化物的构成元素中的元素m的原子个数比。另外,用于氧化物530a的金属氧化物中的相对于in的元素m的原子个数比优选大于用于氧化物530b的金属氧化物中的相对于in的元素m的原子个数比。另外,用于氧化物530b的金属氧化物中的相对于元素m的in的原子个数比优选大于用于氧化物530a的金属氧化物中的相对于元素m的in的原子个数比。另外,氧化物530c可以使用可用于氧化物530a或氧化物530b的金属氧化物。

[0284]

优选的是,使氧化物530a及氧化物530c的导带底的能量高于氧化物530b的导带底的能量。换言之,氧化物530a及氧化物530c的电子亲和势优选小于氧化物530b的电子亲和势。

[0285]

在此,在氧化物530a、氧化物530b及氧化物530c的接合部中,导带底的能级平缓地变化。换言之,也可以将上述情况表达为氧化物530a、氧化物530b及氧化物530c的接合部的导带底的能级连续地变化或者连续地接合。为此,优选降低形成在氧化物530a与氧化物530b的界面以及氧化物530b与氧化物530c的界面的混合层的缺陷态密度。

[0286]

具体而言,通过使氧化物530a与氧化物530b、以及氧化物530b与氧化物530c除了氧之外包含共同元素(为主要成分),可以形成缺陷态密度低的混合层。例如,在氧化物530b为in-ga-zn氧化物的情况下,作为氧化物530a及氧化物530c优选使用in-ga-zn氧化物、ga-zn氧化物及氧化镓等。

[0287]

此时,载流子的主要路径为氧化物530b。通过使氧化物530a及氧化物530c具有上述结构,可以降低氧化物530a与氧化物530b的界面及氧化物530b与氧化物530c的界面的缺陷态密度。因此,界面散射对载流子传导的影响减少,可以提高晶体管500的通态电流。

[0288]

在氧化物530b上设置有被用作源电极及漏电极的导电体542a及导电体542b。作为导电体542a及导电体542b,优选使用选自铝、铬、铜、银、金、铂、钽、镍、钛、钼、钨、铪、钒、铌、锰、镁、锆、铍、铟、钌、铱、锶和镧中的金属元素、以上述金属元素为成分的合金或者组合上述金属元素的合金等。例如,优选使用氮化钽、氮化钛、钨、包含钛和铝的氮化物、包含钽和铝的氮化物、氧化钌、氮化钌、包含锶和钌的氧化物、包含镧和镍的氧化物等。另外,氮化钽、氮化钛、包含钛和铝的氮化物、包含钽和铝的氮化物、氧化钌、氮化钌、包含锶和钌的氧化物、包含镧和镍的氧化物是不容易氧化的导电材料或者吸收氧也维持导电性的材料,所以是优选的。再者,氮化钽等金属氮化物膜对氢或氧具有阻挡性,所以是优选的。

[0289]

此外,虽然在图18a及图18b中将导电体542a及导电体542b示为单层结构,但是也可以采用两层以上的叠层结构。例如,优选层叠氮化钽膜及钨膜。另外,也可以层叠钛膜及铝膜。另外,也可以采用在钨膜上层叠铝膜的两层结构、在铜-镁-铝合金膜上层叠铜膜的两层结构、在钛膜上层叠铜膜的两层结构、在钨膜上层叠铜膜的两层结构。

[0290]

另外,也可以使用:在钛膜或氮化钛膜上层叠铝膜或铜膜并在其上形成钛膜或氮化钛膜的三层结构、在钼膜或氮化钼膜上层叠铝膜或铜膜并在其上形成钼膜或氮化钼膜的三层结构等。另外,也可以使用包含氧化铟、氧化锡或氧化锌的透明导电材料。

[0291]

另外,如图18a所示,有时在氧化物530与导电体542a(导电体542b)的界面及其附近作为低电阻区域形成有区域543a及区域543b。此时,区域543a被用作源区域和漏区域的一个,区域543b被用作源区域和漏区域的另一个。此外,沟道形成区域形成在夹在区域543a

和区域543b之间的区域中。

[0292]

通过以与氧化物530接触的方式形成上述导电体542a(导电体542b),区域543a(区域543b)的氧浓度有时降低。另外,在区域543a(区域543b)中有时形成包括包含在导电体542a(导电体542b)中的金属及氧化物530的成分的金属化合物层。在此情况下,区域543a(区域543b)的载流子密度增加,区域543a(区域543b)成为低电阻区域。

[0293]

绝缘体544以覆盖导电体542a及导电体542b的方式设置,抑制导电体542a及导电体542b的氧化。此时,绝缘体544也可以以覆盖氧化物530的侧面且与绝缘体524接触的方式设置。

[0294]

作为绝缘体544,可以使用包含选自铪、铝、镓、钇、锆、钨、钛、钽、镍、锗、钕、镧和镁等中的一种或两种以上的金属氧化物。此外,作为绝缘体544,也可以使用氮氧化硅或氮化硅等。

[0295]

尤其是,作为绝缘体544,优选使用作为包含铝和铪中的一方或双方的氧化物的绝缘体的氧化铝、氧化铪、包含铝及铪的氧化物(铝酸铪)等。尤其是,铝酸铪的耐热性比氧化铪膜高。因此,在后面的工序的热处理中不容易晶化,所以是优选的。另外,在导电体542a及导电体542b是具有耐氧化性的材料或者即使吸收氧也不会显著降低导电性的情况下,不需要必须设置绝缘体544。根据所需要的晶体管特性,适当地设计即可。

[0296]

通过包括绝缘体544,可以抑制绝缘体580所包含的水及氢等杂质经过氧化物530c、绝缘体550扩散到氧化物530b。此外,可以抑制绝缘体580所包含的过剩氧使导电体560氧化。

[0297]

另外,绝缘体550被用作第一栅极绝缘膜。绝缘体550优选以与氧化物530c的内侧(上面及侧面)接触的方式配置。与上述绝缘体524同样,绝缘体550优选使用包含过量氧且通过加热释放氧的绝缘体形成。

[0298]

具体而言,可以使用包含过剩氧的氧化硅、氧氮化硅、氮氧化硅、氮化硅、添加有氟的氧化硅、添加有碳的氧化硅、添加有碳及氮的氧化硅、具有空孔的氧化硅。尤其是,氧化硅及氧氮化硅具有热稳定性,所以是优选的。

[0299]

通过作为绝缘体550以与氧化物530c的顶面接触的方式设置通过加热而释放氧的绝缘体,可以有效地从绝缘体550通过氧化物530c对氧化物530b的沟道形成区域供应氧。此外,与绝缘体524同样,优选降低绝缘体550中的水或氢等杂质的浓度。绝缘体550的厚度优选为1nm以上且20nm以下。

[0300]

另外,为了将绝缘体550所包含的过剩氧高效地供应到氧化物530,也可以在绝缘体550与导电体560之间设置金属氧化物。该金属氧化物优选抑制从绝缘体550到导电体560的氧扩散。通过设置抑制氧的扩散的金属氧化物,从绝缘体550到导电体560的过剩氧的扩散得到抑制。换言之,可以抑制供应到氧化物530的过剩氧的减少。另外,可以抑制因过剩氧导致的导电体560的氧化。作为该金属氧化物,可以使用可用于绝缘体544的材料。

[0301]

另外,绝缘体550也可以具有与第二栅极绝缘膜同样的叠层结构。随着晶体管的微型化及高集成化,由于栅极绝缘膜的薄膜化,有时发生泄漏电流等问题。因此,通过使被用作栅极绝缘膜的绝缘体具有high-k材料与具有热稳定性的材料的叠层结构,可以在保持物理厚度的同时降低晶体管工作时的栅极电位。此外,可以实现具有热稳定性及高相对介电常数的叠层结构。

[0302]

在图18a及图18b中,被用作第一栅电极的导电体560具有两层结构,但是也可以具有单层结构或三层以上的叠层结构。

[0303]

作为导电体560a,优选使用具有抑制氢原子、氢分子、水分子、氮原子、氮分子、氧化氮分子(n2o、no、no2等)、铜原子等杂质的扩散的功能的导电材料。另外,优选使用具有抑制氧(例如,氧原子、氧分子等中的至少一个)的扩散的功能的导电材料。通过使导电体560a具有抑制氧的扩散的功能,可以抑制因绝缘体550所包含的氧导致导电体560b氧化而导电率下降。作为具有抑制氧的扩散的功能的导电材料,例如,优选使用钽、氮化钽、钌或氧化钌等。此外,作为导电体560a,可以使用适用于氧化物530的氧化物半导体。此时,通过使用溅镀法形成导电体560b,可以降低导电体560a的电阻值并使其成为导电体。可以将其称为oc(oxideconductor:氧化物导电体)电极。

[0304]

作为导电体560b,优选使用以钨、铜或铝为主要成分的导电材料。由于导电体560b还被用作布线,所以优选使用导电性高的导电体。例如,可以使用以钨、铜或铝为主要成分的导电材料。导电体560b也可以具有叠层结构,例如,可以采用钛、氮化钛和上述导电材料的叠层结构。

[0305]

绝缘体580优选隔着绝缘体544设置在导电体542a及导电体542b上。绝缘体580优选具有过剩氧区域。例如,绝缘体580优选包含氧化硅、氧氮化硅、氮氧化硅、氮化硅、添加有氟的氧化硅、添加有碳的氧化硅、添加有碳及氮的氧化硅、具有空孔的氧化硅或树脂等。尤其是,氧化硅及氧氮化硅具有热稳定性,所以是优选的。尤其是,氧化硅和具有空孔的氧化硅容易在后面的工序中形成过剩氧区域,所以是优选的。

[0306]

绝缘体580优选具有过剩氧区域。通过以与氧化物530c接触的方式设置因加热而释放氧的绝缘体580,可以将绝缘体580中的氧通过氧化物530c高效地供应给氧化物530。另外,优选降低绝缘体580中的水或氢等杂质的浓度。

[0307]

绝缘体580的开口以与导电体542a和导电体542b之间的区域重叠的方式形成。由此,导电体560填埋于绝缘体580的开口中及夹在导电体542a与导电体542b之间的区域。

[0308]

在进行半导体装置的微型化时,需要缩短栅极长度,但是需要防止导电体560的导电性的下降。为此,在增大导电体560的厚度的情况下,导电体560有可能具有纵横比高的形状。在本实施方式中,由于将导电体560填埋于绝缘体580的开口,所以即使导电体560具有纵横比高的形状,在工序中也不发生导电体560的倒塌。

[0309]

绝缘体574优选以与绝缘体580的顶面、导电体560的顶面及绝缘体550的顶面接触的方式设置。通过利用溅射法形成绝缘体574,可以在绝缘体550及绝缘体580中形成过剩氧区域。由此,可以将氧从该过剩氧区域供应到氧化物530中。

[0310]

例如,作为绝缘体574,可以使用包含选自铪、铝、镓、钇、锆、钨、钛、钽、镍、锗和镁等中的一种或两种以上的金属氧化物。

[0311]

尤其是,氧化铝具有高阻挡性,即使是0.5nm以上且3.0nm以下的薄膜,也可以抑制氢及氮的扩散。由此,通过利用溅射法形成的氧化铝可以在被用作氧供应源的同时还具有氢等杂质的阻挡膜的功能。

[0312]

另外,优选在绝缘体574上设置被用作层间膜的绝缘体581。与绝缘体524等同样,优选降低绝缘体581中的水或氢等杂质的浓度。

[0313]

另外,在形成于绝缘体581、绝缘体574、绝缘体580及绝缘体544中的开口配置导电

体540a及导电体540b。导电体540a及导电体540b以隔着导电体560彼此对置的方式设置。导电体540a及导电体540b具有与后面说明的导电体546及导电体548同样的结构。

[0314]

在绝缘体581上设置有绝缘体582。绝缘体582优选使用对氧或氢具有阻挡性的物质。因此,作为绝缘体582可以使用与绝缘体514同样的材料。例如,作为绝缘体582优选使用氧化铝、氧化铪、氧化钽等金属氧化物。

[0315]

尤其是,氧化铝的不使氧及导致晶体管的电特性变动的氢、水分等杂质透过的阻挡效果高。因此,在晶体管的制造工序中及制造工序之后,氧化铝可以防止氢、水分等杂质进入晶体管500中。此外,氧化铝可以抑制氧从构成晶体管500的氧化物释放。因此,氧化铝适合用于晶体管500的保护膜。

[0316]

此外,在绝缘体582上设置有绝缘体586。作为绝缘体586可以使用与绝缘体320同样的材料。此外,通过将介电常数较低的材料用于上述绝缘体,可以减少产生在布线之间的寄生电容。例如,作为绝缘体586,可以使用氧化硅膜及氧氮化硅膜等。

[0317]

此外,在绝缘体520、绝缘体522、绝缘体524、绝缘体544、绝缘体580、绝缘体574、绝缘体581、绝缘体582及绝缘体586中埋入导电体546及导电体548等。

[0318]

导电体546及导电体548被用作与电容器600、晶体管500或晶体管300连接的插头或布线。导电体546及导电体548可以使用与导电体328及导电体330同样的材料形成。

[0319]

接着,在晶体管500的上方设置有电容器600。电容器600包括导电体610、导电体620及绝缘体630。

[0320]

此外,也可以在导电体546及导电体548上设置导电体612。导电体612被用作与晶体管500连接的插头或者布线。导电体610被用作电容器600的电极。此外,可以同时形成导电体612及导电体610。

[0321]

作为导电体612及导电体610可以使用包含选自钼、钛、钽、钨、铝、铜、铬、钕、钪中的元素的金属膜或以上述元素为成分的金属氮化物膜(氮化钽膜、氮化钛膜、氮化钼膜、氮化钨膜)等。或者,也可以使用铟锡氧化物、包含氧化钨的铟氧化物、包含氧化钨的铟锌氧化物、包含氧化钛的铟氧化物、包含氧化钛的铟锡氧化物、铟锌氧化物、添加有氧化硅的铟锡氧化物等导电材料。

[0322]

在图16中,导电体612及导电体610具有单层结构,但是不局限于此,也可以具有两层以上的叠层结构。例如,也可以在具有阻挡性的导电体与导电性高的导电体之间形成与具有阻挡性的导电体以及导电性高的导电体紧密性高的导电体。

[0323]

以隔着绝缘体630重叠于导电体610的方式设置导电体620。作为导电体620可以使用金属材料、合金材料、金属氧化物材料等导电材料。优选使用兼具耐热性和导电性的钨或钼等高熔点材料,尤其优选使用钨。当与导电体等其他构成要素同时形成导电体620时,使用低电阻金属材料的cu(铜)或al(铝)等即可。

[0324]

在导电体620及绝缘体630上设置有绝缘体650。绝缘体650可以使用与绝缘体320同样的材料形成。此外,绝缘体650可以被用作覆盖其下方的凹凸形状的平坦化膜。

[0325]

通过采用本结构,可以在抑制使用包含氧化物半导体的晶体管的半导体装置的电特性变动的同时提高可靠性。此外,可以实现使用包含氧化物半导体的晶体管的半导体装置的微型化或高集成化。

[0326]

<关于本说明书等的记载的附记>

[0327]

下面,对上述实施方式及实施方式中的各结构的说明附加注释。

[0328]

各实施方式所示的结构可以与其他实施方式所示的结构适当地组合而构成本发明的一个方式。另外,当在一个实施方式中示出多个结构实例时,可以适当地组合这些结构实例。

[0329]

另外,可以将某一实施方式中说明的内容(或其一部分)应用/组合/替换成该实施方式中说明的其他内容(或其一部分)及/或另一个或多个其他实施方式中说明的内容(或其一部分)。

[0330]

注意,实施方式中说明的内容是指各实施方式中利用各种附图所说明的内容或者利用说明书所记载的文章而说明的内容。

[0331]

另外,通过将某一实施方式中示出的附图(或其一部分)与该附图的其他部分、该实施方式中示出的其他附图(或其一部分)及/或另一个或多个其他实施方式中示出的附图(或其一部分)组合,可以构成更多图。

[0332]

在本说明书等中,根据功能对构成要素进行分类并在方框图中以彼此独立的方框表示。然而,在实际的电路等中难以根据功能分类构成要素,有时一个电路涉及到多个功能或者多个电路涉及到一个功能。因此,方框图中的方框的分割不局限于说明书中说明的构成要素,而可以根据情况适当地不同。

[0333]

为了便于说明,在附图中,任意示出尺寸、层的厚度或区域。因此,本发明并不局限于附图中的尺寸。附图是为了明确起见而示意性地示出的,而不局限于附图所示的形状或数值等。例如,可以包括因噪声或定时偏差等所引起的信号、电压或电流的不均匀等。

[0334]

在本说明书等中,在说明晶体管的连接关系时,使用将源极和漏极中的一方记为“源极和漏极中的一个”(第一电极或第一端子),将源极和漏极中的另一方记为“源极和漏极中的另一个”(第二电极或第二端子)的表述。这是因为晶体管的源极和漏极根据晶体管的结构或工作条件等改变。注意,根据情况可以将晶体管的源极和漏极适当地换称为源极(漏极)端子或源极(漏极)电极等。

[0335]

另外,在本说明书等中,“电极”或“布线”不在功能上限定其构成要素。例如,有时将“电极”用作“布线”的一部分,反之亦然。再者,“电极”或“布线”还包括多个“电极”或“布线”被形成为一体的情况等。

[0336]

另外,在本说明书等中,可以适当地调换电压和电位。电压是指与基准电位之间的电位差,例如在基准电位为地电压(接地电压)时,可以将电压换称为电位。接地电位不一定意味着0v。注意,电位是相对的,对布线等供应的电位有时根据基准电位而变化。

[0337]

在本说明书等中,根据情况或状态,可以互相调换“膜”和“层”等词句。例如,有时可以将“导电层”调换为“导电膜”。此外,有时可以将“绝缘膜”调换为“绝缘层”。

[0338]

在本说明书等中,开关是指具有通过变为导通状态(开启状态)或非导通状态(关闭状态)来控制是否使电流流过的功能的元件。另外,开关是指具有选择并切换电流路径的功能的元件。

[0339]

在本说明书等中,例如,沟道长度是指在晶体管的俯视图中,半导体(或在晶体管处于开启状态时,在半导体中电流流过的部分)和栅极重叠的区域或者形成沟道的区域中的源极和漏极之间的距离。

[0340]

在本说明书等中,例如,沟道宽度是指半导体(或在晶体管处于开启状态时,在半

导体中电流流过的部分)和栅电极重叠的区域、或者形成沟道的区域中的源极和漏极相对的部分的长度。

[0341]

在本说明书等中,“a与b连接”除了包括a与b直接连接的情况以外,还包括a与b电连接的情况。在此,“使a与b电连接”的描述是指当在a与b之间存在具有某种电作用的对象物时,能够进行a和b的电信号的授受的情况。

[0342]

[符号说明]

[0343]

10:存储部、10a:存储部、20a:存储电路、20b:存储电路、21a:存储电路、21b:存储电路、21c:存储电路、21d:存储电路、22a:存储电路、22b:存储电路、22c:存储电路、22d:存储电路、26a:存储电路、26b:存储电路、27a:存储电路、27b:存储电路、27c:存储电路、27d:存储电路、28a:存储电路、28b:存储电路、28c:存储电路、28d:存储电路、30:电路、31:电路、40:输入输出电路、50:控制部、50a:控制部、60:传感器部、70:外围电路、300:晶体管、311:衬底、313:半导体区域、314a:低电阻区域、314b:低电阻区域、315:绝缘体、316:导电体、320:绝缘体、322:绝缘体、324:绝缘体、326:绝缘体、328:导电体、330:导电体、350:绝缘体、352:绝缘体、354:绝缘体、356:导电体、360:绝缘体、362:绝缘体、364:绝缘体、366:导电体、370:绝缘体、372:绝缘体、374:绝缘体、376:导电体、380:绝缘体、382:绝缘体、384:绝缘体、386:导电体、500:晶体管、503:导电体、503a:导电体、503b:导电体、505:导电体、510:绝缘体、512:绝缘体、514:绝缘体、516:绝缘体、518:导电体、520:绝缘体、522:绝缘体、524:绝缘体、530:氧化物、530a:氧化物、530b:氧化物、530c:氧化物、540a:导电体、540b:导电体、542a:导电体、542b:导电体、543a:区域、543b:区域、544:绝缘体、546:导电体、548:导电体、550:绝缘体、560:导电体、560a:导电体、560b:导电体、574:绝缘体、580:绝缘体、581:绝缘体、582:绝缘体、586:绝缘体、600:电容器、610:导电体、612:导电体、620:导电体、630:绝缘体、650:绝缘体、1201:护栏、2100:机器人、2101:照度传感器、2102:麦克风、2103:上部照相机、2104:扬声器、2105:显示器、2106:下部照相机、2107:障碍物传感器、2108:移动机构、2110:运算装置、2120:飞行物、2121:运算装置、2122:照相机、2123:螺旋桨、2910:信息终端、2911:外壳、2912:显示部、2913:照相机、2914:扬声器部、2915:操作开关、2916:外部连接部、2917:麦克风、2920:扫地机器人、2921:外壳、2922:显示部、2923:操作按钮、2924:照相机、2925:刷子、2980:汽车、2981:照相机、5101:显示器、5103:刷子

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。