[0001]

本发明涉及电路装置、物理量测量装置、电子设备以及移动体等。

背景技术:

[0002]

以往,公知有将时间转换为数字值的时间数字转换电路。时间数字转换电路例如将被称为开始信号的第1信号与被称为停止信号的第2信号的转变定时的时间差转换为数字值。作为这样的时间数字转换电路的现有例,例如公知有专利文献1所公开的现有技术。专利文献1的时间数字转换电路将来自2个环形振荡电路的振荡时钟信号的频率差作为分辨率而进行时间数字转换。

[0003]

专利文献1:日本特开2019-39882号公报

[0004]

在使用了振荡时钟信号的频率差的时间数字转换中,当第1信号与第2信号的转变定时的时间差变长时,使2个环形振荡电路进行动作的时间会与该时间差成比例地变长。因此,2个振荡时钟信号的抖动分别被积累,由此时间数字转换的测量精度有可能下降。

技术实现要素:

[0005]

根据本发明的几个方式,能够提供可抑制由于时钟抖动被积累而引起的时间数字转换的测量精度下降的电路装置、物理量测量装置、电子设备以及移动体等。

[0006]

本公开的一个方式涉及电路装置,该电路装置包含:时钟信号生成电路,其生成频率相同且相位不同的多个多相时钟信号;时间数字转换电路,其进行基于与所述多个多相时钟信号中的任意一个多相时钟信号对应的第i时钟信号的计数动作,求出与第1信号的转变定时和第2信号的转变定时的时间差对应的计数值,求出第1数字值并求出第2数字值,所述第1数字值对应于从所述第1信号的转变定时到与所述多个多相时钟信号中的任意一个多相时钟信号对应的第j时钟信号的转变定时为止的时间差,所述第2数字值对应于从所述第2信号的转变定时到与所述多个多相时钟信号中的任意一个多相时钟信号对应的第k时钟信号的转变定时为止的时间差;以及处理电路,其根据所述计数值、所述第1数字值和所述第2数字值,求出与所述第1信号的转变定时和所述第2信号的转变定时的时间差对应的数字值。

附图说明

[0007]

图1是本实施方式的电路装置的结构例。

[0008]

图2是对本实施方式的动作进行说明的信号波形图。

[0009]

图3是比较例的时间数字转换方法的说明图。

[0010]

图4是时钟信号生成电路的结构例。

[0011]

图5是时钟信号生成电路的详细结构例。

[0012]

图6是时间数字转换电路的结构例。

[0013]

图7是时间数字转换电路的详细结构例。

[0014]

图8是对使用振荡时钟信号的频率差来测量转变定时的时间差的处理进行说明的信号波形图。

[0015]

图9是对使用振荡时钟信号的频率差来测量转变定时的时间差的处理进行说明的信号波形图。

[0016]

图10是计数电路的结构例。

[0017]

图11是对本实施方式的详细动作进行说明的信号波形图。

[0018]

图12是对本实施方式的详细动作进行说明的信号波形图。

[0019]

图13是针对时钟信号的选择方法的说明图。

[0020]

图14是针对时钟信号的选择方法的说明图。

[0021]

图15是物理量测量装置的结构例。

[0022]

图16是电子设备的结构例。

[0023]

图17是移动体的结构例。

[0024]

标号说明

[0025]

10:电路装置;20:时钟信号生成电路;22:环形振荡电路;24、26:锁存电路;27、28、29:占空比调整电路;30:pll电路;31:相位比较电路;32:控制电压生成电路;33:电荷泵电路;36:分频电路;38:振荡电路;40:时间数字转换电路;42:计数电路;43、44、45:计数器;50:开始用振荡电路;51:振荡电路;52:振荡电路;53、54、55:振荡电路;55、56、57、58:时间数字转换器;60:停止用振荡电路;61、62、63、64:振荡电路;65、66、67、68:时间数字转换器;80:处理电路;160:时间数字转换电路;162、164:振荡电路;166:处理电路;206:汽车;207:车体;208:控制装置;209:车轮;220:处理装置;400:物理量测量装置;410:发光部;420:受光部;430:处理装置;500:电子设备;510:通信接口;520:处理装置;530:操作界面;540:显示部;550:存储器;an1、an2、an3、an4:and电路;ckf、ckf1~ckf6、ckfj、ckfk:振荡时钟信号;cks、cksa、cksp:振荡时钟信号;cki、ckj、ckk:时钟信号;cnt、cnt1、cnt2、cnt3:计数值;dg1、dg11、dg12、dg13:数字值;dg2、dg21、dg22、dg23、dq:数字值inv;iv1~iv9:反相器;lsta:锁存信号;n1~n9:中间节点;osck:基准时钟信号;pck1~pck9:多相时钟信号;sta、stp:信号;tck1、tck2、tck3:时钟信号;tm1~tm4:转变定时;xtal:振子;δt:时间差。

具体实施方式

[0026]

以下,对本实施方式进行说明。另外,以下说明的本实施方式并非不当地限定权利要求书中记载的内容。并且,在本实施方式中说明的结构并非全部都是必需的构成要件。

[0027]

1.电路装置

[0028]

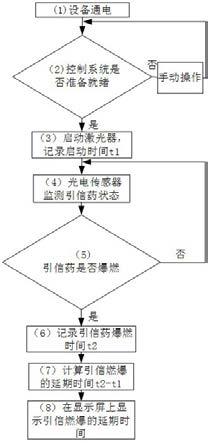

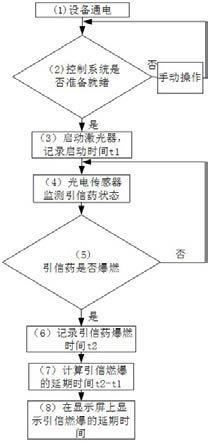

图1示出了本实施方式的电路装置10的结构例,图2示出了对本实施方式的动作进行说明的信号波形图。电路装置10包含时钟信号生成电路20、时间数字转换电路40以及处理电路80。

[0029]

时钟信号生成电路20生成多个多相时钟信号。例如,在图2中,作为多个多相时钟信号,生成了pck1、pck2、pck3、pck4、pck5、pc6、pck7、pck8、pck9。这些多相时钟信号pck1~pck9例如是频率相同且相位不同的时钟信号。并且,如图2所示,多相时钟信号pck1~pck9中的相邻的多相时钟信号的边沿间的相位差是相同的。例如,pck1的上升沿与pck2的下降沿之间的相位差和pck2的下降沿与pck3的上升沿之间的相位差是相同的。pck3的上升沿与

pck4的下降沿之间的相位差和pck4的下降沿与pck5的上升沿之间的相位差是相同的。pck6~pck9也同样如此。另外,在图2中,多相时钟信号的信号数为9,但并不限于此,信号数也可以是8以下,还可以是10以上。

[0030]

时钟信号生成电路20例如根据基准时钟信号osck来生成多相时钟信号pck1~pck9。基准时钟信号osck例如是如后述的图5所示那样通过使振子xtal进行振荡而生成的信号。并且,多相时钟信号pck1~pck9为相位与基准时钟信号osck同步的信号。例如,多相时钟信号pck1~pck9为将基准时钟信号osck的频率倍频后的频率的时钟信号。

[0031]

时间数字转换电路40进行基于与多个多相时钟信号pck1~pck9中的任意一个多相时钟信号对应的时钟信号cki的计数动作,求出与信号sta的转变定时tm1和信号stp的转变定时tm2的时间差δt对应的计数值cnt。时钟信号cki(i为1以上的整数)是第i时钟信号。时钟信号cki例如是基于多相时钟信号pck1~pck9中的任意一个多相时钟信号而生成的时钟信号。例如,时钟信号cki是对多相时钟信号pck1~pck9中的任意一个多相时钟信号的占空比进行调整后的时钟信号。例如,在图2中,时钟信号cki是与多相时钟信号pck7对应的时钟信号,是在多相时钟信号pck7的转变定时发生转变的信号。具体来说,时钟信号cki是对多相时钟信号pck7的占空比进行调整后的时钟信号,例如是占空比被调整成小于50%的时钟信号。另外,时钟信号cki也可以是多相时钟信号pck1~pck9中的任意一个多相时钟信号本身。

[0032]

信号sta是第1信号,例如是开始信号。信号stp是第2信号,例如是停止信号。转变定时tm1在图2中为信号sta的上升沿的定时,但也可以为下降沿的定时。转变定时tm2在图2中为信号stp的上升沿的定时,但也可以为下降沿的定时。计数值cnt是通过从信号sta的转变定时tm1到信号stp的转变定时tm2为止的期间内的计数动作而求出的值,与转变定时tm1、tm2之间的粗略(coarse)时间差对应。在图2中,作为转变定时tm1、tm2之间的粗略时间差,通过基于时钟信号cki的计数动作,求出了计数值cnt=3。

[0033]

例如,时间数字转换电路40包含计数电路42,该计数电路42根据时钟信号cki,从信号sta的转变定时tm1到信号stp的转变定时tm2进行计数动作,并输出计数值cnt。例如,计数电路42在信号sta的转变定时tm1启动计数动作而开始计数动作。然后,如图2所示,计数电路42在作为时钟信号cki的上升沿的转变定时处对计数值cnt进行更新。例如,使计数值以cnt=1、cnt=2、cnt3这一方式增加。然后,计数电路42在信号stp的转变定时tm2禁止计数动作而停止计数动作。这样,能够求出与从信号sta的转变定时tm1到信号stp的转变定时tm2为止的时间差δt对应的计数值cnt,能够进行时间差δt的粗略时间测量。

[0034]

并且,时间数字转换电路40求出从信号sta的转变定时tm1到与多个多相时钟信号pck1~pck9中的任意一个多相时钟信号对应的时钟信号ckj的转变定时tm3为止的时间差所对应的数字值dg1。即,求出与信号sta和时钟信号ckj的转变定时间的精确(fine)时间差对应的数字值dg1。数字值dg1是第1数字值。时钟信号ckj是第j时钟信号(j为1以上的整数)。例如,在图2中,时钟信号ckj是与多相时钟信号pck7对应的时钟信号,是多相时钟信号pck4的转变定时发生转变的信号。例如,时钟信号ckj是对多相时钟信号pck4的占空比进行调整后的时钟信号。另外,时钟信号ckj也可以是多相时钟信号pck1~pck9中的任意一个多相时钟信号本身。

[0035]

并且,时间数字转换电路40求出从信号stp的转变定时tm2到与多个多相时钟信号

pck1~pck9中的任意一个多相时钟信号对应的时钟信号ckk的转变定时tm4为止的时间差所对应的数字值dg2。即,求出与信号stp和时钟信号ckk的转变定时间的精确时间差对应的数字值dg2。数字值dg2是第2数字值。时钟信号ckk是第k时钟信号(k为1以上的整数)。例如,在图2中,时钟信号ckk是与多相时钟信号pck1对应的时钟信号,是在多相时钟信号pck1的转变定时发生转变的信号。例如,时钟信号ckk是对多相时钟信号pck1的占空比进行调整后的时钟信号。另外,时钟信号ckk也可以是多相时钟信号pck1~pck9中的任意一个多相时钟信号本身。

[0036]

然后,处理电路80根据计数值cnt和数字值dg1、dg2,求出与信号sta的转变定时tm1和信号stp的转变定时tm2的时间差δt对应的数字值dq。即,使用计数值cnt来进行时间差δt的粗略时间测量,根据数字值dg1、dg2来进行时间差δt的精确时间测量。例如关于时间差δt的大致长度,在从信号sta的转变定时tm1到信号stp的转变定时tm2为止的期间,利用通过进行基于时钟信号cki的计数动作而得到的计数值cnt来进行测量。然后,通过求出与信号sta的转变定时tm1和时钟信号ckj的转变定时tm3的时间差对应的数字值dg1、以及与信号stp的转变定时tm2和时钟信号ckk的转变定时tm4的时间差对应的数字值dg2,进行时间差δt的精确(fine)时间测量。例如如后述那样,通过使用了计数值cnt和数字值dg1、dg2的规定的运算处理来求出时间差δt。例如通过使用了作为未知的值的计数值cnt、数字值dg1、dg2以及已知的值的规定的运算式来求出时间差δt。

[0037]

图3是比较例的时间数字转换方法的说明图。在比较例的时间数字转换电路160中,在信号sta的转变定时处开始振荡电路162的振荡动作,从而生成振荡时钟信号cks。并且,在信号stp的转变定时处开始振荡电路164的振荡动作而生成频率比振荡时钟信号cks高的振荡时钟信号ckf。然后,处理电路166通过对振荡时钟信号cks的相位和振荡时钟信号ckf的相位进行比较,求出与信号sta和信号stp的转变定时的时间差δt对应的数字值dq。具体来说,处理电路166将通过在振荡时钟信号ckf的边沿超过振荡时钟信号cks的边沿之前的期间内的计数动作而得到的计数值作为与时间差δt对应的数字值dq来输出。由此,能够实现与振荡时钟信号ckf和振荡时钟信号cks的频率差对应的分辨率下的时间数字转换。

[0038]

但是,在该比较例的方法中,如果测量对象时间变长,则时间差δt变长,此时,使振荡电路162、164进行动作的时间会与时间差成比例地变长。因此,存在如下的问题:由于振荡电路162、164中的时钟抖动被分别积累,所以振荡时钟信号ckf的边沿超过振荡时钟信号cks的边沿的定时变得不稳定,从而时间数字转换的测量精度下降。

[0039]

关于该点,根据本实施方式,即使时间差δt变长,也可通过求出基于时钟信号cki的计数动作的计数值cnt来进行针对时间差δt的粗略时间测量。然后,通过求出与信号sta的转变定时tm1和时钟信号ckj的转变定时tm3的时间差对应的数字值dg1、以及与信号stp的转变定时tm2和时钟信号ckk的转变定时tm4的时间差对应的数字值dg2,进行针对时间差δt的精确时间测量。例如,如后述的图6等那样,按照与振荡时钟信号的频率差对应的分辨率,求出与转变定时tm1、tm3之间的时间差对应的数字值dg1和与转变定时tm2、tm4之间的时间差对应的数字值dg2,由此能够高精度地测量时间差δt。因此,能够提供如下的电路装置10:即使时间差δt变长,也能够与之对应,从而能够抑制由于时钟抖动被积累而造成的时间数字转换的测量精度下降。

[0040]

另外,在图2中,以时钟信号cki、ckj、ckk分别为与多相时钟信号pck7、pck4、pck1

对应的时钟信号的情况为例来进行说明,但并不限于此。例如,时钟信号cki、ckj、ckk中的例如至少2个时钟信号也可以是相同的时钟信号。例如,将多相时钟信号pck1~pck9中的哪一个分配给时钟信号cki、ckj、ckk可以可变地设定,也可以固定地分配。例如,可以如后述那样根据信号sta的转变定时tm1处的多相时钟信号pck1~pck9的信号电平、信号stp的转变定时tm2处的多相时钟信号pck1~pck9的信号电平来决定将多相时钟信号pck1~pck9中的哪一个分配给时钟信号cki、时钟信号ckj或时钟信号ckk。例如,在图2中,信号sta的转变定时tm1处的多相时钟信号pck1~pck9的信号电平(电压电平)为与“011010101”对应的信号电平,根据该“011010101”的信息来决定将多相时钟信号pck1~pck9中的哪一个分配给时钟信号cki、时钟信号ckj或时钟信号ckk。并且,信号stp的转变定时tm2处的多相时钟信号pck1~pck9的信号电平为与“010101011”对应的信号电平,根据该“010101011”的信息来决定将多相时钟信号pck1~pck9中的哪一个分配给时钟信号cki、时钟信号ckj或时钟信号ckk。

[0041]

图4示出了时钟信号生成电路20的结构例。如图4所示,时钟信号生成电路20包含环形振荡电路22,该环形振荡电路22从多个中间节点n1~n9输出多个多相时钟信号pck1~pck9。并且,时钟信号生成电路20可以包含锁存电路24、26、占空比调整电路27、28、29。

[0042]

环形振荡电路22具有连接成环状的多个反相器iv1~iv9。即,作为延迟元件的反相器iv1~iv9被级联连接。作为最末级延迟元件的反相器iv9的输出被输入到作为第1级延迟元件的反相器iv1。并且,反相器iv1、iv2之间的节点是中间节点n1,从该中间节点n1输出多相时钟信号pck1。并且,反相器iv2、iv3之间的节点是中间节点n2,从该中间节点n2输出多相时钟信号pck2。同样,从iv3~iv9的相邻反相器间的中间节点n3~n9输出多相时钟信号pck3~pck9。

[0043]

锁存电路24是在信号sta的转变定时tm1对多相时钟信号pck1~pck9进行锁存的电路。由此,转变定时tm1处的多相时钟信号pck1~pck9的信号电平的信息作为锁存信号lsta[1:9]从锁存电路24输出。以图2为例,输出锁存信号lsta[1:9]=[011010101]。

[0044]

锁存电路26是在信号stp的转变定时tm2对多相时钟信号pck1~pck9进行锁存的电路。由此,转变定时tm2处的多相时钟信号pck1~pck9的信号电平的信息作为锁存信号lstp[1:9]从锁存电路26输出。以图2为例,输出锁存信号lstp[1:9]=[010101011]。

[0045]

占空比调整电路27被输入多相时钟信号pck1,并输出以多相时钟信号pck1的h电平的期间变短的方式被调整了占空比的时钟信号tck1。时钟信号tck1是第1时钟信号。占空比调整电路28被输入多相时钟信号pck7,并输出以多相时钟信号pck7的h电平的期间变短的方式被调整了占空比的时钟信号tck2。时钟信号tck2是第2时钟信号。占空比调整电路29被输入多相时钟信号pck4,并输出以多相时钟信号pck4的h电平的期间变短的方式被调整了占空比的时钟信号tck3。时钟信号tck3是第3时钟信号。

[0046]

通过如图4那样在时钟信号生成电路20中设置环形振荡电路22,能够从环形振荡电路22的中间节点n1~n9输出频率相同且相位不同的多个多相时钟信号pck1~pck9。并且,使用与这些多相时钟信号pck1~pck9中的任意一个多相时钟信号对应的时钟信号cki、ckj、ckk来求出计数值cnt、数字值dg1、dg2,从而能够高精度地测量信号sta、信号stp的转变定时的时间差δt。

[0047]

图5示出了时钟信号生成电路20的详细结构例。图5的时钟信号生成电路20包含

pll电路30,该pll电路30设置有环形振荡电路22来作为压控振荡电路(vco),生成与使用振子xtal生成的基准时钟信号osck的相位同步的多个多相时钟信号pck1~pck9。即,pll电路30与基准时钟信号osck的相位同步地生成将基准时钟信号osck的频率倍频后的频率的多相时钟信号pck1~pck9。

[0048]

振荡电路38使振子xtal进行振荡而生成基准时钟信号osck。振荡电路38包括设置在连接振子xtal的第1振子用端子与第2振子用端子之间的振荡用的驱动电路等。例如,振荡电路38能够由实现驱动电路的双极晶体管等晶体管、和电容器或电阻等有源元件实现。作为振荡电路38,例如可以使用皮尔斯型、考毕兹型、反相器型或哈特利型等各种类型的振荡电路。

[0049]

振子xtal是通过电信号产生机械振动的元件。振子xtal例如能够由石英振动片等振动片实现。例如,振子xtal能够由切角为at切或sc切等进行厚度剪切振动的石英振动片等实现。另外,本实施方式的振子xtal例如能够由厚度剪切振动型以外的振动片、由石英以外的材料形成的压电振动片等各种振动片实现。例如,作为振子xtal,也可以采用saw(surface acoustic wave:表面声波)谐振器、使用硅基板形成的作为硅制振子的mems(micro electro mechanical systems:微机电系统)振子等。

[0050]

pll电路30被输入来自振荡电路38的基准时钟信号osck来作为输入时钟信号,从而进行pll(phase locked loop:锁相环)的动作。例如,pll电路30生成将基准时钟信号osck的频率倍频后的频率的输出时钟信号plck。即,生成与基准时钟信号osck的相位同步的高精度的输出时钟信号plck。pll电路30包含相位比较电路31、控制电压生成电路32、作为压控振荡电路(vco)的环形振荡电路22以及分频电路36。

[0051]

相位比较电路31进行基准时钟信号osck与反馈时钟信号fbck之间的相位比较。例如,相位比较电路31对基准时钟信号osck和反馈时钟信号fbck的相位进行比较,将与基准时钟信号osck和反馈时钟信号fbck的相位差对应的信号cq作为相位比较结果信号来输出。与相位差对应的信号cq例如是与相位差成比例的脉冲宽度的脉冲信号。

[0052]

控制电压生成电路32根据相位比较电路31中的相位比较的结果来生成控制电压vc。例如,控制电压生成电路32根据来自相位比较电路31的相位比较结果信号cq,通过电荷泵电路33进行电荷泵动作,并且通过低通滤波器进行滤波处理,从而生成对环形振荡电路22的振荡进行控制的控制电压vc。

[0053]

环形振荡电路22生成与控制电压vc对应的频率的输出时钟信号plck。例如,将图4的多相时钟信号pck9作为输出时钟信号plck来输出。作为基于控制电压vc的输出时钟信号plck的频率的控制方法,可想到各种方法。例如,在图4中,也可以在iv1~iv9的各反相器的输出节点处设置变容二极管等可变电容元件,使该可变电容元件的电容基于控制电压vc发生变化,从而对输出时钟信号plck的频率进行控制。或者,也可以在iv1~iv9的各反相器设置流过驱动电流的电流源,根据控制电压vc对该驱动电流进行控制,从而对输出时钟信号plck的频率进行控制。

[0054]

分频电路36对输出时钟信号plck进行分频而输出反馈时钟信号fbck。例如,分频电路36将按照由分频比设定数据设定的分频比对输出时钟信号plck的频率进行分频而得的频率的信号作为反馈时钟信号fbck而输出到相位比较电路31。由此,能够将作为输出时钟信号plck的频率的多相时钟信号pck1~pck9的频率设定为将基准时钟信号osck的频率

倍频后的频率。另外,振子xtal的振荡频率例如是10mhz~150mhz左右,分频电路36的分频比例如是2分频~64分频左右。

[0055]

这样,通过对时钟信号生成电路20设置图5所示的pll电路30,能够生成与基准时钟信号osck同步的多相时钟信号pck1~pck9,并且能够将多相时钟信号pck1~pck9的频率设定为将基准时钟信号osck的频率倍频后的频率。并且,基准时钟信号osck例如是通过使振子xtal进行振荡而生成的时钟信号,因此能够使其频率为高精度,还能够使多相时钟信号pck1~pck9的频率为高精度。通过这样使多相时钟信号pck1~pck9的频率为高精度,可实现时间数字转换的高精度化。

[0056]

图6示出了时间数字转换电路40的结构例。时间数字转换电路40包含开始用振荡电路50、振荡电路51、停止用振荡电路60、振荡电路61、时间数字转换器55、65。还可以包含计数电路42。

[0057]

开始用振荡电路50在作为第1信号的信号sta的转变定时处开始振荡,生成振荡时钟信号cksa。开始用振荡电路50是第1信号用振荡电路,振荡时钟信号cksa是第1信号用振荡时钟信号。振荡电路51在作为第j时钟信号的时钟信号ckj的转变定时处开始振荡,生成频率与振荡时钟信号cksa不同的振荡时钟信号ckfj。振荡时钟信号ckfj是第j振荡时钟信号,是频率比振荡时钟信号cksa高的时钟信号。开始用振荡电路50、振荡电路51例如能够通过环形振荡电路等实现。

[0058]

然后,时间数字转换器55根据振荡时钟信号cksa和振荡时钟信号ckfj来输出数字值dg1。时间数字转换器55是第1时间数字转换器,数字值dg1是第1数字值。例如,时间数字转换器55通过对振荡时钟信号cksa的相位和振荡时钟信号ckfj的相位进行比较,求出与信号sta和时钟信号ckj的转变定时的时间差对应的数字值dg1并输出。即,求出与图2所示的转变定时tm1、tm3的时间差对应的数字值dg1。具体来说,时间数字转换器55将通过在振荡时钟信号ckfj的边沿超过振荡时钟信号cksa的边沿之前的期间内的计数动作而得到的计数值作为数字值dg1来输出。

[0059]

停止用振荡电路60在作为第2信号的信号stp的转变定时处开始振荡,生成振荡时钟信号cksp。停止用振荡电路60是第2信号用振荡电路,振荡时钟信号cksp是第2信号用振荡时钟信号。振荡电路61在作为第k时钟信号的时钟信号ckk的转变定时处开始振荡,生成频率与振荡时钟信号cksp不同的振荡时钟信号ckfk。振荡时钟信号ckfk是第k振荡时钟信号,是频率比振荡时钟信号cksp高的时钟信号。停止用振荡电路60、振荡电路61例如可以由环形振荡电路等实现。

[0060]

然后,时间数字转换器65根据振荡时钟信号cksp和振荡时钟信号ckfk来输出数字值dg2。时间数字转换器65是第2时间数字转换器,数字值dg2是第2数字值。例如,时间数字转换器65通过对振荡时钟信号cksp的相位和振荡时钟信号ckfk的相位进行比较,求出与信号stp和时钟信号ckk的转变定时的时间差对应的数字值dg2并输出。即,求出与图2所示的转变定时tm2、tm4的时间差对应的数字值dg2。具体来说,时间数字转换器65将通过在振荡时钟信号ckfk的边沿超过振荡时钟信号cksp的边沿之前的期间内的计数动作而得到的计数值作为数字值dg2来输出。

[0061]

然后,处理电路80根据来自计数电路42的计数值cnt和来自时间数字转换器55、65的数字值dg1、dg2,求出与图2的信号sta、信号stp的转变定时tm1、tm2的时间差δt对应的

数字值dq并输出。

[0062]

根据图6的结构的时间数字转换电路40,能够按照开始用振荡电路50的振荡时钟信号cksa与振荡电路51的振荡时钟信号ckfj的频率差所对应的分辨率,测量信号sta与时钟信号ckj的转变定时tm1、tm3的时间差并作为数字值dg1来输出。并且,能够按照停止用振荡电路60的振荡时钟信号cksp与振荡电路61的振荡时钟信号ckfk的频率差所对应的分辨率来测量信号stp与时钟信号ckk的转变定时tm2、tm4的时间差并作为数字值dg2来输出。因此,能够实现时间数字转换电路40的时间测量的高精度化。

[0063]

2.详细结构例

[0064]

图7示出了本实施方式的电路装置10的详细结构例。图7的电路装置10包含时钟信号生成电路20、时间数字转换电路40以及处理电路80。另外,电路装置10并不限于图7的结构,能够实施省略其中一部分结构要素或追加其他结构要素等各种变形。

[0065]

如图4所说明的那样,时钟信号生成电路20输出与pck1~pck9中的多相时钟信号pck1对应的时钟信号tck1、与多相时钟信号pck7对应的时钟信号tck2以及与多相时钟信号pck4对应的时钟信号tck3。多相时钟信号pck1是第1多相时钟信号,时钟信号tck1是第1时钟信号。多相时钟信号pck7是第2多相时钟信号,时钟信号tck2是第2时钟信号。多相时钟信号pck4是第3多相时钟信号,时钟信号tck3是第3时钟信号。并且,图1、图2、图6所说明的时钟信号cki、ckj、ckk分别是时钟信号tck1、tck2、tck3中的任意一个时钟信号。由此,时间数字转换电路40能够使用时钟信号生成电路20所输出的时钟信号tck1、tck2、tck3来输出计数值cnt、数字值dg1、dg2。

[0066]

如图7所示,时间数字转换电路40包含开始用振荡电路50、振荡电路52、53、54以及时间数字转换器56、57、58。开始用振荡电路50是第1信号用振荡电路,振荡电路52、53、54分别是第1振荡电路、第2振荡电路、第3振荡电路。它们是环形振荡电路。时间数字转换器56、57、58分别是第1时间数字转换器、第2时间数字转换器、第3时间数字转换器。

[0067]

开始用振荡电路50在信号sta的转变定时处开始振荡,生成作为第1信号用振荡时钟信号的振荡时钟信号cksa。

[0068]

振荡电路52在作为第1时钟信号的时钟信号tck1的转变定时处开始振荡,生成频率与振荡时钟信号cksa不同的振荡时钟信号ckf1。振荡时钟信号ckf1是第1振荡时钟信号,频率比振荡时钟信号cksa高。例如,在振荡时钟信号cksa的频率是500mhz的情况下,振荡时钟信号ckf1的频率成为例如501mhz这样稍高的频率。

[0069]

振荡电路53在作为第2时钟信号的时钟信号tck2的转变定时处开始振荡,生成频率与振荡时钟信号cksa不同的振荡时钟信号ckf2。振荡时钟信号ckf2是第2振荡时钟信号,频率比振荡时钟信号cksa高。

[0070]

振荡电路54在作为第3时钟信号的时钟信号tck3的转变定时处开始振荡,生成频率与振荡时钟信号cksa不同的振荡时钟信号ckf3。振荡时钟信号ckf3是第3振荡时钟信号,频率比振荡时钟信号cksa高。

[0071]

时间数字转换器56根据振荡时钟信号cksa和振荡时钟信号ckf1来输出数字值dg11。数字值dg11是第1信号用第1数字值。例如,时间数字转换器56通过对振荡时钟信号cksa的相位和振荡时钟信号ckf1的相位进行比较,求出与信号sta和振荡时钟信号ckf1的转变定时的时间差对应的数字值dg11并输出。

[0072]

时间数字转换器57根据振荡时钟信号cksa和振荡时钟信号ckf2来输出数字值dg12。数字值dg12是第1信号用第2数字值。例如,时间数字转换器57通过对振荡时钟信号cksa的相位和振荡时钟信号ckf2的相位进行比较,求出与信号sta和振荡时钟信号ckf2的转变定时的时间差对应的数字值dg12并输出。

[0073]

时间数字转换器58根据振荡时钟信号cksa和振荡时钟信号ckf3来输出数字值dg13。数字值dg13是第1信号用第3数字值。例如,时间数字转换器58通过对振荡时钟信号cksa的相位和振荡时钟信号ckf3的相位进行比较,求出与信号sta和振荡时钟信号ckf3的转变定时的时间差对应的数字值dg13并输出。

[0074]

然后,处理电路80使用数字值dg11、dg12、dg13中的任意一个数字值作为图1、图2所说明的数字值dg1。这样,能够选择时钟信号tck1、tck2、tck3中的适合测量与信号sta的转变定时的时间差的时钟信号,从而测量该时间差。例如,在信号sta与时钟信号tck1的转变定时的时间差最小的情况下,处理电路80选择与时钟信号tck1对应的数字值dg11来作为表示与信号sta的转变定时的时间差的数字值dg1。同样,在信号sta与时钟信号tck2的转变定时的时间差最小的情况下,处理电路80选择与时钟信号tck2对应的数字值dg12并作为数字值dg1来使用。并且,在信号sta与时钟信号tck3的转变定时的时间差最小的情况下,选择与时钟信号tck3对应的数字值dg13并作为数字值dg1来使用。

[0075]

例如,处理电路80根据信号sta的转变定时处的多个多相时钟信号pck1~pck9的信号电平,决定使用数字值dg11、dg12、dg13中的哪一个数字值来作为数字值dg1。这样,通过对信号sta的转变定时处的多相时钟信号pck1~pck9的信号电平进行监视,能够选择时钟信号tck1、tck2、tck3中的适合测量与信号sta的转变定时的时间差的时钟信号,从而能够测量该时间差。另外,在后述的图11~图14对时钟信号的选择方法进行详细说明。

[0076]

并且,如图7所示,时间数字转换电路40包含停止用振荡电路60、振荡电路62、63、64、时间数字转换器66、67、68。停止用振荡电路60是第2信号用振荡电路,振荡电路62、63、64分别是第4振荡电路、第5振荡电路、第6振荡电路。它们是环形振荡电路。并且,时间数字转换器66、67、68分别是第4时间数字转换器、第5时间数字转换器、第6时间数字转换器。

[0077]

停止用振荡电路60在信号stp的转变定时处开始振荡,生成作为第2信号用振荡时钟信号的振荡时钟信号cksp。

[0078]

振荡电路62在时钟信号tck1的转变定时处开始振荡,生成频率与振荡时钟信号cksp不同的振荡时钟信号ckf4。振荡时钟信号ckf4是第4振荡时钟信号,频率比振荡时钟信号cksp高。振荡电路63在时钟信号tck2的转变定时处开始振荡,生成频率与振荡时钟信号cksp不同的振荡时钟信号ckf5。振荡时钟信号ckf5是第5振荡时钟信号,频率比振荡时钟信号cksp高。振荡电路64在时钟信号tck3的转变定时处开始振荡,生成频率与振荡时钟信号cksp不同的振荡时钟信号ckf6。振荡时钟信号ckf6是第6振荡时钟信号,频率比振荡时钟信号cksp高。

[0079]

时间数字转换器66根据振荡时钟信号cksp和振荡时钟信号ckf4来输出数字值dg21。数字值dg21是第2信号用第1数字值。时间数字转换器67根据振荡时钟信号cksp和振荡时钟信号ckf5来输出数字值dg22。数字值dg22是第2信号用第2数字值。时间数字转换器68根据振荡时钟信号cksp和振荡时钟信号ckf6来输出数字值dg23。数字值dg23是第2信号用第3数字值。

[0080]

然后,处理电路80使用数字值dg21、dg22、dg23中的任意一个数字值来作为图1、图2所说明的数字值dg2。这样,能够选择时钟信号tck1、tck2、tck3中的适合测量与信号stp的转变定时的时间差的时钟信号并求出该时间差。例如,在信号stp与时钟信号tck1的转变定时的时间差最小的情况下,处理电路80选择与时钟信号tck1对应的数字值dg21并作为表示与信号stp的转变定时的时间差的数字值dg2来使用。同样,在信号stp与时钟信号tck2的转变定时的时间差最小的情况下,处理电路80选择与时钟信号tck2对应的数字值dg22并作为数字值dg2来使用。并且,在信号stp与时钟信号tck3的转变定时的时间差最小的情况下,选择与时钟信号tck3对应的数字值dg23并作为数字值dg2来使用。

[0081]

例如,处理电路80根据信号stp的转变定时处的多个多相时钟信号pck1~pck9的信号电平,决定使用数字值dg21、dg22、dg23中哪一个数字值来作为数字值dg2。这样,通过对信号stp的转变定时处的多相时钟信号pck1~pck9的信号电平进行监视,能够选择时钟信号tck1、tck2、tck3中的适合测量与信号stp的转变定时的时间差的时钟信号并测量该时间差。

[0082]

图8是对使用振荡时钟信号cksa、ckf1的频率差来测量信号sta与时钟信号tck1的转变定时的时间差的处理进行说明的信号波形图。如图8的b1所示,生成振荡时钟信号cksa的开始用振荡电路50在信号sta的转变定时处开始振荡。并且,如b2所示,生成振荡时钟信号ckf1的振荡电路52在时钟信号tck1的转变定时处开始振荡。在该情况下,振荡时钟信号ckf1的频率比振荡时钟信号cksa的频率高,因此,在b3、b4中,振荡时钟信号ckf1的上升沿超过振荡时钟信号cksa的上升沿而变化为h电平。然后,通过以这种方式对振荡时钟信号ckf1的上升沿超过之前的时钟数进行计数,能够按照与振荡时钟信号cksa、ckf1的频率差对应的分辨率对信号sta与时钟信号tck1的转变定时的时间差进行测量。信号sta与时钟信号tck2、tck3的转变定时的时间差也能够同样地进行测量。

[0083]

图9是对利用振荡时钟信号cksp、ckf1的频率差来测量信号stp与时钟信号tck1的转变定时的时间差的处理进行说明的信号波形图。如图9的b5所示,生成振荡时钟信号cksp的停止用振荡电路60在信号stp的转变定时处开始振荡。并且,如b6所示,生成振荡时钟信号ckf4的振荡电路62在时钟信号tck1的转变定时处开始振荡。在该情况下,振荡时钟信号ckf4的频率比振荡时钟信号cksp的频率高,因此,在b7、b9中,振荡时钟信号ckf4的上升沿超过振荡时钟信号cksp的上升沿而变化为h电平。然后,通过以这种方式对振荡时钟信号ckf4的上升沿超过之前的时钟数进行计数,能够按照与振荡时钟信号cksp、ckf4的频率差对应的分辨率对信号stp与时钟信号tck1的转变定时的时间差进行测量。信号stp与时钟信号tck2、tck3的转变定时的时间差也能够同样地进行测量。

[0084]

另外,如上述专利文献1那样,优选设置调整电路,该调整电路对振荡时钟信号cksa、cksp、ckf1~ckf6的频率进行测量而将该频率调整为目标频率。例如,通过调整电路对作为环形振荡电路的开始用振荡电路50、停止用振荡电路60、振荡电路52、53、54、62、63、64的延迟元件的延迟时间进行调整。这样,可实现时间差的测量的高精度化。

[0085]

图10示出了计数电路42的结构例。计数电路42包含计数器43、44、45。并且,计数电路42可以包含and电路an1、an2、an3、an4以及反相器inv。计数器43是第1计数器,计数器44是第2计数器,计数器45是第3计数器。

[0086]

计数器43根据时钟信号tck1,从信号sta的转变定时到信号stp的转变定时进行计

数动作,并输出计数值cnt1。计数值cnt1是第1计数值。计数器44根据时钟信号tck2,从信号sta的转变定时到信号stp的转变定时进行计数动作,并输出计数值cnt2。计数值cnt2是第2计数值。计数器45根据时钟信号tck3,从信号sta的转变定时到信号stp的转变定时进行计数动作,并输出计数值cnt3。计数值cnt3是第3计数值。即,在信号sta是h电平并且信号stp是l电平的期间内,and电路an1的输出为h电平,经由and电路an1、an2、an3向计数器43、44、45输入时钟信号tck1、tck2、tck3。由此,在信号sta从l电平转变为h电平的定时到信号stp从l电平转变为h电平的定时为止的期间内,计数器43、44、45分别根据时钟信号tck1、tck2、tck3来进行计数动作。然后,作为计数结果的计数值cnt1、cnt2、cnt3被输出到处理电路80。由此,能够将通过时钟信号tck1、tck2、tck3的计数动作以粗略分辨率对信号sta与信号stp的转变定时的时间差进行测量而得的结果作为计数值cnt1、cnt2、cnt3而输出到处理电路80。

[0087]

然后,处理电路80使用计数值cnt1、cnt2、cnt3中的任意一个计数值来作为在图1、图2中说明的计数值cnt。这样,能够选择时钟信号tck1、tck2、tck3中的适合测量信号sta与信号stp的时间差的计数处理的时钟信号并测量该时间差。例如,当信号sta或信号stp的转变定时与时钟信号的转变定时一致时,计数值偏移1个时钟,会产生误差。关于该点,根据图10的计数电路42的结构,能够从时钟信号tck1、tck2、tck3中选择与信号sta或信号stp的转变定时不一致的时钟信号,并将基于该时钟信号的计数值用作表示信号sta与信号stp的转变定时的时间差的计数值cnt。

[0088]

例如,处理电路80根据信号sta的转变定时处的多个多相时钟信号pck1~pck9的信号电平,决定使用计数值cnt1、cnt2、cnt3中的哪一个计数值来作为计数值cnt。这样,通过对信号sta的转变定时处的多相时钟信号pck1~pck9的信号电平进行监视,能够选择时钟信号tck1、tck2、tck3中的适合测量信号sta与信号stp的转变定时的时间差的计数处理的时钟信号并测量该时间差。

[0089]

图11是对本实施方式的详细动作例进行说明的信号波形图。在图11中,对信号sta的转变定时tm1与信号stp的转变定时tm2的时间差δt进行测量。如图11所示,图10的计数器43、44、45根据时钟信号tck1、tck2、tck3来进行计数值cnt1、cnt2、cnt3的计数动作。然后,作为时间差δt的粗略的测量结果,处理电路80根据信号sta的转变定时tm1处的多相时钟信号pck1~pck9的信号电平的信息“011010101”来选择基于时钟信号tck1的计数值cnt1。即,测量出时间差δt的粗略的测量结果是cnt1=3。

[0090]

并且,在图11中,dgt1、dgt2、dgt3分别是与时钟信号tck1、tck2、tck3的周期对应的数字值,是已知的值。dg11、dg12、dg13分别是与信号sta和时钟信号tck1、tck2、tck3的转变定时的时间差对应的数字值,如图7所示那样通过时间数字转换器56、57、58来求出。dg21、dg22、dg23分别是与信号stp和时钟信号tck1、tck2、tck3的转变定时的时间差对应的数字值,如图7所示那样通过时间数字转换器66、67、68来求出。然后,处理电路80例如基于下述的式(1)来求出时间差δt。

[0091]

δt=cnt1

×

rslc (dg13-dg21)

×

rslf dgt3

ꢀꢀꢀ

(1)

[0092]

在上式(1)中,rslc是时间测量的粗略分辨率,是与时钟信号tck1、tck2、tck3的频率对应的分辨率。例如,在时钟信号tck1、tck2、tck3的频率为fc=500mhz的情况下,rscl=1/fs=2ns。rslf是时间测量的精确的分辨率,例如在将振荡时钟信号ckf1~ckf6的频率设

为f1,将振荡时钟信号cksa、cksp的频率设为f2的情况下,能够表示为rslf=(f1-f2)/f1

×

f2。

[0093]

并且,在上式(1)中,dgt3是已知的值,因此能够通过测量计数值cnt1、数字值dg13、dg21来求出时间差δt。并且,在图11中,cnt1是基于时钟信号tck1的计数值,是图10的计数器43的计数值。dg13是信号sta与时钟信号tck3的转变定时的时间差所对应的数字值,通过图7的开始用振荡电路50、振荡电路54、时间数字转换器58来测量。该数字值dg13与图2的数字值dg1对应。dg21是与信号stp和时钟信号tck1的转变定时的时间差对应的数字值,通过图7的停止用振荡电路60、振荡电路62、时间数字转换器66来测量。该数字值dg21与图2的数字值dg2对应。

[0094]

这样,在本实施方式中,关于时间差δt的粗略的测量值,通过时钟信号tck1、tck2、tck3中的任意一个时钟信号的计数动作的计数值来测量。在图11中,通过时钟信号tck1的计数值cnt1来求出时间差δt的粗略的测量值。具体来说,例如根据信号sta的转变定时处的多相时钟信号pck1~pck9的信号电平的信息即“011010101”,从计数值cnt1~cnt3中选择计数值cnt1。

[0095]

另一方面,关于时间差δt的精确的测量值,通过信号sta与时钟信号tck1、tck2、tck3中的任意一个时钟信号的转变定时的时间差和信号stp与时钟信号tck1、tck2、ck3中的任意一个时钟信号的转变定时的时间差来测量。在图11中,通过与信号sta和时钟信号tck3的转变定时的时间差对应的数字值dg13、以及与信号stp和时钟信号tck1的转变定时的时间差对应的数字值dg21来求出时间差δt的精确的测量值。具体来说,根据信号sta的转变定时处的多相时钟信号pck1~pck9的信号电平的信息即“011010101”,判定为与信号sta的转变定时最近的转变定时的时钟信号是tck3,从而选择与时钟信号tck3对应的数字值dg13。并且,根据信号stp的转变定时处的多相时钟信号pck1~pck9的信号电平的信息即“010101011”,判定为与信号stp的转变定时最近的转变定时的时钟信号是tck1,从而选择与时钟信号tck1对应的数字值dg21。通过这样选择与信号sta以及信号stp的转变定时最近的转变定时的时钟信号所对应的数字值,能够减小因振荡时钟信号的累积抖动而造成的不良影响,可实现时间数字转换的高精度化。

[0096]

图12是对本实施方式的详细的其他动作例进行说明的信号波形图。在图12中,作为时间差δt的粗略的测量结果,处理电路80根据信号sta的转变定时tm1处的多相时钟信号pck1~pck9的信号电平的信息“010101101”,选择基于时钟信号tck1的计数值cnt1。即,测量出时间差δt的粗略的测量结果是cnt1=2。然后,处理电路80例如基于下述的式(2)来求出时间差δt。

[0097]

δt=cnt1

×

rslc (dg11-dg22)

×

rslf dgt1

ꢀꢀꢀ

(2)

[0098]

在上式(2)中,dgt1是已知的值,因此能够通过测量计数值cnt1、数字值dg11、dg22来求出时间差δt。并且,在图12中,cnt1是基于时钟信号tck1的计数值,是图10的计数器43的计数值。dg11是与信号sta和时钟信号tck1的转变定时的时间差对应的数字值,通过图7的开始用振荡电路50、振荡电路52、时间数字转换器56来测量。该数字值dg11与图2的数字值dg1对应。dg22是与信号stp和时钟信号tck2的转变定时的时间差对应的数字值,通过图7的停止用振荡电路60、振荡电路63、时间数字转换器67来测量。该数字值dg22与图2的数字值dg2对应。

[0099]

这样,在图12中,时间差δt的粗略的测量值是通过时钟信号tck1的计数值cnt1求出的。具体来说,例如根据信号sta的转变定时处的多相时钟信号pck1~pck9的信号电平的信息即“010101101”,从计数值cnt1~cnt3中选择计数值cnt1。

[0100]

另一方面,时间差δt的精确的测量值是通过与信号sta和时钟信号tck1的转变定时的时间差对应的数字值dg11、以及与信号stp和时钟信号tck2的转变定时的时间差对应的数字值dg22来求出的。具体来说,根据信号sta的转变定时处的多相时钟信号pck1~pck9的信号电平的信息即“010101101”,判定为与信号sta的转变定时最近的转变定时的时钟信号是tck1,从而选择与时钟信号tck1对应的数字值dg11。并且,根据信号stp的转变定时处的多相时钟信号pck1~pck9的信号电平的信息即“101010010”,判定为与信号stp的转变定时最近的转变定时的时钟信号是tck2,从而选择与时钟信号tck2对应的数字值dg22。通过这样选择与信号sta以及信号stp的转变定时最近的转变定时的时钟信号所对应的数字值,能够减小由于振荡时钟信号的累积抖动而造成的不良影响,可实现时间数字转换的高精度化。

[0101]

图13、图14是针对时钟信号的选择方法的说明图。这里,对求出时间差δt的粗略测量值时的时钟信号的选择方法进行说明。在图13、图14中,[1]、[2]、[3]

····

[9]例如与信号sta的转变定时处的多相时钟信号pck1~pck9的信号电平对应,例如是图4的锁存电路24所输出的锁存信号lsta[1:9]。如图11、图12所示,在第偶数个多相时钟信号中,信号电平相对于第奇数个多相时钟信号反转。因此,为了容易理解说明,在图14中,使与第偶数个多相时钟信号对应的锁存信号lsta[1:9]的逻辑电平反转。

[0102]

例如,图13、图14的编号12是信号sta在多相时钟信号pck2的上升沿与多相时钟信号pck3的下降沿之间发生转变的情况。在该情况下,从图11、图12可知,通过选择与多相时钟信号pck1对应的时钟信号tck1,信号sta和时钟信号tck1的转变定时不会重叠,因此能够实现适当的计数动作。同样,在编号13、编号14、编号15、编号16、编号17的情况下,也选择时钟信号tck1。例如,编号17是信号sta在多相时钟信号pck7的下降沿与多相时钟信号pck8的上升沿之间发生转变的情况,但通过使用与多相时钟信号pck1对应的时钟信号tck1,能够实现适当的计数动作。

[0103]

并且,图13、图14的编号0是信号sta在多相时钟信号pck8的上升沿与多相时钟信号pck9的下降沿之间发生转变的情况。在该情况下,从图11、图12可知,通过选择与多相时钟信号pck7对应的时钟信号tck2,能够实现适当的计数动作。同样,在编号1、编号2、编号3、编号4、编号5的情况下,也选择时钟信号tck2。例如,编号5是信号sta在多相时钟信号pck4的下降沿与多相时钟信号pck5的上升沿之间发生转变的情况,但通过使用与多相时钟信号pck7对应的时钟信号tck2,能够实现适当的计数动作。

[0104]

并且,图13、图14的编号6是信号sta在多相时钟信号pck5的上升沿与多相时钟信号pck6的下降沿之间发生转变的情况。在该情况下,从图11、图12可知,通过选择与多相时钟信号pck4对应的时钟信号tck3,能够实现适当的计数动作。同样,在编号7、编号8、编号9、编号10、编号11的情况下也选择时钟信号tck3。例如,编号11是信号sta在多相时钟信号pck1的下降沿与多相时钟信号pck2的上升沿之间发生转变的情况,但通过使用与多相时钟信号pck4对应的时钟信号tck3,能够实现适当的计数动作。

[0105]

通过如以上那样对信号sta的转变定时处的多相时钟信号pck1~pck9的信号电平

进行监视,能够选择适合于计数值的计数动作的时钟信号。同样,通过对信号sta以及信号stp的转变定时处的多相时钟信号pck1~pck9的信号电平进行监视,能够选择在与信号sta以及信号stp的转变定时最近的转变定时处发生变化的时钟信号。

[0106]

3.物理量测量装置、电子设备、移动体

[0107]

图15示出了本实施方式的物理量测量装置400的结构例。物理量测量装置400包含本实施方式的电路装置10和进行基于来自电路装置10的数字值dq的处理的处理装置430。电路装置10与用于生成作为时间数字转换基准的时钟信号的振子xtal连接。处理装置430根据来自电路装置10的时间数字转换结果即数字值dq来执行使用了时间数字转换的各种处理。并且,物理量测量装置400可以包含发光部410和接收来自对象物的反射光的受光部420。发光部410是作为光源的部件,受光部420是受光传感器。处理装置430由cpu等处理器或存储器实现,向发光部410输出发光控制信号psta。

[0108]

发光部410根据来自处理装置430的发光控制信号psta而发光,发光控制信号psta作为信号sta而被输入到电路装置10,受光部420的受光信号作为信号stp而被输入到电路装置10。这样,能够实现测量到对象物的距离来作为物理量的tof方式的距离测量装置。另外,发光控制信号psta也可以是从物理量测量装置400的外部输入的信号。

[0109]

图16示出了本实施方式的电子设备500的结构例。该电子设备500包含本实施方式的电路装置10、和进行基于来自电路装置10的数字值dq的处理的处理装置520。电路装置10与用于生成作为时间数字转换基准的时钟信号的振子xtal连接。处理装置520根据来自电路装置10的时间数字转换结果即数字值dq,执行使用了时间数字转换的各种处理。并且,电子设备500可以包含通信接口510、操作界面530、显示部540、存储器550、天线ant。

[0110]

电子设备500例如是计测距离、时间、流速或流量等物理量的计测设备、测量生物体信息的生物体信息测量设备、车载设备、基站或路由器等网络相关设备。生物体信息测量设备例如是超声波测量装置、脉搏计或血压测量装置等。车载设备例如是自动驾驶用的设备等。并且,电子设备500也可以是头部佩戴型显示装置、钟表相关设备等可穿戴设备、机器人、打印装置、投影装置、智能手机等便携信息终端、分发内容的内容提供设备、数码相机或摄像机等影像设备等。

[0111]

通信接口510进行经由天线ant从外部接收数据或者向外部发送数据的处理。处理装置520进行电子设备500的控制处理、经由通信接口510收发的数据的各种数字处理等。处理装置520的功能例如能够由微型计算机等处理器实现。操作界面530用于供用户进行输入操作,能够由操作按钮或触摸面板显示器等实现。显示部540显示各种信息,能够由液晶或有机el等显示器实现。存储器550存储数据,其功能能够由ram或rom等半导体存储器实现。

[0112]

图17示出了包含本实施方式的电路装置10的移动体的例子。移动体包含电路装置10和根据来自电路装置10的数字值dq进行处理的处理装置220。处理装置220根据来自电路装置10的时间数字转换结果即数字值dq来执行使用了时间数字转换的各种处理。例如,执行自动驾驶用的处理等。本实施方式的电路装置10例如能够组装到汽车、飞机、摩托车、自行车、机器人或船舶等各种移动体中。移动体例如是具有发动机、马达等驱动机构、方向盘或舵等转向机构、车载设备等各种电子设备并在地上、天空或海上移动的设备/装置。图17概略地示出了作为移动体的具体例的汽车206。在汽车206中组装有包含本实施方式的电路装置10的控制装置208。控制装置208根据利用电路装置10的时间数字转换得到的物理量信

息来进行各种控制处理。例如,作为物理量信息,在测量了汽车206周围的物体的距离信息的情况下,控制装置208使用测量出的距离信息来进行用于自动驾驶的各种控制处理。控制装置208例如根据车体207的姿势来控制悬架的软硬或各个车轮209的制动。另外,组装了本实施方式的电路装置10的设备并不限于这样的控制装置208,能够组装到设置于汽车206或机器人等移动体的各种设备中。

[0113]

如以上说明的那样,本实施方式的电路装置包含时钟信号生成电路,该时钟信号生成电路生成频率相同且相位不同的多个多相时钟信号。并且,还包含:时间数字转换电路,其进行基于与多个多相时钟信号中的任意一个多相时钟信号对应的第i时钟信号的计数动作,求出与第1信号的转变定时和第2信号的转变定时的时间差对应的计数值,求出第1数字值并求出第2数字值,所述第1数字值对应于从第1信号的转变定时到与多个多相时钟信号中的任意一个多相时钟信号对应的第j时钟信号的转变定时为止的时间差,所述第2数字值对应于从第2信号的转变定时到与多个多相时钟信号中的任意一个多相时钟信号对应的第k时钟信号的转变定时为止的时间差;以及处理电路,其根据计数值、第1数字值和第2数字值,求出与第1信号的转变定时和第2信号的转变定时的时间差对应的数字值。

[0114]

根据本实施方式,生成频率相同且相位不同的多个多相时钟信号。然后,进行基于第i时钟信号的计数动作而求出与第1信号和第2信号的转变定时的时间差对应的计数值。并且,求出与从第1信号的转变定时到第j时钟信号的转变定时为止的时间差对应的第1数字值,并求出与从第2信号的转变定时到第k时钟信号的转变定时为止的时间差对应的第2数字值。然后,根据所求出的计数值、第1数字值、第2数字值,求出与第1信号的转变定时和第2信号的转变定时的时间差对应的数字值。这样,通过求出第i时钟信号的计数动作的计数值而进行针对时间差的粗略时间测量,并求出与第1信号和第j时钟信号的转变定时的时间差对应的第1数字值、以及与第2信号和第k时钟信号的转变定时的时间差对应的第2数字值,从而进行针对时间差的精确时间测量。因此,在第1信号与第2信号的转变定时的时间差变长的情况下,也能够与之对应,从而能够提供可抑制由于时钟抖动被积累而造成的时间数字转换的测量精度下降的电路装置。

[0115]

并且,在本实施方式中,也可以是,时间数字转换电路包含计数电路,该计数电路根据第i时钟信号,从第1信号的转变定时到第2信号的转变定时进行计数动作,并输出计数值。

[0116]

这样,能够求出与从第1信号的转变定时到第2信号的转变定时为止的时间差对应的计数值,能够进行针对时间差的粗略时间测量。

[0117]

并且,在本实施方式中,也可以是,时钟信号生成电路包含环形振荡电路,该环形振荡电路从多个中间节点输出多个多相时钟信号。

[0118]

这样,能够从环形振荡电路的多个中间节点输出频率相同且相位不同的多个多相时钟信号。

[0119]

并且,在本实施方式中,也可以是,时钟信号生成电路包含pll电路,该pll电路设置有环形振荡电路作为压控振荡电路,生成与使用振子生成的基准时钟信号的相位同步的多个多相时钟信号。

[0120]

这样,通过在时钟信号生成电路中设置pll电路,能够生成与基准时钟信号同步的多个多相时钟信号,并且能够将多相时钟信号的频率设定为将基准时钟信号的频率倍频后

的频率。

[0121]

并且,在本实施方式中,也可以是,时间数字转换电路包含:第1信号用振荡电路,其在第1信号的转变定时处开始振荡,生成第1信号用振荡时钟信号;第j振荡电路,其在第j时钟信号的转变定时处开始振荡,生成频率与第1信号用振荡时钟信号不同的第j振荡时钟信号;以及第1时间数字转换器,其根据第1信号用振荡时钟信号和第j振荡时钟信号,输出第1数字值。并且,还可以包含:第2信号用振荡电路,其在第2信号的转变定时处开始振荡,生成第2信号用振荡时钟信号;第k振荡电路,其在第k时钟信号的转变定时处开始振荡,生成频率与第2信号用振荡时钟信号不同的第k振荡时钟信号;以及第2时间数字转换器,其根据第2信号用振荡时钟信号和第k振荡时钟信号,输出第2数字值。

[0122]

这样,能够按照与第1信号用振荡时钟信号和第j振荡时钟信号的频率差对应的分辨率,对第1信号与第j时钟信号的转变定时的时间差进行测量并作为第1数字值来输出。并且,能够按照与第2信号用振荡时钟信号和第k振荡时钟信号的频率差对应的分辨率,对第2信号与第k时钟信号的转变定时的时间差进行测量并作为第2数字值来输出。

[0123]

并且,在本实施方式中,也可以是,时钟信号生成电路输出与多个多相时钟信号中的第1多相时钟信号对应的第1时钟信号、与第2多相时钟信号对应的第2时钟信号以及与第3多相时钟信号对应的第3时钟信号,第i时钟信号、第j时钟信号、第k时钟信号分别是第1时钟信号、第2时钟信号以及第3时钟信号中的任意一个时钟信号。

[0124]

这样,时间数字转换电路能够使用时钟信号生成电路所输出的第1时钟信号、第2时钟信号、第3时钟信号来输出计数值、第1数字值、第2数字值。

[0125]

并且,在本实施方式中,也可以是,时间数字转换电路包含:第1计数器,其根据第1时钟信号,从第1信号的转变定时到第2信号的转变定时进行计数动作,并输出第1计数值;第2计数器,其根据第2时钟信号,从第1信号的转变定时到第2信号的转变定时进行计数动作,并输出第2计数值;以及第3计数器,其根据第3时钟信号,从第1信号的转变定时到第2信号的转变定时进行计数动作,并输出第3计数值。并且,处理电路也可以使用第1计数值、第2计数值以及第3计数值中的任意一个计数值来作为计数值。

[0126]

这样,能够选择第1时钟信号、第2时钟信号、第3时钟信号中的适合测量第1信号与第2信号的时间差的计数处理的时钟信号并测量该时间差。

[0127]

并且,在本实施方式中,也可以是,处理电路根据第1信号的转变定时处的多个多相时钟信号的信号电平,决定使用第1计数值、第2计数值以及第3计数值中的哪一个计数值来作为计数值。

[0128]

这样,通过对第1信号的转变定时处的多个多相时钟信号的信号电平进行监视,能够选择第1时钟信号、第2时钟信号、第3时钟信号中的适合测量第1信号与第2信号的时间差的计数处理的时钟信号并测量该时间差。

[0129]

并且,在本实施方式中,也可以是,时间数字转换电路包含:第1信号用振荡电路,其在第1信号的转变定时处开始振荡,生成第1信号用振荡时钟信号;第1振荡电路,其在第1时钟信号的转变定时处开始振荡,生成频率与第1信号用振荡时钟信号不同的第1振荡时钟信号;第2振荡电路,其在第2时钟信号的转变定时处开始振荡,生成频率与第1信号用振荡时钟信号不同的第2振荡时钟信号;以及第3振荡电路,其在第3时钟信号的转变定时处开始振荡,生成频率与第1信号用振荡时钟信号不同的第3振荡时钟信号。并且,还可以包含:第1

时间数字转换器,其根据第1信号用振荡时钟信号和第1振荡时钟信号,输出第1信号用第1数字值;第2时间数字转换器,其根据第1信号用振荡时钟信号和第2振荡时钟信号,输出第1信号用第2数字值;以及第3时间数字转换器,其根据第1信号用振荡时钟信号和第3振荡时钟信号,输出第1信号用第3数字值。并且,也可以是,处理电路使用第1信号用第1数字值、第1信号用第2数字值以及第1信号用第3数字值中的任意一个数字值来作为第1数字值。

[0130]

这样,能够选择第1时钟信号、第2时钟信号、第3时钟信号中的适合测量与第1信号的转变定时的时间差的时钟信号并测量该时间差,因此,可实现时间数字转换的高精度化。

[0131]

并且,在本实施方式中,也可以是,处理电路根据第1信号的转变定时处的多个多相时钟信号的信号电平,决定使用第1信号用第1数字值、第1信号用第2数字值以及第1信号用第3数字值中的哪一个数字值来作为第1数字值。

[0132]

这样,通过对第1信号的转变定时处的多个多相时钟信号的信号电平进行监视,能够选择适合测量与第1信号的转变定时的时间差的时钟信号并测量该时间差。

[0133]

并且,在本实施方式中,也可以是,时间数字转换电路包含:第2信号用振荡电路,其在第2信号的转变定时处开始振荡,生成第2信号用振荡时钟信号;第4振荡电路,其在第1时钟信号的转变定时处开始振荡,生成频率与第2信号用振荡时钟信号不同的第4振荡时钟信号;第5振荡电路,其在第2时钟信号的转变定时处开始振荡,生成频率与第2信号用振荡时钟信号不同的第5振荡时钟信号;以及第6振荡电路,其在第3时钟信号的转变定时处开始振荡,生成频率与第2信号用振荡时钟信号不同的第6振荡时钟信号。并且,还可以包含:第4时间数字转换器,其根据第2信号用振荡时钟信号和第4振荡时钟信号,输出第2信号用第1数字值;第5时间数字转换器,其根据第2信号用振荡时钟信号和第5振荡时钟信号,输出第2信号用第2数字值;以及第6时间数字转换器,其根据第2信号用振荡时钟信号和第6振荡时钟信号,输出第2信号用第3数字值。并且,也可以是,处理电路使用第2信号用第1数字值、第2信号用第2数字值以及第2信号用第3数字值中的任意一个数字值来作为第2数字值。

[0134]

这样,能够选择第1时钟信号、第2时钟信号、第3时钟信号中的适合测量与第2信号的转变定时的时间差的时钟信号并测量该时间差,因此,可实现时间数字转换的高精度化。

[0135]

并且,在本实施方式中,也可以是,处理电路根据第2信号的转变定时处的多个多相时钟信号的信号电平,决定使用第2信号用第1数字值、第2信号用第2数字值以及第2信号用第3数字值中的哪一个数字值来作为第2数字值。

[0136]

这样,通过对第2信号的转变定时处的多个多相时钟信号的信号电平进行监视,能够选择适合测量与第2信号的转变定时的时间差的时钟信号并测量该时间差。

[0137]

并且,本实施方式涉及物理量测量装置,该物理量测量装置包含:上述电路装置;以及处理装置,其进行基于来自电路装置的数字值的处理。

[0138]

并且,本实施方式涉及电子设备,该电子设备包含:上述电路装置;以及处理装置,其进行基于来自电路装置的数字值的处理。

[0139]

并且,本实施方式涉及移动体,该移动体包含:上述电路装置;以及处理装置,其进行基于来自电路装置的数字值的处理。

[0140]

另外,如上述那样对本实施方式进行了详细地说明,但本领域技术人员应当能够容易地理解,可以实施实质上不脱离本发明的新事项和效果的多个变形。因此,这样的变形例全部包含在本发明的范围内。例如,在说明书或附图中至少有一次与更广义或同义的不

同用语一起记载的用语也能够在说明书或附图的任意位置处置换为该不同用语。并且,本实施方式和变形例的全部组合也包含在本发明的范围内。并且,电路装置、时钟信号生成电路、时间数字转换电路、处理电路、电子设备、移动体的结构和动作等也并不限定于本实施方式中的说明,能够实施各种变形。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。