本实用新型属于时间同步技术领域,具体涉及一种利于实现时统设备低成本、低功耗和小型化的多时标源时统电路板。

背景技术:

在诸如卫星发射与测控系统、航空管理系统、社会联动系统以及银行系统等系统中,时间同步扮演着关键的角色,这些系统经过长期运行,系统中各节点之间的时间差会越来越大,如果不进行时间同步,会引发很多问题。时间同步也叫“对钟”,是指系统中的时统系统或时统设备为各节点时钟提供标准时间源,保证系统内各节点时钟运行的一致性。

传统的时间同步方案是选择通用型时统设备作为系统的主时钟,时统设备在溯源后提供标准时间源,对系统内各节点进行授时。通用型时统设备一般具有人机操作界面(如屏幕和按键)、由多种溯源子模块组成的溯源功能(即输入时间参考信息)、由多种授时子模块组成的授时功能(即输出统一授时信息)和内置标准频率源(原子钟或高稳恒温晶振,用于提供时间运行所需要的钟频信号)。通用型时统设备虽然能够为用户提供多种选择,但也伴随着体积大、功耗高和单价贵等劣势,多用于专业领域。

随着电子信息技术的不断发展,各行业对时间精度的要求也越来越高,时间同步技术不在限于专业领域,也逐渐走向市场化,传统时统设备已不能满足于对产品体积、功耗以及制造成本有更多要求的民用市场。

技术实现要素:

为了解决当前通用型时统设备所存在的体积大、功耗高和成本高的问题,本实用新型目的在于提供一种利于实现时统设备低成本、低功耗和小型化的多时标源时统电路板。

本实用新型所采用的技术方案为:

一种多时标源时统电路板,包括电路板本体,在所述电路板本体上布置有时码输入单元、多路选择器、时频处理单元和授时输出单元,其中,所述时码输入单元包括有如下多路时标源输入接口:irig-b码参考信息输入接口、卫星时间参考信息输入接口和/或时间码1pps tod参考信息输入接口,所述时频处理单元包括有贴片晶振电路和脉冲相位检测同步电路,所述授时输出单元包括有网络协议phy层芯片电路和rj45接口;

所述时码输入单元的多路时标源输入接口分别电连接所述多路选择器的不同输入端,所述多路选择器的输出端电连接所述脉冲相位检测同步电路的时标源信号输入端,所述脉冲相位检测同步电路的钟频信号输入端电连接所述贴片晶振电路的输出端,所述脉冲相位检测同步电路通过mii接口通信连接所述网络协议phy层芯片电路,所述网络协议phy层芯片电路还电连接所述rj45接口。

优化的,当所述时码输入单元包括有卫星时间参考信息输入接口时,在所述电路板本体上还布置有卫星接收机和卫星接收天线,其中,所述卫星接收天线电连接所述卫星接收机,所述卫星接收机电连接所述卫星时间参考信息输入接口。

优化的,在所述电路板本体上还布置有供电单元,其中,所述供电单元包括有12v直流电输入接口和实现12v转3.3v的第一dc-dc电源转换芯片电路;

所述第一dc-dc电源转换芯片电路的输入端电连接所述12v直流电输入接口,所述第一dc-dc电源转换芯片电路的输出端分别电连接所述脉冲相位检测同步电路和所述网络协议phy层芯片电路的供电端。

进一步优化的,当布置有卫星接收机时,所述供电单元还包括有实现12v转5v的第二dc-dc电源转换芯片电路;

所述第二dc-dc电源转换芯片电路的输入端电连接所述12v直流电输入接口,所述第二dc-dc电源转换芯片电路的输出端电连接所述卫星接收机的供电端。

优化的,在所述电路板本体上还布置有复位芯片电路,其中,所述复位芯片电路的输出端电连接所述脉冲相位检测同步电路/和所述网络协议phy层芯片电路的复位受控端。

具体的,所述复位芯片电路采用型号为max811teus-t的复位ic芯片及其外围电路。

优化的,所述时频处理单元还包括有若干工作状态指示灯,其中,所述工作状态指示灯的受控端电连接所述脉冲相位检测同步电路的输出端。

具体的,所述脉冲相位检测同步电路采用型号为stm32f207系列的mcu芯片及其外围电路。

本实用新型的有益效果为:

(1)本发明创造提供了一种利于实现时统设备低成本、低功耗和小型化的新型时统模块,通过在时码输入单元布置有多路时标源输入接口,在时频处理单元中布置有贴片晶振电路和脉冲相位检测同步电路,以及在授时输出单元中布置有网络协议phy层芯片电路和rj45接口,可一方面将溯源、授时以及控制功能均集成于一块小型电路板上,实现高度集成化和小型化目的,另一方面由于是选用贴片晶振代替原子钟或高稳恒温压控晶振来提供钟频信号,可极大地降低成本及功耗,运用最少的资源,满足大多数民用市场对时间同步的需求;

(2)所述多时标源时统电路板既可定型为小型的时统终端,也可以定型为板卡接入用户设备机箱完成时间同步功能,具有灵活性强和可移植性强的特点,便于实际应用和推广。

附图说明

为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

图1是本实用新型提供的多时标源时统电路板的电路原理结构示意图。

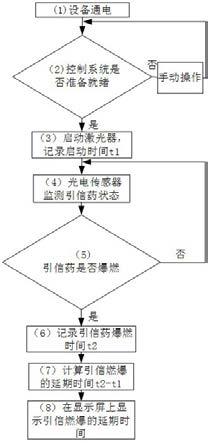

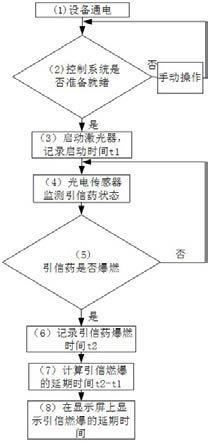

图2是本实用新型提供的在解调秒脉冲上升沿时常规的中断服务程序流程示意图。

图3是本实用新型提供的irig-b码在解调秒起始时刻的信号示意图。

图4是本实用新型提供的多时标源时统电路板在通过网络接入两级交换机下(其共接入50台以上计算机)作为ntp服务端对客户端节点的时间同步测试精度结果示例图。

具体实施方式

下面结合附图及具体实施例来对本实用新型作进一步阐述。在此需要说明的是,对于这些实施例方式的说明虽然是用于帮助理解本实用新型,但并不构成对本实用新型的限定。本文公开的特定结构和功能细节仅用于描述本实用新型的示例实施例。然而,可用很多备选的形式来体现本实用新型,并且不应当理解为本实用新型限制在本文阐述的实施例中。

应当理解,尽管本文可能使用术语第一、第二等等来描述各种单元,但是这些单元不应当受到这些术语的限制。这些术语仅用于区分一个单元和另一个单元。例如可以将第一单元称作第二单元,并且类似地可以将第二单元称作第一单元,同时不脱离本实用新型的示例实施例的范围。

应当理解,对于本文中可能出现的术语“和/或”,其仅仅是一种描述关联对象的关联关系,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,单独存在b,同时存在a和b三种情况;对于本文中可能出现的术语“/和”,其是描述另一种关联对象关系,表示可以存在两种关系,例如,a/和b,可以表示:单独存在a,单独存在a和b两种情况;另外,对于本文中可能出现的字符“/”,一般表示前后关联对象是一种“或”关系。

应当理解,在本文中若将单元称作与另一个单元“连接”、“相连”或“耦合”时,它可以与另一个单元直相连接或耦合,或中间单元可以存在。相対地,在本文中若将单元称作与另一个单元“直接相连”或“直接耦合”时,表示不存在中间单元。另外,应当以类似方式来解释用于描述单元之间的关系的其他单词(例如,“在……之间”对“直接在……之间”,“相邻”对“直接相邻”等等)。

应当理解,本文使用的术语仅用于描述特定实施例,并不意在限制本实用新型的示例实施例。若本文所使用的,单数形式“一”、“一个”以及“该”意在包括复数形式,除非上下文明确指示相反意思。还应当理解,若术语“包括”、“包括了”、“包含”和/或“包含了”在本文中被使用时,指定所声明的特征、整数、步骤、操作、单元和/或组件的存在性,并且不排除一个或多个其他特征、数量、步骤、操作、单元、组件和/或他们的组合存在性或增加。

应当理解,还应当注意到在一些备选实施例中,所出现的功能/动作可能与附图出现的顺序不同。例如,取决于所涉及的功能/动作,实际上可以实质上并发地执行,或者有时可以以相反的顺序来执行连续示出的两个图。

应当理解,在下面的描述中提供了特定的细节,以便于对示例实施例的完全理解。然而,本领域普通技术人员应当理解可以在没有这些特定细节的情况下实现示例实施例。例如可以在框图中示出系统,以避免用不必要的细节来使得示例不清楚。在其他实例中,可以不以不必要的细节来示出众所周知的过程、结构和技术,以避免使得示例实施例不清楚。

实施例一

如图1~4所示,本实施例提供的所述多时标源时统电路板,包括电路板本体,并在所述电路板本体上布置有时码输入单元、多路选择器、时频处理单元和授时输出单元,其中,所述时码输入单元包括有如下多路时标源输入接口:irig-b码参考信息输入接口、卫星时间参考信息输入接口和/或时间码1pps tod参考信息输入接口,所述时频处理单元包括有贴片晶振电路和脉冲相位检测同步电路,所述授时输出单元包括有网络协议phy层芯片电路和rj45接口;所述时码输入单元的多路时标源输入接口分别电连接所述多路选择器的不同输入端,所述多路选择器的输出端电连接所述脉冲相位检测同步电路的时标源信号输入端,所述脉冲相位检测同步电路的钟频信号输入端电连接所述贴片晶振电路的输出端,所述脉冲相位检测同步电路通过mii接口通信连接所述网络协议phy层芯片电路,所述网络协议phy层芯片电路还电连接所述rj45接口。

如图1所示,在所述多时标源时统电路板的具体结构中,所述时码输入单元用于提供多路时标源输入接口,可以但不限于有所述irig-b码参考信息输入接口、所述卫星时间参考信息输入接口和所述时间码1pps tod参考信息输入接口等。所述irig-b码参考信息输入接口用于导入外部第一时标源的irig-b码,由于irig(interrangeinstrumentationgroup)时间标准有两大类:一类是并行时间码格式,这类码由于是并行格式,传输距离较近,且是二进制,因此远不如串行格式广泛;另一类是串行时间码,共有六种格式,即a、b、d、e、g、h,它们的主要差别是时间码的帧速率不同,irig-b即为其中的b型码,b型码的时帧速率为1帧/s,可传递100位的信息,因而作为应用广泛的时间码,b型码具有以下主要特点:携带信息量大,经译码后可获得1、10、100、1000c/s的脉冲信号和bcd编码的时间信息及控制功能信息;高分辨率;调制后的b码带宽,适用于远距离传输;分直流、交流两种;具有接口标准化,国际通用等特点。从而可以便于所述脉冲相位检测同步电路能够基于常规手段先找出码元头部,确定解调秒的起始时刻,同步本地秒,再依照irig-b码元信息的标准格式解析出时间信息,进而同步本地时间完成溯源。具体的,所述irig-b码参考信息输入接口采用现有硬件结构实现。所述卫星时间参考信息输入接口用于导入来自外部定位卫星(即外部第二时标源)的卫星时间参考信息,以便所述脉冲相位检测同步电路能够基于常规手段在判定卫星定位和时间报文有效时,同步本地秒和时间完成溯源。具体的,所述卫星时间参考信息输入接口也可以采用现有硬件结构实现。所述时间码1pps tod参考信息输入接口用于导入外部第三时标源的1pps tod时间码信号,以便所述脉冲相位检测同步电路能够基于常规手段在判定时间报文有效时,也同步本地秒和时间完成溯源。具体的,所述时间码1pps tod参考信息输入接口可参照现有的《中国移动高精度时间同步1pps tod接口规范》进行常规硬件设计实现。

所述多路选择器用于实现对某一路时标源输入接口的导通选择,使对应的参考信息能够进入所述脉冲相位检测同步电路中去同步本地秒和时间完成溯源,具体的,所述多路选择器可采用4选1或8选1等现有的模拟多路选择器实现。所述时频处理单元用于根据外部时标源提供的时间参考信息,同步本地秒和时间完成溯源,其中,所述贴片晶振电路用于为所述脉冲相位检测同步电路提供运行时钟,并作为钟频信号源保障时统模块能够运行本地时钟,由于是采用普通的贴片晶振替代原子钟或高稳恒温压控晶振来为时统模块提供钟频信号(例如25mhz的信号),可以极大地降低成本及功耗,实现运用最少的资源,满足大多数民用市场对时间同步的需求。此外,所述贴片晶振电路可采用现有的贴片晶振电路实现。

所述脉冲相位检测同步电路用于采用常规的脉冲相位检测同步方式,同步本地秒和时间完成溯源,例如采用秒脉冲相位同步方式,以解调出外部某个时标参考源的1pps脉冲作为基准秒,每秒地将本地1pps脉冲上升沿与外部时标参考源的1pps脉冲上升沿进行同步,进而可将时间同步精度控制在10us以内,满足民用市场的应用。详细举例的,可采用如下常规的秒脉冲相位同步方式:以解调出外部时标参考源的1pps脉冲的上升沿作为外部中断触发条件,每秒触发一次中断;并在中断服务程序中,进行防抖动检测,即当解调秒处于正常状态,每秒执行一次同步本地秒脉冲相位的操作(例如清零1pps定时器计数值,重新加载),若检测到解调秒相位异常突跳,维持本地秒正常运行,详细的,中断服务程序执行流程如图2所示,在进入中断服务程序后,首先测量本地秒与解调秒的上升沿相差δt;如果δt小于门限t(具体取值可为1ms),则执行一次同步本地秒脉冲的操作,而如果δt大于门限t,检测到解调秒异常突跳,不进行同步操作;如果δt连续3秒超过门限t,则认为解调秒相位正常变化,执行一次同步本地秒脉冲的操作。此外详细举例的,所述脉冲相位检测同步电路可以但不限于采用型号为stm32f207系列的mcu芯片及其外围电路。

详细举例的,所述脉冲相位检测同步电路实现解调出外部某个时标参考源的1pps脉冲的常规方式可具体如下(1)~(3)。

(1)irig-b(dc)码参考信息解析:以定时器捕获方式采集输入irig-b(dc)码信号的数字电平,通过判断脉冲宽度的方式确定码元信号,完整的irig-b(dc)码信号由1个整秒内的100个码元组成,每个码元分为高低电平两部分,码元速率为100pps,有三种形态,分别为“0”,“1”以及“p”(若脉冲宽度在1.5-2.5ms范围内,则判定为“0”码元;若脉冲宽度在4.5-5.5ms范围内,则判定为“1”码元;若脉冲宽度在7.5-8.5ms范围内,则判定为“p”码元,在一帧中共出现11次,表示pr、p1、……p9、p0;其它则为异常码元),然后通过下述两个常规步骤完成对irig-b(dc)码信号的溯源,首先检测irig-b(dc)头部,若连续捕获的两个码元均为“p”,第一个为p0,第二个为pr,即为起始码元(编号0),其上升沿为解调秒的起始时刻,如图3所示,将本地秒脉冲与其进行同步;然后分别在第1~8码元、10~17码元、20~26码元、27~28码元、30~41码元和43~48码元解调出对应的秒、分、时、闰秒、一年内的总天数以及年等信息,将本地时间与b码时间进行同步。另外,还可以在irig-b(dc)信号中的51~98码元中加入控制信息,用于其它方面的可选功能。

(2)卫星时间参考信息解析:由于卫星信号包括卫星接收机输出的解调秒以及串口数据信息,可通过下述两个常规步骤完成对卫星时间信号的溯源:首先通过串口接收卫星接收机输入的时间以及定位信息,若有效卫星数大于4颗,定位以及时间数据有效,以卫星时间为基准,将本地时间的年月日、时分秒信息与其进行同步;然后以卫星接收机输出的解调秒为基准,将本地秒脉冲与其进行同步。

(3)时间码1pps tod参考信息的解析:由于该时间码信号包括解调秒以及串口时间信息,可通过如下常规步骤完成对该时间码参考信号的溯源:即通过串口接收时间码输入的时间信息,若数据有效,以解析的时间为基准,将本地时间的年月日、时分秒信息与其进行同步。

所述授时输出单元用于构成网络底层接口,以便通过现有的ntp协议(networktimeprotocol,一种用来使计算机时间同步化的协议)完成网络授时功能,即在网络坏境中,可使所述多时标源时统电路板作为ntp服务器端,当接收到来自客户端的ntp时间同步请求指令时,将标准时间信息填充至ntp应答报文以响应客户端。具体的,以mac phy片(mac-以太网媒体接入控制器;phy-物理接口收发器)的形式构建网络授时的硬件接口,其中的所述网络协议phy层芯片电路可选用占用资源少且可移植性强的现有lwip协议栈(由瑞典计算机科学院的adamdunkels开发的一个小型开源的tcp/ip协议栈)实现tcp/ip网络协议功能。同时可采用ntp协议网络授时方式对用户设备的时间进行同步,最好可兼容sntp协议(simplenetworktimeprotocol,简单网络时间协议),即时统模块作为服务端接收来自客户端的ntp时间同步请求报文,在收到时间同步请求报文的时刻,由所述脉冲相位检测同步电路读取1pps定时器,获取当前1pps内经过的计数值,记录亚秒级时间(单位为纳秒),与当前本地秒级时间(1900年开始计算的总秒数)组合为接收时间戳,在准备响应的时刻,再次记录亚秒级时间与本地秒级时间,组合为发送时间戳,由ntp时间应答报文作为载体将两次的时间戳信息发送至客户端,客户端收到时间应答报文后,进行时钟过滤和选择,将时间同步至服务端,完成一次ntp时间同步的操作;结合图4所示,守时模块ntp时间同步精度平均偏差为-29768.850ns,标准方差为10120.449ns,满足民用市场对于ntp时间同步精度低于1ms的指标需求。此外,由于具备了网络通信能力,可以在此基础上扩展网络管理功能,通过定制udp(userdatagramprotocol,internet协议集支持一个无连接的传输协议,该协议称为用户数据报协议)、tcp(transmissioncontrolprotocol,传输控制协议)以及snmp(简单网络管理协议,是专门设计用于在ip网络管理网络节点的一种标准协议)等协议实现远端对时统模块的状态查询和工作模式设置等功能。具体举例的,所述网络协议phy层芯片电路可采用现有型号为ip101gri的以太网收发器芯片及其外围电路实现,可通过常规的mii接口((mediaindependentinterface,介质无关接口或称为媒体独立接口,它是ieee-802.3定义的以太网行业标准;它包括一个数据接口和一个mac和phy之间的管理接口)与所述脉冲相位检测同步电路通信连接。另外,所述rj45接口用于接入以太网,以便为联网的其他节点授时,可以但不限于采用型号为13f-60fgydpnw2nl的接口芯片及其外围电路。

由此通过前述多时标源时统电路板的详细结构以及常规软件方法描述,提供了一种利于实现时统设备低成本、低功耗和小型化的新型时统模块,通过在时码输入单元布置有多路时标源输入接口,在时频处理单元中布置有贴片晶振电路和脉冲相位检测同步电路,以及在授时输出单元中布置有网络协议phy层芯片电路和rj45接口,可一方面将溯源、授时以及控制功能均集成于一块小型电路板上,实现高度集成化和小型化目的,另一方面由于是选用贴片晶振代替原子钟或高稳恒温压控晶振来提供钟频信号,可极大地降低成本及功耗,运用最少的资源,满足大多数民用市场对时间同步的需求;此外,所述多时标源时统电路板既可定型为小型的时统终端,也可以定型为板卡接入用户设备机箱完成时间同步功能,具有灵活性强和可移植性强的特点,便于实际应用和推广。

优化的,当所述时码输入单元包括有卫星时间参考信息输入接口时,在所述电路板本体上还布置有卫星接收机和卫星接收天线,其中,所述卫星接收天线电连接所述卫星接收机,所述卫星接收机电连接所述卫星时间参考信息输入接口。如图1所示,通过前述电路结构设计,可以实现卫星时间参考信息的正常接收,满足应用需求。具体举例的,所述卫星接收机和所述卫星接收天线可分别采用现有的硬件结构实现。

优化的,在所述电路板本体上还布置有供电单元,其中,所述供电单元包括有12v直流电输入接口和实现12v转3.3v的第一dc-dc电源转换芯片电路;所述第一dc-dc电源转换芯片电路的输入端电连接所述12v直流电输入接口,所述第一dc-dc电源转换芯片电路的输出端分别电连接所述脉冲相位检测同步电路和所述网络协议phy层芯片电路的供电端。如图1所示,通过前述电路结构设计,可利用所述第一dc-dc电源转换芯片电路的12v-3.3v稳定降压功能,为所述mcu芯片和所述网络协议phy层芯片等提供合适的3.3v工作电压;具体的,所述第一dc-dc电源转换芯片电路可采用型号为rt8292ahgsp的直流降压芯片及外围电路实现。

优化的,当布置有卫星接收机时,所述供电单元还包括有实现12v转5v的第二dc-dc电源转换芯片电路;所述第二dc-dc电源转换芯片电路的输入端电连接所述12v直流电输入接口,所述第二dc-dc电源转换芯片电路的输出端电连接所述卫星接收机的供电端。如图1所示,通过前述电路结构设计,可利用所述第二dc-dc电源转换芯片电路的12v-5v的稳定降压功能,为所述卫星接收机等提供合适的5v工作电压;具体的,所述第二dc-dc电源转换芯片电路可采用型号为lt1761is5-5(ldo)的直流降压芯片实现。

优化的,在所述电路板本体上还布置有复位芯片电路,其中,所述复位芯片电路的输出端电连接所述脉冲相位检测同步电路/和所述网络协议phy层芯片电路的复位受控端。如图1所示,通过布置所述复位芯片电路,可以基于现有看门狗程序对所述脉冲相位检测同步电路/和所述网络协议phy层芯片电路进行防死机控制,确保在无人值守时能够长期进行对外客户端的统一授时。具体举例的,所述复位芯片电路可采用型号为max811teus-t的复位ic芯片及其外围电路。

优化的,所述时频处理单元还包括有若干工作状态指示灯,其中,所述工作状态指示灯的受控端电连接所述脉冲相位检测同步电路的输出端。如图1所示,通过设置所述工作状态指示灯,可以对外指示时统模块的运行状态,具体可以但不限于包括有用于指示时标参考源输入、工作模式、1pps时钟信号、网络连接状态等情况的led指示灯。

综上,采用本实施例所提供的多时标源时统电路板,具有如下技术效果:

(1)本实施例提供了一种利于实现时统设备低成本、低功耗和小型化的新型时统模块,通过在时码输入单元布置有多路时标源输入接口,在时频处理单元中布置有贴片晶振电路和脉冲相位检测同步电路,以及在授时输出单元中布置有网络协议phy层芯片电路和rj45接口,可一方面将溯源、授时以及控制功能均集成于一块小型电路板上,实现高度集成化和小型化目的,另一方面由于是选用贴片晶振代替原子钟或高稳恒温压控晶振来提供钟频信号,可极大地降低成本及功耗,运用最少的资源,满足大多数民用市场对时间同步的需求;

(2)所述多时标源时统电路板既可定型为小型的时统终端,也可以定型为板卡接入用户设备机箱完成时间同步功能,具有灵活性强和可移植性强的特点,便于实际应用和推广。

以上所描述的多个实施例仅仅是示意性的,若涉及到作为分离部件说明的单元,其可以是或者也可以不是物理上分开的;若涉及到作为单元显示的部件,其可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本实施例方案的目的。本领域普通技术人员在不付出创造性的劳动的情况下,即可以理解并实施。

以上实施例仅用以说明本实用新型的技术方案,而非对其限制;尽管参照前述实施例对本实用新型进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换。而这些修改或者替换,并不使相应技术方案的本质脱离本实用新型各实施例技术方案的精神和范围。

最后应说明的是,本实用新型不局限于上述可选的实施方式,任何人在本实用新型的启示下都可得出其他各种形式的产品。上述具体实施方式不应理解成对本实用新型的保护范围的限制,本实用新型的保护范围应当以权利要求书中界定的为准,并且说明书可以用于解释权利要求书。

本文用于企业家、创业者技术爱好者查询,结果仅供参考。