1.本发明涉及晶体氧化物薄膜、层叠体以及薄膜晶体管。

背景技术:

2.无定形氧化物半导体的技术问题在于氧缺陷导致的电子载体不稳定。

3.对此,在专利文献1以及专利文献2中,主要使用包含in(铟)以及ga(镓)的组成,将水(h2o)加入溅射气体中进行成膜,由此可将晶体氧化物半导体材料用于沟道,制作了高迁移率且稳定的tft。

4.在将水加入溅射气体中而进行成膜的情况下,与工艺装置相关的技术问题在于管道的腐蚀,与tft特性相关的课题在于氢原子的影响所引起的阈值电压vth的面内偏差以及可靠性变差。

5.对于这些技术问题,在专利文献3、专利文献4以及专利文献5中记载有如下内容:应用在in

‑

ga

‑

o中加入了ln(镧系元素)的组成,即便是在含氧(o2)的成膜中,也可制作高迁移率且稳定的tft。

6.在专利文献6中记载有tft的特性。专利文献6所记载的tft具有一种氧化物薄膜,该氧化物薄膜是使用包含含有铟、镓以及钐的氧化物烧结体的溅射靶成膜而得的。

7.现有技术文献

8.专利文献

9.专利文献1:日本专利第5373212号公报

10.专利文献2:日本特开2018

‑

107316号公报

11.专利文献3:日本专利第6097458号公报

12.专利文献4:日本专利第6334598号公报

13.专利文献5:日本专利第6289693号公报

14.专利文献6:国际公开第2018/043323号

技术实现要素:

15.发明要解决的技术问题

16.近年来,tft元件存在逐渐小型化的倾向,小型tft中的特性变得较为重要。这里的小型tft是指沟道长度l为50μm以下的tft。

17.若将专利文献1~3以及专利文献5所记载的氧化物薄膜、及专利文献4所记载的一部分氧化物薄膜应用于小型tft,则存在陷阱限制传导区域特性恶化的技术问题。陷阱限制传导区域特性定义为栅极施加电压vg在低电压区域中作为氧化物半导体的主要的传导特性的、陷阱限制传导所贡献的迁移率。若tft的尺寸变小,则存在陷阱限制传导区域特性降低的倾向。

18.在专利文献6中,记载有通过金属掩模将电极图案化而得的沟道长度l超过50μm的tft。在专利文献6所记载的tft中,虽然可得到良好的tft特性,但未能得到小型tft中的陷

阱限制传导区域特性。

19.本发明的目的在于提供一种即使在小型tft中也示出良好的迁移率的晶体氧化物薄膜、具有该晶体氧化物薄膜的层叠体、以及具有该晶体氧化物薄膜的薄膜晶体管。

20.用于解决上述技术问题的方案

21.[1]一种晶体氧化物薄膜,其包含in元素、ga元素以及ln元素,in元素为主成分,ln元素是从la、nd、sm、eu、gd、tb、dy、ho、er、tm、yb以及lu构成的组中选择的一种以上的元素,平均晶体粒径d1为0.05μm以上、0.5μm以下。

[0022]

[2]如[1]所述的晶体氧化物薄膜,所述晶体氧化物薄膜的薄膜表面与薄膜中的晶体晶界所成的平均晶界角度θ为70

°

以上、110

°

以下。

[0023]

[3]如[1]或[2]所述的晶体氧化物薄膜,所述晶体氧化物薄膜的薄膜中的晶体晶界彼此的平均间隔d2为0.05μm以上、0.40μm以下。

[0024]

[4]如[1]~[3]的任一项所述的晶体氧化物薄膜,在所述晶体氧化物薄膜的平面tem

‑

eds解析中,构成所述晶体氧化物薄膜的金属元素不在薄膜中的晶体晶界处偏析。

[0025]

[5]如[1]~[4]的任一项所述的晶体氧化物薄膜,其满足以下述(1)、(2)以及(3)表示的原子组成比的范围。

[0026]

0.85<in/(in ga ln)≤0.98

…

(1)

[0027]

0.01≤ga/(in ga ln)<0.11

…

(2)

[0028]

0.01≤ln/(in ga ln)<0.04

…

(3)

[0029]

[6]如[1]~[5]的任一项所述的晶体氧化物薄膜,其包含在所述晶体氧化物薄膜的电子射线衍射中为方铁锰矿结构的晶粒。

[0030]

[7]如[1]~[6]的任一项所述的晶体氧化物薄膜,ln元素为sm元素。

[0031]

[8]一种层叠体,具有如[1]~[6]的任一项所述的晶体氧化物薄膜与支承所述晶体氧化物薄膜的支承体,所述支承体的表面与所述晶体氧化物薄膜中的晶体晶界所成的平均晶界角度θsub为70

°

以上、110

°

以下,薄膜中的晶体晶界彼此的平均间隔d2为0.05μm以上、0.40μm以下。

[0032]

[9]一种薄膜晶体管,其具有电极、晶体氧化物薄膜,在所述薄膜晶体管的截面tem观察中,所述电极与所述晶体氧化物薄膜的接触区域长度ls以及所述晶体氧化物薄膜中的晶体晶界彼此的平均间隔d2满足式(4)以及式(5)的关系。

[0033]

1μm≤ls≤50μm

…

(4)

[0034]

10≤ls/d2≤1000

…

(5)

[0035]

[10]如[9]所述的薄膜晶体管,所述晶体氧化物薄膜包含in元素、ga元素以及ln元素,in元素为主成分,ln元素是从la、nd、sm、eu、gd、tb、dy、ho、er、tm、yb以及lu构成的组中选择的一种以上的元素,所述晶体氧化物薄膜中的平均晶体粒径d1为0.05μm以上、0.5μm以下。

[0036]

[11]如[9]或[10]所述的薄膜晶体管,所述晶体氧化物薄膜的薄膜表面与薄膜中的晶体晶界所成的平均晶界角度θ为70

°

以上、110

°

以下,薄膜中的晶体晶界彼此的平均间隔d2为0.05μm以上、0.40μm以下。

[0037]

[12]一种薄膜晶体管,其具有晶体氧化物薄膜,所述晶体氧化物薄膜包含in元素、ga元素以及ln元素,in元素为主成分,ln元素是从la、nd、sm、eu、gd、tb、dy、ho、er、tm、yb以

及lu构成的组中选择的一种以上的元素,所述晶体氧化物薄膜中的平均晶体粒径d1为0.05μm以上、0.5μm以下,所述晶体氧化物薄膜的薄膜表面与薄膜中的晶体晶界所成的平均晶界角度θ为70

°

以上、110

°

以下,薄膜中的晶体晶界彼此的平均间隔d2为0.05μm以上、0.40μm以下。

[0038]

[13]如[12]所述的薄膜晶体管,在所述晶体氧化物薄膜的平面tem

‑

eds解析中,构成所述晶体氧化物薄膜的金属元素不在薄膜中的晶体晶界处偏析。

[0039]

[14]如[12]或[13]所述的薄膜晶体管,所述晶体氧化物薄膜满足以下述(1)、(2)以及(3)表示的原子组成比的范围。

[0040]

0.85<in/(in ga ln)≤0.98

…

(1)

[0041]

0.01≤ga/(in ga ln)<0.11

…

(2)

[0042]

0.01≤ln/(in ga ln)<0.04

…

(3)

[0043]

[15]如[12]~[14]的任一项所述的薄膜晶体管,所述晶体氧化物薄膜包含在电子射线衍射中为方铁锰矿结构的晶粒。

[0044]

[16]如[12]~[15]的任一项所述的薄膜晶体管,ln元素为sm元素。

[0045]

发明效果

[0046]

根据本发明的一方案,能够提供一种即使在小型tft中也示出良好的迁移率的晶体氧化物薄膜、具有该晶体氧化物薄膜的层叠体、以及具有该晶体氧化物薄膜的薄膜晶体管。

附图说明

[0047]

图1是示出本发明的一方案所涉及的层叠体的纵剖视图。

[0048]

图2a是示出在玻璃基板上形成了氧化物薄膜的状态的纵剖视图。

[0049]

图2b是示出在图2a的氧化物薄膜上形成了sio2膜的状态的图。

[0050]

图3是示出本发明的一方案所涉及的薄膜晶体管的纵剖视图。

[0051]

图4是示出本发明的一方案所涉及的薄膜晶体管的纵剖视图。

[0052]

图5是示出本发明的一方案所涉及的量子隧道场效应晶体管的纵剖视图。

[0053]

图6是示出量子隧道场效应晶体管的另一例的纵剖视图。

[0054]

图7是在图5中的p型半导体层与n型半导体层之间形成有氧化硅层的部分的tem(透射型电子显微镜)照片。

[0055]

图8a是用于说明量子隧道场效应晶体管的制造步骤的纵剖视图。

[0056]

图8b是用于说明量子隧道场效应晶体管的制造步骤的纵剖视图。

[0057]

图8c是用于说明量子隧道场效应晶体管的制造步骤的纵剖视图。

[0058]

图8d是用于说明量子隧道场效应晶体管的制造步骤的纵剖视图。

[0059]

图8e是用于说明量子隧道场效应晶体管的制造步骤的纵剖视图。

[0060]

图9a是示出使用了本发明的一方案所涉及的薄膜晶体管的显示装置的俯视图。

[0061]

图9b是用于说明使用了本发明的一方案所涉及的薄膜晶体管的显示装置的像素部的电路的电路图。

[0062]

图9c是用于说明使用了本发明的一方案所涉及的薄膜晶体管的显示装置的像素部的电路的电路图。

[0063]

图10是示出使用了本发明的一方案所涉及的薄膜晶体管的固体拍摄元件的像素部的电路的图。

[0064]

图11是实施例以及比较例所涉及的半导体图案化后的膜状态的显微镜像。

[0065]

图12是实施例1所涉及的氧化物薄膜的截面tem图像。

[0066]

图13是实施例2所涉及的氧化物薄膜的截面tem图像。

[0067]

图14是实施例3所涉及的氧化物薄膜的截面tem图像。

[0068]

图15是比较例1所涉及的氧化物薄膜的截面tem图像。

[0069]

图16是比较例2所涉及的氧化物薄膜的截面tem图像。

[0070]

图17是比较例3所涉及的氧化物薄膜的截面tem图像。

[0071]

图18是比较例4所涉及的氧化物薄膜的截面tem图像。

[0072]

图19是实施例1所涉及的氧化物薄膜的平面tem图像。

[0073]

图20是实施例2所涉及的氧化物薄膜的平面tem图像。

[0074]

图21是实施例3所涉及的氧化物薄膜的平面tem图像。

[0075]

图22是比较例1所涉及的氧化物薄膜的平面tem图像。

[0076]

图23是比较例2所涉及的氧化物薄膜的平面tem图像。

[0077]

图24是比较例3所涉及的氧化物薄膜的平面tem图像。

[0078]

图25是比较例4所涉及的氧化物薄膜的平面tem图像。

[0079]

图26是实施例1所涉及的氧化物薄膜的平面tem

‑

eds图像。

[0080]

图27是实施例3所涉及的氧化物薄膜的平面tem

‑

eds图像。

[0081]

图28是比较例1所涉及的氧化物薄膜的平面tem

‑

eds图像。

[0082]

图29是比较例2所涉及的氧化物薄膜的平面tem

‑

eds图像。

[0083]

图30是比较例3所涉及的氧化物薄膜的平面tem

‑

eds图像。

[0084]

图31a是与实施例1所涉及的小型tft有关的传递特性id

‑

vg图表。

[0085]

图31b是示出与实施例1所涉及的小型tft有关的vg与迁移率μsat的关系的图表。

[0086]

图32a是与实施例2所涉及的小型tft有关的传递特性id

‑

vg图表。

[0087]

图32b是示出与实施例2所涉及的小型tft有关的vg与迁移率μsat的关系的图表。

[0088]

图33a是与实施例3所涉及的小型tft有关的传递特性id

‑

vg图表。

[0089]

图33b是示出与实施例3所涉及的小型tft有关的vg与迁移率μsat的关系的图表。

[0090]

图34a是与比较例1所涉及的小型tft有关的传递特性id

‑

vg图表。

[0091]

图34b是示出与比较例1所涉及的小型tft有关的vg与迁移率μsat的关系的图表。

[0092]

图35a是与比较例2所涉及的小型tft有关的传递特性id

‑

vg图表。

[0093]

图35b是示出与比较例2所涉及的小型tft有关的、vg与迁移率μsat的关系的图表。

[0094]

图36是与比较例3所涉及的小型tft有关的、传递特性id

‑

vg图表。

[0095]

图37a是与比较例4所涉及的小型tft有关的传递特性id

‑

vg图表。

[0096]

图37b是示出与比较例4所涉及的小型tft有关的vg与迁移率μsat的关系的图表。

具体实施方式

[0097]

以下,参照附图等对实施方式进行说明。但是,实施方式能够以很多不同的方案进行实施,若为本领域的技术人员,则容易理解可以在不脱离主旨及其范围的情况下对该实

施方式以及详细内容进行各种变更。因此,本发明不限定于以下的实施方式所记载的内容来进行解释。

[0098]

在附图中,有时为了明确而将大小、层的厚度以及区域等夸张表现。因此,本发明不限定于图示的大小、层的厚度以及区域等。另外,附图示意性地示出理想的例子,本发明并不限定于附图所示的形状以及值等。

[0099]

本说明书中使用的“第1”、“第2”、“第3”这样的序数词是为了避免构成要素的混淆而附加的,对于未记载在数量上进行限定的意旨的构成要素,不在数量上进行限定。

[0100]

在本说明书等中,“膜”或“薄膜”这样的用语与“层”这样的用语可根据情况相互替换。

[0101]

在本说明书等的烧结体以及氧化物薄膜中,“化合物”这样的用语与“晶相”这样的用语可根据情况相互替换。

[0102]

在本说明书中,有时将“氧化物烧结体”简称为“烧结体”。

[0103]

在本说明书中,有时将“溅射靶”简称为“靶”。

[0104]

在本说明书等中,“电连接”包括经由“某种具有电性作用的物质”而连接的情况。在此,“某种具有电性作用的物质”只要可进行在连接对象之间的电信号的收发,就没有特别限制。例如,“某种具有电性作用的物质”包括电极、布线、开关元件(晶体管等)、电阻元件、电感器、电容器以及其它的具有各种功能的元件等。

[0105]

在本说明书等中,晶体管所具有的源极或漏极的功能有时在采用不同极性的晶体管的情况下或者在电路动作中电流的方向发生变化的情况下等会进行替换。因此,在本说明书等中,源极或漏极的用语能够替换使用。

[0106]

在本说明书中,使用“~”表示的数值范围是指,将记载在“~”前的数值作为下限值,将记载在“~”后的数值作为上限值从而包括的范围。

[0107]

本发明人等得出以下认知:通过在包含in(铟)元素、ga(镓)元素以及ln元素(镧系元素)且in元素为主成分的晶体氧化物薄膜中,将平均晶体粒径控制得较小,从而即便在小型tft中也可得到良好的迁移率。

[0108]

此外,本发明人等得出以下认知:例如通过将晶体氧化物薄膜中的in元素、ga元素以及ln元素的组成比率控制在规定范围内、或将小型tft制作工艺中的条件控制在规定范围内等,从而即使溅射气体不含有水,也可得到将平均晶体粒径控制得较小的晶体氧化物薄膜。

[0109]

本发明人等基于这些认知发明了本发明。

[0110]

1.晶体氧化物薄膜

[0111]

本实施方式所涉及的晶体氧化物薄膜包含in元素(铟元素)、ga元素(镓元素)以及ln元素(镧系元素)。

[0112]

在本实施方式所涉及的晶体氧化物薄膜中,in元素为主成分,ln元素是从la、nd、sm、eu、gd、tb、dy、ho、er、tm、yb以及lu构成的组中选择的一种以上的元素。

[0113]

本实施方式所涉及的晶体氧化物薄膜可以实质上仅由in元素(铟元素)、ga元素(镓元素)、ln元素(镧系元素)以及o元素(氧元素)构成。在此,“实质上”是指,在产生由上述in元素(铟元素)、ga元素(镓元素)、ln元素(镧系元素)以及o元素(氧元素)的组合带来的本发明的效果的范围内,本实施方式所涉及的晶体氧化物薄膜也可以包含其它成分。

[0114]

(平均晶体粒径d1)

[0115]

在本实施方式所涉及的晶体氧化物薄膜中,平均晶体粒径d1为0.05μm以上、0.5μm以下,优选为0.05μm以上、0.4μm以下。

[0116]

在本说明书中,晶体氧化物薄膜中的平均晶体粒径d1基于平面tem观察图像(有时称为“平面tem像”)进行测量。即,通过解析使用透射型电子显微镜对以倍率200,000倍放大而观察到的平面tem进行观察而得的晶粒的直径来计算。此外,作为平均晶体粒径d1的其它测量方法,也可如后述的实施例所记载的那样利用针对镓离子束照射后且平面tem观察前的样品的ebsp(背散射电子衍射像)进行同样的解析。

[0117]

(薄膜表面与薄膜中的晶体晶界所成的角度)

[0118]

本实施方式所涉及的晶体氧化物薄膜中,薄膜表面与薄膜中的晶体晶界所成的平均晶界角度θ优选为70

°

以上、110

°

以下。

[0119]

如果薄膜表面与薄膜中的晶体晶界所成的平均晶界角度θ为70

°

以上、110

°

以下,则即使在与电极的接触区域长度较短的小型tft中,晶体晶界也不会相对于电极面过于倾斜,能够使晶体晶界在接触区域长度的长度方向上密集地存在,其结果为,具有本实施方式所涉及的晶体氧化物薄膜的薄膜晶体管示出更良好的迁移率。

[0120]

在本说明书中,薄膜表面与薄膜中的晶体晶界所成的平均晶界角度θ基于截面tem观察图像(有时称为“截面tem像”)进行测量。即,通过解析使用透射型电子显微镜对以倍率200,000倍放大而观察到的截面tem进行观察而得的晶体晶界与薄膜表面所成的角来计算。

[0121]

(薄膜中的晶体晶界彼此的平均间隔d2)

[0122]

在本实施方式所涉及的晶体氧化物薄膜中,薄膜中的晶体晶界彼此的平均间隔d2优选为0.05μm以上、0.40μm以下,更优选为0.08μm以上、0.30μm以下。

[0123]

在本说明书中,薄膜中的晶体晶界彼此的平均间隔d2基于截面tem观察图像进行测量。即,在使用透射型电子显微镜以倍率200,000倍观测到的像之中,以在沟道方向上为1μm、氧化物膜厚为50nm的尺寸,按观测点不在薄膜晶体管中的l长度方向上重叠的方式提取任意的3个视野,解析通过截面tem像观察到的晶粒的间隔,从而计算d2。

[0124]

(向晶体晶界的偏析状态)

[0125]

在针对本实施方式所涉及的晶体氧化物薄膜的平面tem

‑

eds解析中,构成该晶体氧化物薄膜的金属元素优选不在薄膜中的晶体晶界处偏析。在本说明书中,“不在薄膜中的晶体晶界处偏析”是指各金属元素均匀分布且在晶界处也没有偏向。通过使构成晶体氧化物薄膜的金属元素不在晶体晶界处偏析,陷阱限制传导区域特性提高。

[0126]

(薄膜的组成)

[0127]

本实施方式所涉及的晶体氧化物薄膜优选满足以下述(1)、(2)以及(3)表示的原子组成比的范围。

[0128]

0.85<in/(in ga ln)≤0.98

…

(1)

[0129]

0.01≤ga/(in ga ln)<0.11

…

(2)

[0130]

0.01≤ln/(in ga ln)<0.04

…

(3)

[0131]

在本实施方式所涉及的晶体氧化物薄膜中,如果in/(in ga ln)超过0.85,则在小型tft驱动时作为载体的电子难以受到氧化物薄膜中的缺陷带来的能量势垒的影响,结果可得到陷阱限制传导区域特性优异的小型tft。

[0132]

在本实施方式所涉及的晶体氧化物薄膜中,如果in/(in ga ln)为0.98以下,则在小型tft中将栅极电压以负值施加时,难以产生漏电流,可得到on/off优异的晶体管特性。

[0133]

in/(in ga ln)优选超过0.86、0.98以下。进一步优选in/(in ga ln)超过0.87、0.98以下。

[0134]

在本实施方式所涉及的晶体氧化物薄膜中,如果ga/(in ga ln)为0.01以上,则能够将晶体粒径控制得较小。

[0135]

在本实施方式所涉及的晶体氧化物薄膜中,如果ga/(in ga ln)小于0.11,则在小型tft驱动时作为载体的电子难以受到氧化物薄膜中的ln(例如sm)所形成的势垒的影响,结果可得到陷阱限制传导区域特性优异的小型tft。

[0136]

ga/(in ga ln)优选为0.01以上、小于0.11,进一步优选为0.03以上、小于0.10。

[0137]

在本实施方式所涉及的晶体氧化物薄膜中,如果ln/(in ga ln)为0.01以上,则在氧化物薄膜退火后在相对于支承体垂直的方向上形成柱状晶体,结果为可得到陷阱限制传导区域特性优异的小型tft。

[0138]

在本实施方式所涉及的晶体氧化物薄膜中,如果ln/(in ga ln)小于0.04,则在小型tft驱动时作为载体的电子难以受到氧化物薄膜中的ln(例如sm)所形成的势垒的影响,结果可得到陷阱限制传导区域特性优异的小型tft。

[0139]

ln/(in ga ln)优选为0.01以上、小于0.04,进一步优选为0.02以上、小于0.04。

[0140]

本实施方式所涉及的晶体氧化物薄膜中使用的ln元素在6s轨道上具有最外层电子,因此通常包含ln元素的化合物各自的电气性质相互相似而为人所知。因此,ln元素没有特别限定,优选为sm元素(钐元素)。sm元素与其它ln元素相比,即使在晶体氧化物薄膜中的含量较少,也能够形成在相对于支承体垂直的方向上延伸的柱状晶体。此外,对于作为ln元素的钐元素以外的元素,只要具有与钐相同程度的离子半径,则可以认为其作为ln元素起到与包含钐元素的晶体氧化物薄膜同样的效果。

[0141]

在本实施方式中,在ln元素为sm元素(钐元素)的情况下,本实施方式所涉及的晶体氧化物薄膜优选满足以下述(1a)、(2a)以及(3a)表示的原子组成比的范围。

[0142]

0.85<in/(in ga sm)≤0.98

…

(1a)

[0143]

0.01≤ga/(in ga sm)<0.11

…

(2a)

[0144]

0.01≤sm/(in ga sm)<0.04

…

(3a)

[0145]

在本说明书中,“in元素为主成分”或“以铟元素为主成分”是指构成晶体氧化物薄膜或后述的溅射靶的金属元素的总原子数内50at%以上为铟元素。优选构成晶体氧化物薄膜的金属元素的总原子数内70at%以上为铟元素,更优选80at%以上为铟元素,进一步优选85at%以上为铟元素。如果构成晶体氧化物薄膜的金属元素的总原子数内50at%以上为铟元素,则在tft中采用本实施方式所涉及的晶体氧化物薄膜的情况下,能够发挥出足够高的饱和迁移率。

[0146]

能够通过icp(inductive coupled plasma:电感耦合等离子体)测量或xrf(x

‑

ray fluorescence:x射线荧光光谱)测量对各元素的存在量进行测量,从而求出晶体氧化物薄膜中的各金属元素的含量(原子比)。icp测量能够使用电感耦合等离子体发光分析装置。xrf测量能够使用薄膜荧光x射线分析装置。

[0147]

此外,小型tft元件中的晶体氧化物薄膜中的各金属元素的含量(原子比)能够通

过使用了电子显微镜的tem

‑

eds测量、使用了电感耦合等离子体发光分析装置的icp测量、以及使用了扇区型动态二次离子质量分析仪的sims分析,以2原子%以内的误差精度进行分析。首先,通过截面tem

‑

eds鉴定晶体氧化物薄膜中的金属元素,以及通过半定量分析以10原子%左右的误差范围鉴定组成比率。接着,根据半定量分析结果在20原子%的范围内制作由金属元素的原子比为已知的10种组成比率组成的标准氧化物薄膜。对于标准氧化物薄膜,将由电感耦合等离子体发光分析装置或薄膜荧光x射线分析装置测量而得的值作为组成比率的绝对值。进而,在标准氧化物薄膜的上表面,制作以与tft元件同样的材料以及同样的沟道长度形成的源电极、漏电极,将其作为标准材料,通过扇区型动态二次离子质量分析仪sims(ims 7f

‑

auto,ametek公司制)进行氧化物半导体层的分析,得到各元素的质谱强度,制作已知的元素浓度与质谱强度的标准曲线。接着,若根据使用了扇区型动态二次离子质量分析仪的sims分析得到的光谱强度,使用上述的标准曲线计算出从面板取出的实际tft元件的氧化物薄膜部分的原子比,则能够另行由薄膜荧光x射线分析装置或电感耦合等离子体发光分析装置以测量出的氧化物薄膜的原子比的2原子%以内的精度确认计算出的原子比。

[0148]

本实施方式所涉及的晶体氧化物薄膜优选包含方铁锰矿结构的晶粒。能够通过电子射线衍射来确认晶体氧化物薄膜包含方铁锰矿结构的晶粒。

[0149]

在晶体氧化物薄膜包含方铁锰矿结构的晶粒的情况下,由于方铁锰矿结构的晶粒是对称性良好的立方晶状,因此即使越过晶体晶界也能够抑制tft特性(迁移率)的降低。

[0150]

根据本实施方式所涉及的晶体氧化物薄膜,含有规定的元素(in、ga、ln以及o),平均晶体粒径d1被控制在0.05μm以上、0.5μm以下。因此,具有本实施方式所涉及的晶体氧化物薄膜的小型tft示出良好的陷阱限制传导区域特性,即使在低电压下也能够较多地流过电流。由此,能够在组装有小型tft的显示器中使开口率提高,并且使电力消耗降低。

[0151]

本发明的一方案的晶体氧化物薄膜作为用于液晶显示器以及有机el显示器等显示装置等的小型tft是有用的。

[0152]

2.晶体氧化物薄膜的制造方法

[0153]

本实施方式所涉及的晶体氧化物薄膜例如能够使用包含含in元素、ga元素以及ln元素的氧化物烧结体的溅射靶来成膜。有时将该溅射靶称为本实施方式所涉及的溅射靶。有时将本实施方式所涉及的溅射靶所包含的氧化物烧结体称为本实施方式所涉及的氧化物烧结体。

[0154]

在本实施方式所涉及的氧化物烧结体中,ln元素是从la、nd、sm、eu、gd、tb、dy、ho、er、tm、yb以及lu构成的组中选择的一种以上的元素。

[0155]

在本实施方式所涉及的氧化物烧结体中,优选in元素为主成分。

[0156]

作为本实施方式所涉及的晶体氧化物薄膜的制造方法,可例举具有使用本实施方式所涉及的溅射靶、利用溅射而成膜出氧化物薄膜的工序的制造方法。在通过溅射进行的成膜工序中,将实质上不含杂质气体的从氩以及氧构成的组中选择的1种以上的气体用作溅射气体。溅射气体中所包含的“杂质”表示并非有意添加的元素,且为对溅射性能不造成实质上的影响的微量元素。

[0157]

由溅射法得到的氧化物薄膜的原子组成比反映了溅射靶中的氧化物烧结体的原子组成比。因此,优选使用包含具有与所期望的氧化物薄膜的原子组成比相同的原子组成

比的氧化物烧结体的溅射靶进行成膜。

[0158]

在溅射法所使用的靶中,优选杂质金属为500ppm以下,更优选为100ppm以下。特别是通过使4价的sn在靶中的含量为500ppm以下、更优选为100ppm以下,从而即使靶中所包含的sn在氧化物膜中作为杂质残留,也不会在本实施方式的晶体氧化物半导体中成为电子散射源,可得到良好的tft特性。靶中的杂质金属的含量与晶体氧化物薄膜同样地能够通过icp或sims进行测量。靶中所包含的“杂质”表示在原料或制造工序中混入的并非有意添加的元素,且为对靶以及半导体的性能不造成实质上的影响的微量元素,“杂质金属”表示作为“杂质”的元素中的金属元素。

[0159]

此外,本实施方式所涉及的晶体氧化物薄膜例如也能够作为包含晶体氧化物薄膜与保护膜的层叠体的一部分来制造。

[0160]

作为该层叠体的制造方法,可例举包括以下工序的制造方法:使用本实施方式所涉及的溅射靶且将实质上不含杂质气体的从氩以及氧构成的组中选择的1种以上的气体用作溅射气体,通过溅射成膜出氧化物薄膜的工序;不对所述氧化物薄膜进行氧化气氛下的加热处理,在所述氧化物薄膜之上形成保护膜的工序;对包含所述氧化物薄膜以及所述保护膜的层叠体实施加热处理的工序。

[0161]

使用以氧化铟为主成分的溅射靶且将实质上不含杂质的从氩以及氧构成的组中选择的1种以上的气体用作溅射气体,通过溅射成膜从而得到的氧化物薄膜是无定形的氧化物薄膜。利用光刻将该氧化物薄膜图案化为岛状,在形成保护膜之前加热而使其晶化,由此能够得到表面晶体具有单一的晶体取向的晶体氧化物薄膜。

[0162]

以下,对各工序进行说明。

[0163]

(氧化物薄膜成膜工序)

[0164]

在氧化物薄膜成膜工序中,使用本实施方式所涉及的溅射靶且将实质上不含杂质气体的从氩以及氧构成的组中选择的1种以上的气体用作溅射气体,通过溅射成膜出氧化物薄膜(例如,参照图2a)。在图2a中示出在玻璃基板81上形成了氧化物薄膜83的状态。

[0165]

溅射气体“实质上不含杂质气体”是指,除了伴随着气体的插入而带入的吸附水、以及腔室的泄漏或吸附气体等不能去除的气体(不可避免的杂质气体)以外,不主动投入氩以及氧以外的杂质气体。在本实施方式中,作为溅射气体,例如能够使用市售的高纯度氩以及高纯度氧的混合气体。若可以实现,则优选将杂质从溅射气体中去除。

[0166]

溅射气体中的杂质气体的比例优选为0.1体积%以下,更优选为0.05体积%以下。如果杂质气体的比例为0.1体积%以下,则顺利推进氧化物薄膜的晶化。

[0167]

高纯度氩以及高纯度氧的纯度优选为99体积%以上,更优选为99.9体积%以上,进一步优选为99.99体积%以上。

[0168]

氩以及氧的混合气体中的氧分压优选为超过0体积%、10体积%以下,更优选为超过0体积%、5体积%以下。如果氧分压超过0体积%、10体积%以下,则在加热时容易晶化而半导体化。能够通过改变氧分压来调节氧化物薄膜的氧化程度即晶化程度。氧分压根据需要适当选择即可。

[0169]

溅射中的磁通密度优选为700g以上。如果溅射中的磁通密度为700g以上,则能够提高溅射成膜时的等离子体的密度,氧化物薄膜的密度提高,在图案化后的退火时容易形成晶核,结果能够将晶粒控制得较小。

[0170]

即使溅射中的磁通密度不足700g,也能够通过使溅射时的输出密度为2.5kw/cm2以上来提高溅射成膜时的等离子体的密度,结果能够将氧化物薄膜中的晶粒控制得较小。

[0171]

在氧化物薄膜成膜工序中,优选将本实施方式所涉及的溅射靶安装在rf磁控溅射装置或dc磁控溅射装置进行溅射。

[0172]

本实施方式所涉及的溅射靶优选含有铟元素、镓元素以及镧系元素。

[0173]

在溅射靶中,通过不仅添加铟元素还添加镓元素以及镧系元素,能够在形成氧化物薄膜时形成均匀的无定形结构。

[0174]

本实施方式所涉及的溅射靶通过含有铟元素、镓元素以及镧系元素(例如钐元素),从而即使未将稀有气体以及氧以外的物质(例如水等)导入溅射气体,也能够在成膜时得到无定形的氧化物薄膜。通过利用后述的加热处理工序对该氧化物薄膜进行加热,能够使柱状的晶体相对于支承体生长。通过将如上所述地成膜而得的氧化物薄膜应用于小型tft,在驱动时电子载体的注入性优异,结果可得到陷阱限制传导区域特性优异的小型tft元件。

[0175]

(保护膜形成工序)

[0176]

在晶体氧化物薄膜之上形成保护膜的情况下,优选在对得到的氧化物薄膜进行了氧化气氛下的加热处理后,在氧化物薄膜之上形成保护膜。通过在保护膜形成前进行退火使氧在氧化物薄膜的表面共有,由此在保护膜形成后界面电子陷阱能级较小,可得到陷阱限制传导区域特性优异的小型tft元件。

[0177]

作为保护膜的材料,可例举例如sio2、sin

x

、sion

x

、al2o3以及ga2o3等。保护膜的厚度通常为50nm以上、500nm以下。

[0178]

作为保护膜的成膜方法,例如可例举cvd法、溅射法以及涂布法等。在图2b中示出在图2a的氧化物薄膜83上形成了sio2膜85的状态。

[0179]

(加热处理工序)

[0180]

接着,在成膜出氧化物薄膜后或成膜出保护膜后进行加热处理。有时将该加热处理称为退火。

[0181]

加热处理的温度优选为250℃以上、500℃以下,更优选为280℃以上、470℃以下,进一步优选为300℃以上、450℃以下。

[0182]

如果氧化物薄膜成膜后的加热处理温度为250℃以上,则氧化物薄膜容易晶化。

[0183]

如果氧化物薄膜成膜后的加热处理温度为500℃以下,则能够防止晶体异常生长而使晶粒变大,能够将晶体粒径控制得较小。

[0184]

加热处理工序中的加热时间优选为0.1小时以上、5小时以下,更优选为0.3小时以上、3小时以下,进一步优选为0.5小时以上、2小时以下。

[0185]

如果加热处理工序中的加热时间为0.1小时以上,则不存在不发生晶化这样的情况,氧化物薄膜容易晶化。

[0186]

如果加热处理工序中的加热时间为5小时以下,则经济性优异。

[0187]“加热时间”是指在加热处理时维持规定的最高温度的时间(保持时间)。

[0188]

加热处理工序中的升温速度优选为2℃/分钟以上、40℃/分钟以下,更优选为3℃/分钟以上、20℃/分钟以下。

[0189]

如果加热处理工序中的升温速度为2℃/分钟以上,则与小于1℃/分钟的情况相

比,氧化物薄膜的制造效率提高。

[0190]

如果加热处理工序中的升温速度为40℃/分钟以下,则在晶化时金属元素均匀扩散,能够形成金属不在晶界处偏析的晶体。

[0191]

此外,加热处理工序中的升温速度与根据炉的设定温度与设定时间计算出的值不同,是将氧化物薄膜的实际温度除以时间而得的值。氧化物薄膜的实际温度例如能够通过用热电偶测量炉中的氧化物薄膜的1cm以内的区域来求出。

[0192]

加热处理工序优选在大气气氛下实施。

[0193]

加热处理工序优选在氧化物薄膜的图案化之后进行。通过在图案化之后进行,能够使在成膜时存在于膜中的多余的氧以及在图案化时附着的有机物脱离,同时促进晶化。其结果为,能够形成在晶粒内没有有机物或多余的氧的、晶体缺陷较少的膜,能够形成没有电子陷阱而具有良好的传导特性的氧化物薄膜。

[0194]

优选在形成栅极绝缘膜后且形成接触孔前、或者在形成栅极绝缘膜以及接触孔后,进一步进行加热处理工序。有时将在氧化物薄膜的图案化后进行的加热处理工序称为第1加热处理工序,将在形成栅极绝缘膜后且形成接触孔前、或者在形成栅极绝缘膜以及接触孔后进行的加热处理工序称为第2加热处理工序。第2加热处理工序优选在比第1加热处理工序高的退火温度下进行。通过在形成栅极绝缘膜后进行退火,栅极绝缘膜中所包含的氢扩散到氧化物薄膜,通过羟基使存在于氧化物薄膜表面的晶体缺陷终止,结果能够形成电子陷阱少且具有良好的传导特性的氧化物薄膜。

[0195]

根据本实施方式所涉及的晶体氧化物薄膜的制造方法,能够得到将平均晶体粒径控制在0.05μm以上、0.5μm以下的晶体氧化物薄膜。其结果为,具有由本实施方式所涉及的晶体氧化物薄膜的制造方法成膜而得的晶体氧化物薄膜的小型tft示出良好的陷阱限制传导区域特性。

[0196]

3.层叠体

[0197]

本实施方式所涉及的层叠体具有本实施方式所涉及的晶体氧化物薄膜与支承晶体氧化物薄膜的支承体。

[0198]

在图1中示出作为本实施方式的一例的层叠体10的截面概略图。层叠体10具有晶体氧化物薄膜11与支承晶体氧化物薄膜11的支承体12。

[0199]

在层叠体10中,优选为,支承体12的表面与晶体氧化物薄膜11中的晶体晶界所成的平均晶界角度θsub为70

°

以上、110

°

以下,晶体氧化物薄膜11中的晶体晶界彼此的平均间隔d2为0.01μm以上、0.5μm以下。

[0200]

通过使支承体12的表面与晶体氧化物薄膜11中的晶体晶界所成的平均晶界角度θsub以及晶体晶界彼此的平均间隔d2满足上述范围,能够使晶体晶界相对于与晶体氧化物薄膜11相接的支承体12的表面密集地存在。其结果为,在晶体氧化物薄膜11与作为支承体的电极(例如,源电极)相接的情况下,晶体晶界相对于该电极面密集地存在。其结果为,即使在与电极的接触区域较狭小的情况下(例如,小型tft),也能够确保向晶体氧化物薄膜的电子注入,能够抑制迁移率的降低。

[0201]

4.薄膜晶体管以及电子设备

[0202]

本实施方式所涉及的薄膜晶体管(tft)具有电极、晶体氧化物薄膜与绝缘膜。作为电极,可例举源电极、漏电极以及栅电极,作为绝缘膜,可例举栅极绝缘膜以及保护膜。

[0203]

在沿着本实施方式的薄膜晶体管的沟道长度方向切出的截面tem观察中,电极与晶体氧化物薄膜的接触区域长度ls以及晶体氧化物薄膜中的晶体晶界彼此的平均间隔d2满足式(4)以及式(5)的关系。

[0204]

1μm≤ls≤50μm

…

(4)

[0205]

10≤ls/d2≤1000

…

(5)

[0206]

在本实施方式所涉及的薄膜晶体管中,优选晶体氧化物薄膜与作为电极的源电极相接。优选与源电极相接的接触区域长度ls满足上述式(4)的关系。进而,优选源电极和与源电极相接的晶体氧化物薄膜满足上述式(5)的关系。

[0207]

在本实施方式所涉及的薄膜晶体管中,晶体氧化物薄膜优选为本实施方式所涉及的晶体氧化物薄膜。

[0208]

在薄膜晶体管中,通过满足上述式(4)以及式(5)的关系,即使电极与氧化物半导体层的接触区域较小,也示出优异的迁移率。

[0209]

在现有技术中制作的tft中,使用金属掩模在氧化物薄膜之上形成有源电极以及漏电极,结果例如源电极与氧化物薄膜的接触区域长度为100μm左右。因此,即使氧化物薄膜中的晶体粒径为1μm以上,在与源电极的接触区域中也存在100个左右的晶体晶界,作为导电区域的晶体晶界以足够的数目相对于源电极相接,从迁移率的观点出发,未成为较大的问题。

[0210]

但是,近年来,为了提高oled等显示器中的开口率,tft的元件尺寸变小。因此,在不通过以往那样使用了金属掩模的成膜,而是通过光刻进行图案化而得的小型tft中,需要进行特性控制。在小型tft结构中,缩短源电极与氧化物薄膜的接触区域长度。为了即使在接触区域长度较短的tft结构中也得到充分的迁移率,需要在与源电极的接触区域中存在足够数目的晶体晶界,根据本实施方式所涉及的tft,由于满足上述式(4)以及式(5),因此迁移率优异。

[0211]

接触区域长度ls更优选为满足下述式(4a),进一步优选为满足下述式(4b)。

[0212]

2μm≤ls≤50μm

…

(4a)

[0213]

2μm≤ls≤10μm

…

(4b)

[0214]

ls/d2更优选为满足下述式(5a),进一步优选为满足下述式(5b)。

[0215]

10≤ls/d2≤1000

…

(5a)

[0216]

10≤ls/d2≤250

…

(5b)

[0217]

本实施方式所涉及的薄膜晶体管优选具有源电极、漏电极、栅电极、栅极绝缘膜、保护绝缘膜以及氧化物半导体层。

[0218]

氧化物半导体层位于栅极绝缘膜与保护绝缘膜之间。氧化物半导体层包含本实施方式所涉及的晶体氧化物薄膜。

[0219]

作为本实施方式所涉及的tft的构成,例如能够采用以往公知的构成。

[0220]

本实施方式所涉及的tft能够通过采用本实施方式所涉及的晶体氧化物薄膜的制造方法来制造。即,包括如下工序的制造方法:使用本实施方式所涉及的溅射靶且将实质上不含杂质气体的从氩以及氧构成的组中选择的1种以上的气体用作溅射气体,通过溅射成膜出氧化物薄膜的工序(有时称为成膜工序);以及对氧化物薄膜实施加热处理的工序(有时称为加热处理工序)。成膜工序以及加热处理工序的各条件等如上所述。源电极、漏电极、

栅电极以及栅极绝缘膜能够通过公知的材料以及形成方法形成。

[0221]

本实施方式所涉及的晶体氧化物薄膜示出良好的陷阱限制传导区域特性。通过将这样的晶体氧化物薄膜用于tft的氧化物半导体层(沟道层),从而具有较高的陷阱限制传导区域特性。此处的陷阱限制传导区域特性是施加vg=5v时的迁移率。施加vg=0.1v时的迁移率作为线性迁移率求出,施加vg=10v时或施加vg=20v时的迁移率将饱和迁移率定义为指标。

[0222]

具体而言,生成施加了各vd时的传递特性id

‑

vg图表,计算各vg的跨导(gm),使用线性区域或饱和区域的公式求出迁移率,从而能够计算出陷阱限制传导区域特性。电流id是源电极、漏电极间的电流,电压vd是施加在源电极与漏电极之间的电压(漏极电压),电压vg是施加在源电极与栅电极之间的电压(栅极电压)。陷阱限制传导区域特性优选为17cm2/(v

·

s)以上,进一步优选为19cm2/(v

·

s)以上。

[0223]

此外,本实施方式所涉及的晶体氧化物薄膜还能够在其中一个面配置金属、ito或izo等欧姆电极,在另一个面配置功函数为4.8ev以上的金属或氧化物电极等肖特基电极,由此构成肖特基势垒二极管。

[0224]

本实施方式所涉及的薄膜晶体管的形状没有特别限定,但优选背沟道蚀刻型晶体管、蚀刻阻挡层型晶体管、或者顶栅型晶体管等。

[0225]

具体的薄膜晶体管的例子在图3以及图4示出。

[0226]

如图3所示,薄膜晶体管100具备硅晶圆20、栅极绝缘膜30、氧化物薄膜40、源电极50、漏电极60以及层间绝缘膜70、70a。

[0227]

硅晶圆20是栅电极,以夹着栅极绝缘膜30而与氧化物薄膜40相对置的方式设置在栅极绝缘膜30。栅极绝缘膜30是阻断栅电极与氧化物薄膜40导通的绝缘膜,设置在硅晶圆20上,且设置在氧化物薄膜40的一个面上。

[0228]

氧化物薄膜40是沟道层,设置在栅极绝缘膜30上。氧化物薄膜40使用本实施方式所涉及的晶体氧化物薄膜。在本实施方式中,在薄膜晶体管100为小型tft的情况下,作为相对于源电极50以及漏电极60为沟道层的氧化物薄膜40的沟道长度(l长度)为1μm以上、50μm以下,沟道宽度(w长度)为1μm以上、80μm以下。

[0229]

源电极50以及漏电极60是用于使源极电流以及漏极电流流过氧化物薄膜40的导电端子,分别以与氧化物薄膜40的两端附近接触的方式设置,与氧化物薄膜40电连接。

[0230]

层间绝缘膜70是阻断源电极50以及漏电极60与氧化物薄膜40之间的接触部分以外的部分的导通的绝缘膜。

[0231]

层间绝缘膜70a是阻断源电极50以及漏电极60与氧化物薄膜40之间的接触部分以外的部分的导通的绝缘膜。层间绝缘膜70a也是阻断源电极50与漏电极60之间的导通的绝缘膜。层间绝缘膜70a也是沟道层保护层。

[0232]

如图4所示,虽然薄膜晶体管100a的结构与薄膜晶体管100相同,但是在将源电极50以及漏电极60设置为与栅极绝缘膜30和氧化物薄膜40双方接触这一点上与薄膜晶体管100不同。薄膜晶体管100a还在以覆盖栅极绝缘膜30、氧化物薄膜40、源电极50以及漏电极60的方式一体地设置层间绝缘膜70b这一点上与薄膜晶体管100不同。

[0233]

对于形成漏电极60、源电极50以及栅电极的材料没有特别限制,能够任意选择通常所使用的材料。在图3以及图4所例举的例子中,将硅晶圆作为基板使用,硅晶圆也作为电

极发挥作用,但电极材料不限定于硅。

[0234]

例如能够使用氧化铟锡(ito)、氧化铟锌(izo)、zno以及sno2等的透明电极,或者al、ag、cu、cr、ni、mo、au、ti以及ta等的金属电极,或者包含这些的合金的金属电极或层叠电极。

[0235]

此外,在图3以及图4中,也可以在玻璃等的基板上形成栅电极。

[0236]

形成层间绝缘膜70、70a、70b的材料也没有特别限制,能够任意选择通常使用的材料。作为形成层间绝缘膜70、70a、70b的材料,具体而言,例如能够使用sio2、sin

x

、al2o3、ta2o5、tio2、mgo、zro2、ceo2、k2o、li2o、na2o、rb2o、sc2o3、y2o3、hfo2、cahfo3、pbtio3、bata2o6、srtio3、sm2o3以及aln等化合物。

[0237]

在本实施方式所涉及的薄膜晶体管为背沟道蚀刻型(底栅型)的情况下,优选在漏电极、源电极以及沟道层上设置保护膜。通过设置保护膜,即便在长时间驱动tft的情况下,耐久性也容易提高。另外,在顶栅型的tft的情况下,例如是在沟道层上形成栅极绝缘膜的结构。

[0238]

保护膜或者绝缘膜例如能够通过cvd形成,此时存在进行高温度的工艺的情况。此外,保护膜或者绝缘膜在刚刚成膜后含有杂质气体的情况较多,从而优选进行加热处理(退火处理)。利用加热处理去除杂质气体,由此成为稳定的保护膜或绝缘膜,容易形成耐久性高的tft元件。此外,通过在形成栅极绝缘膜后进行退火,栅极绝缘膜中所包含的氢扩散到氧化物薄膜,通过羟基使存在于氧化物薄膜表面的晶体缺陷终止,结果能够形成电子陷阱少且具有良好的传导特性的氧化物薄膜。

[0239]

由于通过使用本实施方式所涉及的氧化物薄膜,变得难以受到cvd工艺中温度的影响以及之后的加热处理造成的影响,因此即便在形成保护膜或绝缘膜的情况下也能够提高tft特性的稳定性。

[0240]

阈值电压(vth)优选为

‑

3.0v以上、3.0v以下,更优选为

‑

2.0v以上、2.0v以下,进一步优选为

‑

1.0v以上、1.0v以下。若阈值电压(vth)为

‑

3.0v以上、3.0v以下,则可通过在tft搭载vth校正电路来进行向vth=0v的校正。将由此得到的tft搭载于面板时,能够不引起亮度不均以及烧屏地驱动显示器。

[0241]

阈值电压(vth)能够根据传递特性的图表以id=10

‑9a下的vg来定义。

[0242]

通断比(on

‑

off比)优选为106以上、10

12

以下,更优选为107以上、10

11

以下,进一步优选为108以上、10

10

以下。若通断比为106以上,则能够驱动液晶显示器。若通断比为10

12

以下,则能够驱动对比度较大的有机el元件。此外,若通断比为10

12

以下,则能够使断开(off)电流为10

‑

12

a以下,在将薄膜晶体管用于cmos图像传感器的传输晶体管或复位晶体管的情况下,能够延长图像的保持时间或提高灵敏度。

[0243]

通过将vg=

‑

10v的id的值设为断开电流值,将vg=20v的id的值设为导通(on)电流值,确定比[导通电流值/断开电流值]从而求出通断比。

[0244]

断开电流值优选为10

‑

10

a以下,更优选为10

‑

11

a以下,进一步优选为10

‑

12

a以下。若断开电流值为10

‑

10

a以下,则能够驱动对比度较大的有机el。此外,在用于cmos图像传感器的传输晶体管或复位晶体管的情况下,能够延长图像的保持时间或提高灵敏度。

[0245]

<量子隧道场效应晶体管>

[0246]

本实施方式所涉及的晶体氧化物薄膜还能够用于量子隧道场效应晶体管(fet)。

[0247]

在图5示出本实施方式所涉及的量子隧道场效应晶体管(fet)的示意图(纵剖视图)。

[0248]

量子隧道场效应晶体管501具备p型半导体层503、n型半导体层507、栅极绝缘膜509、栅电极511、源电极513以及漏电极515。

[0249]

依次将p型半导体层503、n型半导体层507、栅极绝缘膜509以及栅电极511进行层叠。

[0250]

源电极513设置在p型半导体层503上。漏电极515设置在n型半导体层507上。

[0251]

p型半导体层503是p型的iv族半导体层,在此是p型硅层。

[0252]

n型半导体层507在此是用于本实施方式所涉及的图像传感器的n型的氧化物薄膜。源电极513以及漏电极515是导电膜。

[0253]

虽然在图5中未图示,但也可以在p型半导体层503上形成绝缘层。在该情况下,p型半导体层503与n型半导体层507经由将绝缘层局部开口而得的区域即接触孔连接。虽然在图5中未图示,但量子隧道场效应晶体管501也可以具备覆盖其上表面的层间绝缘膜。

[0254]

量子隧道场效应晶体管501是进行电流的开关的量子隧道场效应晶体管(fet),通过栅电极511的电压控制在由p型半导体层503与n型半导体层507形成的能量势垒中隧穿的电流。在该结构中,构成n型半导体层507的氧化物半导体的带隙变大,能够减小断开电流。

[0255]

在图6示出另一方案所涉及的量子隧道场效应晶体管501a的示意图(纵剖视图)。

[0256]

量子隧道场效应晶体管501a的构成与量子隧道场效应晶体管501的构成相同,但在p型半导体层503与n型半导体层507之间形成有氧化硅层505这一点上不同。通过具有氧化硅层,能够减小断开电流。

[0257]

氧化硅层505的厚度优选为10nm以下。通过使其厚度为10nm以下,能够防止隧道电流不流动、或者形成的能量势垒难以形成或势垒高度发生变化,从而可防止隧穿电流降低或变化。氧化硅层505的厚度优选为8nm以下,更优选为5nm以下,进一步优选为3nm以下,更进一步优选为1nm以下。

[0258]

在图7示出在p型半导体层503与n型半导体层507之间形成有氧化硅层505的部分的tem照片。

[0259]

在量子隧道场效应晶体管501以及501a中,n型半导体层507也是n型氧化物半导体。

[0260]

构成n型半导体层507的氧化物半导体也可以是非晶质。通过使其为非晶质,可用草酸等有机酸进行蚀刻,与其它层的蚀刻速度的差变大,也不会对布线等的金属层造成影响,能够良好地进行蚀刻。

[0261]

构成n型半导体层507的氧化物半导体也可以是晶体。通过使构成n型半导体层507的氧化物半导体为晶体,与非晶质的情况相比带隙变大且能够减小断开电流。由于也能够使功函数增大,因此容易对隧穿由p型iv族半导体材料与n型半导体层507形成的能量势垒的电流进行控制。

[0262]

量子隧道场效应晶体管501的制造方法没有特别限定,能够例示以下的方法。

[0263]

首先,如图8a所示,在p型半导体层503上形成绝缘膜505a,并通过使用蚀刻等将绝缘膜505a的一部分开口来形成接触孔505b。

[0264]

接着,如图8b所示,在p型半导体层503以及绝缘膜505a上形成n型半导体层507。此

时,经由接触孔505b连接p型半导体层503与n型半导体层507。

[0265]

接着,如图8c所示,在n型半导体层507上依次形成栅极绝缘膜509以及栅电极511。

[0266]

接着,如图8d所示,设置层间绝缘膜519以覆盖绝缘膜505a、n型半导体层507、栅极绝缘膜509以及栅电极511。

[0267]

接着,如图8e所示,通过将p型半导体层503上的绝缘膜505a以及层间绝缘膜519的一部分开口来形成接触孔519a,并在接触孔519a设置源电极513。

[0268]

进而,如图8e所示,通过将n型半导体层507上的栅极绝缘膜509以及层间绝缘膜519的一部分开口来形成接触孔519b,并在接触孔519b形成漏电极515。

[0269]

能够通过以上的步骤制造量子隧道场效应晶体管501。

[0270]

另外,在p型半导体层503上形成n型半导体层507后,以150℃以上、600℃以下的温度进行热处理,由此能够在p型半导体层503与n型半导体层507之间形成氧化硅层505。通过追加该工序,能够制造量子隧道场效应晶体管501a。

[0271]

本实施方式所涉及的tft能够适宜地用于太阳能电池、液晶元件、有机电致发光元件、无机电致发光元件等显示元件或功率半导体器件、触控面板等电子设备。

[0272]

本实施方式所涉及的薄膜晶体管也能够应用于场效应型晶体管、逻辑电路、存储电路以及差动放大电路等各种集成电路,能够将这些应用于电子设备等。进而,本实施方式所涉及的薄膜晶体管除了场效应型晶体管以外,还能够适用于静电感应型晶体管以及肖特基势垒型晶体管。

[0273]

本实施方式所涉及的薄膜晶体管能够适宜地用于便携用或车载用显示装置等显示装置以及固体拍摄元件等。进而,本实施方式所涉及的薄膜晶体管还能够适宜地用作医疗用途的x射线图像传感器用平板探测器用的晶体管。

[0274]

此外,本实施方式所涉及的晶体氧化物薄膜还能够适用于肖特基二极管、可变电阻型存储器以及电阻元件。

[0275]

以下,对将本实施方式所涉及的薄膜晶体管用于显示装置以及固体拍摄元件的情况进行说明。

[0276]

首先,参照图9对将本实施方式所涉及的薄膜晶体管用于显示装置的情况进行说明。

[0277]

图9a是本实施方式所涉及的显示装置的俯视图。图9b是用于说明在本实施方式所涉及的显示装置的像素部中应用液晶元件的情况下的像素部的电路的电路图。此外,图9c是用于说明在本实施方式所涉及的显示装置的像素部中应用有机el元件的情况下的像素部的电路的电路图。

[0278]

配置于像素部的晶体管能够使用本实施方式所涉及的薄膜晶体管。由于本实施方式所涉及的薄膜晶体管容易设为n沟道型,因此将能够由n沟道型晶体管构成的驱动电路的一部分形成在与像素部的晶体管相同的基板上。通过在像素部或驱动电路中使用本实施方式所示的薄膜晶体管,能够提供可靠性高的显示装置。

[0279]

在图9a示出有源矩阵型显示装置的俯视图的一例。在显示装置的基板300上形成有像素部301、第1扫描线驱动电路302、第2扫描线驱动电路303、信号线驱动电路304。在像素部301中,多条信号线从信号线驱动电路304延伸配置,多条扫描线从第1扫描线驱动电路302以及第2扫描线驱动电路303延伸配置。在扫描线与信号线的交叉区域分别以矩阵状设

置有具有显示元件的像素。显示装置的基板300经由fpc(flexible printed circuit:柔性印刷电路板)等连接部而与定时控制电路(也称为控制器、控制ic)连接。

[0280]

在图9a中,第1扫描线驱动电路302、第2扫描线驱动电路303、信号线驱动电路304形成在与像素部301相同的基板300上。因此,设置在外部的驱动电路等部件的数量减少,所以能够实现成本的降低。此外,在基板300外部设置有驱动电路的情况下,需要使布线延伸,布线间的连接数增加。在相同的基板300上设置有驱动电路的情况下,能够减少该布线间的连接数,从而能够实现可靠性的提高或者成品率的提高。

[0281]

此外,在图9b示出像素的电路构成的一例。在此,示出能够应用于va型液晶显示装置的像素部的像素部的电路。

[0282]

该像素部的电路能够应用于在一个像素中具有多个像素电极的构成。各个像素电极与不同的晶体管连接,各晶体管构成为能够通过不同的栅极信号进行驱动。由此,能够独立地对施加于多畴设计的像素的各个像素电极的信号进行控制。

[0283]

以能够向晶体管316的栅极布线312与晶体管317的栅极布线313提供不同的栅极信号的方式使得两者分离。另一方面,作为数据线发挥功能的源电极或漏电极314在晶体管316与晶体管317中共用。晶体管316与晶体管317能够使用本实施方式所涉及的晶体管。由此,能够提供可靠性高的液晶显示装置。

[0284]

第1像素电极与晶体管316电连接,第2像素电极与晶体管317电连接。第1像素电极与第2像素电极分离。第1像素电极与第2像素电极的形状没有特别限定。例如,只要使第1像素电极为v字状即可。

[0285]

晶体管316的栅电极与栅极布线312连接,晶体管317的栅电极与栅极布线313连接。对栅极布线312与栅极布线313提供不同的栅极信号,使晶体管316与晶体管317的动作定时不同,从而能够控制液晶的取向。

[0286]

此外,也可以利用电容布线310、作为电介质发挥功能的栅极绝缘膜、与第1像素电极或第2像素电极电连接的电容电极来形成保持电容。

[0287]

多畴结构在一个像素中具备第1液晶元件318与第2液晶元件319。第1液晶元件318由第1像素电极、对置电极与其间的液晶层构成,第2液晶元件319由第2像素电极、对置电极与其间的液晶层构成。

[0288]

像素部并不限定于图9b所示的构成。也可以在图9b所示的像素部追加开关、电阻元件、电容元件、晶体管、传感器或逻辑电路。

[0289]

在图9c示出像素的电路构成的另一例。在此,示出使用有机el元件的显示装置的像素部的结构。

[0290]

图9c是示出可应用的像素部320的电路的一例的图。在此,示出在一个像素中使用两个n沟道型晶体管的例子。本实施方式所涉及的晶体氧化物薄膜能够用于n沟道型的晶体管的沟道形成区域。该像素部的电路能够应用数字时间灰度级驱动。

[0291]

开关用晶体管321以及驱动用晶体管322能够使用本实施方式的薄膜晶体管。由此,能够提供可靠性较高的有机el显示装置。

[0292]

像素部的电路的构成并不限定于图9c所示的构成。也可以在图9c所示的像素部的电路中追加开关、电阻元件、电容元件、传感器、晶体管或逻辑电路。

[0293]

此外,在使用了本实施方式所涉及的薄膜晶体管的显示装置中,也可以搭载有si

类晶体管与本实施方式的晶体氧化物晶体管双方。

[0294]

以上是对将本实施方式所涉及的薄膜晶体管用于显示装置的情况的说明。

[0295]

接着,参照图10对将本实施方式所涉及的薄膜晶体管用于固体拍摄元件的情况进行说明。

[0296]

cmos(complementary metal oxide semiconductor:互补金属氧化物半导体)图像传感器是在信号电荷蓄积部保持电位,并将该电位经由放大晶体管输出至垂直输出线的固体拍摄元件。若在cmos图像传感器所包含的复位晶体管以及/或者传输晶体管中存在漏电流,则由于该漏电流引起充电或放电,使信号电荷蓄积部的电位发生变化。若信号电荷蓄积部的电位发生变化,则放大晶体管的电位也变化,变成偏离原本的电位的值,导致所拍摄的影像劣化。

[0297]

对将本发明的一方案所涉及的薄膜晶体管应用于cmos图像传感器的复位晶体管以及传输晶体管的情况下的动作的效果进行说明。放大晶体管可以应用薄膜晶体管以及体晶体管中的任一个。

[0298]

图10是示出cmos图像传感器的像素构成的一例的图。像素由作为光电转换元件的光电二极管3002、传输晶体管3004、复位晶体管3006、放大晶体管3008以及各种布线构成,以矩阵状配置有多个来构成传感器。也可以设置与放大晶体管3008电连接的选择晶体管。在晶体管附图标记中标记的“os”表示氧化物半导体(oxide semiconductor),“si”表示硅,表示应用于各个晶体管时优选的材料。对于以后的附图也同样如此。

[0299]

光电二极管3002被连接至传输晶体管3004的源极侧,在传输晶体管3004的漏极侧形成有信号电荷蓄积部3010(也被称为fd:floating diffusion(浮动扩散))。在信号电荷蓄积部3010连接有复位晶体管3006的源极以及放大晶体管3008的栅极。作为另一构成,也能够删除复位电源线3110。例如,还有使复位晶体管3006的漏极不与复位电源线3110连接而是与电源线3100或垂直输出线3120连接的方法。

[0300]

另外,还可以将本发明的氧化物半导体膜用于光电二极管3002,且可以使用与用于传输晶体管3004、复位晶体管3006的氧化物半导体膜相同的材料。

[0301]

以上是对将本实施方式的薄膜晶体管用于固体拍摄元件的情况的说明。

[0302]

实施例

[0303]

以下基于实施例对本发明具体地进行说明。本发明并不受这些实施例的限定。

[0304]

<小型tft的制造>

[0305]

(实施例1)

[0306]

通过以下的工序制造薄膜晶体管。

[0307]

(1)氧化物半导体层的成膜

[0308]

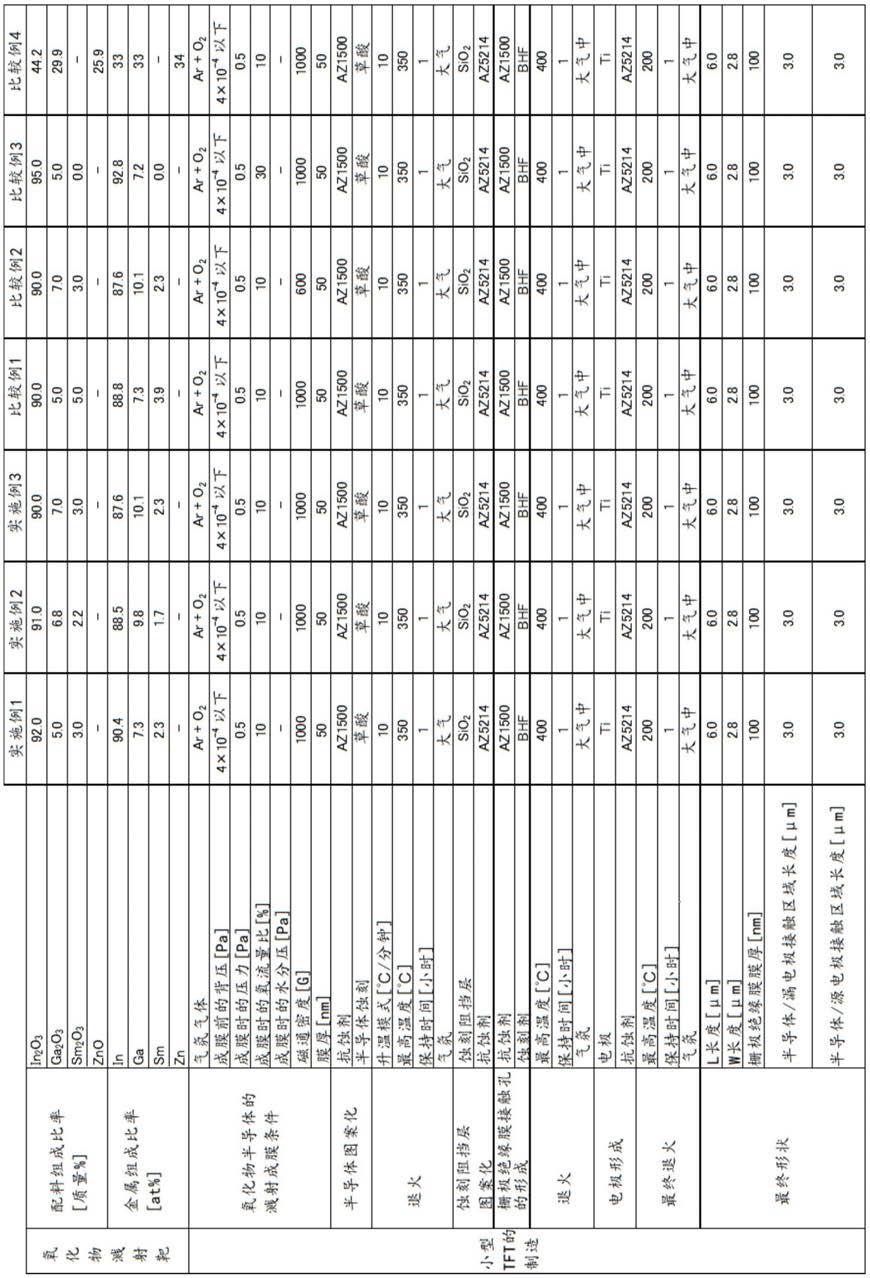

使用由表1所示的配料组成比率的原料混合物得到的溅射靶。氧化物溅射靶中的金属组成比率(单位:at%)示出在表1。

[0309]

使用该氧化物溅射靶,在厚度为100nm的带有热氧化膜(栅极绝缘膜)的硅晶圆(栅电极)上,通过溅射形成厚度为50nm的氧化物半导体薄膜(氧化物半导体层)。成膜条件如表1所示。使用高纯度氩以及高纯度氧的混合气体(杂质气体浓度:0.01体积%)作为溅射气体。

[0310]

(2)半导体图案化

[0311]

接着,通过光刻将成膜而得的氧化物半导体层图案化为岛状。

[0312]

首先,在氧化物半导体层上形成光致抗蚀剂的膜。作为光致抗蚀剂,使用az1500(az electronic materials(az电子材料)公司制)。经由以14μm

×

4μm的尺寸形成有图案的光掩模进行曝光。曝光后,用四甲基氢氧化铵(tmah)进行显影。显影后,利用草酸蚀刻氧化物半导体层。蚀刻后,剥离光致抗蚀剂,得到带有图案化后的氧化物薄膜的基板。所得到的半导体区域通过蚀刻液的回绕而变得比光掩模的图案更小,如表1以及图11所示,为12μm

×

2.8μm的尺寸。

[0313]

(3)退火

[0314]

接着,将带有图案化后的氧化物薄膜的基板放入炉中,在大气中以10℃/分钟升温至350℃后,保持1小时。将炉的内部在350℃下保持1小时后,自然放冷,炉的内部温度恢复到室温后,从炉中取出带有氧化物薄膜的基板。

[0315]

(4)蚀刻阻挡层图案化

[0316]

接着,在退火后的带有氧化物薄膜的基板的半导体图案化面上旋涂图像反转抗蚀剂。作为图像反转抗蚀剂,使用az5214(az electronic materials(az电子材料)公司制)。旋涂后,使用以6μm

×

6μm的尺寸形成有图案的光掩模进行曝光。在翻转烘烤工序后将图像反转抗蚀剂az5214全面曝光,用tmah显影。对于带有图案化后的抗蚀剂的基板,通过溅射成膜出膜厚为100nm的sio2膜。溅射条件如下所述。

[0317]

基板温度:25℃

[0318]

极限压力:8.5

×

10

‑5pa

[0319]

气氛气体:ar 02(02流量30%)

[0320]

溅射压力(总压):0.4pa

[0321]

接通电流:rf100w

[0322]

s(基板)―t(靶)间距离:70mm

[0323]

然后,将成膜出sio2膜的基板在丙酮中剥离(lift

‑

off),从而将sio2图案化。

[0324]

(5)栅极绝缘膜接触孔的形成

[0325]

进而,对于将sio2图案化后的带氧化物薄膜的基板,使用光致抗蚀剂az1500(az electronic materials(az电子材料)公司制)经由光掩模进行曝光后,用四甲基氢氧化铵(tmah)进行显影。显影后,利用缓冲氢氟酸(bhf)对带有热氧化膜的si(硅晶圆)进行蚀刻,形成栅电极取出用的接触孔。形成接触孔后,在大气中实施400℃、1小时的退火。

[0326]

(6)源电极、漏电极的形成

[0327]

接着,使用图像反转抗蚀剂az5214以及光掩模,通过剥离(lift

‑

off)工艺对源电极、漏电极层进行图案化。经由以能够将图像反转抗蚀剂az5214图案化为表1的最终元件形状(l长度:6μm,w长度:2.8μm,源电极以及漏电极各自的ls长度:3μm)的方式形成的光掩模进行曝光,在翻转烘烤工序后全面曝光,用tmah显影。对于带有图案化后的抗蚀剂的基板,将厚度为150nm的ti层在以下的条件下成膜。

[0328]

基板温度:25℃

[0329]

极限压力:8.5

×

10

‑5pa

[0330]

气氛气体:ar

[0331]

溅射压力(总压):0.4pa

[0332]

接通电流:dc100w

[0333]

s(基板)―t(靶)间距离:70mm

[0334]

之后,将对ti层成膜后的基板在丙酮中剥离,从而将欧姆电极层图案化。

[0335]

(7)最终退火

[0336]

最后,在大气中进行200℃、1小时的退火。

[0337]

得到的元件(小型tft)的最终形状如表1所示。

[0338]

(实施例2~3)

[0339]

除了将溅射靶的配料组成比率以及小型tft制作条件如表1所示地进行变更之外,与实施例1同样地制造了实施例2~3所涉及的小型tft。

[0340]

(比较例1~4)

[0341]

除了将溅射靶的配料组成比率以及小型tft制作条件如表1所示地进行变更之外,与实施例1同样地制造了比较例1~4所涉及的小型tft。

[0342]

(实施例4~8)

[0343]

除了将溅射靶的配料组成比率以及小型tft制作条件如表2所示地进行变更之外,与实施例1同样地制造了实施例4~8所涉及的小型tft。

[0344]

(比较例5~10)

[0345]

除了将溅射靶的配料组成比率以及小型tft制作条件如表2以及表3所示地进行变更之外,与实施例1同样地制造了比较例5~10所涉及的小型tft。

[0346]

[表1]

[0347][0348]

[表2]

[0349][0350]

[表3]

[0351][0352]

<氧化物薄膜以及小型tft的评价>

[0353]

对实施例1~8以及比较例1~10所涉及的小型tft以及该小型tft所具有的氧化物薄膜的特性等进行了评价。

[0354]

评价方法如下所示,评价结果示出在表4、表5以及表6。

[0355]

(1)半导体图案化后的状态

[0356]

通过光学显微镜确认抗蚀剂剥离后的半导体图案化形状。

[0357]

在图11示出用显微镜观察抗蚀剂剥离后的半导体图案而得的像。在实施例1~3、比较例4所涉及的氧化物薄膜中,确认到没有残渣,形成有期望的图案。另一方面,在比较例3所涉及的氧化物薄膜中,确认到图案化残渣。

[0358]

(2)制作小型tft后的半导体膜的状态

[0359]

(2

‑

1)利用截面tem测量氧化物薄膜截面的晶体状态的方法

[0360]

对于tft元件中的氧化物薄膜的截面的晶体状态,使用聚焦离子束装置(fib:focused ion beam)对该氧化物薄膜进行前处理,利用透射型电子显微镜(tem:transmission electron microscope)观察该前处理后的氧化物薄膜的截面从而进行了测量。

[0361]

具体地说,首先,在相对于tft元件的氧化物半导体薄膜被图案化的区域的膜表面垂直的方向上,使用fib(日立高新技术公司制“fb2100型”)装置放入离子束,对尺寸为16μm

×

4μm的试验片进行采样。然后,对采样后的试验片,针对在沟道长度方向上从源电极或漏电极与氧化物薄膜重叠的区域的端部起朝向未重叠的区域中的3μm的区域提取两个样品。对于所提取的两个样品,在相对于沟道长度以及膜厚方向垂直的沟道宽度方向上进行ar离子铣削直至薄片的厚度达到大约100nm左右,使所提取的两个样品的厚度变薄。在由于fib加工时的离子溅射损伤而无法确认到晶粒的情况下,由ar离子铣削(gatan公司制“model691”)反复实施蚀刻直至能够在离子枪电压4kev下确认到晶粒为止。

[0362]

对于截面tem像,使用透射型电子显微镜(日本电子制“jem

‑

2800型”)设为加速电压200kv,以观察倍率200,000倍(约4μm见方的区域)、观察倍率500,000倍(约800nm见方的区域)、观察倍率2,000,000倍(约200nm见方的区域)、以及观察倍率10,000,000倍(约40nm见方的区域)实施区域的观察。

[0363]

(a)相对于薄膜表面的平均晶界角度θ

[0364]

观察氧化物薄膜的截面时的相对于薄膜表面的平均晶界角度θ能够通过解析利用截面tem观察到的晶体晶界与薄膜表面所成的角来计算。在以观察倍率200,000倍观测到的像之中,以在沟道方向上为1μm、氧化物膜厚为50nm的尺寸中观测点在薄膜晶体管中的l长度方向上不重叠的方式提取任意的3个视野,观测截面tem像。对于得到的3个视野的截面tem像,使用image metrology公司制“spip,version4.3.2.0”进行图像解析,从而计算出薄膜表面与晶体晶界所成的角。详细情况如下。

[0365]

对于截面tem图像,在晶体晶界处划出色标h0,s0,v10的线。进而,使用图像解析软件将对比度数值化,将(最大浓度

‑

最小浓度)

×

1/4的高度设定为阈值。接着,将示出阈值以下的对比度的区域定义为晶体晶界,求出各薄膜表面与晶体晶界所成的角。将得到的各薄膜表面与晶体晶界所成的角的合计值除以粒子数,进而将在3个视野中求出的角度的平均值设为相对于薄膜表面的平均晶界角度θ。

[0366]

其结果为,实施例1~8、比较例1、2、5~7为70

°

<θ<110

°

的范围。

[0367]

(b)相对于支承体的平均晶界角度θsub

[0368]

通过与相对于薄膜表面的平均晶界角度θ同样的截面tem像与解析方法,提取晶体晶界,求出相对于支承体所成的角。将得到的各支承体表面与晶体晶界所成的角的合计值除以粒子数,进而将在3个视野中求出的角度的平均值设为相对于支承体表面的平均晶界角度θsub。

[0369]

其结果为,实施例1~8、比较例1、2、5~7为70

°

<θsub<110

°

的范围。

[0370]

(c)晶体晶界的平均间隔d2[0371]

对氧化物薄膜的截面进行观察时的平均间隔d2能够通过解析利用截面tem观察到的晶粒的间隔来计算。在以观察倍率200,000倍观测到的像之中,以在沟道方向上为1μm、氧化物膜厚为50nm的尺寸中观测点在薄膜晶体管中的l长度方向上不重叠的方式提取任意的3个视野,观测截面tem像。对于得到的3个视野的截面tem像,使用image metrology公司制“spip,version4.3.2.0”进行图像解析,从而计算出晶体晶界的平均间隔d2。详细情况如下。

[0372]

对于截面tem图像,在晶体晶界处划出色标h0,s0,v10的线。进而,使用图像解析软件将对比度数值化,将(最大浓度

‑

最小浓度)

×

1/4的高度设定为阈值。接着,将示出阈值以下的对比度的区域定义为晶体晶界,求出各晶体晶界与最靠近粒子之间的间隔,设为晶体

晶界的间隔。将得到的各晶体晶界的间隔的合计值除以测量了间隔的部位的数目,将结果设为晶体晶界的平均间隔,将分别在3个视野中得到的晶体晶界的平均间隔的平均值设为d2求出。

[0373]

其结果为,在实施例1~3、7、8中,d2<0.40μm,在比较例1、2、5~7中为0.40μm<d2。

[0374]

(d)利用电子射线衍射判定无定形、晶体的方法

[0375]

对于无定形、晶体的判定方法,通过观察截面tem像,对得到的样品观察电子射线衍射图案,从而进行判断。

[0376]

具体而言,使用电子显微镜(日本电子制“jem

‑

2800型”)利用限制视场光阑以照射区域约100nmφ、加速电压200kv对在截面tem像中观察到的氧化物薄膜区域照射电子射线,将相机长度设定为2m来测量衍射图案。在以观测点在截面tem像样品中的l长度方向上不重叠的方式提取出的任意的3个视野中,将无法得到清晰的衍射点的氧化物薄膜判断为“无定形”。另一方面,将从衍射图案中观察到具有对称性的衍射点的氧化物薄膜判断为“晶体”。

[0377]

其结果为,将实施例1~8、比较例1、2、3、5~7的氧化物薄膜判断为“晶体”,将比较例4的氧化物薄膜判断为“无定形”。

[0378]

(2

‑

2)利用平面tem测量氧化物薄膜的晶体状态的方法

[0379]

对于从垂直方向观察tft元件中的氧化物薄膜的膜面而得的晶体状态,使用聚焦离子束装置(fib:focused ion beam)对该氧化物薄膜的膜面进行前处理,利用透射型电子显微镜(tem:transmission electron microscope)观察该前处理后的膜面,从而进行了测量。

[0380]

具体地说,首先,在相对于tft元件的氧化物半导体薄膜被图案化的区域的膜表面平行的方向上,使用fib(日立高新技术公司制“fb2100型”)装置放入离子束,对尺寸为12μm

×

4μm的试验片进行采样。然后,对采样后的试验片,在沟道方向上从源电极或漏电极与氧化物薄膜交叠的区域的端部起朝向未重叠的区域中提取3处2μm2(2μm

×

2μm的尺寸)的范围(样品),对于所提取的3处范围,照射镓离子束直至薄片的厚度达到大约100nm左右,使样品(提取的3处范围)的厚度变薄。使用透射型电子显微镜(日本电子株式会社制“jem

‑

2800型”)将加速电压设为200kv,分别提高倍率,直至能够观测到5个以上晶粒,实施了对平面tem像的观察。

[0381]

(e)平均晶体粒径d1[0382]

能够通过解析对3个样品由以倍率200,000倍放大而观察到的平面tem观察而得的晶粒的直径,来计算从氧化物薄膜的膜厚方向观察时的平均晶体粒径d1。使用image metrology公司制“spip,version4.3.2.0”对平面tem像进行图像解析,由此计算出平均晶体粒径d1。

[0383]

对于平面tem图像,在晶体晶界处划出色标h0,s0,v10的线。进而,使用图像解析软件将对比度数值化,将(最大浓度

‑

最小浓度)

×

1/4的高度设定为阈值。接着,将示出阈值以上的对比度的区域定义为晶粒,求出各粒子的面积。求出得到的各粒子的面积的合计值,将得到的面积除以测量的粒子的数目,从而得到平均粒子面积s1。进而,假定晶粒为圆,根据平均粒子面积s1以及式(a)求出直径,将该直径设为晶粒的平均晶体粒径。计算三个样品中的平均晶体粒径的平均值,设为最终的平均晶体粒径d1。

[0384]

[数1]

[0385][0386]

其结果为,在实施例1~8中,d1<0.50μm,在比较例1、2、5~10中,0.50μm<d1,在比较例3中,d1<0.05μm。

[0387]

(f)金属元素的偏析(利用平面tem

‑

eds测量氧化物薄膜的金属元素的偏析的方法)

[0388]

利用透射型电子显微镜(tem:transmission electron microscope)/能量分散型x射线分光法(eds:energy dispersive x

‑

ray spectroscopy)观察通过平面tem观察得到的样品的3个视野,从而测量氧化物薄膜的金属分散状态(金属元素的偏析)。

[0389]

具体而言,使用电子显微镜(日本电子制“jem

‑

2800型”),对观察了平面tem像后的氧化物薄膜区域中包含5个以上晶粒的观测范围以加速电压200kv照射电子射线,实施各元素的eds映射(eds

‑

mapping)测量。其结果为,将在各元素的映射中未在晶粒间观察到金属元素的偏向的情况判断为“无偏析”,将在映射中在每个晶粒中都观察到偏向的情况判断为“有偏析”。

[0390]

对于有无金属的偏向,通过使用image metrology公司制“spip,version4.3.2.0”对各样品、各元素的平面tem

‑

eds映射进行图像解析而数值化,从而进行判断。具体而言,首先,将各映射像的对比度数值化,用265像素

×

265像素表示。接着,对整个视野求出每1像素的平均浓度i

ave

。接下来,对平面tem像与平面tem

‑

eds映射进行比较,对来自各视野的5个以上的晶粒,在晶粒内选定各平均晶体粒径d1的1/2的尺寸见方的区域。求出所选定的区域的平均浓度i

grain

。对于通过这样的图像解析得到的平均浓度i

ave

与区域平均浓度i

grain

,将满足i

ave

<i

grain

的关系的区域在每个视野存在2处以上的情况判断为“有偏析”,将小于2处的情况判断为“无偏析”。

[0391]

由此,在实施例1~实施例3以及比较例1中未确认到偏析。另一方面,对于比较例2,通过in的eds映射的解析判断为有金属的偏析,对于比较例3,通过ga的eds映射的解析判断为有金属的偏析。

[0392]

(2

‑

3)金属组成比率

[0393]

用电感耦合等离子体发光分析装置(icp

‑

aes,株式会社岛津制作所制)对得到的样品的氧化物薄膜进行分析。

[0394]

(2

‑

4)利用电子射线衍射对晶体结构的鉴定

[0395]

通过观察利用对截面tem图像的观察得到的样品的电子射线衍射图案,评价氧化物薄膜的晶体结构是否为方铁锰矿结构。评价结果示出在表4、表5以及表6。

[0396]

具体而言,使用电子显微镜(日本电子制“jem

‑

2800型”)利用选区光阑以照射区域约100nmφ、加速电压200kv对在截面tem像中观察到的氧化物薄膜区域照射电子射线,将相机长度设定为2m来测量衍射图案。

[0397]

进而,为了鉴定晶体结构,使用电子射线衍射模拟软件reci pro(免费软件ver4.641(2019/03/04))实施in2o3的方铁锰矿结构的电子射线衍射图案的模拟。在模拟中,方铁锰矿结构的晶体结构数据使用icsd(inorganic crystal structure database:无机

晶体结构数据库)的14388,使用空间群:ia

‑

3、晶格常数:原子坐标in位点(0.250,0.250,0.250)、in位点(0.466,0.000,0.250)、o位点(0.391,0.156,0.380)。

[0398]

进而,以相机长度2mm、以11种倒易晶格向量(100)、(111)、(110)、(211)、(311)、(221)、(331)、(210)、(310)、(321)以及(230)作为入射电子射线方向实施模拟。

[0399]

对氧化物薄膜的电子射线衍射图案与得到的模拟图案比较衍射点的结果,在与11种模拟图案的任一种一致的情况下,判断为在氧化物薄膜中包含方铁锰矿结构的晶粒。

[0400]

其结果为,在实施例1~8、比较例1~3、5~7中,判断为元件内的氧化物膜的晶体结构为“方铁锰矿”结构。

[0401]

(3)小型tft特性

[0402]

对按照表1、表2以及表3的最终形状得到的小型tft元件,使用半导体参数分析仪(agilent株式会社制“b1500”)在室温、遮光环境下(屏蔽盒内)测量小型tft特性。另外,漏极电压(vd)以0.1v、10v或20v施加。对于各vd施加,使栅极电压(vg)从

‑

5v到20v以0.2v步幅测量电流值id,由此得到id

‑

vg特性。

[0403]

对于实施例1~8、比较例1~10,以表1、表2或表3所示的制作条件制作小型tft,对成为表4、表5以及表6所示的半导体膜的状态的小型tft元件,将施加vd=20v时的id

‑

vg特性示出在图31a~图35a、图37a中,将根据id

‑

vg特性求出饱和迁移率(μsat)的结果作为vg

‑

μsat特性示出在图31b~图35b、图37b中。另外,在图36中,示出与比较例3所涉及的小型tft有关的传递特性id

‑

vg图表。

[0404]

进而,将根据id

‑

vg特性计算出的各种参数(vg=0~20v中的线性迁移率的最大值、陷阱限制传导区域特性、s值、vth、漏电流)示出在表4、表5以及表6。另外,各参数的计算方法如下所述。

[0405]

(3

‑

1)

[0406]

(a)vd=0.1v、vg=0~20v中的线性迁移率的最大值

[0407]

对于施加vd=0.1v时的线性迁移率的最大值,生成id

‑

vg特性的图表,计算各vg的跨导(gm),使用线性区域的公式导出线性迁移率(μlin)。具体而言,gm通过计算。进而,通过线性区域的式(b)计算出μlin。

[0408]

μlin=(gm

·

l)/(w

·

ci

·

vd)

…

(b)

[0409]

此外,式(b)的ci是栅极绝缘膜的电容,使用基于膜厚100nm的sio2的相对介电常数3.9、真空的介电常数8.85

×

10

‑

14

[f/cm]计算出的ci=3.45

×

10

‑8[f/cm2]的值。式(b)中的l是沟道长度(l长度),w是沟道宽度(w长度)。

[0410]

进而,根据各vg

‑

μlin的图表,计算出vg=0~20v中的μlin的最大值。

[0411]

其结果为,实施例1~8、比较例7的vd=0.1v、vg=0~20v中的线性迁移率的最大值为30cm2/(v

·

s)以上,比较例1、2、4~6、8~10中的为小于30cm2/(v

·

s)。

[0412]

(b)vd=10v、vg=0~10v中的饱和迁移率的最大值

[0413]

对于施加vd=10v时的饱和迁移率的最大值,生成id

‑

vg特性的图表,计算各vg的跨导(gm),使用饱和区域的公式导出饱和迁移率(μsat)。具体而言,gm通过下述数学式(c1)计算。

[0414]

[数2]

[0415][0416]

进而,通过饱和区域的下述式(c)计算出μsat。

[0417]

μsat=(2

·

gm

·

l)/(w

·

ci)

…

(c)

[0418]

式(c)中的l是沟道长度(l长度),w是沟道宽度(w长度)。

[0419]

进而,根据各vg

‑

μsat的图表,计算出vg=0~10v中的μsat的最大值。

[0420]

(c)vd=20v、vg=0~20v中的饱和迁移率的最大值

[0421]

对于施加vd=20v时的饱和迁移率的最大值,生成id

‑

vg特性的图表,计算各vg的跨导(gm),使用饱和区域的公式导出饱和迁移率(μsat)。具体而言,通过所述数学式(c1)计算。进而,通过饱和区域的所述式(c)计算出μsat。进而,根据各vg

‑

μsat的图表,计算出vg=0~20v中的μsat的最大值。

[0422]

其结果为,实施例1~8、比较例7的vd=20v、vg=0~20v中的饱和迁移率的最大值为25cm2/(v

·

s)以上,比较例1、2、4~6、8~10中的为小于25cm2/(v

·

s)。

[0423]

(3

‑

2)陷阱限制传导区域特性

[0424]

利用通过与(3

‑

1)同样的方法求出的vg

‑

μlin(vd=0.1v)以及vg

‑

μsat(vd=10v或20v)的图表来求出陷阱限制传导区域特性。具体而言,将vg=5v的μlin或μsat定义为陷阱限制传导区域特性,在vd=0.1v中将μlin的值定义为陷阱限制传导区域特性,在vd=10v或20v中将μsat的值定义为陷阱限制传导区域特性。

[0425]

其结果为,vd=0.1v中的陷阱限制传导区域特性在实施例1~8中为16cm2/(v

·

s)以上,在比较例1、2、4~10中为小于16cm2/(v

·

s)。

[0426]

进而,vd=20v中的陷阱限制特性在实施例1~8中为23cm2/(v

·

s)以上,在比较例1、2以及4~10中为小于20cm2/(v

·

s)。

[0427]

无论在哪个vd中,实施例1~8的陷阱限制传导区域特性均高于比较例1、2、4~10,小型tft特性优异。

[0428]

(3

‑

3)s值以及阈值电压(vth)

[0429]

根据各个id

‑

vg特性的图表评价s值以及阈值电压(vth)。具体而言,在电流值id=10

‑

11

~10

‑

10

[a]区域中,将由下述式(d)求出的值作为s值进行计算。进而,计算电流值id=10

‑8[a]中的vg的值作为阈值电压(vth)。

[0430]

[数3]

[0431][0432]

其结果为,实施例1~8、比较例1、2、4、5中s值为0.5[v/decade]以下。

[0433]

(3

‑

4)漏电流

[0434]

根据各个id

‑

vg特性的图表评价漏电流。漏电流是作为通过对vg=

‑

5v~

‑

2v的范围求出id的合计值,并将合计值除以测量个数而得到的平均值导出的。

[0435]

其结果为,在实施例1~8、比较例1、2、4~6、8~10中漏电流为1.0

×

10

‑

14

[a]以下。另一方面,在比较例3以及比较例7中,漏电流为10

‑4[a]以上,作为晶体管未确认到导通/断开。

[0436]

[表4]

[0437][0438]

[表5]

[0439][0440]

[表6]

[0441][0442]

在实施例1~8所涉及的晶体氧化物薄膜中,平均晶体粒径为0.5μm以下,与平均晶体粒径超过0.5μm的比较例1、2、5~10所涉及的氧化物薄膜相比,漏电压(vd)为0.1v、10v以及20v中的陷阱限制传导区域特性优异。

[0443]

在实施例1~8所涉及的晶体氧化物薄膜中,例举了使用钐元素作为ln元素的例子,但对于钐元素以外的元素,只要具有与钐相同程度的离子半径,则可以认为其作为ln元素起到与包含钐元素的晶体氧化物薄膜同样的效果。

[0444]

附图标记说明

[0445]

10 层叠体

[0446]

11 晶体氧化物薄膜

[0447]

12 支承体

[0448]

30 栅极绝缘膜

[0449]

50 源电极

[0450]

60 漏电极

[0451]

100 薄膜晶体管

[0452]

100a 薄膜晶体管

[0453]

511 栅电极

[0454]

513 源电极

[0455]

515 漏电极。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。