1.本发明是有关于一种驱动电路,尤其是一种驱动电路的耐高压电路。

背景技术:

2.随着液晶显示器技术的进步,液晶显示器已朝向高分辨率及大尺吋发展,且液晶显示器具有重量轻、寿命长及高画质等优点,广泛应用于各式电子装置中,例如手持式电子装置、家用电视与室外各式大型屏幕。

3.现今为了优化液晶显示器,已发展出非结晶硅闸极(amorphous silicon gate,asg)的技术,其可以称为闸极面板(gate on panel,gop或gate on array,goa或gate in panel,gip)。即在显示面板的薄膜晶体管阵列制作时,形成用于驱动闸极线的电路于显示面板的基板上,基板上的电路会接收一闸极驱动电路所产生的闸极讯号,进而依据闸极讯号产生多个闸极线驱动讯号,以驱动闸极线所耦接的像素,如此可降低闸极驱动电路与显示面板互相耦接所需的脚位。

4.于习用技术,利用单一供应电源作为闸极驱动电路所需的电力来源。再者,由于应用于gip架构的闸极驱动电路产生多个闸极讯号的时间会部份相互重迭,例如在同一时间点下,第一闸极讯号的电压准位已在一导通电压准位,而第二闸极讯号的电压准位尚在爬升中,如此,在提供单一供应电源至闸极驱动电路产生该些闸极讯号下,电压准位已是导通电压准位的第一闸极讯号会受电压准位尚在爬升中的第二闸极讯号所影响,其原因在于第二闸极讯号会拉低此供应电源的电压准位,而第一闸极讯号的电压准位当下是藉由此供应电源维持为导通电压准位,如此就会影响第一闸极讯号的电压准位。如此,即会影响显示面板的显示质量。对于上述问题,专利证书号tw i546797b提出相关解决办法,但其效果无法满足高标准的液晶显示器需求。

5.所以,本发明提出一种显示面板驱动电路,以可解决上述问题。

技术实现要素:

6.本发明的目的,在于提供一种显示面板驱动电路,其利用不同电源驱动能力的电源电路,控制闸极讯号的电压准位互不干扰。

7.本发明揭示一种显示面板驱动电路,其包含一第一电源电路、一第二电源电路及多个驱动器。第一电源电路产生一第一供应电压,第二电源电路产生一第二供应电压,第二电源电路提供的电荷量低于第一电源电路提供的电荷量。该些驱动器产生多个闸极讯号,且包含多个第一电源输入端与多个第二电源输入端,该些第一电源输入端耦接第一电源电路而接收第一供应电压,该些第二电源输入端耦接第二电源电路而接收第二供应电压,该些驱动器分别于一电压上升区间依据第一供应电压提升该些闸极讯号的电压准位,该些驱动器分别于一电压维持区间依据第二供应电压维持该些闸极讯号的电压准位。

8.此外,本发明揭示一种驱动电路的耐高压电路,其包含一第一开关元件、一第二开关元件与一控制元件。第一开关元件接收一输入电压并传输该输入电压,第二开关元件耦

接于第一开关元件与一输出端之间,并传输该输入电压至输出端,第二开关元件的一本体耦接第一开关元件的一本体,控制元件耦接于第一开关元件与第二开关元件的一本体接点,并耦接一控制电压,控制元件依据控制电压控制第一开关元件与第二开关元件的本体接点的一电压准位。

附图说明

图1:其为本发明的显示器的显示面板驱动电路的一实施例的示意图;图2:其为本发明的闸极驱动电路配合多组电源电路于不同时间产生闸极讯号的一实施例的时序图;图3:其为本发明的驱动器的一第一实施例的电路图;图4:其为本发明的驱动器的一第二实施例的电路图;图5:其为本发明的驱动器的一第三实施例的电路图;及图6:其为本发明的闸极讯号的电压准位上升与下降的一实施例的波形图。【图号对照说明】10

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

显示器20

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

显示面板21

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

闸极线22

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

源极线23

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

像素晶体管25

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

闸极面板电路30

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

源极驱动电路40

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

闸极驱动电路41

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

驱动器42

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

预充电电路43

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

预充电电路44

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

下拉电路50

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一电源电路51

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二电源电路52

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三电源电路60

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

控制电路70

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

比较器c1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电荷量c2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电荷量cl

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

液晶电容cs

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

储存电容holding

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电压维持区间rising

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电压上升区间scmp

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

比较讯号t0

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

时间

t1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

时间t2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

时间t3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

时间t4

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

时间t5

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

时间t6

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

时间t7

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

时间t8

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

时间t9

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

时间t10

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

时间t1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

晶体管t2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

晶体管t3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

晶体管t4

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

晶体管t5

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

晶体管t6

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

晶体管t7

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

晶体管t8

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

晶体管t9

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

晶体管t10

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

晶体管v1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一预充电电压v2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二预充电电压v44

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

下拉电压vb1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

本体电压vb2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

本体电压vb3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

本体电压vb4

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

本体电压vb5

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

本体电压vb6

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

本体电压vb7

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

本体电压vb8

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

本体电压vb9

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

本体电压vb10

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

本体电压vc

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

控制电压vc1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

控制讯号vc2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

控制讯号vc3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

控制讯号vc4

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

控制讯号vc5

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

控制讯号

vc6

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

控制讯号vc7

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

控制讯号vc8

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

控制讯号vcmp

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

基准电压vcn

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

控制讯号vg1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

闸极讯号vg2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

闸极讯号vg3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

闸极讯号vg4

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

闸极讯号vg5

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

闸极讯号vghp

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一供应电压vghs

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二供应电压vgl

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三供应电压vgl1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

闸极线讯号vgl2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

闸极线讯号vgl3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

闸极线讯号vgl4

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

闸极线讯号vgl5

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

闸极线讯号vgl6

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

闸极线讯号vgl7

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

闸极线讯号vgl8

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

闸极线讯号vgl9

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

闸极线讯号vgl10

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

闸极线讯号vgnd

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

参考电压vs1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

源极讯号vs2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

源极讯号vs3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

源极讯号vs4

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

源极讯号vs5

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

源极讯号vs6

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

源极讯号

具体实施方式

9.在说明书及后续的申请专利范围当中使用了某些词汇指称特定的元件,然,所属本发明技术领域中具有通常知识者应可理解,制造商可能会用不同的名词称呼同一个元件,而且,本说明书及后续的申请专利范围并不以名称的差异作为区分元件的方式,而是以元件在整体技术上的差异作为区分的准则。在通篇说明书及后续的申请专利范围当中所提及的「包含」为一开放式用语,故应解释成「包含但不限定于」。再者,「耦接」一词在此包含任何直接及间接的连接手段。因此,若文中描述一第一装置耦接一第二装置,则代表该第一装置可直接连接该第二装置,或可透过其他装置或其他连接手段间接地连接至该第二装置。

10.为了使本发明的结构特征及所达成的功效有更进一步的了解与认识,特用较佳的实施例及配合详细的说明,说明如下:

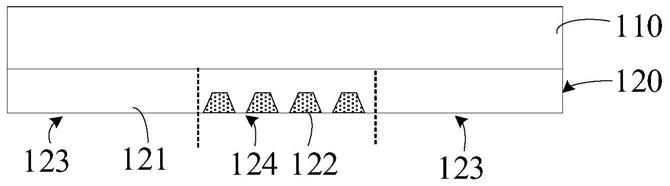

11.请参阅图1,其为本发明的显示器的显示面板驱动电路的一实施例的示意图。如图所示,一显示器10包含一显示面板20与一显示面板驱动电路。显示面板20具有多个像素、多个闸极线21与多个源极线22,每一像素包含一像素晶体管23、一液晶电容cl与一储存电容cs,像素晶体管耦接液晶电容cl与储存电容cs。一闸极面板电路25形成于显示面板20并耦接该些闸极线21而耦接该些像素晶体管23的一闸极端,且闸极面板电路25接收多个闸极讯号vg1、vg2、vg3、vg4及vg5,如此,闸极面板电路25依据该些闸极讯号vg1

‑

vg5产生多个闸极线驱动讯号,以分别传输至该些闸极线21,以控制该些像素晶体管23的闸极端,以控制该些像素晶体管23导通与截止。该些源极线22耦接该些像素晶体管23的一源极端,且传输多个源极讯号vs1、vs2、vs3、vs4、vs5、vs6至该些像素晶体管23的源极端,而充电液晶电容cl与储存电容cs。储存电容cs的一储存电压用于稳定液晶电容cl的液晶电压的电压准位。

12.显示面板驱动电路包含一源极驱动电路30与一闸极驱动电路40,源极驱动电路30耦接显示面板20,且产生该些源极讯号vs1

‑

vs6至显示面板20的该些源极线22,以传送至该些像素晶体管23;闸极驱动电路40耦接显示面板20,且产生该些闸极讯号vg1

‑

vg5至显示面板20的闸极面板电路25。如此,显示面板驱动电路驱动显示面板20显示多个画面。

13.复参阅图1,显示面板驱动电路包含一第一电源电路50与一第二电源电路51,第一电源电路50依据一第一输入电源产生一第一供应电压vghp,第二电源电路51依据一第二输入电源产生一第二供应电压vghs,然而,第二电源电路51可以依据第一输入电源产生第二供应电压vghs,其非图1实施例所限。第一电源电路50与第二电源电路51耦接闸极驱动电路40,且分别输出第一供应电压vghp与第二供应电压vghs至闸极驱动电路40,闸极驱动电路40依据第一供应电压vghp与第二供应电压vghs输出该些闸极讯号vg1

‑

vg5至显示面板20。

14.显示面板驱动电路包含一控制电路60与一比较器70。比较器70的两输入端分别接收一基准电压vcmp与第一电源电路50的第一供应电压vghp,其中,比较器70可以透过一分压电路耦接第一电源电路50的第一供应电压vghp。所以,比较器70依据基准电压vcmp与第一供应电压vghp而产生一比较讯号scmp。所以,比较讯号scmp可以表示第一供应电压vghp的电压准位是否上升至超过一预定电压准位,此预定电压准位与基准电压vcmp的电压准位呈一倍数关系。控制电路60可以为一时序控制器(timing controller),控制电路60耦接比较器70与闸极驱动电路40,控制电路60接收比较讯号scmp而依据比较讯号scmp产生该些控制讯号vc1

‑

vcn至闸极驱动电路40。所以,控制电路60依据比较讯号scmp控制闸极驱动电路40产生该些闸极讯号vg1

‑

vg5。

15.于图1实施例中,第一电源电路50输出的电荷量高于第二电源电路51输出的电荷量,即第一电源电路50的输出电流高于第二电源电路51的输出电流,所以,第一电源电路50的电源驱动能力高于第二电源电路51的电源驱动能力。因此,闸极驱动电路40依据多组不同电源驱动能力的电源电路50、51产生该些闸极讯号vg1

‑

vg5,其中电源电路50、51可以为一充电泵电源电路。再者,闸极驱动电路40依据高电源驱动能力或低电源驱动能力的电源电路50、51所提供的第一供应电压vghp或者第二供应电压vghs而产生该些闸极讯号vg1

‑

vg5是由控制电路60决定。即控制电路60依据比较器70产生的比较讯号scmp,而控制闸极驱动电路40于不同时间依据不同电源驱动能力的电源电路50、51所提供的第一供应电压vghp

或者第二供应电压vghs而提升或维持该些闸极讯号vg1

‑

vg5的电压准位。

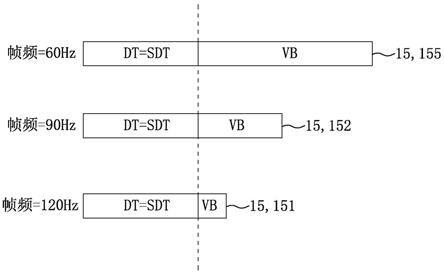

16.请参阅图2,其为本发明的闸极驱动电路配合多组电源电路于不同时间产生闸极讯号的一实施例的时序图。如图所示,该些闸极讯号vg1

‑

vg5于电压准位变化可以包含一电压上升区间rising与一电压维持区间holding,其中,电压上升区间rising为该些闸极讯号vg1

‑

vg5的电压准位从一截止电压准位上升至一预定电压准位,电压维持区间holding为该些闸极讯号vg1

‑

vg5的电压准位维持于一导通电压准位。于实施例中,截止电压准位是截止像素晶体管23的电压准位,导通电压准位是导通像素晶体管23的电压准位,预定电压准位是设定该些闸极讯号vg1

‑

vg5于电压上升区间rising的电压爬升目标,于实施例中的电压爬升目标是第一供应电压vghp的电压准位。所以,实施例未限制截止电压准位、导通电压准位与预定电压准位的电压值,其可以依据各种电源电路的电源驱动能力与显示面板20的显示质量而决定。

17.闸极驱动电路40于电压上升区间rising依据第一供应电压vghp提升该些闸极讯号vg1

‑

vg5的电压准位,而于电压维持区间holding依据第二供应电压vghs维持该些闸极讯号vg1

‑

vg5的电压准位。于此实施例中,每个闸极讯号vg1

‑

vg5的电压上升区间rising互不重迭,及每个闸极讯号vg1

‑

vg5的电压维持区间holding也互不同重迭,所以,闸极驱动电路40分别于不同时间依据第一供应电压vghp提升该些闸极讯号vg1

‑

vg5的电压准位,与门极驱动电路40分别于不同时间依据第二供应电压vghs维持该些闸极讯号vg1

‑

vg5的电压准位。此外,于本发明的另一实施例中,该些闸极讯号vg1

‑

vg5的电压上升区间rising可互相重迭,且电压维持区间holding也可互相重迭。由于,该些闸极讯号vg1

‑

vg5的电压准位被第一供应电压vghp拉升至预定电压准位时,即换由第二供应电压vghs维持该些闸极讯号vg1

‑

vg5的电压准位于导通电压准位,如此当其他闸极讯号的电压准位藉由第一供应电压vghp被拉升时,并不会影响电压准位已是导通电压准位的闸极讯号。

18.换言之,显示面板驱动电路利用较大电源驱动能力的第一电源电路50与有限电源驱动能力的第二电源电路51控制各闸极线21的电压准位,以达到高效率的驱动电路。其中,较大电源驱动能力的第一电源电路50是指适用于可快速拉升电压准位的电源电路,反之,有限电源驱动能力的电源电路51是指拉升电压准位的能力小而拉升速度慢的电源电路。

19.请参阅图3,其为本发明的驱动器的一第一实施例的电路图。如图所示,驱动器41包含多个晶体管t1、t2、t3。晶体管t1的一输入端耦接第一电源电路50而接收第一供应电压vghp,而晶体管t1的输入端为驱动器41的一第一电源输入端。晶体管t1的一控制端耦接控制电路60而接收控制讯号vc1,晶体管t1的一输出端耦接驱动器41的一输出端,于控制电路60输出控制讯号vc1而控制晶体管t1导通后,晶体管t1传输第一供应电压vghp至驱动器41的输出端,以于电压上升区间rising提升闸极讯号vg1的电压准位至第一供应电压vghp的电压准位。实施例中晶体管的输入端与输出端可以为晶体管的源极或汲极,晶体管的控制端可以为晶体管的闸极。

20.晶体管t2的一输入端耦接第二电源电路51而接收第二供应电压vghs,而晶体管t2的输入端为驱动器41的一第二电源输入端。晶体管t2的一控制端耦接控制电路60而接收一控制讯号vc2,晶体管t2的一输出端耦接驱动器41的输出端,于控制电路60输出控制讯号vc2而控制晶体管t2导通后,晶体管t2传输第二供应电压vghs至驱动器41的输出端,以于电压维持区间holding维持闸极讯号vg1的电压准位至第二供应电压vghs的电压准位,即为导

通电压准位。如此,闸极讯号vg1可以控制像素晶体管23为导通状态。此外,于图3实施例中,第二供应电压vghs的电压准位低于第一供应电压vghp的电压准位。于本发明的另一实施例中,第二供应电压vghs的电压准位可等于或者近似于第一供应电压vghp的电压准位。

21.再者,于闸极讯号vg1维持于导通电压准位时,第一电源电路50未提供电力予闸极讯号vg1,所以第一电源电路50供应第一供应电压vghp至下一条闸极线21的闸极讯号vg2,以提升闸极讯号vg2的电压准位。如此,闸极讯号vg1与闸极讯号vg2分别由不同组电源电路50、51供应电力,闸极讯号vg1的导通电压准位不受下一条闸极线21开启的影响,即闸极讯号vg1可以维持于导通电压准位而不会被闸极讯号vg2下拉。

22.复参阅图3,晶体管t3的一输出端耦接晶体管t1、晶体管t2与驱动器41的输出端,晶体管t3的一控制端耦接控制电路60而接收一控制讯号vc3,晶体管t3的一输入端耦接驱一第三供应电压vgl,其中第三供应电压vgl可以为截止像素晶体管23的一截止电压。于控制电路60输出控制讯号vc3而控制晶体管t3导通后,晶体管t3传输第三供应电压vgl至驱动器41的输出端,以下拉闸极讯号vg1的电压准位至第三供应电压vgl的电压准位,即闸极讯号vg1改变为截止电压准位,并截止像素晶体管23。

23.此外,第一电源电路50输出的电荷量(或电流)c1高于第二电源电路51输出的电荷量(或电流)c2,即第一电源电路50的电源驱动能力高于第二电源电路51的电源驱动能力。所以晶体管t1传输的电流也高于晶体管t2的传输的电流。

24.请参阅图4,其为本发明的驱动器的一第二实施例的电路图。如图所示,在为了节省闸极讯号vg1于电压上升区间rising的功耗,驱动器41可以包含一预充电电路42,预充电电路42包含一高压元件,例如耐高压的晶体管t4。预充电电路42耦接驱动器41的输出端,以输出一预充电电压至驱动器41的输出端。如此,闸极讯号vg1可以先被充电至预充电电压的电压准位后再被充电至第一供应电压vghp的电压准位。图4实施例包含一第三电源电路52,且第三电源电路52可以输出不同准位的预充电电压,即图4实施例的一第一预充电电压v1与一第二预充电电压v2。第三电源电路52接收第一预充电电压v1,且未升压第一预充电电压v1而直接输出第一预充电电压v1。或者,第三电源电路52接收第一预充电电压v1,且升压第一预充电电压v1而输出第二预充电电压v2,所以第二预充电电压v2的一第二预充电压准位高于第一预充电电压v1的一第一预充电压准位。此外,第三电源电路52可以包含一切换元件或一切换电路,而输出第一预充电电压v1或第二预充电电压v2至预充电电路42。

25.此外,第一预充电电压v1可以为一外部电源电路所产生的一外部电源电压vdd,且外部电源电压vdd可以不透过第三电源电路52而直接输出至预充电电路42。换言之,第一预充电电压v1与第二预充电电压v2可以依据不同的外部电源电路而产生。再者,晶体管t1

‑

t4的一本体(或称基极端)分别具有一本体电压(或称基极偏压)vb1、一本体电压vb2、一本体电压vb3与一本体电压vb4。于本发明的另一实施例中,预充电电路42可耦接于第一电源电路50,第一电源电路50可提供第一预充电电压v1与第二预充电电压v2,第一电源电路50内可包含切换电路,以提供第一预充电电压v1、第二预充电电压v2与第一供应电压vghp。

26.请参阅图5,其为本发明的驱动器的一第三实施例的电路图。如图所示,图5实施例的预充电电路43取代图4实施例的预充电电路42,其差异在于图5的预充电电路43包含多个晶体管,该些晶体管的闸极与本体间可承受中压,而源极与汲极间可承受高压,所以可应用于需要耐高电压的需求,而图4的预充电电路42包含至少一耐高压的晶体管t4。预充电电路

43包含多个晶体管t5、t6、t7、t8、d1,晶体管t5、晶体管t6、晶体管d1、晶体管t7与晶体管t8分别为预充电电路43的一第一开关元件、一第二开关元件、一控制元件、一第三开关元件与一第四开关元件。如此,第一开关元件(即t5)接收一输入电压(第一预充电电压v1或者第二预充电电压v2),并传输第一预充电电压v1或者第二预充电电压v2。第二开关元件(即t6)耦接于第一开关元件与预充电电路43的一输出端之间,且传输第一预充电电压v1或者第二预充电电压v2至预充电电路43的输出端,第二开关元件的一本体(body)耦接第一开关元件的一本体(body)。控制元件(即d1)耦接于第一开关元件与第二开关元件的一本体接点,并耦接一控制电压vc,控制元件依据控制电压vc控制第一开关元件与第二开关元件的本体接点的一电压准位。第三开关元件(即t7)耦接控制元件并接收一高电压(此实施例为第一供应电压vghp),而传输第一供应电压vghp至控制元件并做为控制电压vc。第四开关元件(即t8)耦接控制元件并接收一低电压(此实施例为参考电压vgnd),而传输参考电压vgnd至控制元件并做为控制电压vc。所以,控制电压vc在不同电路运作下可以为第一供应电压vghp或参考电压vgnd。

27.其中,晶体管d1的控制端与输出端相连接而为一二极管,晶体管d1的输入端为二极管的一正端,晶体管d1的输出端为二极管的一负端。

28.晶体管t7的一输入端耦接第一供应电压vghp,晶体管t7的一控制端耦接控制电路60产生的一控制讯号vc5,晶体管t7的一输出端耦接晶体管d1的一输入端,晶体管t7的一本体耦接一本体电压vb7。晶体管t8的一输出端耦接晶体管t7的输出端与晶体管d1的输入端,晶体管t8的一控制端耦接控制电路60产生的一控制讯号vc6,晶体管t8的一输入端耦接一参考电压vgnd,晶体管t8的一本体耦接一本体电压vb8。再者,晶体管t8的本体耦接晶体管t8的输入端,所以晶体管t8的本体与晶体管t8的输入端同为参考电压vgnd的电压准位。

29.因此,当控制讯号vc5控制晶体管t7导通时,晶体管d1的输入端为第一供应电压vghp的电压准位,而当控制讯号vc5控制晶体管t7截止,且控制讯号vc6控制晶体管t8导通时,晶体管d1的输入端为参考电压vgnd的电压准位。

30.复参阅图5,晶体管t5的一输入端耦接第三电源电路的预充电电压v1、v2,晶体管t5的一控制端耦接晶体管d1的输入端,晶体管t5的一输出端耦接晶体管d1的一输出端。晶体管t6的一输入端耦接晶体管t5的输出端与晶体管d1的输出端,晶体管t6的一控制端耦接晶体管d1的输入端,晶体管t6的一输出端耦接驱动器41的输出端。晶体管d1的一控制端耦接晶体管d1的输出端。再者,晶体管d1、晶体管t5与晶体管t6的一本体相互耦接而为相同电压准位的本体电压,所以,本体电压vb5、本体电压vb6与本体电压vb9为相同电压准位。

31.因此,当晶体管d1的输入端为第一供应电压vghp的电压准位时,本体电压vb5、本体电压vb6、本体电压vb9、晶体管t5的控制端与晶体管t6的控制端的电压准位近似于第一供应电压vghp的电压准位,如此,晶体管t5、t6趋于截止状态,所以预充电电路43未供应电力至驱动器41的输出端。再者,当晶体管d1的输入端为参考电压vgnd的准位时,晶体管t5、t6为导通状态,如此,预充电电路43传输第一预充电电压v1或第二预充电电压v2至驱动器41的输出端,而控制闸极讯号vg1上升至第一预充电压准位或第二预充电压准位。

32.此外,第一预充电压准位低于第二预充电压准位,第二预充电压准位低于预定电压准位,所以在驱动器41的预充电电路43依据第一预充电电压v1或/及第二预充电电压v2提升闸极讯号vg1的电压准位后,预充电电路43即会关闭,而驱动器41再依据第一供应电压

vghp提升闸极讯号vg1的电压准位至预定电压准位。再者,于控制像素晶体管23导通与截止下,闸极讯号vg1的电压准位可以是由截止电压准位开始提升,及由导通电压准位开始降低。一般而言,为确保像素晶体管23处于截止状态,截止电压(第三供应电压vgl)的电压准位可以低于参考电压vgnd的准位,而参考电压vgnd的准位可以为零电压的一接地准位,所以,截止电压也可以为一负电压。

33.再参阅图5,显示面板驱动电路可以包含一下拉电路44,其耦接控制元件,并输出一下拉电压v44至控制元件而为控制电压vc,下拉电压v44的一电压准位随时间而降低。晶体管t3同样可以下拉闸极讯号vg1的电压准位,所以下拉电路44除了包含多个晶体管t9、t10外,还可以包含晶体管t3。晶体管t9的一输出端耦接预充电电路43的晶体管d1的输入端,晶体管t9的一控制端耦接控制电路60产生的一控制讯号vc7,晶体管t9的一输入端耦接晶体管t0的一输出端。晶体管t0的一控制端耦接控制电路60的一控制讯号vc8,晶体管t0的一输入端耦接一接地与晶体管t10的一本体,所以晶体管t0的输入端与本体同为接地,即本体电压vb10为接地的电压准位。此外,晶体管t10可以为一电流源,其电流值可以经由设计而不同,电流值决定下拉电压v44的下降速度。

34.另外,为了节省电能,闸极讯号vg1的电压准位维持于导通电压准位而欲降低至截止电压准位之前,下拉电路44可控制预充电电路43的晶体管t5、t6导通,而控制闸极讯号vg1的电压准位降至第一预充电电压v1或第二预充电电压v2的准位。如此可知,预充电电路43的晶体管t5、t6也相当于下拉电路。

35.由于预充电电路43的晶体管t6的闸极与本体间只可承受中压,所以下拉电路44为避免晶体管t6承受高压,例如晶体管t6的高跨压(即控制端与输出端的压差)为参考电压vgnd与第二供应电压vghs,而控制晶体管t6的控制端的电压准位阶段式下降,即不直接降至参考电压vgnd的准位。如此,下拉电路44控制晶体管t6的输出端与控制端间的跨压(闸极讯号vg1的电压准位与下拉电压v44的压差)不高于可承受的电压,而非为高跨压状态,以确保预充电电路43的开关元件不会崩溃。尔后,预充电电路43即会关闭,而闸极讯号vg1的电压准位因晶体管t3的导通而降至至截止电压vgl的准位,仍为晶体管t6能承受的中压范围。

36.复参阅第一图,第一图实施例可以不设置比较器70,而设置一计数器,其中计数器可以设置于控制电路60外或控制电路60内,其非实施例所限。计数器依据第一供应电压vghp拉升闸极讯号vg1的电压准位超过预定电压准位所需的时间而设定一预定时间,当计数时间超过预定时间时产生一计数讯号,控制电路60依据计数讯号即可控制该些驱动器41依据第二供应电压vghs维持些闸极讯号vg1的电压准位。由上述说明可知,控制电路60控制该些驱动器41依据第一供应电压vghp提升闸极讯号vg1的电压准位,且计数时间,当计数时间到预定时间时,控制电路60控制该些驱动器41依据该第二供应电压vghs维持闸极讯号vg1的电压准位。

37.图6,其为本发明的闸极讯号的电压准位上升与下降的一实施例的波形图。如图所示,闸极讯号vg1于一时间t0前为截止电压准位(即vgl),其仅是用于说明闸极讯号vg1的初始电压准位,非限制闸极讯号vg1的初始电压准位仅能为截止电压vgl的准位。于一时间t1,闸极讯号vg1因预充电电路43的充电而从初始电压准位提升至第一预充电电压v1的准位,于一时间t2,再从第一预充电电压v1的第一预充电压准位提升至第二预充电电压v2的第二预充电压准位。但是,闸极讯号vg1可以直接充电至第二预充电电压v2的第二预充电压准

位,而无须先充电至第一预充电电压v1的第一预充电压准位,其为实施例变化的选项之一。

38.再者,预充电电路43停止供应电力后,于一时间t3与一时间t4,驱动器41利用第一电源电路50的电力而提升闸极讯号vg1的电压准位至第一供应电压vghp的电压准位。其中,第一供应电压vghp的电压准位高于第二供应电压vghs的电压准位为较佳选项。因此,时间t0至一时间t5之间为闸极讯号vg1的电压上升区间rising。于电压维持区间holding,即一时间t6与一时间t7之间,驱动器41利用第二电源电路51的电力而维持闸极讯号vg1的电压准位于第二供应电压vghs的电压准位,即导通电压准位。

39.从一时间t7、一时间t8、一时间t9至一时间t10为类似预充电区间,以可节省电源。所以,闸极讯号vg1的电压准位先从导通电压准位降低至一下拉电压准位,此实施例即为第一预充电电压v1的第一预充电压准位。其中,闸极讯号vg1的电压准位亦可以先降低至下拉电压准位(此时为第二预充电电压v2的第二预充电压准位),再降低至第一预充电电压v1的第一预充电压准位,其为实施例的变化之一。最后,晶体管t3控制闸极讯号vg1的电压准位降低至截止电压准位。

40.综上所述,本发明揭示一种显示面板驱动电路,其包含一第一电源电路、一第二电源电路及多个驱动器。第一电源电路产生一第一供应电压,第二电源电路产生一第二供应电压,第二电源电路提供的电荷量低于第一电源电路提供的电荷量。该些驱动器包产生多个闸极讯号,且含多个第一电源输入端与多个第二电源输入端,该些第一电源输入端耦接第一电源电路而接收第一供应电压,该些第二电源输入端耦接第二电源电路而接收第二供应电压,该些驱动器分别于一电压上升区间依据第一供应电压提升该些闸极讯号的电压准位,该些驱动器分别于一电压维持区间依据第二供应电压维持该些闸极讯号的电压准位。

41.上文仅为本发明的较佳实施例而已,并非用来限定本发明实施的范围,凡依本发明权利要求范围所述的形状、构造、特征及精神所为的均等变化与修饰,均应包括于本发明的权利要求范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。