技术特征:

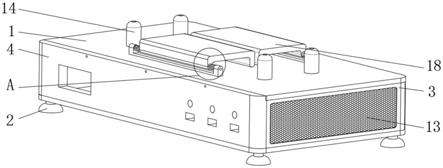

1.一种基于并行lvds接口的高速数据采集系统,其特征在于,该系统包括:soc

‑

fpga可编程门阵列zynq ultrascal子系统(1)、fpga可编程门阵列kintex子系统(2)、子板模块(3)及一电源模块(4),所述的soc

‑

fpga可编程门阵列zynq ultrascal子系统(1)分别与fpga可编程门阵列kintex子系统(2)、子板模块(3)连接;fpga可编程门阵列kintex子系统(2)与soc

‑

fpga可编程门阵列zynq ultrascal子系统(1)、子板模块(3)连接;电源模块(4)为soc

‑

fpga可编程门阵列zynq ultrascal子系统(1)、fpga可编程门阵列kintex子系统(2)及一子板模块(3)供电;其中:所述的soc

‑

fpga可编程门阵列zynq ultrascal子系统(1)包括zynq ultrascal芯片(11)、4gb64bit ddr4存储器(12)、第一flash模块(13)、usb模块(14)、usb

‑

uart接口(15)、sd卡(16)及一与子板连接的lvds接口(17),所述的4gb 64bit ddr4存储器(12)、第一flash模块(13)、usb模块(14)、usb

‑

uart接口(15)、sd卡(16)、子板lvds接口(17)分别与zynq ultrascal芯片(11)连接;所述的fpga可编程门阵列kintex子系统(2)包括kintex7芯片(21)、sfp/sfp 万兆以太网光口(22)、第二flash模块(23)及一子板控制io接口(24)、所述的sfp/sfp 万兆以太网光口(22)、第二flash模块(23)、子板控制io接口(24)分别与kintex7芯片(21)连接;所述的子板模块(3)包括子板(31)、产生高速数字信号的信号源芯片(32)、lvds接口(33)及一单端io接口(34),所述的产生高速数字信号的信号源芯片(32)、lvds接口(33)、单端io接口(34)分别与子板(31)连接;子板(31)通过lvds接口(33)连接到soc

‑

fpga可编程门阵列zynq ultrascale

子系统(1)中的与子板连接的lvds接口(17)上;子板(31)通过单端io接口(34)连接到fpga可编程门阵列kintex子系统(2)中的子板控制io接口(24)上。2.根据权利要求1所述的基于并行lvds接口的高速数据采集系统,其特征在于,所述的usb模块(14)由usb3.0接口(141)、usb2.0接口芯片(142)组成;其中usb3.0接口(141)中的usb3.0高速差分信号与soc

‑

fpga可编程门阵列zynq ultrascale

子系统(1)中的zynq ultrascale

芯片(11)连接;usb3.0接口(141)中的usb2.0差分信号与usb2.0接口芯片(142)连接;usb2.0接口芯片(142)与soc

‑

fpga可编程门阵列zynq ultrascale

子系统(1)中的zynq ultrascale

芯片(11)连接。

技术总结

本发明公开了一种基于并行LVDS接口的高速数据采集系统,包括SOC

技术研发人员:唐宇枫 洪展鹏 王泽宇 刘一清

受保护的技术使用者:华东师范大学

技术研发日:2021.05.24

技术公布日:2021/10/18

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。