本发明涉及控制系统技术领域,特别涉及一种外部时钟诊断方法。

背景技术:

图1是控制系统中比较常见的控制器硬件架构,其为mcu(microcontrollerunit,微控制单元) cpld(complexprogrammablelogicdevice,复杂可编程逻辑器件)的硬件架构,通常mcu用来实现控制算法,而cpld用来做接口以及实现快速响应的安全保护策略。在这种架构中,mcu和cpld的工作都需要时钟的驱动。针对cpld,有些系统会单独为其设计一个外部时钟晶振,也有的为了降低成本,会将mcu的时钟输出接到cpld的时钟输入引脚上作为cpld的工作时钟。目前主流的mcu大都有时钟输出功能,输出时钟频率可在mcu的软件里配置。另外有些cpld,比如altera公司的maxii和maxv系列的cpld内部也有时钟可供配置使用。目前这种常见的硬件架构中,cpld一般是使用外部晶振或者mcu输出的时钟信号作为工作主时钟。但是当外部晶振失效或者mcu功能异常导致cpld的输入时钟clk频率偏差过大甚至停振时,将无法及时诊断出这种故障,cpld用于通信接口的功能模块将会无法正常发送和接收数据,用于保护策略的功能模块也会因为时序错乱导致保护功能失效。比如串行通信波特率偏差导致通信异常,或者用于电机控制逆变桥死区控制的定时偏差导致逆变桥上下直通短路造成严重的安全问题。故如果不对cpld的外部时钟频率进行监控,将会使系统处在风险之中。

技术实现要素:

本发明的目的在于提供一种外部时钟诊断方法,以监控外部时钟是否发生故障。

为解决上述技术问题,本发明提供一种外部时钟诊断方法,包括:

基于外部时钟生成周期性的参考信号,并将所述参考信号的一个周期作为时间窗口;

计算与所述时间窗口之宽度相对应的内部时钟周期的个数的上限阈值及下限阈值;

对每个所述时间窗口内的所述内部时钟周期的个数进行计数,以及

在每个所述时间窗口内,比较所述内部时钟周期的个数与所述上限阈值及所述下限阈值的大小,若所述内部时钟周期的个数大于所述上限阈值或小于所述下限阈值,则判定所述外部时钟故障。

可选的,在所述的外部时钟诊断方法中,对每个所述时间窗口内的所述内部时钟周期的个数进行计数包括:

在每个所述时间窗口起始时,对所述内部时钟周期的个数开始计数;以及

在每个所述时间窗口还未结束时,若所述内部时钟周期的个数大于所述上限阈值,则停止对所述内部时钟周期的个数进行计数。

可选的,在所述的外部时钟诊断方法中,若每个所述时间窗口内的所述内部时钟周期的个数大于所述上限阈值或小于所述下限阈值,则判定所述外部时钟故障包括:

在每个所述时间窗口还未结束时,若所述计数值大于所述上限阈值,则判定所述外部时钟故障;以及

在每个所述时间窗口结束时,若所述计数值大于所述上限阈值或者小于所述下限阈值,则判定所述外部时钟故障。

可选的,在所述的外部时钟诊断方法中,所述外部时钟诊断方法还包括:

设置故障标志位,当判定所述外部时钟故障时,所述故障标志位输出第一标识值,当判定所述外部时钟频率无故障时,所述故障标志位输出第二标识值。

可选的,在所述的外部时钟诊断方法中,若所述故障标志位输出所述第一标识值,则停止对当前所述时间窗口内的所述内部时钟周期的个数进行计数。

可选的,在所述的外部时钟诊断方法中,基于外部时钟生成参考信号的方法为:对所述外部时钟进行n分频,并生成一个周期性的方波信号,将所述方波信号作为所述参考信号,其中,n为自然数。

可选的,在所述的外部时钟诊断方法中,设置时间窗口切换位,若在某个所述内部时钟周期的上升沿检测到所述方波信号的值为1,而在前一个所述内部时钟周期的上升沿检测到所述方波信号的值为0,则所述时间窗口切换位输出第三标识值。

可选的,在所述的外部时钟诊断方法中,若所述时间窗口切换位输出所述第三标识值,则停止对当前所述时间窗口的所述内部时钟周期的个数进行计数,以及,开始对下一所述时间窗口的所述内部时钟周期的个数进行计数。

可选的,在所述的外部时钟诊断方法中,若所述时间窗口切换位输出第三标识值时,则重置所述内部时钟周期的个数为初始值。

可选的,在所述的外部时钟诊断方法中,所述上限阈值及所述下限阈值依据内部时钟频率以及能够允许的频率偏差计算得到。

在本发明提供的外部时钟诊断方法中,基于外部时钟生成参考信号,并将所述参考信号的一个周期作为时间窗口;计算与所述时间窗口的宽度对应的内部时钟周期的个数的上限阈值及下限阈值;对每个所述时间窗口内的所述内部时钟周期的个数进行计数,在每个所述时间窗口内,若所述内部时钟周期的个数大于所述上限阈值或小于所述下限阈值,则判定所述外部时钟故障。与现有技术相比,本发明能够监控外部时钟频率是否故障,使系统能够基于监控结果,判定是否进入安全风险防范保护措施。

附图说明

图1是mcu cpld硬件架构的示意图;

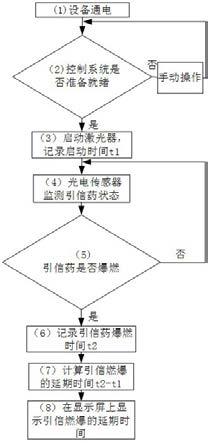

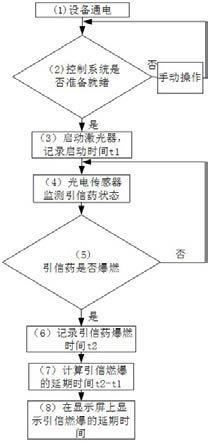

图2是本发明实施例的外部时钟诊断方法的流程图;

图3是本发明实施例基于外部时钟生成参考信号的逻辑框图;

图4是本发明实施例中cpld外部时钟频率监控的程序状态图;

图5是本发明实施例中外部时钟频率为4.348m时的仿真结果;

图6是本发明实施例中外部时钟频率为3.03m时的仿真结果;

图7是本发明实施例中外部时钟频率为7.14m时的仿真结果。

具体实施方式

目前多数cpld应用中,直接采用外部晶振或者其他cpu输出的时钟信号作为内部逻辑处理的时钟输入,而没有对外部时钟的频率进行监控,一旦外部时钟频率偏差过大甚至因器件失效而停振,cpld无法诊断出来,内部逻辑在错误的时钟驱动下将发生功能异常,这在汽车电子领域将可能导致难以挽回的损失。

有鉴于此,本发明旨在提供一种外部时钟诊断方法,以能够对外部时钟进行监控,通过采用本发明提供的外部时钟诊断方法,可以及时有效地识别出外部时钟的频率异常,并通过标志位输出给cpld其他模块以便紧急进入安全保护的模式,比如让汽车紧急减速、停车,从而尽可能使风险降到最低。

以下结合附图和具体实施例对本发明提出的外部时钟诊断方法作进一步详细说明。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。此外,附图所展示的结构往往是实际结构的一部分。特别的,各附图需要展示的侧重点不同,有时会采用不同的比例。

如图2所示,其为本发明实施例提供的外部时钟诊断方法的流程图,本发明实施例提供的外部时钟诊断方法包括以下步骤:

步骤s11,基于外部时钟生成参考信号,并将所述参考信号的一个周期作为时间窗口;

步骤s12,计算出与所述时间窗口的宽度对应的所述内部时钟周期的个数的上限阈值及下限阈值;

步骤s13,对每个所述时间窗口内的所述内部时钟周期的个数进行计数;

步骤s14,在每个所述时间窗口内,比较所述内部时钟周期的个数与所述上限阈值及所述下限阈值的大小,若所述内部时钟周期的个数大于所述上限阈值或小于所述下限阈值,则判定所述外部时钟故障。

以下所述外部时钟周期通过clk_outside表示,所述内部时钟周期通过clk_inside表示。

对于本发明实施例提出的所述外部时钟诊断方法,可适用于一切同时运用到所述外部时钟和所述内部时钟的硬件结构,例如复杂可编程逻辑器件(cpld)、现场可编程门阵列(fpga)、或微控制单元(mcu)等,目前一些mcu,如st公司的stm32芯片也有内部时钟,一般应用中为提高cpu工作频率精度,多会使用外部高精度晶振或者其他芯片输出的时钟信号。这种场合为保证对外部时钟失效的及时监控,同样可使用本专利提出的方法。

对于步骤s11,具体的,请参考图3,基于外部时钟生成参考信号的方法包括:对所述外部时钟进行n分频生成一个周期性的方波信号,将所述方波信号作为所述参考信号,其中,n为自然数,例如可为5、6、7、8、9、10等。进一步具体的,可首先定义一个信号clk_out_n,每x,n-x个所述外部时钟周期交替将所述clk_out_n取反一次,那么clk_out_n将会是周期性的所述方波信号,其周期为n个clk_outside,其中,x可以取1~n-1中任一个。

请继续参考图3,在本发明实施例中,一方面可通过定义所述clk_out_n以得到所述时间窗口,另一方面,可通过所述clk_out_n的状态设置时间窗口切换位ring_clk_out_n。具体的,若某个所述内部时钟周期的上升沿检测到clk_out_n为1,而前一个所述内部时钟周期的上升沿检测到clk_out_n为0,则所述ring_clk_out_n输出第三标识值,否则,所述rising_clk_out_n输出第四标识值,若所述时间窗口切换位输出所述第三标识值,则停止对当前所述时间窗口的所述内部时钟周期的个数进行计数,以及,开始对下一所述时间窗口的所述内部时钟周期的个数进行计数,即,将所述rising_clk_out_n输出第三标识值作为两个时间窗口的边界标志。其中,所述第三标识值可为1,所述第四标识值可为0。

对于步骤s12,具体的,所述上限阈值及所述下限阈值依据内部时钟频率以及能够允许的频率偏差计算得到。一般的,对所述上限阈值和所述下限阈值的选择,关系到对所述外部时钟频率偏差的容忍度,当能够允许的频率偏差越大,对应的,所述上限阈值和所述下限阈值的差值越大。而所述时间窗口的宽度决定了对所述外部时钟的响应时间,所述时间窗口的宽度越大,对所述外部时钟的响应时间越长。因此在实际应用场景中,可根据要求的对所述外部时钟的响应时间,设置合适的所述时间窗口。

对于步骤s13,具体的,对每个所述时间窗口内的所述内部时钟周期的个数进行计数包括:在每个所述时间窗口起始时,对所述内部时钟周期的个数开始计数;在每个所述时间窗口还未结束时,若所述内部时钟周期的个数大于所述上限阈值,则停止对所述内部时钟周期的个数进行计数。并且在每个所述时间窗口结束时,将所述内部时钟周期的计数值重置为初始值。所述初始值可为0或者1。

对于步骤s14,具体的,对所述外部时钟故障的判定包括:在每个所述时间窗口还未结束时,若所述计数值大于所述上限阈值,则判定所述外部时钟故障;在每个所述时间窗口结束时,若所述计数值大于所述上限阈值或者小于所述下限阈值,则判定所述外部时钟故障。即,每个所述时间窗口内和每个所述时间窗口结束时均有可能触发故障。

在此基础上,本发明实施例提供的所述外部时钟诊断方法还可包括以下步骤:

设置故障标志位,当判定所述外部时钟故障时,所述故障标志位输出第一标识值,当判定所述外部时钟频率无故障时,所述故障标志位输出第二标识值。若所述故障标志位输出所述第一标识值,则停止对当前所述时间窗口内的所述内部时钟周期的个数进行计数。其中,所述第一标识值可为0,所述第二标识值可为1。

以下结合图4对步骤s13和步骤s14进一步详细描述。

可定义变量counter为每个所述时间窗口内通过计数器统计的所述内部周期个数的计数值,另外,可定义c_max和c_min分别为所述上限阈值和所述下限阈值,可定义err_clk为所述故障标志位。在每个所述时间窗口起始时,即当rising_clk_out_n输出第三标识值时,对所述内部时钟周期clk_inside的个数开始计数;在每个所述时间窗口还未结束时,若所述clk_inside的个数不超过c_max,则counter值加1,若所述clk_inside的个数大于c_max,说明所述外部时钟频率过低导致基于所述外部时钟定义的所述时间窗口过宽,故判定所述外部时钟故障,所述err_clk输出第一标识值,报出故障,counter值不再发生变化,之后等所述rising_clk_out_n输出所述第三标识值时,即本次所述时间窗口结束时,将所述counter值重置为所述初始值再开始下一所述时间窗口的诊断。另外,当某个所述时间窗口结束时,若所述counter值小于c_min或者大于c_max,则所述err_clk输出第一标识值,报出故障,counter值重置为所述起始值,若所述counter大于等于c_min且小于等于c_max,则所述err_clk输出第二标识值,表示外部时钟诊断为正常,同时将counter值重置为初始值,再开始下一所述时间窗口的诊断。所述err_clk输出第一标识值时,可用于触发系统进入安全保护状态,降低控制系统发生严重后果的风险。

下面基于altera公司的maxv系列cpld5m570zt100a5n,进行本发明提出的方法的效果验证。

maxv系列的cpld的内部时钟输出频率范围为3.9mhz到5.3mhz,如果根据需求选择时间窗口宽度为10个外部时钟周期,即n=10,所述cpld内部时钟周期个数的标准阈值的最大值为12个,最小值为8个,即c_max=12,c_min=8。那么可以计算出所述cpld外部时钟频率异常对应的频率范围为小于3.25mhz或者大于6.625mhz,即所述cpld外部时钟在此范围内,所述故障标志位err_clk将会输出0,报出所述cpld外部时钟频率异常,否则所述故障标志位err_clk将会输出1,报出所述cpld外部时钟频率正常。另外监控的响应时间最大为2.564μs。

针对上述的参数并假设当前所述cpld内部时钟频率为5mhz,对外部时钟分别为4.348m(周期230ns)、3.03m(周期330ns)和7.14m(周期140ns)三种情况进行仿真,仿真结果如图5、图6和图7所示。

可见,图5中第一个时间窗口结束后,cpld内部时钟计数值未超出所述正常阈值范围,所述故障标志位err_clk输出从0变为1,而图6和图7中cpld内部时钟计数值超出了所述正常阈值范围,所述故障标志位err_clk输出则从1变为0,输出结果符合预期。本发明所提出的方法成功实现。

综上所述,本发明实施例提供的外部时钟诊断方法基于外部时钟周期性地产生固定的时间窗口,并结合内部时钟的频率精度和容许的频率偏差计算出在每个时间窗口内对应的内部时钟周期个数的上下限阈值。每个时间窗口开始时,基于内部时钟的计数器开始计数,如果某段时间外部时钟频率偏差过大,将导致对应的时间窗口宽度偏差过大。这个时间窗口对应的内部时钟的计数值将超出阈值,此时时钟故障标志位输出相应的标识值触发其他模块迅速做出相应的安全保护响应,从而实现对外部时钟的诊断。

这里需要说明的是,本发明实施例提供的外部时钟诊断方法能达到的效果以在cpld上的应用做出的示例,但应理解,对于同样具有内部时钟的芯片,例如fpga、mcu等,在使用外部晶振或者其他芯片输出的时钟信号时,为了保证对外部时钟频率失效的及时诊断,所述外部时钟诊断方法同样适用。

上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

本文用于企业家、创业者技术爱好者查询,结果仅供参考。