延迟电路和相位插值器

1.相关申请的交叉引用

2.本技术根据35u.s.c.

§

119要求于2020年04月09日提交的韩国专利申请no.10-2020-0043459的优先权,其通过整体引用并入本文。

技术领域

3.各个实施例涉及延迟电路和相位插值器。

背景技术:

4.通常,相位插值器被用来在各种集成电路中生成具有各种相位的时钟。相位插值器接收具有不同相位的多个时钟,并且将所接收到的时钟进行合成,由此生成输出时钟,该输出时钟具有在所接收到的时钟的相位之间的中间相位。

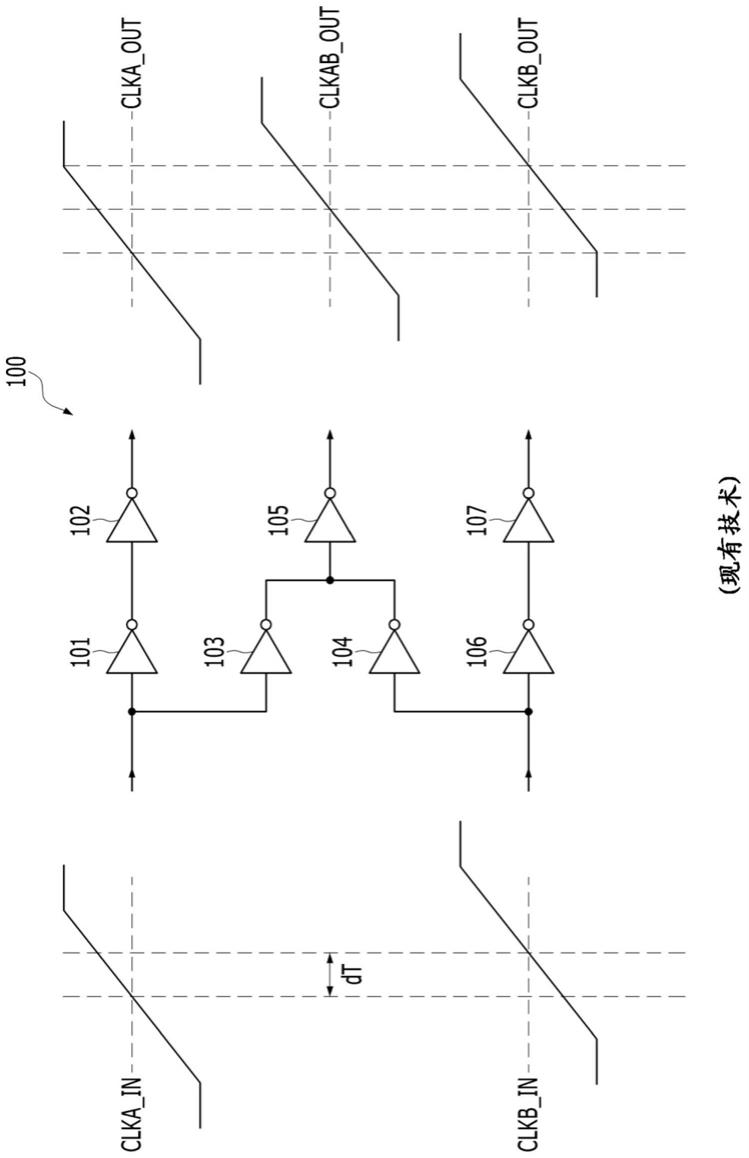

5.图1是图示常规相位插值器100及其操作的示图。

6.参考图1,相位插值器100可以包括用于传输第一输入时钟clka_in的反相器101和102,用于传输第二输入时钟clkb_in的反相器106和107,以及用于将该第一输入时钟clka_in和第二输入时钟clkb_in进行合成的反相器103至105。

7.图1示出了第一输入时钟clka_in和第二输入时钟clkb_in,二者之间具有相位差“dt”,并且从相位插值器100输出的插值输出时钟clkab_out具有在第一输出时钟clka_out和第二输出时钟clkb_out之间的中间相位。这是因为插值输出时钟clkab_out是通过将第一输入时钟clka_in和第二输入时钟clkb_in转变的周期的模拟分量进行融合而生成的。

8.当第一输入时钟clka_in和第二输入时钟clkb_in之间的相位差“dt”大时,第一输入时钟clka_in转变的周期和第二输入时钟clkb_in转变的周期彼此不重叠。在这种情形中,重要的是将两个时钟clka_in和clkb_in的模拟分量进行合成。因此,当待被合成的两个时钟clka_in和clkb_in是低频时钟时,就不可能使用图1的常规相位插值器100来执行相位插值。

技术实现要素:

9.各个实施例针对一种相位插值器,该相位插值器能够生成在其间具有相位差的多个时钟之间的中间相位时钟。

10.在一个实施例中,一种延迟电路可以包括:第一延迟线路,其适用于以基于延迟控制代码而被调节的延迟值,来延迟第一时钟;延迟控制电路,其适用于将通过第一延迟线路而被延迟的第一时钟的相位与第二时钟的相位进行比较,以生成延迟控制代码;和第二延迟线路,其基于延迟控制代码而具有对应于第一延迟线路的延迟值的一半的延迟值。

11.在一个实施例中,一种相位插值器可以包括:第一延迟线路,其适用于以基于延迟控制代码而被调节的延迟值,来延迟第一时钟;延迟控制电路,其适用于将通过第一延迟线路而被延迟的第一时钟的相位与第二时钟的相位进行比较,以生成延迟控制代码;以及第二延迟线路,其适用于基于延迟控制代码,以对应于该第一延迟线路的延迟值的一半的延

迟值,来延迟该第一时钟,用以生成相位插值时钟。

12.在一个实施例中,一种相位插值器可以包括:第一延迟线路,其适用于以基于延迟控制代码而被调节的延迟值,来延迟第一输入时钟;延迟控制电路,其适用于将通过第一延迟线路而被延迟的第一输入时钟的相位与第二输入时钟的相位进行比较,以生成延迟控制代码;第一驱动器,其适用于将通过第一延迟线路而被延迟的第一输入时钟作为第一输出时钟输出;第一合成器,其适用于将通过第一延迟线路而被延迟的第一输入时钟与第二输入时钟进行合成,以利用合成后的时钟驱动第一节点;第二延迟线路,其适用于基于该延迟控制代码,以对应于第一延迟线路的延迟值的一半的延迟值,来延迟第一节点的合成后的时钟,用以将延迟时钟作为第二输出时钟输出;第二驱动器,其适用于将第二输入时钟传输至第二节点;以及第三延迟线路,其适用于以基于延迟控制代码而被调节的、并且等于第一延迟线路的延迟值的延迟值,来延迟该第二节点的时钟,用以将延迟时钟作为第三输出时钟输出。

13.在一个实施例中,一种相位插值方法可以包括:以基于延迟控制代码而被调节的延迟值,来延迟第一时钟;将经延迟的第一时钟的相位与第二时钟的相位进行比较,以生成延迟控制代码,该延迟控制代码被配置为使第一和第二输入时钟同相;对经延迟的第一输入时钟和该第二输入时钟进行合成以输出合成后的时钟;基于延迟控制代码,以对应于该第一输入时钟的延迟值的一半的延迟值,延迟该合成后的时钟,用以输出经延迟的合成后的时钟;基于延迟控制代码,以等于第一输入时钟的延迟值的延迟值,来延迟第二输出时钟。

14.本实施例可以能够生成在其间具有大相位差的时钟之间的中间相位时钟。

附图说明

15.图1是图示常规相位插值器及其操作的示图。

16.图2是图示根据本发明实施例的延迟电路200的示图。

17.图3是图示图2的第一和第二延迟线路的第一实施例的详细示图。

18.图4是图示图2的第一和第二延迟线路的第二实施例的详细示图。

19.图5是图示图2的第一和第二延迟线路的第三实施例的详细示图。

20.图6是图示根据本发明实施例的相位插值器的示图。

21.图7是图示根据本发明另一个实施例的相位插值器的示图。

具体实施方式

22.随后将参考附图描述各个实施例以便对本公开进行详细描述,而使得本公开所属领域的技术人员可以易于实施本公开的技术精神。在本实施例的描述中,可以省略与本实施例的主题无关的组件。在附图标记被赋予附图中的组件时,即使组件在不同的附图中所图示,相同的组件也可以由相同的附图标记来表示。

23.注意到,对“实施例”、“另一实施例”等的引用不一定意味着仅一个实施例,并且对任何这种短语的不同引用不一定是针对相同的(多个)实施例。

24.将要理解的是,虽然本文可以使用术语“第一”、“第二”、“第三”等来描述各个元件,但是这些元件并不被这些术语所限制。这些术语被用来将一个元件与另一个元件加以

区分。因此,下文所描述的第一元件也可以被称作第二或第三元件而并不脱离本发明的精神和范围。

25.进一步将要理解的是,术语“包括”、“包括了”、“包含”和“包含了”在被用于该说明书中时,指定了所陈述元件的存在,但是并不排除一个或多个其它元件的存在或添加。如本文所使用的,术语“和/或”包括一个或多个相关联列出项的任意和全部的组合。

26.如本文所使用的,除非上下文明确另外指出,否则单数形式也可以包括复数形式,反之亦然。除非另外有所规定或者根据上下文明确是针对单数形式,否则在本技术和所附权利要求中使用的冠词“一”(“a”和“an”)一般应当被理解为表示“一个或多个”。

27.图2是图示根据本发明实施例的延迟电路200的示图。

28.参考图2,延迟电路200可以包括第一延迟线路210、延迟控制电路220和第二延迟线路230。

29.第一延迟线路210可以通过延迟第一时钟clk1而生成经延迟的第一时钟clk1d。第一延迟线路210可以具有由延迟控制代码dly_cont<n:1>调节的延迟值。

30.延迟控制电路220可以通过将经延迟的第一时钟clk1d和第二时钟clk2进行比较,而生成延迟控制代码dly_cont<n:1>。延迟控制电路220可以根据经延迟的第一时钟clk1d和第二时钟clk2之间的相位比较结果,而增大或减小延迟控制代码dly_cont<n:1>的代码值。因此,延迟控制电路220可以生成延迟控制代码dly_cont<n:1>,使得经延迟的第一时钟clk1d和第二时钟clk2同相,即,第一延迟线路210的延迟值变得与第一时钟clk1和第二时钟clk2之间的相位差相等。

31.第二延迟线路230可以具有由延迟控制代码dly_cont<n:1>调节的延迟值,并且该延迟值对应于第一延迟线路210的延迟值的一半。由于第二延迟线路230接收与第一延迟线路210相同的延迟控制代码dly_cont<n:1>,所以第二延迟线路230可以被设计为具有对应于第一延迟线路210的延迟值的一半的延迟值。第二延迟线路230可以被用来延迟需要被延迟的随机信号in。

32.参考图2,第一延迟线路210可以具有对应于第一时钟clk1和第二时钟clk2之间的相位差的延迟值,并且第二延迟线路230可以具有对应于第一时钟clk1和第二时钟clk2之间的相位差的一半的延迟值。基于这种特性,可以设计将在下文描述的相位插值器。

33.图3是图示图2的第一延迟线路210和第二延迟线路230的第一实施例的详细示图。

34.参考图3,第一延迟线路210可以包括两个可变延迟311和312,并且第二延迟线路230可以包括一个可变延迟321。

35.第一延迟线路210可以包括串联耦合的第一可变延迟311和第二可变延迟312。第一可变延迟311和第二可变延迟312中的每一个可以具有由延迟控制代码dly_cont<n:1>调节的延迟值,并且第一可变延迟311和第二可变延迟312可以以相同方式来设计(即,可以具有相同的元件配置),并且具有相同的延迟值。

36.第二延迟线路230可以包括第三可变延迟321。第三可变延迟321可以具有由延迟控制代码dly_cont<n:1>调节的延迟值。第三可变延迟321可以以与第一可变延迟311相同的方式来设计(即,可以具有相同的元件配置),并且具有与第一可变延迟311相同的延迟值。

37.由于第一至第三可变延迟311、312和321以相同方式设计,并且接收相同的延迟控

制代码dly_cont<n:1>,所以第一至第三可变延迟311、312和321可以彼此相等。由于第一延迟线路210包括串联耦合的两个可变延迟311和312,并且第二延迟线路230包括一个可变延迟321,所以第一延迟线路210的延迟值可以是第二延迟线路230的延迟值的两倍大。

38.图4是图示图2的第一延迟线路210和第二延迟线路230的第二实施例的详细示图。

39.参考图4,第一延迟线路210可以包括第一可变延迟411。第一可变延迟411可以具有由延迟控制代码dly_cont<n:1>调节的延迟值。

40.第二延迟线路230可以包括代码值变换器431和第二可变延迟432。

41.代码值变换器431可以通过将延迟控制代码dly_cont<n:1>的代码值减半,而生成半延迟控制代码dly_cont_half<n:1>。该半延迟控制代码dly_cont_half<n:1>可以是这样的代码:用于将延迟值控制为延迟控制代码dly_cont<n:1>的代码值的一半。延迟控制代码dly_cont<n:1>可以具有二进制代码格式或温度计代码格式(thermometer code format)。在任意情形中,代码值变换器431可以生成半延迟控制代码dly_cont_half<n:1>,使得对应于该半延迟控制代码dly_cont_half<n:1>的延迟值变为对应于延迟控制代码dly_cont<n:1>的代码值的一半。

42.第二可变延迟432可以以与第一可变延迟411相同的方式来设计(即,可以具有相同的元件配置),并且可以具有由半延迟控制代码dly_cont_half<n:1>调节的延迟值。因此,第二可变延迟432可以具有延迟值,该延迟值对应于第一可变延迟411的延迟值的一半。

43.图5是图示图2的第一延迟线路210和第二延迟线路230的第三实施例的详细示图。在图5中,<1>至<n>可以表示延迟控制代码dly_cont<n:1>的n个比特。此外,<1>b至<n>b可以表示通过将延迟控制代码dly_cont<n:1>的n个比特反相而获得的比特。

44.参考图5,第一延迟线路210可以包括nand门511至521以及反相器522至527。第一延迟线路210可以具有由延迟控制代码dly_cont<n:1>调节的延迟值。当延迟控制代码具有值000

…

11时,第一时钟clk1可以通过nand门511、513、515、516、520、519和518而被延迟。此外,当延迟控制代码具有值000

…

01时,第一时钟clk1可以通过nand门511、513、514、519和518而被延迟。反相器522至527可以充当被用来形成加载的锁存器。根据延迟控制代码dly_cont<n:1>的值,第一时钟clk1在第一延迟线路210中所经过的路径可以在第一延迟线路210中被调节。即,根据延迟控制代码dly_cont<n:1>的值,可以选择n条路径中的一条路径,并且第一时钟clk1可以由所选择的路径延迟。例如,nand门512、514和516可以在第一延迟线路210中选择第一时钟clk1所经过的路径。

45.第二延迟线路230可以包括nand门531至541以及反相器542至547。第二延迟线路230具有n/2条路径,并且可以通过延迟控制代码dly_cont<n:1>的偶数代码值dly_cont<2>,<4>,...,和<n>,来选择n/2条路径中的一条路径,并且该一条路径被用来延迟输入信号in。延迟控制代码dly_cont<n:1>的奇数代码值dly_cont<1>,<3>,...,和<n-1>,可以将由反相器542至547组成的锁存器启用或禁用,由此调节加载。当该延迟控制代码具有值000

…

11时,输入信号可以通过nand门531、533、534、539和538而被延迟。在此情形中,反相器543可以被禁用。因此,由反相器544和545所形成的锁存器可以被禁用。当延迟控制代码具有值000

…

01时,输入信号in可以通过nand门531、532和538而被延迟。在此情形中,反相器543可以被启用。因此,由反相器542和543所形成的锁存器可以被启用以增加加载。作为参考,nand门542、544和546可以在第二延迟线路230中选择输入信号in所经过的路径。

46.由于第一延迟线路210和第二延迟线路230的延迟值由相同的延迟控制代码dly_cont<n:1>调节,并且在第二延迟线路230中选择具有长度对应于第一延迟线路210的长度的一半的路径,所以第二延迟线路230可以具有对应于第一延迟线路210的延迟值的一半的延迟值。

47.图6是图示根据本发明实施例的相位插值器600的示图。

48.参考图6,相位插值器600可以包括第一延迟线路610、延迟控制电路620和第二延迟线路630。

49.第一延迟线路610可以通过延迟第一时钟clk1生成经延迟的第一时钟clk1d。第一延迟线路610可以具有由延迟控制代码dly_cont<n:1>调节的延迟值。第一延迟线路610可以以与第一延迟线路210相同的方式来设计(即,可以具有相同的元件配置)。

50.延迟控制电路620可以通过将经延迟的第一时钟clk1d和第二时钟clk2的相位进行比较,而生成延迟控制代码。延迟控制电路620可以根据经延迟的第一时钟clk1d和第二时钟clk2之间的相位比较结果,而增大或减小延迟控制代码dly_cont<n:1>的代码值。因此,延迟控制电路620可以生成延迟控制代码dly_cont<n:1>,使得经延迟的第一时钟clk1d和第二时钟clk2同相,即,第一延迟线路610的延迟值变得与第一时钟clk1和第二时钟clk2之间的相位差相等。

51.第二延迟线路630可以具有由延迟控制代码dly_cont<n:1>调节的延迟值,并且该延迟值对应于第一延迟线路610的延迟值的一半。由于第二延迟线路630接收与第一延迟线路610相同的延迟控制代码dly_cont<n:1>,所以第二延迟线路630可以被设计为具有对应于第一延迟线路610的延迟值的一半的延迟值。第二延迟线路630可以以与第二延迟线路230相同的方式来设计(即,可以具有相同的元件配置)。

52.第二延迟线路630可以通过延迟第一时钟clk1而生成相位插值时钟clk12。由于第二延迟线路630具有对应于第一时钟clk1和第二时钟clk2之间的相位差的一半的延迟值,并且相位插值时钟clk12通过经由第二延迟线路630延迟第一时钟clk1而获得,所以相位插值时钟clk12可以具有在第一时钟clk1和第二时钟clk2之间的中间相位。

53.图7是图示根据本发明另一实施例的相位插值器700的示图。图7的相位插值器700可以使用其间具有90度相位差的四个输入时钟clk0_in、clk90_in、clk180_in和clk270_in,生成8个输出时钟clk0_out、clk45_out、clk90_out、clk135_out、clk180_out、clk225_out、clk270_out和clk315_out,上述输出时钟之间具有45度的相位差。

54.参考图7,相位插值器700可以包括第一延迟线路711至第十一延迟线路721、延迟控制电路730、第一驱动器741至第四驱动器744,以及第一合成器751至第四合成器754。

55.第一延迟线路711可以具有由延迟控制代码dly_cont<n:1>调节的延迟值,并且延迟第一输入时钟clk0_in。

56.延迟控制电路730可以通过将第一延迟线路711的输出时钟和第二输入时钟clk90_in的相位进行比较,而生成延迟控制代码dly_cont<n:1>。因此,延迟控制电路730可以生成延迟控制代码dly_cont<n:1>,使得第一延迟线路711的输出时钟和第二输入时钟clk90_in同相,即,第一延迟线路711的延迟值变得与第一输入时钟clk0_in和第二输入时钟clk90_in之间的相位差相等。

57.第一驱动器741可以将第一延迟线路711的输出时钟作为第一输出时钟clk0_out

输出。第一驱动器741可以包括串联耦合的两个反相器。

58.第一合成器751可以将第一延迟线路711的输出时钟和第二输入时钟clk90_in进行合成,并且将合成后的时钟传输至第二延迟线路712。由于第一延迟线路711的输出时钟和第二输入时钟clk90_in同相,所以可以认为第一合成器751向第二延迟线路712传输了两个时钟。第一合成器751可以包括三个反相器。

59.第二延迟线路712可以具有由延迟控制代码dly_cont<n:1>调节的延迟值,并且该延迟值对应于第一延迟线路711的延迟值的一半。即,第二延迟线路712可以具有对应于时钟之间的45度相位差的延迟值。第二延迟线路712可以延迟第一合成器751的输出时钟,并且将经延迟的时钟作为第二输出时钟clk45_out输出。

60.第二驱动器742可以将第二输入时钟clk90_in传输至第三延迟线路713。第二驱动器742可以包括串联耦合的两个反相器。

61.第三延迟线路713可以具有由延迟控制代码dly_cont<n:1>调节的延迟值,并且该延迟值与第一延迟线路711的延迟值相等。即,第三延迟线路713可以具有对应于时钟之间的90度相位差的延迟值。第三延迟线路713可以延迟第二驱动器的输出时钟,并且将经延迟的时钟作为第三输出时钟clk90_out输出。

62.第四延迟线路714可以具有由延迟控制代码dly_cont<n:1>调节的延迟值,并且该延迟值与第一延迟线路711的延迟值相等。第四延迟线路714可以延迟第二输入时钟clk90_in。

63.第二合成器752可以将第四延迟线路714的输出时钟和第三输入时钟clk180_in传输至第五延迟线路715。第二合成器752可以包括三个反相器。

64.第五延迟线路715可以具有由延迟控制代码dly_cont<n:1>调节的延迟值,并且该延迟值对应于第一延迟线路711的延迟值的一半。第五延迟线路715可以延迟第二合成器752的输出时钟,并且将经延迟的时钟作为第四输出时钟clk135_out输出。

65.第三驱动器743可以将第三输入时钟clk180_in传输至第六延迟线路716。第三驱动器743可以包括串联耦合的两个反相器。

66.第六延迟线路716具有由延迟控制代码dly_cont<n:1>调节的延迟值,并且该延迟值与第一延迟线路711的延迟值相等。第六延迟线路可以延迟第三驱动器743的输出时钟,并且将经延迟的时钟作为第五输出时钟clk180_out输出。

67.第七延迟线路717可以具有由延迟控制代码dly_cont<n:1>调节的延迟值,并且该延迟值与第一延迟线路711的延迟值相等。第七延迟线路717可以延迟第三驱输入时钟clk180_in。

68.第三合成器753可以将第七延迟线路717的输出时钟和第四输入时钟clk270_in传输至第八延迟线路718。第三合成器753可以包括三个反相器。

69.第八延迟线路718可以具有由延迟控制代码dly_cont<n:1>调节的延迟值,并且该调节值对应于第一延迟线路711的延迟值的一半。第八延迟线路718可以延迟第三合成器753的输出时钟,并且将经延迟的时钟作为第六输出时钟clk225_out输出。

70.第四驱动器744可以将第四输入时钟clk270_in传输至第九延迟线路719。第四驱动器744可以包括串联耦合的两个反相器。

71.第九延迟线路719可以具有由延迟控制代码dly_cont<n:1>调节的延迟值,并且该

延迟值与第一延迟线路711的延迟值相等。第九延迟线路719可以延迟第四驱动器744的输出时钟,并且将经延迟的时钟作为第七输出时钟clk270_out输出。

72.第十延迟线路720可以具有由延迟控制代码dly_cont<n:1>调节的延迟值,并且该延迟值与第一延迟线路711的延迟值相等。第十延迟线路720可以延迟第四驱输入时钟clk270_in。

73.第四合成器754可以将第十延迟线路720的输出时钟和第一输入时钟clk0_in传输至第十一延迟线路721。

74.第十一延迟线路721可以具有由延迟控制代码dly_cont<n:1>调节的延迟值,并且该延迟值对应于第一延迟线路711的延迟值的一半。第十一延迟线路721可以延迟第四合成器754的输出时钟,并且将经延迟的时钟作为第八输出时钟clk315_out输出。

75.根据图7的实施例,可以组合具有对应于时钟之间的90度相位差的延迟值的延迟线路711、713、714、716、717、719和720,以及具有对应于时钟之间的45度相位差的延迟值的延迟线路712、715、718和721,使得相位插值器可以能够生成具有期望相位的时钟clk0_out、clk45_out、clk90_out、clk135_out、clk180_out、clk225_out、clk270_out和clk315_out。

76.根据本发明的实施例,即使在待被合成的两个时钟是低频时钟的情形中,也可以在使该两个时钟同相之后将该两个时钟合成。

77.虽然已经出于说明的目的描述了各个实施例,但是本领域技术人员将清楚的是,可以进行各种变化和修改而并不脱离如以下权利要求中所限定的精神和范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。