半导体器件

1.相关申请的交叉引用

2.于2021年5月21日提交的日本专利申请号2021-085964的公开内容(包括说明书、附图和摘要)通过整体引用并入本文。

技术领域

3.本发明涉及一种半导体器件,并且例如涉及适用于包括横向扩散mosfet(ldmosfet:横向扩散金属氧化物半导体场效应晶体管)的半导体器件的技术。

背景技术:

4.下面列出了公开的技术。

5.[非专利文献1]keita takahashi、kanako komatsu、toshihiro sakamoto、koji kimura和fumitomo matsuoka“hot-carrier induced off-state leakage current increase of ldmos and approach to overcome the phenomenon”(proceedings of the 30th international symposium on power semiconductor devices&ics may 13-17,2018,chicago,usa)

[0006]

非专利文献1公开了,根据采用阶梯绝缘膜(step-ox)的ld mosfet,可以抑制由于热载流子注入而引起的截止泄漏电流的增加而导致功耗增加和电路操作故障。

技术实现要素:

[0007]

如上述非专利文献1中所述,与采用sti结构的ldmosfet相比,通过将sti结构替换为阶梯绝缘膜,采用阶梯绝缘膜的ld mosfet能够抑制截止泄漏电流的增加。

[0008]

然而,即使在采用阶梯绝缘膜的ldmosfet中,由于不能充分抑制热载流子注入到阶梯绝缘膜中,因此从提高包括ldmosfet的半导体器件的性能的观点来看,仍有改进空间。

[0009]

根据一个实施例的一种半导体器件包括半导体衬底、形成在半导体衬底上的栅极电介质膜、形成在栅极电介质膜上的栅极电极、与栅极电极一体形成的场板部、与场板部接触的阶梯绝缘膜、以及具有高于硅的电介质常数并且与阶梯绝缘膜接触的高电介质常数膜。

[0010]

根据一个实施例,可以提高包括ldmosfet的半导体器件的性能。

附图说明

[0011]

图1是用于说明当热载流子注入到阶梯绝缘膜中时ldmosfet的导通电阻增加的机制的流程图;

[0012]

图2是用于说明本实施例的基本构思的图;

[0013]

图3是示意性地示出在其中不存在电位控制膜的ldmosfet中电子流动的状态的图;

[0014]

图4是示意性地示出在其中体现了提供电位控制膜的基本构思的ldmosfet中电子

流动的状态的图;

[0015]

图5是示出本实施例的ldmosfet的器件结构的截面图;

[0016]

图6a是示意性地示出例如在n型resurf层上形成有由氧化硅膜构成的栅极电介质膜时n型resurf层的表面处的能带结构的图;

[0017]

图6b是示意性地示出在n型resurf层上形成有由氧化硅膜构成的栅极电介质膜和高电介质常数膜时n型resurf层的表面处的能带结构的图;

[0018]

图7a和图7b是示意性地示出能带结构的图,其中图6a和图6b的费米能级被调节到相同的能量水平;

[0019]

图8是示出本实施例的半导体器件的制造过程的截面图;

[0020]

图9是示出接着图8的半导体器件的制造过程的截面图;

[0021]

图10是示出接着图9的半导体器件的制造过程的截面图;

[0022]

图11是示出接着图10的半导体器件的制造过程的截面图;

[0023]

图12是示出第一修改示例的ldmosfet的器件结构的截面图;

[0024]

图13是示出第一修改示例的半导体器件的制造过程的截面图;

[0025]

图14是示出接着图13的半导体器件的制造过程的截面图;

[0026]

图15是示出第二修改示例的ldmosfet的器件结构的截面图;

[0027]

图16是示出第二修改示例的半导体器件的制造过程的截面图;

[0028]

图17是示出接着图16的半导体器件的制造过程的截面图;

[0029]

图18是示出接着图17的半导体器件的制造过程的截面图;

[0030]

图19是示出第三修改示例的ldmosfet的器件结构的截面图;

[0031]

图20是示出第三修改示例的半导体器件的制造过程的截面图;

[0032]

图21是示出接着图20的半导体器件的制造过程的截面图;

[0033]

图22是示出接着图21的半导体器件的制造过程的截面图;

[0034]

图23是示出第四修改示例的ldmosfet的器件结构的截面图;

[0035]

图24是示出第四修改示例的半导体器件的制造过程的截面图;

[0036]

图25是示出接着图24的半导体器件的制造过程的截面图;以及

[0037]

图26是示出接着图25的半导体器件的制造过程的截面图。

具体实施方式

[0038]

在用于说明实施例的所有附图中,原则上,相同的构件用相同的附图标记表示,并且省略其重复描述。注意,为了清楚起见,甚至平面图也可能被加影线。

[0039]

改进研究

[0040]

本发明人发现,在采用阶梯绝缘膜的ldmosfet中,关于由于将热载流子注入到阶梯绝缘膜中而导致导通电阻增加,存在新的改进空间。因此,将描述当热载流子注入到阶梯绝缘膜中时ldmosfet的导通电阻增加的机制。

[0041]

图1是用于说明当热载流子注入到阶梯绝缘膜中时ldmosfet的导通电阻增加的机制的流程图。

[0042]

在图1中,首先,在ldmosfet的源极与漏极之间施加有高电压的状态下,通过向栅极电极施加高于阈值电压的栅极电压,ldmosfet导通(s101)。这导致电子从源极通过沟道

流向漏极。此时,由于在源极与漏极之间施加的高电压加速了电子,因此生成热载流子(s102)。特别地,由于阶梯绝缘膜的角部附近是高电场,因此通过高电场进行加速而生成的热载流子克服了阶梯绝缘膜的位垒,并且热载流子被注入到阶梯绝缘膜中(s103)。因此,固定电荷(负电荷)被俘获在阶梯绝缘膜中(s104)。因此,由于阶梯绝缘膜带负电(负),在与阶梯绝缘膜接触的n型降低表面场(reduce surface field)resurf层的表面上发生耗尽现象(s105)。然后,由于该耗尽区用作绝缘区,从源极通过沟道流向漏极的电子将被绕过,来避免在n型resurf层的表面上形成耗尽区(s106)。

[0043]

如上所述,ldmosfet的导通电阻由于以下两者而增加:“因素1”,即,由热载流子注入到阶梯绝缘膜中而引起的n型resurf层的耗尽,以及“因素2”,即,距离变长,因为电子流过的路径是交替路径(s107)。通过这种机制,在采用阶梯绝缘膜的ldmosfet中,关于由于将热载流子注入到阶梯绝缘膜中而导致导通电阻增加的改进空间变得明显。

[0044]

因此,在本实施例中,对于上述使用阶梯绝缘膜的ldmosfet中存在的导通电阻的增加,进行了改进。在下文中,将描述应用了该器件的本实施例中的技术思想。

[0045]

本实施例的基本构思

[0046]

本实施例的基本构思是在ldmosfet中设置有电位控制膜,以在位于阶梯绝缘膜下方的半导体衬底的表面上形成电子的位垒。这允许电子流动的电流路径通过形成在位于阶梯绝缘膜下方的半导体衬底的表面上的位垒,而从“半导体衬底的表面”被转移到“半导体衬底的内部(体内部)”。即,由于位垒将电子从半导体衬底表面移开,电子流过的电流路径从“半导体衬底表面”转移到“半导体衬底的内部(体内部)”。这表示,电子流过的电流路径从阶梯绝缘膜与半导体衬底之间的界面移开,从而抑制了热载流子注入到阶梯绝缘膜中。因此,根据基本构思,可以抑制由热载流子注入到阶梯绝缘膜中引起的ldmosfet的导通电阻的增加。

[0047]

在下文中,将参考附图详细描述本实施例。

[0048]

图2是用于说明本实施例的基本构思的图。在图2中,ldmosfet100具有半导体衬底1。在半导体衬底1中,形成有p型resurf层10和n型resurf层11,n型resurf层11形成在p型resurf层10上。n型resurf层11也称为n型漂移层。在半导体衬底1上形成有栅极电介质膜12,并且在栅极电介质膜12上形成有电位控制膜13。电位控制膜13与阶梯绝缘膜14接触,并且与阶梯绝缘膜14接触的场板部15和与电位控制膜13接触的栅极电极16一体地形成。此外,在n型resurf层11中形成有由n型半导体区形成的漏极区17,以与阶梯绝缘膜14对准。此外,在半导体衬底1中形成有p型体区18,并且由n型半导体区形成的源极区和由p型半导体区形成的体接触区20被形成为被包括在p型体区18中。

[0049]

本实施例中的基本构思是通过设置在如上所述配置的ldmosfet 100中的电位控制膜13,在位于阶梯绝缘膜14下方的半导体衬底1的表面上形成电子的位垒。具体地,如图2的右侧所示,由于电位控制膜13的存在,半导体衬底1的表面处的电位从实线a转移到虚线b。在这种情况下,从电子的角度来看,半导体衬底1的表面处的电位朝向高能方向转移。这表示,电子从半导体衬底1的表面处朝向高能量转移的电位受到的排斥力增加。这导致电子流过的电流路径从“半导体衬底1的表面”转移到“半导体衬底1的内部(体内部)”。这表示,电子流过的电流路径从阶梯绝缘膜与半导体衬底之间的界面移开,从而抑制了热载流子注入到阶梯绝缘膜中。

[0050]

例如,图3是示意性地示出在其中未提供有电位控制膜13的ldmosfet中电子流动的状态的图。

[0051]

如图3所示,电子从源极区19通过形成在p型体区18的表面上的沟道流向漏极区17。此时,如图3所示,由施加在漏极区17与源极区19之间的高电压生成的热载流子,通过阶梯绝缘膜14的角部附近的高电场被注入到阶梯绝缘膜14中。结果,在图3所示的ldmosfet中,由注入到阶梯绝缘膜14中的热载流子引起的导通电阻增加。

[0052]

另一方面,图4是示意性地示出在其中体现了提供电位控制膜13的基本构思的ldmosfet中电子流动的状态的图。

[0053]

如图4所示,电子从源极区19通过形成在p型体区18的表面上的沟道流向漏极区17。此时,在图4所示的ldmosfet中,电位控制膜13在半导体衬底1的表面上形成对电子施加排斥力的位垒pb。因此,如图4所示,电子流过的电流路径从“半导体衬底1的表面”转移到“半导体衬底1的内部(体内部)”。结果,电子流过的电流路径从阶梯绝缘膜14与半导体衬底1之间的界面移开,从而抑制了热载流子注入到阶梯绝缘膜14中。因此,在图4所示的ldmosfet中,可以抑制由热载流子注入到阶梯绝缘膜14中引起的导通电阻的增加。

[0054]

由以上可知,从减小导通电阻的观点来看,通过电位控制膜13在位于阶梯绝缘膜14下方的半导体衬底1的表面上形成电子的位垒pb的基本构思是有效的技术思想。在下文中,将描述体现该基本构思的实现的示例。

[0055]

ldmosfet的器件结构

[0056]

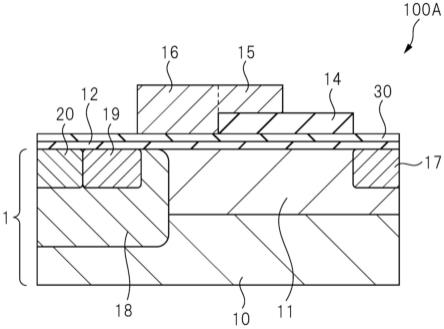

图5是示出ldmosfet 100a的示意性器件结构的截面图。

[0057]

在图5中,ldmosfet例如具有由硅构成的半导体衬底1。半导体衬底1具有p型resurf层10和n型resurf层11,n型resurf层11形成在p型resurf层10(n型漂移层)上。在半导体衬底1上形成有由例如氧化硅膜形成的栅极电介质膜12。

[0058]

在栅极电介质膜12上形成有由例如n型多晶硅膜形成的栅极电极16。这里,“形成在栅极电介质膜12上的栅极电极16”用于广义的意图,不仅包括其中栅极电极16形成在栅极电介质膜12正上方的配置,而且也包括其中高电介质常数膜30形成在栅极电介质膜12上并且栅极电极16形成在高电介质常数膜30上的配置,如图5所示。

[0059]

具体地,在图5中,在栅极电介质膜12上形成有高电介质常数膜30,在高电介质常数膜30上形成有栅极电极16。

[0060]

在此,本说明书中的“高电介质常数膜30”定义为电介质常数高于硅的膜。在本实施例中,如图5所示,高电介质常数膜30包括夹在栅极电介质膜12与栅极电极16之间的“第一部分”、以及夹在阶梯绝缘膜14与栅极电介质膜12之间的“第二部分”。

[0061]

接着,ldmosfet 100a包括与栅极电极16一体形成的场板部15、以及与场板部15接触的阶梯绝缘膜14。阶梯绝缘膜14由例如氧化硅膜形成。高电介质常数膜30与阶梯绝缘膜14接触。

[0062]

随后,如图5所示,在n型resurf层11中形成有由与阶梯绝缘膜14对准的n型半导体区形成的漏极区17。此外,在半导体衬底1中形成有由p型半导体区形成的p型体区18,并且在p型体区18中,形成有作为n型半导体区的源极区19和作为p型半导体区的体接触区20。源极区19和体接触区20彼此电连接,并且例如被提供有0v的地电位。结果,地电位也被提供给与体接触区20电连接的p型体区18。另一方面,漏极区17被提供有正电位。

[0063]

在此,图5所示的高电介质常数膜30是图2所示的电位控制膜13的一个示例。即,高电介质常数膜30用作电位控制膜13,用于在位于阶梯绝缘膜14下方的半导体衬底1的表面上形成电子的位垒。更具体地,如后所述,高电介质常数膜30具有通过转移位于阶梯绝缘膜14下方的半导体衬底1的表面上的费米能级而在表面上形成位垒的功能。具有这种功能的高电介质常数膜30包括例如hfsio、hfsion、hfalon、y2o3或al2o3中的任何一种。

[0064]

如上所述,配置了ldmosfet 100a。

[0065]

ldmosfet的操作

[0066]

接下来,描述ldmosfet 100a的操作。

[0067]

首先,将描述ldmosfet 100a的导通操作。在图5中,在向漏极区17提供正电位同时向源极区19提供地电位的状态下,高于阈值电压的栅极电压被施加到栅极电极16。然后,在位于栅极电极16下方的p型体区18的表面上形成用作沟道层的反型层(n型层)。因此,电子依次在源极区19、沟道层(反型层)、n型resurf层11和漏极区17的路径中流动。以这种方式,ldmosfet 100a以导通状态操作。

[0068]

随后,将描述ldmosfet 100a的截止操作。在ldmosfet 100a的导通状态下,小于阈值电压的栅极电压(例如,0v)被施加到栅极电极16。然后,形成在p型体区18的表面上的反型层消失。结果,电子从源极区19到漏极区17的流动路径被阻断。以这种方式,ldmosfet 100a被截止。

[0069]

本实施例的特征

[0070]

接下来,将描述本实施例的特征点。

[0071]

本实施例的特征点是,例如,如图5所示,高电介质常数膜30用作电位控制膜13,用于在位于阶梯绝缘膜14下方的半导体衬底1的表面上形成电子的位垒。换言之,本实施例的特征点在于,通过高电介质常数膜30在位于阶梯绝缘膜14下方的半导体衬底1的表面上形成位垒,并且电子流过的电流路径通过这个位垒从“半导体衬底的表面”转移到“半导体衬底的内部(体内部)”。结果,根据本实施例,电子流过的路径可以从阶梯绝缘膜14与半导体衬底1之间的界面移开,从而抑制热载流子注入到阶梯绝缘膜14中。结果,根据本实施例,可以有效地抑制由热载流子注入到阶梯绝缘膜14中引起的ldmosfet的导通电阻的增加。

[0072]

在下文中,将描述高电介质常数膜30用作电位控制膜13。

[0073]

图6a是示意性地示出在n型resurf层11上形成有例如由氧化硅膜构成的栅极电介质膜12时、n型resurf层11的表面处的能带结构的图。如图6a所示,由于n型resurf层11是n型半导体层,所以费米能级ef存在于导带的下端附近。

[0074]

然而,在n型resurf层11上,不仅形成有由氧化硅膜构成的栅极电介质膜12,而且还形成有高电介质常数膜30,包括例如hfsio、hfsion、hfalon、y2o3或al2o3等,该高电介质常数膜30的构成材料具有高于硅的电介质常数并且该高电介质常数膜30在该栅极电介质膜12上,费米能级ef从导带的下端移开,发生所谓的“费米能级钉扎”现象。具体地,图6b是示意性地示出在n型resurf层11上形成有由氧化硅膜构成的栅极电介质膜12和高电介质常数膜30时、n型resurf层11的表面处的能带结构的图。如图6b所示,尽管n型resurf层11是n型半导体层,通过由于高电介质常数膜30的存在而导致的“费米能级钉扎”,可以看出,费米能级ef向远离导带下端的方向转移。在本实施例中,该“费米能级钉扎”用于在位于阶梯绝缘膜14下方的半导体衬底1的表面上形成位垒。下面将描述这一点。

[0075]

当图6a和图6b的费米能级ef与相同能级匹配时,费米能级如图7a和图7b所示。图7a是示意性地示出例如在n型resurf层11上形成有由氧化硅膜构成的栅极电介质膜12时n型resurf层11的表面处的能带结构的图。图7b是示意性地示出在n型resurf层11上形成有由氧化硅膜构成的栅极电介质膜12和高电介质常数膜30时n型resurf层11的表面处的能带结构的图。

[0076]

从图7a和图7b所示,当在n型resurf层11上形成高电介质常数膜30时,可以看出,通过“费米能级钉扎”,n型resurf层11的表面处的能带结构朝向高能量的方向转移。这表示,通过设置高电介质常数膜30,n型resurf层11的表面的能级电性地升高,换言之,这表示,在位于阶梯绝缘膜14下方的半导体衬底1的表面上形成有电子的位垒。通过这种机制,可以理解,高电介质常数膜30用作电位控制膜13。

[0077]

如上所述,可以说,本实施例的特征点是,利用由高电介质常数膜30引起的“费米能级钉扎”现象,在位于阶梯绝缘膜14下方的半导体衬底1的表面上形成位垒。利用该特征点,通过由位垒引起的排斥力,电子流过的路径可以从阶梯绝缘膜14与半导体衬底1之间的界面移开。因此,根据本实施例,能够抑制热载流子注入到阶梯绝缘膜14中,并且结果,能够抑制由热载流子注入到阶梯绝缘膜14中而引起的ldmosfet的导通电阻的增加。

[0078]

包括ldmosfet的半导体器件的制造方法

[0079]

接下来,将描述制造包括ldmosfet的半导体器件的方法。

[0080]

首先,如图8所示,制备例如由硅构成的半导体衬底1。在半导体衬底1上形成牺牲氧化硅膜35之后,通过离子注入在半导体衬底1中形成p型resurf层10和n型resurf层11。具体地,p型resurf层10是通过将硼作为p型杂质(受主)注入到半导体衬底1中而形成的。另一方面,n型resurf层11是通过将磷(p)作为n型杂质(施主)注入到半导体衬底1中而形成的。

[0081]

接下来,如图9所示,通过使用例如热氧化方法在半导体衬底1上形成由氧化硅膜形成的栅极电介质膜12。此后,通过使用ald(原子层沉积)方法或cvd(化学气相沉积)方法形成高电介质常数膜30。作为高电介质常数膜30,例如,可以提及hfsio膜、hfsion膜、hfalon膜、y2o3膜和al2o3膜。然后,例如,通过使用cvd方法,在高电介质常数膜30上形成氧化硅膜14a。

[0082]

随后,如图10所示,通过使用光刻技术和蚀刻技术对氧化硅膜14a进行图案化以形成阶梯绝缘膜14。接下来,通过使用例如cvd方法,在高电介质常数膜30上形成多晶硅膜以覆盖阶梯绝缘膜14。然后,通过使用光刻和蚀刻技术对多晶硅膜进行图案化。因此,由多晶硅膜形成的栅极电极16和场板部15一体地形成。此后,通过使用光刻技术和倾斜离子注入方法将作为p型杂质的硼注入到半导体衬底1中以形成p型体区18。

[0083]

接下来,如图5所示,通过使用光刻技术和离子注入方法,将作为n型杂质的磷注入到半导体衬底1中以形成漏极区17和源极区19,并且将作为p型杂质的硼注入到半导体衬底1中以形成体接触区20。此后,通过形成层间绝缘膜的层间绝缘膜形成步骤和形成布线的布线形成步骤,可以制造包括ldmosfet 100a的半导体器件。

[0084]

第一修改示例

[0085]

在上述实施例中,例如,如图5所示,高电介质常数膜30包括夹在栅极电介质膜12与栅极电极16之间的“第一部分”、以及夹在阶梯绝缘膜14与栅极电介质膜12之间的“第二部分”。

[0086]

这里,从在位于阶梯绝缘膜14下方的半导体衬底1的表面上形成电子位垒的观点来看,高电介质常数膜30的“第二部分”是重要的。另一方面,高电介质常数膜30的“第一部分”与栅极电介质膜12构成叠层膜,并且该叠层膜影响用于形成反型层的阈值电压。即,从在位于阶梯绝缘膜14下方的半导体衬底1的表面上形成电子的位垒的观点来看,高电介质常数膜30的“第一部分”不是必需的。相反,通过由高电介质常数膜30的“第一部分”引起的“费米能级钉扎”,来增加用于形成反型层的阈值电压存在缺点。

[0087]

因此,图12是示意性地示出本第一修改示例中的ldmosfet100b的器件结构的截面图。如图12所示,高电介质常数膜30仅由夹在阶梯绝缘膜14与栅极电介质膜12之间的“第二部分”构成。结果,根据本第一修改示例,能够在位于阶梯绝缘膜14下方的半导体衬底1的表面上形成电子的位垒,同时抑制了用于形成反型层的阈值电压增加的副作用。

[0088]

包括ldmosfet的半导体器件的制造方法

[0089]

在本第一修改示例中的包括ldmosfet的半导体器件中,图8和图9所示的步骤与上述实施例相同。接下来,如图13所示,通过使用蚀刻技术,去除从阶梯绝缘膜14暴露的高电介质常数膜30。结果,可以形成仅由夹在阶梯绝缘膜14与栅极电介质膜12之间的“第二部分”构成的高电介质常数膜30。

[0090]

随后,通过使用例如cvd方法,在栅极电介质膜12上形成多晶硅膜以覆盖阶梯绝缘膜14。然后,通过使用光刻和蚀刻技术对多晶硅膜进行图案化。因此,由多晶硅膜形成的栅极电极16和场板部15一体地形成。此后,通过使用光刻技术和倾斜离子注入方法,将作为p型杂质的硼注入到半导体衬底1中以形成p型体区18。

[0091]

接下来,如图12所示,通过使用光刻技术和离子注入方法,将作为n型杂质的磷注入到半导体衬底1中以形成漏极区17和源极区19,并且将作为p型杂质的硼注入到半导体衬底1中以形成体接触区20。此后,通过形成层间绝缘膜的层间绝缘膜形成步骤和形成布线的布线形成步骤,可以制造包括ldmosfet 100b的半导体器件。

[0092]

第二修改示例

[0093]

ldmosfet的器件结构

[0094]

图15是示意性地示出本第二修改示例中的ldmosfet 100c的器件结构的截面图。在图15中,第二修改示例的特征点在于,在暴露的栅极电介质膜12、栅极电极16、场板部15、暴露的阶梯绝缘膜14之上形成高电介质常数膜30。特别地,本第二修改示例中的高电介质常数膜30的膜厚度比上述实施例和第一修改示例中的高电介质常数膜30的膜厚度厚。这是因为,考虑到由于高电介质常数膜30设置在阶梯绝缘膜14上方而不是下方,从而降低了在半导体衬底1的表面上形成位垒的效果,在本第二修改示例中,通过增加高电介质常数膜30的膜厚度来确保形成位垒的效果。以这种方式,配置了本第二修改示例中的ldmosfet 100c。

[0095]

包括ldmosfet的半导体器件的制造方法

[0096]

在本第二修改示例中的包括ldmosfet的半导体器件中,图8所示的步骤与上述实施例相同。接下来,如图16所示,通过使用例如cvd法在半导体衬底1上形成氧化硅膜之后,通过使用光刻技术和蚀刻技术对氧化硅膜进行图案化以形成阶梯绝缘膜14。此后,如图17所示,通过使用例如热氧化法在半导体衬底1的暴露表面上形成栅极电介质膜12。

[0097]

接下来,如图18所示,通过使用例如cvd法在栅极电介质膜12和阶梯绝缘膜14上形

成多晶硅膜。然后,通过使用光刻和蚀刻技术对多晶硅膜进行图案化。因此,由多晶硅膜形成的栅极电极16和场板部15一体地形成。此后,通过使用光刻技术和倾斜离子注入方法将作为p型杂质的硼注入到半导体衬底1中以形成p型体区18。接下来,通过使用光刻技术和离子注入方法,将作为n型杂质的磷注入到半导体衬底1中以形成漏极区17和源极区19,并且将作为p型杂质的硼注入到半导体衬底1中以形成体接触区20。然后,如图15所示,形成高电介质常数膜30以覆盖暴露的栅极电介质膜12、栅极电极16、场板部15和暴露的阶梯绝缘膜14。此后,通过形成层间绝缘膜的层间绝缘膜形成步骤和形成布线的布线形成步骤,可以制造包括ldmosfet 100c的半导体器件。

[0098]

第二修改示例的优点

[0099]

在本第二修改示例中,也可以通过膜厚度较厚的高电介质常数膜30在位于阶梯绝缘膜14下方的半导体衬底1的表面上形成电子的位垒,但是由于在栅极电极16下方不存在高电介质常数膜30,因此可以抑制用于形成反型层的阈值电压增加的副作用。

[0100]

特别地,在本第二修改示例中,由于不需要如上述第一修改示例那样对高电介质常数膜30进行图案化的步骤,因此能够抑制用于形成反型层的阈值电压的上升而不增加图案化步骤,同时在位于阶梯绝缘膜14下方的半导体衬底1的表面上形成电子位垒。

[0101]

第三修改示例

[0102]

ldmosfet的器件结构

[0103]

图19是示意性地示出本第三修改示例中的ldmosfet 100d的器件结构的截面图。在图19中,本第三修改示例的特征点在于,以阶梯绝缘膜14具有与场板部15接触的“接触部”和从场板部15突出的“非接触部”为前提,“非接触部”由其中形成有凹部的“薄膜部分”和比“薄膜部分”厚的“厚膜部分”构成,并且高电介质常数膜30形成在暴露的栅极电介质膜12、栅极电极16、场板部15和暴露的阶梯绝缘膜14之上。此时,“厚膜部分”的膜厚度设置为“t1”并且“薄膜部分”的膜厚度设置为“t2”,t2《t1的关系成立。

[0104]

包括ldmosfet的半导体器件的制造方法

[0105]

在第三修改示例中的包括ldmosfet的半导体器件中,直到图16所示的步骤与第二修改示例相同。此后,如图20所示,通过使用光刻技术和蚀刻技术在阶梯绝缘膜14中形成凹部40。然后,如图21所示,通过使用例如热氧化法在半导体衬底1的暴露表面上形成栅极电介质膜12。

[0106]

接下来,如图22所示,通过使用例如cvd法在栅极电介质膜12和阶梯绝缘膜14上形成多晶硅膜。然后,通过使用光刻和蚀刻技术对多晶硅膜进行图案化。因此,由多晶硅膜形成的栅极电极16和场板部15一体地形成。此后,通过使用光刻技术和倾斜离子注入方法将作为p型杂质的硼注入到半导体衬底1中以形成p型体区18。接下来,通过使用光刻技术和离子注入方法,将作为n型杂质的磷注入到半导体衬底1中以形成漏极区17和源极区19,并且将作为p型杂质的硼注入到半导体衬底1中以形成体接触区20。然后,如图19所示,形成高电介质常数膜30以覆盖暴露的栅极电介质膜12、栅极电极16、场板部15和暴露的阶梯绝缘膜14。此后,通过形成层间绝缘膜的层间绝缘膜形成步骤和形成布线的布线形成步骤,可以制造包括ldmosfet 100d的半导体器件。

[0107]

第三修改示例的优点

[0108]

根据本第三修改示例,其中形成有凹部的“薄膜部分”形成在阶梯绝缘膜14中,并

且高电介质常数膜30也形成在“薄膜部分”的凹部内部。在这点上,由于可以确保在半导体衬底1的表面上形成位垒的效果,因此在本第三修改示例中,与第二修改示例相比,具有可以减小高电介质常数膜30的膜厚度的优点。

[0109]

第四修改示例

[0110]

ldmosfet的器件结构

[0111]

图23是示意性地示出本第四修改示例中的ldmosfet 100e的器件结构的截面图。在图23中,本第四修改示例的特征点在于,包括设置在阶梯绝缘膜14中的凹部在内的“薄膜部分”的膜厚度“t2”等于栅极电介质膜12的膜厚度。

[0112]

包括ldmosfet的半导体器件的制造方法

[0113]

在本第四修改示例中的包括ldmosfet的半导体器件中,直到图16所示的步骤与第二修改示例相同。此后,如图24所示,通过使用光刻技术和蚀刻技术在阶梯绝缘膜14中形成凹部40。此时,凹部40被形成以使得凹部40的底部到达半导体衬底1的表面。然后,如图25所示,通过使用例如热氧化法在半导体衬底1的暴露表面上形成栅极电介质膜12。这里,栅极电介质膜12也形成在在凹部40的底部处暴露的半导体衬底1的表面上。

[0114]

形成在凹部40的底部处的栅极电介质膜12的膜厚度与形成在半导体衬底1的另一面上的栅极电介质膜12的膜厚度相等。

[0115]

接下来,如图26所示,通过使用例如cvd法在栅极电介质膜12和阶梯绝缘膜14上形成多晶硅膜。然后,通过使用光刻和蚀刻技术对多晶硅膜进行图案化。因此,由多晶硅膜形成的栅极电极16和场板部15一体地形成。此后,通过使用光刻技术和倾斜离子注入方法将作为p型杂质的硼注入到半导体衬底1中以形成p型体区18。接下来,通过使用光刻技术和离子注入方法,将作为n型杂质的磷注入到半导体衬底1中以形成漏极区17和源极区19,并且将作为p型杂质的硼注入到半导体衬底1中以形成体接触区20。然后,如图23所示,形成高电介质常数膜30以覆盖暴露的栅极电介质膜12、栅极电极16、场板部15和暴露的阶梯绝缘膜14。此后,通过形成层间绝缘膜的层间绝缘膜形成步骤和形成布线的布线形成步骤,可以制造包括ldmosfet 100e的半导体器件。

[0116]

第四修改示例的优点

[0117]

例如,在上述第三修改示例中,由于“薄膜部分”的膜厚度“t2”与栅极电介质膜12的膜厚度不同,因此需要在形成凹部40的步骤中调节凹部40的蚀刻量(参见图20)。另一方面,在本第四修改示例中,由于“薄膜部分”的膜厚度“t2”与栅极电介质膜12的膜厚度相等,例如,如图24所示,在形成凹部40的步骤中,也可以形成凹部40以使半导体衬底1在凹部40的底部处暴露,而不需要微调凹部40的蚀刻量。这是因为,“过蚀刻”也被允许,从而促进了用于形成凹部40的蚀刻步骤。然后,在本第四修改示例中,通过对半导体衬底1的暴露的整个表面(包括从凹部40的底部暴露的半导体衬底1的表面)应用热氧化法,因为栅极电介质膜12是也形成在凹部40的底部处,“薄膜部分”的膜厚度“t2”可以自动地等于其他区域的栅极电介质膜12的膜厚度。

[0118]

以上,基于实施例对本发明人的发明进行了详细说明,但本发明不限于上述实施例,在不脱离其主旨的范围内,当然可以进行各种变形。

[0119]

实施例包括以下实施例。

[0120]

附录1

[0121]

根据实施例的制造半导体器件的方法

[0122]

一种半导体器件的制造方法,该方法包括:

[0123]

(a)在半导体衬底上形成栅极电介质膜;

[0124]

(b)在栅极电介质膜上形成电介质常数高于硅的高电介质常数膜;

[0125]

(c)形成与高电介质常数膜接触的阶梯绝缘膜;以及

[0126]

(d)一体地形成与高电介质常数膜接触的栅极电极和与阶梯绝缘膜接触的场板部。

[0127]

附录2

[0128]

根据第一修改示例的制造半导体器件的方法

[0129]

一种半导体器件的制造方法,该方法包括:

[0130]

(a)在半导体衬底上形成栅极电介质膜;

[0131]

(b)在栅极电介质膜上形成电介质常数高于硅的高电介质常数膜;

[0132]

(c)形成与高电介质常数膜接触的阶梯绝缘膜;

[0133]

(d)去除从阶梯绝缘膜暴露的高电介质常数膜;以及

[0134]

(e)一体地形成与栅极电介质膜接触的栅极电极和与阶梯绝缘膜接触的场板部。

[0135]

附录3

[0136]

根据第二修改示例的制造半导体器件的方法

[0137]

一种半导体器件的制造方法,该方法包括:

[0138]

(a)在半导体衬底上形成阶梯绝缘膜;

[0139]

(b)在半导体衬底上除阶梯绝缘膜之外的位置形成栅极电介质膜;

[0140]

(c)一体形成与栅极电介质膜接触的栅极电极和与阶梯绝缘膜接触的场板部;以及

[0141]

(d)形成电介质常数高于硅的高电介质常数膜以与栅极电极、场板部和阶梯绝缘膜接触。

[0142]

附录4

[0143]

根据第三修改示例的制造半导体器件的方法

[0144]

一种半导体器件的制造方法,该方法包括:

[0145]

(a)在半导体衬底上形成阶梯绝缘膜;

[0146]

(b)在阶梯绝缘膜上形成凹部;

[0147]

(c)在半导体衬底上除阶梯绝缘膜之外的位置形成栅极电介质膜;

[0148]

(d)一体形成与栅极电介质膜接触的栅极电极和与阶梯绝缘膜接触的场板部,场板部不与凹部接触;以及

[0149]

(e)形成电介质常数高于硅的高电介质常数膜以与栅极电极、场板部和阶梯绝缘膜接触。

[0150]

附录5

[0151]

根据第四修改示例的制造半导体器件的方法

[0152]

一种半导体器件的制造方法,该方法包括:

[0153]

(a)在半导体衬底上形成阶梯绝缘膜;

[0154]

(b)在阶梯绝缘膜中形成到达半导体衬底的凹部。

[0155]

(c)在包括凹部底部的半导体衬底上形成栅极电介质膜;

[0156]

(d)一体形成与栅极电介质膜接触的栅极电极和与阶梯绝缘膜接触的场板部,场板部不与凹部接触;以及

[0157]

(e)形成电介质常数高于硅的高电介质常数膜以与栅极电极、场板部、阶梯绝缘膜和凹部的内侧表面接触。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。