一种高稳定性倒装led芯片及其制备方法

技术领域

1.本发明涉及光电子制造技术领域,尤其涉及一种高稳定性的倒装led芯片及其制备方法。

背景技术:

2.led是一种pn结电致发光的发光器件,作为新一代的固体冷光源,具有高电光转换效率、低能耗、寿命长、节能环保、高可靠性等优点,被广泛运用于室内照明、光伏、医疗照明、汽车车灯、lcd显示屏等各个场所。

3.传统led芯片一般为蓝宝石衬底,有源层发光不均匀、散热性差、部分膜层角度大、结温高等问题,严重影响led芯片的可靠性能。

4.按芯片结构分类,led芯片可分为正装芯片、倒装芯片和垂直芯片三种。其中,正装芯片存在电流拓展性差、发光不均匀、散热性差等问题;垂直芯片则存在制作过程及其复杂、制作成本高等问题,故而目前市场中垂直芯片相对较少;而倒装芯片具有优于正装芯片的性能,低于垂直芯片的成本,被市场广泛关注。但目前市倒装led芯片存在由于芯片电流分布不均匀、部分膜层角度大、芯片结温高、工艺相对复杂等因素引起的芯片稳定性差的问题,严重影响着倒装led芯片的应用。

技术实现要素:

5.本发明所要解决的技术问题在于,提供一种高稳定性的倒装led芯片的制备方法,其可提升芯片良率和稳定性。

6.本发明还要解决的技术问题在于,提供一种高稳定性的倒装led芯片。

7.为了解决上述技术问题,本发明提供了一种高稳定性倒装led芯片的制备方法,其包括:

8.(1)提供衬底,在所述衬底上形成n-gan层、mqw层和p-gan层;

9.(2)采用第一光刻胶为掩膜,刻蚀形成多个第一孔道,刻蚀后去除第一光刻胶;其中,所述第一孔道贯穿至所述n-gan层;

10.(3)采用第二光刻胶为掩膜,对预设区域的第一孔道进行刻蚀,形成多个第二孔道;刻蚀后去除第二光刻胶;其中,所述第二孔道贯穿至所述衬底;

11.(4)在所述第一孔道、第二孔道、衬底、p-gan层上形成电流扩展层;

12.(5)采用第三光刻胶为掩膜,刻蚀去除第一孔道、第二孔道、衬底表面的电流扩展层以及p-gan层上的预设量的电流扩展层;刻蚀后去除所述第三光刻胶;

13.(6)在所述第一孔道、第二孔道、衬底、p-gan层和电流扩展层上形成钝化保护层;

14.(7)采用第四光刻胶为掩膜,刻蚀去除电流扩展层上的钝化保护层;

15.(8)采用第四光刻胶为掩膜,在所述电流扩展层上形成金属反射层,然后去除所述第四光刻胶;

16.(9)采用第五光刻胶为掩膜,在所述金属反射层上、靠近所述金属反射层的钝化保

护层上形成金属导电层,然后去除第五光刻胶;

17.(10)在所述钝化保护层、金属导电层上形成第一绝缘层;

18.(11)采用第六光刻胶为掩膜,在所述第一孔道的底部形成第三孔道;然后去除第六光刻胶;其中,所述第三孔道贯穿所述第一绝缘层和钝化保护层,暴露出所述n-gan层;

19.(12)采用第七光刻胶为掩膜,在所述第一孔道以及所述第一绝缘层的预设位置形成n电极层,然后去除第七光刻胶;

20.(13)在所述n电极层、第一绝缘层上形成第二绝缘层;

21.(14)采用第八光刻胶为掩膜,形成第四孔道和第五孔道,然后去除第八光刻胶;所述第四孔道贯穿至所述n电极层,所述第五孔道贯穿至所述金属导电层;

22.(15)采用第九光刻胶为掩膜,在所述第四孔道、第五孔道内形成焊盘层,然后去除第九光刻胶;

23.(16)研磨减薄所述衬底,沿所述第二孔道劈裂,即得到高稳定性的倒装led芯片成品。

24.作为上述技术方案的改进,步骤(4)中,通过磁控溅射法或电子束蒸发法形成所述电流扩展层,所述电流扩展层由ito、izo、azo中的一种或多种制成;

25.步骤(5)中,采用ito蚀刻液腐蚀去除所述电流扩展层。

26.作为上述技术方案的改进,步骤(6)中,通过磁控溅射法、电子束蒸发法或pecvd法形成所述钝化保护层,所述钝化保护层由sio2、sin

x

、sin

x

oy中的一种或多种制成,所述钝化保护层的厚度为

27.步骤(7)中,所述第四光刻胶为正性光刻胶,采用湿法刻蚀去除电流扩展层上的钝化保护层,且过刻蚀5~10μm,以使金属反射层两侧与钝化保护层之间存在5~10μm的间隙,所述钝化保护层的膜层角度为20~40

°

。

28.作为上述技术方案的改进,步骤(8)中,通过磁控溅射法或电子束蒸发法形成所述金属反射层;

29.所述金属反射层包括ag层和保护层,所述保护层由ti、w、pt中的一种或多种制成;所述金属反射层的厚度为所述金属反射层的膜层角度为20~40

°

,所述保护层的厚度为

30.作为上述技术方案的改进,步骤(9)中,通过电子束蒸镀法形成金属导电层,所述金属导电层由cr、al、ti、pt、au中的一种或多种制成;所述金属导电层的厚度为所述金属导电层的膜层角度为20~40

°

。

31.作为上述技术方案的改进,所述钝化保护层包括sio2层;所述金属导电层覆盖部分靠近所述金属导电层的钝化保护层,以使所述金属导电层与所述sio2层复合形成全方位反射镜结构;

32.所述金属导电层的顶层为pt层和/或ni层;其中,pt层和/或ni层厚度为所述pt层和/或ni层为干法刻蚀阻挡层,阻挡后续干法刻蚀技术对金属导电层的刻蚀损伤。

33.作为上述技术方案的改进,步骤(10)中,采用pecvd法形成所述第一绝缘层;所述第一绝缘层由sio2、sin

x

、sin

x

oy、ti2o5中的一种或多种制成;所述第一绝缘层的膜层角度为

20~40

°

;

34.步骤(11)中,通过icp刻蚀形成第三孔道;其中,刻蚀气体为cf4和o2,刻蚀功率为100~500w,采用较低的刻蚀功率可达到无损刻蚀n型gan的目的。

35.作为上述技术方案的改进,步骤(12)中,通过电子束蒸镀法形成n电极层,所述n电极层由cr、al、ni、ti、pt、au中的一种或多种制成;所述n电极层的膜层角度为20~40

°

;

36.步骤(13)中,采用pecvd法形成所述第二绝缘层;所述第二绝缘层由sio2、sin

x

、sin

x

oy、ti2o5中的一种或多种制成;所述第二绝缘层的膜层角度为20~40

°

。

37.作为上述技术方案的改进,步骤(14)中,通过icp刻蚀形成第四孔道和第五孔道;其中,刻蚀气体为cf4和o2,刻蚀功率为100~500w;采用较低的刻蚀功率可减少金属导电层的顶层为pt层和/或ni层的刻蚀损伤。

38.步骤(15)中,通过电子束蒸镀法形成焊盘层,所述焊盘层由cr、ni、ti、pt、au、sn、ausn中的一种或多种制成。

39.相应的,本发明还公开了一种高稳定性的倒装led芯片,其由上述的制备方法制备而得。

40.实施本发明,具有如下有益效果:

41.1.本发明的高稳定性倒装led芯片的制备方法,通过第四光刻胶同时形成了钝化保护层和金属反射层,有效减少了倒装led芯片制程道数,减少了物料消耗,降低了人工成本。且通过这种制备方法,可得到坡度较缓(20~40

°

)的钝化保护层刻蚀台阶,使得金属导电层平缓过渡,使得金属反射镜与钝化保护层间距为5-10μm(单边),解决了金属反射镜沉积到钝化保护层上所引起金属反射镜爬坡和翘曲的问题,使得芯片良率和稳定性均有大幅提升。

42.2.本发明的高稳定性倒装led芯片的制备方法,使用干法刻蚀的方法合并刻蚀钝化保护层和第一绝缘层,以形成第三孔道;干法刻蚀工艺代替湿法刻蚀工艺,可解决现有湿法蚀刻过程中常出现的过蚀刻、蚀刻不净等蚀刻工艺不稳定的问题;上述干法刻蚀工艺可使得整体刻蚀角度单一化,且刻蚀台阶较缓(30-50

°

),以便于n电极层平缓过渡,避免后续膜层出现空洞、断开的现象,提高了芯片的稳定性,同时干法刻蚀工艺可稳定制作较小孔径的钝化孔,可进一步提升芯片亮度。

43.3.本发明的高稳定性倒装led芯片的制备方法,使用干法刻蚀的方法合并刻蚀去除第一绝缘层和第二绝缘层,以形成第五孔道。这种合并技术可显著减低生产成本,还可有效杜绝湿法蚀刻对金属反射层的损伤,且该技术制作的p电极区域结构简单,角度平缓,空洞率低,可焊性高,芯片整体稳定性高。

44.4.本发明的高稳定性倒装led芯片的制备方法,引入了金属导电层,显著提升了电流的横向扩展能力、降低芯片结温、提升芯片老化性能,提高芯片整体稳定性,且可保护金属反射镜不被氧化、不被湿法蚀刻所损伤,提高了芯片aoi良率,同时金属导电层有助于形成odr结构,可进一步提升芯片亮度。

附图说明

45.图1是高稳定性倒装led芯片制备方法中步骤s1后led芯片的结构示意图;

46.图2是高稳定性倒装led芯片制备方法中步骤s2后led芯片的结构示意图;

47.图3是高稳定性倒装led芯片制备方法中步骤s3后led芯片的结构示意图;

48.图4是高稳定性倒装led芯片制备方法中步骤s5后led芯片的结构示意图;

49.图5是高稳定性倒装led芯片制备方法中步骤s7后led芯片的结构示意图;

50.图6是高稳定性倒装led芯片制备方法中步骤s8后led芯片的结构示意图;

51.图7是高稳定性倒装led芯片制备方法中步骤s9后led芯片的结构示意图;

52.图8是高稳定性倒装led芯片制备方法中步骤s11后led芯片的结构示意图;

53.图9是高稳定性倒装led芯片制备方法中步骤s12后led芯片的结构示意图;

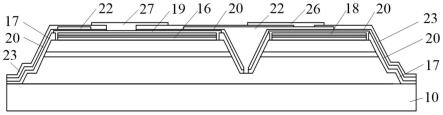

54.图10是高稳定性倒装led芯片制备方法中步骤s14后led芯片的结构示意图;

55.图11是高稳定性倒装led芯片制备方法中步骤s15后led芯片的结构示意图。

具体实施方式

56.为使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明作进一步地详细描述。仅此声明,本发明在文中出现或即将出现的上、下、左、右、前、后、内、外等方位用词,仅以本发明的附图为基准,其并不是对本发明的具体限定。

57.本发明公开了一种倒装led芯片的制备方法,其包括以下步骤:

58.s1:提供衬底,在所述衬底上形成n-gan层、mqw层和p-gan层;

59.具体的,采用mocvd法在衬底10形成n-gan层11、mqw层12和p-gan层13,但不限于此。

60.s2:采用第一光刻胶为掩膜,刻蚀形成多个第一孔道,刻蚀后去除第一光刻胶;

61.其中,光刻胶为正性光刻胶或负性光刻胶,但不限于此。刻蚀为湿法刻蚀或干法刻蚀,但不限于此。优选的为icp刻蚀。

62.具体的,刻蚀形成的第一孔道14贯穿至n-gan层11,暴露出n-gan层11、mqw层12和部分p-gan层13的侧壁表面(第一侧壁141,图2)。

63.s3:采用第二光刻胶为掩膜,对预设区域的第一孔道进行刻蚀,形成多个第二孔道;刻蚀后去除第二光刻胶;

64.其中,第二光刻胶为厚性光刻胶,但不限于此;刻蚀为湿法刻蚀或干法刻蚀,但不限于此。优选的为icp刻蚀。

65.具体的,对位于后续晶圆劈裂位置出的第一孔道的底部进行进一步刻蚀,以形成第二孔道15,第二孔道15贯穿至衬底10,其暴露p-gan层13的整个侧壁(第二侧壁151,图3)。

66.s4:在第一孔道、第二孔道、衬底、p-gan层上形成电流扩展层;

67.其中,通过电子束蒸发法或磁控溅射法在第一孔道14、第二孔道15、衬底10、p-gan层13上(即步骤s3得到的衬底的整体表面上)形成电流扩展层16。电流扩展层16由ito、izo、azo中的一种或多种制成,但不限于此。优选的,电流扩展层16为ito层。

68.s5:采用第三光刻胶为掩膜,刻蚀去除第一孔道、第二孔道、衬底表面的电流扩展层以及p-gan层上的预设量的电流扩展层;刻蚀后去除第三光刻胶;

69.其中,第二光刻胶为正性光刻胶或负性光刻胶,优选的为正性光刻胶。刻蚀为干法刻蚀或湿法刻蚀。优选的为湿法刻蚀,具体的,采用ito蚀刻液等化学药液腐蚀,去除第一孔道14内(包括第一侧壁141上)、第二孔道15(包括第二侧壁151上)内、衬底10上的电流扩展层16和p-gan层13上的预设量的电流扩展层(图4)。其中,p-gan层13上电流扩展层16的刻蚀

去除量为p-gan层13宽度的1~5%。步骤s5完成后,去除第三光刻胶所形成的掩膜。

70.s6:在第一孔道、第二孔道、衬底、p-gan层和电流扩展层上形成钝化保护层;

71.其中,通过磁控溅射法、电子束蒸发法或pecvd法在步骤s6得到的衬底表面(即第一孔道14内、第二孔道15内、衬底10上、p-gan层13上和电流扩展层16上)整体上形成钝化保护层17。其中,第一侧壁141、第二侧壁151上覆盖的钝化保护层17形成了侧壁保护结构171,其可起到阻挡金属的作用,可防止mqw层12露出导致后续金属反射层18中的ag迁移到mqw层12而漏电。

72.其中,钝化保护层17由sio2、sin

x

、sin

x

oy中的一种或多种制成,其厚度为采用此厚度的钝化保护层,可减少芯片的高低差,提升芯片的稳定性。示例性的,钝化保护层17的厚度为或但不限于此。基于上述成分、厚度的钝化保护层17,其膜层致密性和绝缘性好,且透光性好。

73.s7:采用第四光刻胶为掩膜,刻蚀去除电流扩展层上的钝化保护层;

74.其中,第四光刻胶为负性光刻胶或正性光刻胶,但不限于此;优选的为正性光刻胶;其可有效避免负性光刻胶工艺光刻底切大及工艺不稳定等问题,且正性光刻胶价格便宜,去胶工艺也相对简单。

75.刻蚀为干法刻蚀或湿法刻蚀,但不限于此。优选的,刻蚀为湿法刻蚀,具体的,可通过boe蚀刻液去除电流扩展层16上的钝化保护层17。进一步的,通过采用湿法刻蚀工艺,可在不损伤第四光刻胶所形成掩膜的情况下对钝化保护层17进行过刻蚀,即去除部分在掩膜下方的钝化保护层17。具体的,在本发明的一个实施例中,过刻蚀5~10μm,以使金属反射层18(电流扩展层16)两侧与钝化保护层17之间存在5~10μm的间隙2(参图5)。这种间隙2不仅可以预防后期金属反射层18沉积到钝化保护层17上面,引起金属反射层18爬坡和翘曲等现象,使钝化保护层17边沿出现金属小凸起等异常造成芯片esd良率差的问题;还可以预留足够的空间使后续金属导电层19沉积于此并完全覆盖包覆金属反射层18,防止金属反射层18中的ag迁移出来,提高芯片稳定性。

76.此外,通过湿法蚀刻,可保证芯片钝化保护层17的膜层角度、金属反射层18的膜层角度均为20

°‑

40

°

,确保后续需要覆盖在钝化保护层17和金属反射层18上的金属导电层19及需要覆盖在金属导电层19的其他膜层在此平缓过渡、避免出现空洞、断开的现象,提高芯片稳定性。

77.步骤s7完成后,不去除第四光刻胶形成的掩膜1(图5),直接进入步骤s8。

78.s8:采用第四光刻胶为掩膜,在所述电流扩展层上形成金属反射层,然后去除所述第四光刻胶;

79.其中,通过磁控溅射法或电子束蒸发法在电流扩展层16上形成金属反射层18,但不限于此。金属反射层18包括ag层181和保护层182,保护层182由ti、w、pt中的一种或多种制成。金属反射层18整体的厚度与钝化保护层17的厚度相当,即为采用这种方案,可减少芯片的高低差,提升芯片的稳定性。其中,保护层的厚度为

80.s9:采用第五光刻胶为掩膜,在所述金属反射层上、靠近所述金属反射层的钝化保护层上形成金属导电层,然后去除第五光刻胶;

81.其中,第五光刻胶为正性光刻胶或负性光刻胶,但不限于此。通过电子束蒸镀法形

成金属导电层19,金属导电层19由cr、al、ti、pt、au中的一种或多种,但不限于此。金属导电层19可提升金属反射层18的粘附力,减少芯粒脱落。优选的,金属导电层19为叠层结构,其采用cr或ti作为底层,主体可采用alti/alti/alti、altipt/altipt/altipt等叠层结构,这种结构的金属导电层可有效降低金属应力,降低膜层孔洞率,提升芯片稳定性;同时金属导电层19的al层和钝化保护层17的sio2层复合形成全方位反射镜结构,进一步提升芯片亮度;也保证了金属导电层19膜层角度平缓,约为20~40

°

,从而避免后续膜层在此过渡时出现空洞、断开的现象,提高芯片稳定性。进一步的,在本发明的另一个优选实施例中,金属导电层19的叠层结构中,顶层采用pt层和/或ni层,这种顶层可起到阻挡干法刻蚀的作用;从而阻挡后续干法刻蚀过程中对金属导电层19的损伤。

82.其中,金属导电层19形成的位置是金属反射层上、靠近所述金属反射层的钝化保护层上。即金属导电层19完全覆盖金属反射层18,且覆盖局部的钝化保护层17(图7),具体的,覆盖量为钝化保护层17面积的1~3%。基于这种结构,不仅有效保护金属反射层18不被氧化、不被湿法蚀刻所损伤、防止金属反射层18中ag迁移等以提升芯片的稳定性。而且金属导电层19能起到提升电流横向扩展能力的作用,即电流经过金属导电层19时会首先在金属导电层19内部横向扩展到金属导电层19覆盖的所有区域,之后再垂直向下扩展到金属反射层18内部进而垂直扩展到金属反射层18下方的电流扩展层16,可弥补金属反射层18在大电流情况下内部横向扩展能力较差的缺点,提高芯片大电流横向扩展的能力,增大电流扩展均匀性,能进一步降低芯片结温,提升芯片老化性能。

83.优选的,在本发明的一个实施例中,钝化保护层17中包括sio2层,金属导电层19与该sio2层形成了全方位反射镜结构,进一步提升了无金属反射层18区域的出光效率,提升芯片亮度。

84.s10:在钝化保护层、金属导电层上形成第一绝缘层;

85.其中,通过pecvd在步骤s9得到的衬底10表面上(即钝化保护层17和金属导电层19上)形成第一绝缘层20,第一绝缘层20由sio2、sin

x

、sin

x

oy、ti2o5中的一种或多种制成,其形成的第一绝缘层20膜层致密、绝缘性好且透光率高。

86.s11:采用第六光刻胶为掩膜,在第一孔道的底部形成第三孔道,然后去除第六光刻胶;

87.其中,第六光刻胶可为正性光刻胶或负性光刻胶。刻蚀工艺为湿法刻蚀或干法刻蚀。优选的为icp干法刻蚀。其中,刻蚀气体为cf4和o2。刻蚀后形成的第三孔道21贯穿第一绝缘层20和钝化保护层17,暴露出n-gan层11(图8)。

88.具体的,在本步骤中,需将刻蚀功率控制在合适范围内;刻蚀功率过高导致刻蚀速率过高对n型gan层的刻蚀损伤引起电压升高的问题,刻蚀功率过低则刻蚀速率小、工艺时间长、效率低;刻蚀功率一般控制在100w-500w,或者多段刻蚀功率的方式来制作如前期高功率 后期低功率两段式,即第一绝缘层20的刻蚀采用高功率刻蚀(400~500w)、接近n-gan层的钝化保护层17的刻蚀则采用低功率刻蚀(100~150w);进一步的,低功率刻蚀时还可以通过加大o2流量、降低cf4流量等工艺手段来辅助降低刻蚀速率,达到无损刻蚀n-gan层11,确保芯片电压正常。

89.本发明的步骤s11中,同时刻蚀第一绝缘层20和钝化保护层17,这种工艺称为“合并”干刻工艺。这种“合并”干刻工艺不仅避开了boe湿法蚀刻过程中常出现的过蚀刻、蚀刻

不干净等蚀刻工艺不稳定的问题,还避免对第一绝缘层20、钝化保护层17分步做boe蚀刻时出现蚀刻角度不同,导致后续膜层在此过渡时出现空洞、断开的现象,提高芯片稳定性。该“合并”干刻工艺稳定,且该工艺制作的刻蚀角度较缓(30~50

°

),可进一步使得后续的n电极层22在此平缓过渡,提高芯片的稳定性。同时干刻工艺可稳定制作较小孔径的第三孔道(5~20μm),以此来进一步增大芯片的发光面积、提升亮度。

90.s12:采用第七光刻胶为掩膜,在第一孔道以及第一绝缘层的预设位置形成n电极层,然后去除第七光刻胶;

91.其中,第七光刻胶为正性光刻胶或负性光刻胶。通过电子束蒸发法形成n电极层22。在第一孔道14以及第一绝缘层20的预设位置形成n电极层22(图9)。具体的,预设位置是指除了芯片p电极区域内每4个相邻第一孔道14中间预留的一个圆孔之外的其他区域,这样分布的n电极层会使芯片电流拓展更加均匀,降低芯片电压,进一步提高芯片散热性。

92.其中,n电极层22由cr、al、ni、ti、pt、au中的一种或几种制成。优选的,n电极层22为叠层结构,其底层金属采用cr和/或ti,其可保证n电极层22的底层金属与金属导电层19、芯片中间部分n-gan层11的粘附良好。其中间结构可采用alti/alti/alti/

……

等形式,但不限于此。金属叠层结构可以增强金属层的柔韧性、降低金属层整体的内应力;还会将叠层金属的优劣性能充分利用、提高导电性、降低成本。进一步优选的,叠层结构的顶层采用pt和/或ni,其可阻挡后续第二“合并”干刻技术对n电极层22的刻蚀损伤。

93.具体的,n电极层22的膜层角度为20-40

°

,这样可避免后续膜层在此过渡时出现空洞、断开的现象,提高芯片稳定性。

94.s13:在n电极层、第一绝缘层上形成第二绝缘层;

95.其中,通过pecvd在步骤s12得到的衬底上(即n电极层22、第一绝缘层20上)形成第二绝缘层23,第二绝缘层23由sio2、sin

x

、sin

x

oy、ti2o5中的一种或多种制成,这种第二绝缘层23膜层致密、绝缘性好且透光率高。

96.s14:采用第八光刻胶为掩膜,形成第四孔道和第五孔道,然后去除第八光刻胶;

97.其中,第八光刻胶为正性光刻胶或负性光刻胶,优选的为正性光刻胶。第四孔道和第五孔道通过干法刻蚀工艺形成。具体的,第四孔道24贯穿至n电极层22,第五孔道25贯穿至金属导电层19,第五孔道25作为p电极窗口(图10)。

98.其中,干法刻蚀工艺所采用的刻蚀气体为cf4和o2,刻蚀功率为100~500w。通过上述干法刻蚀工艺,将金属导电层19上的第一绝缘层20和第二绝缘层23同时开孔,这种工艺称为第二“合并”干刻技术。这种第二“合并”干刻技术,缩短了制程工艺时间、节省了物料、降低了人工成本、同时提高了esd良率、增强了芯片的稳定性。具体的,这种第二“合并”干刻技术可有效杜绝湿法蚀刻对金属反射层18的损伤,避免芯片结构损伤,提升芯片稳定性;且该技术制作的p电极区域极其简单,金属导电层19上的第一绝缘层20和第二绝缘层23的膜层角度相同且平缓为20-40

°

,这样可避免后续膜层在此过渡时出现空洞、断开的现象,提高芯片稳定性。此外,通过该技术制作的芯粒具有单向坡度性,有助于助焊剂的流动,改善芯片焊接工艺,芯片空洞率大大降低,芯片可焊性提高。

99.进一步的,由于本发明的金属导电层19、n电极层22的表面均采用pt和/或ni作为干法刻蚀阻挡层,可有效保护该金属下层其他结构不被干法刻蚀损伤。故本发明可采用多段刻蚀方式,例如可采用前期大功率 后期小功率的方式。示例性的,在刻蚀第二绝缘层23

时,采用大功率(400~500w);在刻蚀第一绝缘层20时,采用小功率(100~150w),基于上述工艺,可进一步提升生产效率。

100.s15:采用第九光刻胶为掩膜,在所述第四孔道、第五孔道内形成焊盘层,然后去除第九光刻胶;

101.其中,第九光刻胶为正性光刻胶或负性光刻胶。通过电子束蒸镀方法,在第四孔道24、第五孔道25内形成焊盘层,具体的,焊盘层包括第一焊盘层26和第二焊盘层27,其中,第一焊盘层26与n电极层22电连接,第二焊盘层27与金属导电层19电连接。

102.具体的,焊盘层由cr、ni、ti、pt、au、sn、ausn等导电性好的金属元素中的一种或多种制成。优选的,焊盘层为叠层结构,其底层采用cr和/或ti,以提升粘附性。中间叠层结构可采用tipt/tipt/tipt/

……

,但不限于此。金属叠层结构可以增强焊盘层的柔韧性、降低焊盘层整体的内应力;还会将叠层金属的优劣性能充分利用、提高导电性、降低成本。

103.s16:研磨减薄衬底,沿所述第二孔道劈裂,即得到高稳定性的倒装led芯片成品。

104.综上,基于本发明的制备方法,首先,通过第四光刻胶同时形成了钝化保护层和金属反射层,有效减少了倒装led芯片制程道数,减少了物料消耗。降低了人工成本。且通过这种制备方法,可得到坡度较缓(20~40

°

)的钝化保护层刻蚀台阶,使得金属导电层)平缓过度,使得芯片良率和稳定性均有大幅提升。其次,使用干法刻蚀的方法合并刻蚀钝化保护层和第一绝缘层,以形成第三孔道;这种工艺可使得整体刻蚀台阶较缓(30-50

°

),以便于n电极层平缓过渡,避免后续膜层出现空洞、断开的现象,提高了芯片的稳定性,同时干法刻蚀工艺可稳定制作较小孔径的钝化孔,可进一步提升芯片亮度。再者,使用干法刻蚀的方法合并刻蚀去除第一绝缘层和第二绝缘层,以形成第五孔道。这种合并技术可显著减低生产成本,还可有效杜绝湿法蚀刻对-金属反射层的损伤,且该技术制作的p电极区域结构简单,角度平缓,空洞率低,可焊性高,芯片整体稳定性高。最后,本发明引入了金属导电层,其可提升了电流的横向扩展能力、降低芯片结温、提升芯片老化性能,提高芯片整体稳定性,且可保护金属反射镜不被氧化、不被湿法蚀刻所损伤,提高了芯片aoi良率,同时金属导电层有助于形成odr结构,可进一步提升芯片亮度。

105.以上所述是发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。