1.本发明属于集成电路散热技术领域,主要涉及一种基于忆阻器阵列的可持续散热结构及制备方法。

背景技术:

2.忆阻器是除电阻、电容、电感之外的第四类无源元件,是一个与磁通量和电荷相关的无源电路元件。早在1971年,蔡少棠教授基于电路理论,从理论上预言了忆阻器的存在。2008年,惠普实验室首次在实验上构筑了忆阻器原型器件,证实了蔡少棠有关忆阻器的学说。忆阻器具有新颖的非线性电学性质,并兼具密度高、尺寸小、功耗低、非易失性等特点,被认为是发展下一代新型非易失性内存器的理想方案。忆阻器的第一个实物是一种三明治结构,顶电极和底电极是惰性金属,阻变机理是基于掺杂氧空穴的二氧化钛。近些年来,忆阻器的阻变层正在被一些性能卓越的材料所替代。

3.目前,随着忆阻器尺寸的不断降低,其电热效应导致的不利影响日渐突出,这一效应会改变忆阻器功能层的材料结构和化学性质,导致其功耗增加,运行结果偏离设计预期。一些散热结构被提出,其具有较高的散热效率、较低的技术要求和制作成本等特点。金属导线本身具有良好的热导率,通过改变其在电路中的拓扑结构可以实现各种尺寸下电路的散热。目前这一技术已经在互补型金属氧化物场效应管(cmos)中得到应用。但是忆阻器散热的微观结构,由于其工艺关键尺寸和应用的局限性,目前这方面研究比较稀少。此外,如何设计合理的忆阻器网络散热结构,也需要一定探究,从而降低忆阻器的能耗,提升其工作效率。

技术实现要素:

4.为了解决背景技术中存在的问题,本发明提供了一种基于忆阻器阵列的可持续散热结构及制备方法,在硅基氮化镓衬底的忆阻器网络上,设计一种新型忆阻器网络的可持续散热结构及制备方法。

5.为实现上述目的,本发明采用的技术方案为:

6.一种基于忆阻器阵列的可持续散热结构,包括从上至下依次贴合设置的底电极、翻转基板、势垒层和衬底层,所述衬底层设有底电极导线散热通道和冷凝液流通通道。

7.进一步地,所述导线散热通道沿衬底层纵向深度大于横向深度,横纵比范围为1:10~1:20,所述底电极为铝、钼、铌、铜、金、钯、铂、钽、钌、氧化钌、银、氮化钽、氮化钛、钨或氮化钨中的一种。

8.进一步地,所述衬底层底部还设有冷却液管道,所述冷却液管道与导线散热通道垂直设置。

9.进一步地,所述势垒层为氮化镓势垒层。

10.进一步地,所述翻转基板选用钛、铝、镍或金中的一种制成。

11.进一步地,所述底电极导线形状呈相互交叉的鱼鳍状分布,所述鱼鳍状区域的导

线厚度不超过底电极厚度。

12.一种采用上述基于忆阻器阵列的可持续散热结构的方法,包括以下步骤

13.步骤s1、在纯净硅基衬底上通过气相沉积法沉积一层sio2等离子体作为刻蚀掩模版;

14.步骤s2、通过化学刻蚀方法,采用电感耦合等离子体蚀刻的方式,根据预设图案,在sio2刻蚀掩模版中打开若干交错的缝隙图案;

15.步骤s3、使用等离子体剥离残留光刻胶,沿纵向依次蚀刻sio2刻蚀掩模版和势垒层,直至到达纯净的硅基衬底层;

16.步骤s4、将芯片放置于温度为60℃,质量比为40%的koh溶液中浸泡5分钟,除去狭缝中残留的势垒层材料,用于进一步蚀刻硅狭缝;

17.步骤s5、使用各向同性的xef2气体蚀刻,进一步蚀刻硅狭缝,并扩大硅中的微通道;具体地,所述xef2气体蚀刻以脉冲方式进行:将待蚀刻样品在受控压力下暴露于xef2,然后抽空蚀刻室;重复该过程若干次,直到获得所需的通道宽度;所述通道即为导线散热通道;步骤s6、使用电子束蒸发沉积翻转基板,实现欧姆接触,并对翻转基板进行剥离光刻并退火;将入口和出口通道蚀刻至芯片的背面,直至从散热孔与底层冷凝液流通通道合并通道;

18.步骤s7、采用电子束蒸发方式,在翻转基板顶部沉积一层均匀的铬

‑

铜籽晶层;将芯片浸入h2so4溶液中去除表面氧化层;基于预设图样,定义待电镀区域并进行电镀;

19.步骤s8、剥离光刻胶,采用短铜湿蚀刻对底电极层进行选择性蚀刻;使用划片机将覆盖在底电极上的光刻胶去除,形成上述底电极图案,形成底电极,并在上方安装忆阻器。

20.与现有技术相比,本发明的有益效果如下:

21.在忆阻器crossbar结构底电极结构的设计上改变了电极和衬底的结构,同时在衬底中加入冷却液,加速热量的传递,具有较强的散热性能、控温性能,操作简单,成本低廉,利于大规模应用,提升了忆阻器crossbar结构的性能,扩展了其应用。

附图说明

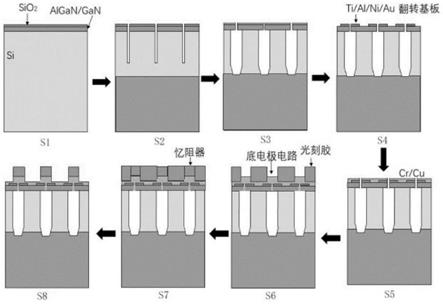

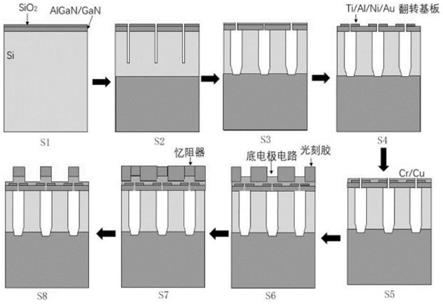

22.图1是本发明提供的基于忆阻器阵列的可持续散热结构制备流程图;

23.图2是本发明提供的基于忆阻器阵列的可持续散热结构俯视图。

具体实施方式

24.下面结合附图对本发明作更进一步的说明。

25.本发明提供的基于忆阻器阵列的可持续散热结构,包括从上至下依次贴合设置的底电极、翻转基板、势垒层和衬底层。其中衬底层设有导线散热通道,导线散热通道沿衬底层纵向深度大于横向深度,横纵比范围为1:10~1:20,本发明实施例优选为1:16。衬底层底部还设有冷却液管道,所述冷却液管道与导线散热通道垂直设置。势垒层优选氮化镓势垒层。翻转基板选用钛、铝、镍或金中的一种。底电极选用铝、钼、铌、铜、金、钯、铂、钽、钌、氧化钌、银、氮化钽、氮化钛、钨、氮化钨中的一种。

26.底电极导线形状呈相互交叉的鱼鳍状分布,如图2所示。其中鳍状区域的导线厚度不超过底电极厚度。

27.本发明提供的基于忆阻器阵列的可持续散热结构的制备方法如图1所示,具体包括:

28.步骤s1、在纯净的硅基衬底上通过气相沉积法沉积一层sio2等离子体作为刻蚀掩模版。

29.步骤s2、使用c4f8通过化学方法,采用电感耦合等离子体蚀刻的方式,根据预设图案,在sio2刻蚀掩模版中打开若干交错的缝隙图案。

30.步骤s3、使用o2等离子体剥离光刻胶,沿纵向依次蚀刻sio2刻蚀掩模版和势垒层,直至到达纯净硅基衬底层。这里蚀刻方法可以采用cl2 ar的化学方法。

31.步骤s4、将芯片放置于温度为60℃,40%浓度koh溶液中浸泡5分钟,除去狭缝中残留的势垒层材料,用于进一步蚀刻硅狭缝。

32.步骤s5、使用各向同性的xef2气体蚀刻,进一步蚀刻硅狭缝,并扩大硅中的微通道;具体地,所述xef2气体蚀刻以脉冲方式进行:将待蚀刻样品在受控压力下暴露于xef2,然后抽空蚀刻室;重复该过程若干次,直到获得所需的通道宽度;所述通道即为导线散热通道;

33.步骤s6、使用电子束蒸发沉积翻转基板实现欧姆接触堆叠,并对翻转基板进行剥离光刻并退火;将入口和出口通道蚀刻至芯片的背面,直至从散热孔与底层冷凝液流通通道两侧合并通道。

34.步骤s7、采用电子束蒸发方式,在翻转基板顶部沉积一层均匀的铬

‑

铜籽晶层。将芯片浸入h2so4溶液中去除表面氧化层;基于预设图样,定义待电镀区域并进行电镀。具体地,电镀方法采用cup阳极在含有cuso4,h2so4和cl

‑

的溶液中使用恒电流仪电镀。

35.步骤s8、剥离光致抗蚀剂,采用短铜湿蚀刻对底电极层进行选择性蚀刻;使用划片机将各个模具分开,形成底电极,并在上方安装忆阻器。

36.以上所述仅是本发明的优选实施方式,应当指出:对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。