1.本公开内容的多个实施方式一般涉及用于处理基板的方法和设备,且更具体地,涉及用于处理基板以形成低电阻触点的方法和设备。

背景技术:

2.对于高级逻辑(advanced logic)和存储装置中的主动触点(aggressive contact),存在有许多基本挑战。例如,为了获得最佳的逻辑和存储装置性能,需要将接触电阻保持在最小值。此外,由于正在开发具有非常小的临界尺寸(cd)和非常高的深宽比(har)的高级逻辑和存储装置,间隙填充挑战变得越来越难以克服。

3.因此,发明人提供了用于处理用于高级逻辑和存储装置的基板的方法和设备。

技术实现要素:

4.本文提供了用于处理基板的方法和设备。在一些实施方式中,例如,一种用于处理基板的方法包括以下步骤:在基板上的至少一个特征结构内选择性地沉积第一金属层;在第一金属层的顶上(atop)且至少在界定至少一个特征结构的侧壁上沉积第二金属层;在第二金属层的顶上并在特征结构内沉积第三金属层,以至少完全填充至少一个特征结构;和移除一些第二金属层或移除一些第二金属层和一些第三金属层,使得第二金属层和第三金属层的剩余部分与至少一个特征结构的顶表面齐平(flush)。

5.根据至少一些实施方式,一种用于处理基板的方法包括以下步骤:在基板上的至少一个特征结构内选择性地沉积第一金属层;在第一金属层的顶上且至少在界定至少一个特征结构的侧壁上沉积第二金属层;在第二金属层的顶上沉积第三金属层,以完成以下中的一个:部分填充、完全填充或过度填充至少一个特征结构;和移除一些侧壁、一些第三金属层和一些第二金属层,使得第二金属层和第三金属层的剩余部分彼此齐平,并且与侧壁的剩余部分齐平。

6.根据至少一些实施方式,一种非暂时性计算机可读储存介质,该非暂时性计算机可读储存介质上储存有指令,指令在由处理器运行时执行一种方法,方法包括以下步骤:在基板上的至少一个特征结构内选择性地沉积第一金属层;在第一金属层的顶上且至少在界定至少一个特征结构的侧壁上沉积第二金属层;在第二金属层的顶上沉积第三金属层,以完成以下中的一个:部分填充、完全填充或过度填充至少一个特征结构;和移除一些侧壁、一些第三金属层和一些第二金属层,使得第二金属层和第三金属层的剩余部分彼此齐平,并且与侧壁的剩余部分齐平。

7.下面描述了本公开内容的多个其他和进一步的实施方式。

附图说明

8.通过参考在附图中描绘的本公开内容的多个说明性实施方式,可理解上面简要概述并在下面更详细地讨论的本公开内容的多个实施方式。然而,附图仅显示了本公开内容

的多个典型实施方式,且因此不应视为对范围的限制,因为本公开内容可允许其他多个等效实施方式。

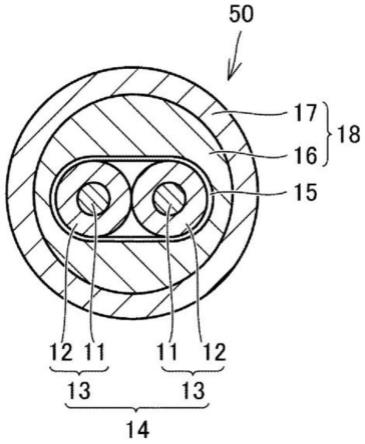

9.图1是包括根据本公开内容的至少一些实施方式的设备的系统的图。

10.图2是根据本公开内容的至少一些实施方式的用于处理基板的方法的流程图。

11.图3a-图3f是显示使用图2的方法而处理的基板的图。

12.图4a-图4e是显示使用类似于图2的方法而处理基板的图。

13.为促进理解,在可能的情况下使用了相同的附图标记来表示图中共有的相同组件。图未按比例绘制,且为清楚起见可简化。一个实施方式的元件和特征结构可有益地并入其他多个实施方式中,而无需进一步叙述。

具体实施方式

14.本文提供了用于处理基板的方法和设备的多个实施方式。例如,可将一种方法用于处理需要(或者可从中受益)较低接触电阻、较小的临界尺寸和/或较高的深宽比的基板,例如当将基板用于高级逻辑和/或存储装置中时。例如,可在基板上沉积一种或多种金属(如,钨(w)),以部分填充使用一种或多种电介质形成的一个或多个特征结构(如,过孔(via)、沟槽(trench)和/或双镶嵌过孔链(dual damascene via-chain))。随后,可在第一w层的顶上沉积另一金属(如,w)层,以形成衬里(liner),在衬里上可沉积另一w层,以部分填充、完全填充或过度填充一个或多个特征结构,从而获得用于高级逻辑和/或存储装置的较低接触电阻、更小的临界尺寸和更高的深宽比。

15.例如,在至少一些实施方式中,一种用于处理基板的方法可包括以下步骤:使用选择性化学气相沉积(cvd)/原子层沉积(ald)来部分填充(如,自下而上的间隙填充处理)在具有第一w层的基板上的一个或多个特征结构,从而有效地降低了特征结构的整体深宽比。接下来,可使用物理气相沉积(pvd)在第一w层的顶上形成w的衬里和/或阻挡层,w的衬里和/或阻挡层可用作特征结构的保护层,以防止用于后续处理的某些前驱物化学物质。例如,在使用pvd形成衬里w之后,使用诸如氟(氟有时会与形成特征结构的电介质反应(或侵蚀(attack)形成特征结构的电介质))之类的前驱物化学物质的cvd w处理可用以填充特征结构。

16.图1是系统的图,系统包括往往被称为群集工具的多腔室处理设备(设备100)和独立的化学机械抛光(cmp)处理腔室107,且系统构造为根据本公开内容的至少一些实施方式处理基板。例如,设备100包括安装到真空传送腔室的多个处理腔室。处理腔室可以是任何类型的处理腔室,包括(但不限于)pvd腔室、cvd处理腔室、ald处理腔室、蚀刻腔室或其他类型的处理腔室。

17.可构造为与设备100一起使用的pvd处理腔室的示例可以是可从加州圣塔克拉拉市的应用材料公司取得的系列的独立pvd设备。可构造为与设备100一起使用的cvd处理腔室的示例可以是可从应用材料公司取得的系列的独立cvd设备。类似地,可构造为与设备100一起使用的ald处理腔室的示例可以是可从应用材料公司取得的系列的ald设备。可构造为用作cmp处理腔室107的cmp处理腔室的示例可以是可从应用材料公司取得的

系列的独立设备的一种。

18.可将上述设备的一个或多个结合在整合工具或群集工具(如,可从加州圣塔克拉拉市的应用材料公司取得的系列的设备)上。在一些实施方式中,以下描述的发明性方法可有利地在群集工具中执行,使得在处理时存在有限的真空破坏或没有真空破坏。群集工具可构造为执行ald、cvd、pvd、预清洁、外延、蚀刻、光掩模制造、除气、等离子体掺杂、等离子体氮化和rtp,以及整合的多步骤处理,诸如高k晶体管栅极堆叠物制造。然而,本文描述的方法可使用耦合(couple)有合适的处理腔室的其他群集工具实施或在其他处理腔室中实施。

19.为了说明性目的,显示了设备100,包括体现在群集工具102中的多个处理腔室,群集工具102包括第一组处理腔室和第二组处理腔室,第一组处理腔室和第二组处理腔室可包括构造为执行包括以下所述的方法200的各种基板处理操作的处理腔室的任何结合。例如,在至少一些实施方式中,第一组处理腔室可包括构造为在基板上执行cvd的cvd处理腔室104a、构造为在基板上执行ald的ald处理腔室104b、构造为在基板上执行预清洁处理的预清洁处理腔室104c和/或构造为蚀刻基板的蚀刻腔室104d(下文中统称为处理腔室104)。在至少一些实施方式中,第二组处理腔室可包括(例如)构造为在基板上执行pvd的pvd处理腔室105a、构造为在基板上执行cvd的cvd处理腔室105b、构造为蚀刻基板的蚀刻处理腔室105c、构造为在基板上执行预清洁处理的预清洁处理腔室105d和构造为在基板上执行ald的ald处理腔室105e(以下统称为处理腔室105)。

20.若对于由群集工具102执行的特定处理不是必需的,则可从群集工具102移除任何处理腔室104、105。

21.群集工具102可包括两个装载锁定腔室106a、106b,用于将基板传送进群集工具102中和从群集工具102传送出基板。通常,由于群集工具102处于真空状态下,因此装载锁定腔室106a、106b可将引入到群集工具102中的基板“抽空(pump down)”。第一机械手108可在耦接至第一中央传送腔室110的装载锁定腔室106a、106b和处理腔室104之间传送基板,用于在基板上执行相应的处理。

22.第一机械手108还可向两个中间传送腔室112a、112b传送基板,或从两个中间传送腔室112a、112b传送基板。中间传送腔室112a、112b可用以维持超高真空条件,同时允许在群集工具102内传送基板。第二机械手114可在耦接到第二中央传送腔室116的中间传送腔室112a、112b和处理腔室105之间传送基板。

23.另外,控制器118(或处理器)被提供并耦合至群集工具102的各个部件,以控制处理腔室104、105用于处理基板的操作。控制器118包括中央处理单元(cpu)119、支持电路120和存储器或非暂时性计算机可读储存介质121。控制器118可操作地耦合到并控制一个或多个能量源(未显示),一个或多个能量源构造为用于直接地或经由与特定处理腔室和/或支撑系统部件关联(associate with)的计算机(或控制器)与处理腔室104、105一起使用。

24.控制器118可以是可在工业环境中用于控制各种腔室和子处理器的任何形式的通用计算机处理器。控制器118的存储器(或非暂时性计算机可读储存介质)121可以是可易于取得的存储器的一个或多个,诸如随机存取存储器(ram)、只读存储器(rom)、软盘、硬盘、光学储存介质(如光盘或数字视频光盘)、闪存驱动器或任何其他形式的本地或远程的数字储存器。支持电路120耦合到cpu 119,用于以常规方式支持cpu 119。支持电路120包括高速缓

冲存储器、电源、时钟电路、输入/输出电路和子系统和类似电路。如本文所述的发明性方法(诸如用于处理基板的方法(如,用于低电阻触点互连))可作为软件例程122储存在存储器121中,软件例程122可被运行或调用而以本文所述的方式控制一个或多个能量源的操作。软件例程也可由位于cpu 119控制的硬件远程的第二cpu(未显示)储存和/或运行。

25.图2是根据本公开内容的至少一些实施方式的用于处理基板的方法200的流程图,而图3a-图3f是根据本公开内容的至少一些实施方式的显示使用图2的方法而处理的基板的图。

26.为了说明性目的,描述了用于处理预制造的基板300的方法200。在至少一些实施方式中,可使用(例如)上述处理腔室(如,沉积处理腔室、蚀刻处理腔室、cmp处理腔室等,这些腔室可构造为用于多个图案化处理和/或一个或多个填充循环)的一个或多个来预制基板300。替代地,在至少一些实施方式中,可使用(例如)群集工具102来形成基板300300。

27.基板300可由用于形成基板的任何合适的材料形成,包括(但不限于)硅、锗等。例如,在至少一些实施方式中,基板300可由硅制成。基底层302可沉积在基板300的顶上,并且可由用于在基板300上形成导电基底层的任何合适的材料制成,包括(但不限于)铝(al)、铜(cu)、钴(co)、钼(mo)、钌(ru)、钛(ti)或钨(w)。例如,在至少一些实施方式中,基底层302a可由钨(w)和/或铜(cu)制成。

28.另外,可在基底层302和/或基板300的顶上沉积一个或多个附加层。例如,在至少一些实施方式中,可将具有一个或多个特征结构306的附加层304沉积在一些基板300和/或一些基底层302的顶上。在图中显示了一个特征结构306。特征结构306可以是过孔、沟槽和/或双镶嵌过孔链或类似特征结构,并且可具有一个或多个几何结构,包括(但不限于)矩形、三角形、圆形等。例如,在至少一些实施方式中,特征结构306可具有由顶表面312、底表面(如,一些基底层302)和四个侧壁(如,界定特征结构306的侧壁)所界定的大致矩形的结构。为了说明性目的,仅显示了特征结构306的第一侧壁308和第二侧壁310。层304可由用于形成特征结构306的一种或多种合适的介电材料制成,包括(但不限于)氧化硅(siox)、氮化硅(sin)或其他介电材料或膜。

29.继续参照图3a,在制造基板300之后,可将基板300传输到群集工具102的装载锁定腔室106a、106b之一,以使用群集工具102的处理腔室104、105的一个或多个进行进一步处理。将基板300传输到群集工具102期间,暴露于基板300的大气有时会导致氧化物(如,金属氧化物)形成在基底层302的表面(如,顶表面)上。为了说明性目的,在基底层302的顶表面的一部分的顶上显示了金属氧化物层314。因此,在至少一些实施方式中,在基底层302的顶上沉积另外的(additional)材料层之前,可执行一个或多个处理以移除金属氧化物层314。

30.例如,参照图3b,第一机械手108可在真空下将基板300从装载锁定腔室106a、106b的一个(如,装载锁定腔室106a)传送到预清洁处理腔室104c(如,第五处理腔室),而以任何合适的方式执行预清洁(如,蚀刻)处理以从基板300移除金属氧化物层314(以虚线显示)。替代地,在将基板300传送到群集工具102之前,可使用单独的或远程的处理腔室(如,预清洁或蚀刻处理腔室)从基底层302移除金属氧化物层314。

31.接下来,取决于进入的基板(如,具有har或低深宽比(lar)),在202处,任选地,可在基板上的特征结构内沉积第一材料层。例如,参照图3c,在至少一些实施方式中,对于具有相对har的基板而言,可使用(例如)cvd处理腔室104a(如,第一处理腔室)以任何合适的

方式将第一材料层318沉积在基板300的特征结构306内。在一些实施方式中,可使用ald处理腔室104b代替cvd处理腔室104a或与cvd处理腔室104a结合来沉积第一材料层318。替代地,对于具有相对lar的基板(诸如具有过孔、沟槽或类似结构的进入的基板)而言,可省略202。第一机械手108可在真空下将基板300从预清洁处理腔室104c传送到cvd处理腔室104a。第一材料层318可以是用于形成第一材料层的任何合适的金属,包括(但不限于)al、co、cu、mo、ru、ti和/或w。例如,在至少一些实施方式中,第一材料层318可以是w。

32.可沉积第一材料层318以部分填充特征结构306,特征结构306的高度可以是5nm至约500nm,且ar是约2至约20。例如,在至少一些实施方式中,诸如当特征结构306包括约470nm的高度、约550nm的宽度和至少约5.5的深宽比(诸如约5.5至约12)时,特征结构306可被第一材料层318填充达到约30nm至约600nm的高度。在至少一些实施方式中,第一材料层318可填充到特征结构306的高度的约三分之一(1/3)至约三分之二(2/3)的高度。用第一材料层318填充特征结构306的高度可取决于(例如)制造商的偏好、用于第一材料层318的材料的类型、基板300的预期用途(如,逻辑和/或存储器应用)等。

33.在至少一些实施方式中,cvd处理腔室104a可构造为执行选择性cvd w处理。更特别地,根据方法200,cvd处理腔室104a构造为在基底层302的顶上以任何合适的方式选择性地沉积(如,生长)w,同时沉积很少或不沉积(如,不生长)w在介电表面(如,包括第一侧壁308、第二侧壁310和/或顶表面312的层304)的顶上或介电表面上。也就是,在202处,在特征结构306内的基底层302的顶上的cvd w填充处理是自底向上的填充处理(如,低接触电阻),而不是使用常规填充处理来填充特征结构306时所需的高电阻阻障处理(high resistance barrier process)和成核处理。可与本文所述的方法和设备一起使用的合适的选择性cvd处理的示例公开于标题为“一种用于实现低接触电阻和无缝隙填充的表面清洁和选择性钨自下而上生长的综合方法(an integration approach of surface cleaning and selective tungsten bottom-up growth for low contact resistance and seam-free gapfill)”的共同拥有的美国专利申请案第16/803,842号、标题为“选择性沉积无腐蚀金属触点的方法(methods to selectively deposit corrosion-free metal contacts)”的美国专利公开号第2018/0145034号、标题为“选择性层沉积方法(methods of selective layer deposition)”的美国专利第9,716,012号、标题为“选择性钨过孔填充工艺集成方法(process integration approach of selective tungsten via fill)”的美国专利第10,256,144号及标题为“用于选择性沉积的选择性改进的原位预清洁(in-situ pre-clean for selectivity improvement for selective deposition)”的美国专利第10,395,916号。

34.接下来,在204处,在将第一材料层318沉积在基底层302的顶上以部分填充特征结构306之后,第一机械手108可在真空下将基板300从cvd处理腔室104a传送到上述处理腔室的一个或多个,使得第二材料层可沉积在第一材料层318的顶上。

35.参照图3d,可将包括基底层302的基板300从cvd处理腔室104a传送到pvd处理腔室105a(如,第二处理腔室),以在第一材料层318的顶上沉积第二材料层320。例如,在至少一些实施方式中,第一机械手108可在真空下将基板300从cvd处理腔室104a传送到中间传送腔室112a、112b的一个(如,中间传送腔室112a)。此后,第二机械手114可将基板300从中间传送腔室112a传送到pvd处理腔室105a。

36.第二材料层320沿着第一材料层318和/或基板300的层304的顶表面312形成衬里,如上所述,衬里可用作特征结构306的保护层306,针对用于后续处理的某些前驱物化学物质。第二材料层320可以是用于形成保护层的任何合适的金属,包括(但不限于)al、co、cu、mo、ru、ti和/或w。例如,在至少一些实施方式中,第二材料层320可以是w。

37.一旦传送后,pvd处理腔室105a可以任何合适的方式在第一材料层318的顶上并沿着界定基板300的特征结构306的第一侧壁308和第二侧壁310(和/或第三和第四侧壁)沉积第二材料层320(如,以沿着第一材料层318、第一侧壁308和第二侧壁310形成衬里)。另外,在至少一些实施方式(诸如所示的实施方式)中,第二材料层320可在第一材料层318的顶上并沿着第一侧壁308和第二侧壁310(和/或第三和第四侧壁),并且还在基板300的层304的顶表面312上沉积(如,以沿着第一材料层318、第一侧壁308、第二侧壁310和顶表面312形成衬里)。

38.用于pvd的高电离等离子体向特征结构306提供具有优越方向性的金属离子,从而提供进入特征结构306的增强的阶梯覆盖率(step coverage)。替代地,在至少一些实施方式中,可使用(例如)cvd处理腔室104a和/或ald处理腔室104b的一个或两个来沉积第二材料层320,但是由于高电阻率的膜在使用cvd/ald处理以在特征结构内形成衬里时会包含有时存在的杂质,因此这种相应处理通常无法获得与pvd一样低的电阻。

39.沿着第一侧壁308和第二侧壁310和/或基板300的顶表面312沉积在第一材料层318上的第二材料层320的量或厚度可取决于(例如)制造商的偏好、用于第二材料层320的材料的类型、基板300的预期用途(如,逻辑和/或存储器应用)等。

40.接下来,在206处,在将第二材料层320沉积在第一材料层318的顶上和/或在基板300的顶表面312上之后,可将基板300从pvd处理腔室105a传送至其他前述处理腔室的一个或多个,使得第三材料层可沉积在第二材料层320的顶上,(如)以至少部分地填充基板300的特征结构306。

41.例如,参照图3e,可将包括基底层302的基板300从pvd处理腔室105a传送回到cvd处理腔室104a或另一个cvd处理腔室(诸如cvd处理腔室105b(如,第三处理腔室)),而以任何合适的方式在第二材料层320的顶上沉积第三材料层322。在一些实施方式中,cvd处理腔室105b可以是与cvd处理腔室104a相同类型的处理腔室。替代地,cvd处理腔室105b可以是与cvd处理腔室104a不同类型的处理腔室。例如,cvd处理腔室105b可构造为使用wf6作为前驱物材料并且使用氢2(h2)作为还原剂,以便于在第二材料层320的顶上沉积第三层322,虽然cvd处理腔室104a可能无法以这种方式构造。为了说明的目的,第二机械手114在本文中被描述为在真空下将基板300从pvd处理腔室105a传送到cvd处理腔室105b。

42.沉积在第二材料层320的顶上的第三材料层322的数量或厚度可取决于(例如)制造商的偏好、用于第三材料层322的材料的类型、基板300的特征结构306是否将被部分填充、完全填充或过度填充、基板300的预期用途(如,逻辑和/或存储器应用)等。

43.例如,在至少一些实施方式中,诸如当沿着第一材料层318、第一侧壁308和第二侧壁310形成衬里时,可将第三材料层322沉积在第二材料层320的顶上,以完全填充特征结构306。当特征结构306被完全填充时,沉积在特征结构306(如,由第一侧壁308和第二侧壁310界定的区域)内的第二材料层320被第三材料层322完全覆盖,使得第三材料层322与层30e的顶表面312齐平(如虚线cf所示)。

44.在至少一些实施方式中,诸如当沿着第一材料层318、第一侧壁308、第二侧壁310和顶表面312形成衬里时,特征结构306可被过度填充。当特征结构306被过度填充时,包括第二材料层320的沉积在顶表面312的顶上的部分的所有第二材料层320被第三材料层322覆盖(如虚线of所示)。

45.替代地,在至少一些实施方式中,当特征结构306被部分填充时,第三材料层322可沉积在第二材料层320的顶上,以实质覆盖沉积在特征结构306内的第二材料层320(如,由第一侧壁308和第二侧壁310e界定的区域的实质部分,并且如虚线pf所示)。

46.不管特征结构306用第三材料层322填充了多少,第三材料层322应该沉积在特征结构306内,使得在层304的第一侧壁308和第二侧壁310之间不存在第三材料层322的间隙或空间。

47.第三材料层322可以是任何合适的材料,包括(但不限于)al、co、cu、mo、ru、ti和/或w。例如,在至少一些实施方式中,第三材料层322可以是w。

48.若在206处,特征结构306用第三材料层322完全填充(如,第三材料层322与层304的顶表面312齐平(或实质齐平)),则第二材料层320不存在于顶表面312上,可结束方法200。然而,在一些实施方式中,可执行cmp处理。例如,即使第三材料层322与层304的顶表面312齐平,某些第三材料层322也可能无意中沉积在顶表面312上。

49.因此,若在206处,特征结构306被部分填充、完全填充或过度填充,则在208处可移除至少一些侧壁、至少一些第三材料层和至少一些第二材料层,使得第二材料层320和第三材料层322的剩余部分彼此齐平,并且与侧壁的剩余部分(如,层304的顶表面312)齐平。

50.例如,参照图3f,在将第三材料层322沉积在基板300的第二材料层320的顶上之后,可将基板300传送到上述处理腔室的一个或多个,以用于进一步处理。例如,在至少一些实施方式中,第二机械手114可在真空下将基板300从cvd处理腔室105b传送到中间传送腔室112a、112b之一(如,中间传送腔室112a)。此后,第一机械手108可将基板300从中间传送腔室112传送到装载锁定腔室106a、106b之一(如,装载锁定腔室106a)。

51.接下来,可将基板300传送到独立的cmp处理腔室107(如,第四处理腔室),以移除一些第三材料层322、一些第二材料层320和/或一些层304(如,第一侧壁308、第二侧壁310和顶表面312的一些)。也就是,cmp处理腔室107可用以抛光基板300,以确保第二材料层320和第三材料层322相对于彼此齐平并且与基板300的层304齐平。

52.如上所述,在一些实施方式中,如,对于具有相对lar的基板(诸如具有过孔、沟槽或类似特征结构的进入基板)而言,可省略202。因此,除了省略202之外,如图4a-图4e所示,可与基板300相同地处理基板400。例如,除了在202处将第一材料层沉积在基底层402的顶上之外,可将第二材料层420直接沉积在基底层402上,且方法200可如上所述继续进行,例如参见图4d和图4e。

53.尽管前述内容针对本公开内容的多个实施方式,但是在不背离本公开内容的基本范围的情况下,可设计本公开内容的多个其他和进一步的实施方式。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。