vcsel装置的制造方法以及vcsel装置

技术领域

1.本发明涉及一种制造垂直腔表面发射激光器(vcsel)装置的方法。本发明进一步涉及一种vcsel装置。

背景技术:

2.vcsel是一种半导体激光二极管,其激光束发射垂直于顶表面或底表面。典型地,vcsel包括:与晶片表面平行的两个分布式布拉格反射镜;以及有源区,该有源区包括布置在这两个分布式布拉格反射镜之间的用于激光生成的一个或多个量子阱。dbr镜典型地包括具有交替的高折射率和低折射率的层。在普通的vcsel中,上镜和下镜被掺杂为p型材料和n型材料,从而形成二极管结。在其他常规构造中,p型区和n型区可以嵌入在dbr之间。整个vcsel层结构包括一种或多种半导体材料。当制造包括一个或多个vcsel(vcsel阵列)的vcsel装置时,vcsel层结构在晶片上外延生长。vcsel制造工艺的主要部分是晶片上的一个或多个单个vcsel的电隔离。这典型地通过刻蚀vcsel外延结构、分离p-n结并因此在晶片上产生特定拓扑结构来完成。根据vcsel装置的类型,半导体刻蚀可以在工艺序列的不同点处进行多次,从而产生包括vcsel层结构的晶片的顶表面的拓扑结构,其高度可达15μm。为了将载体注入vcsel,必须向p-n结的n型掺杂侧和p型掺杂侧应用电接触区域。这通常通过在包括vcsel层结构的晶片上的不同高度沉积导电材料来完成。为了在vcsel装置与电驱动器之间提供连接,需要应用外部电链路。这可以通过焊接直接完成,而接触区域需要具有一定的尺寸,以便将焊球充分黏着在接触区域上。然而,vcsel的尺寸往往比典型的焊球(50-60μm)更小(20-30μm)。此外,vcsel本身是机械不稳定的(例如,由于之前用于形成电流孔的氧化工艺),因此不可能在vcsel结构上直接焊接。为此,有必要预留一定的接合区域。在接合区域中,给出了用于接合工艺的机械稳定性。接合区域和电接触区域通过vcsel上的电链路连接。虽然这种布局支持不同的接合技术、例如焊接、碰撞等,但缺点是以这种方式制造的vcsel装置的尺寸是实际的vcsel的数倍大。这是因为金属走线需要克服装置的表面拓扑结构才能连接处于多个高度的接触区域。高级布线概念、例如仅连接vcsel阵列中的某些vcsel需要大量空间、额外的电隔离和金属层。在普通制造方法中,上述问题已经通过在vcsel芯片上预留用于焊接目的的空间(被称为接合区域)而得到解决。从接合区域到vcsel装置的不同高度的电连接是通过金属走线完成的。这些走线必须通过分级刻蚀断面或专门的沉积工艺来克服包括vcsel层结构的晶片上的高度。因此,最先进的vcsel装置需要1/4的占用空间用于vcsel本身,而需要3/4的占用空间用于接合区域、金属走线和支撑结构。

3.因此,需要改进的制造方法和改进的vcsel装置。

技术实现要素:

4.本发明的一个目的是提供一种制造方法,该方法能够制造具有减小的占用空间的vcsel装置。

5.本发明的另一目的是提供一种具有减小的占用空间的vcsel装置。

6.根据第一方面,提供了一种用于制造垂直腔表面发射激光器(vcsel)装置的方法,该方法包括:

7.提供第一结构,该第一结构包括晶片上的vcsel层结构,该vcsel层结构、包括该晶片在内均包含一种或多种半导体材料,该第一结构具有非平坦的第一结构顶表面,该非平坦的第一结构顶表面具有沿非平坦的顶表面变化的高度水平,其中,该非平坦的第一结构顶表面包括位于该晶片上方的不同高度水平处的一个或多个电接触区域;

8.在该非平坦的第一结构顶表面上沿着该非平坦的第一结构顶表面施加一层或多层与该一种或多种半导体材料不同的覆盖材料以获得第二结构,该覆盖材料的厚度使得覆盖材料顶表面的最低高度水平至少等于或高于该非平坦的第一结构顶表面的最高高度水平,该第二结构包括该第一结构和该一层或多层覆盖材料,该第二结构具有第二结构顶表面;

9.对该第二结构顶表面进行平坦化;

10.产生从该第二结构顶表面穿过该一层或多层覆盖材料的一个或多个第一电过孔,以用于电连接到该一个或多个电接触区域。

11.可以以与上述不同的顺序执行该方法。该方法可以包括在上述步骤之前、之间和之后的另外加工步骤。根据本发明的方法提出了制造vcsel装置的新构思,该新构思使得vcsel装置具有更小的占用空间。根据本发明的方法提供了对晶片和vcsel层结构的初始结构的非平坦的顶表面的平坦化。通过将一层或多层覆盖材料施加到初始(第一)结构的非平坦的顶表面上来执行平坦化。然后对该覆盖材料进行加工以提供平坦化的第二结构,该平坦化的第二结构包括初始的vcsel晶片结构和该一层或多层覆盖材料。因此,该第二结构具有平坦的顶表面。用于将该vcsel装置与驱动器进行外部连接的一个或多个电接合区域可以直接布置在平坦化的vcsel芯片的顶部上以与这些电过孔电接触,从而显著减小占用空间。

12.根据本发明的方法不仅适于具有单个台面或vcsel的vcsel装置,而且适于具有多个台面的vcsel阵列。本发明能够实现在一个芯片上的阵列中的单一可寻址vcsel。

13.此外,该平坦化允许通过直接外部连接到散热器来改善热传递。此外,按照根据本发明的方法制造的vcsel装置允许该vcsel装置与外部驱动器之间更短的电连接。更短的电连接减小了寄生电容。本发明的另一优点是该vcsel装置内、即在vcsel装置的顶表面之下的电链路的内部布线通过多次重复平坦化序列来实现,如本文将描述的。

14.另一优点是由于该覆盖材料而改善了vcsel装置的机械稳定性。

15.根据本发明的方法可以从晶片上的电功能vcsel装置开始。vcsel层结构包括一种或多种半导体材料,该一种或多种半导体材料优选地是ii-vi或iii-v化合物半导体材料。例如,该晶片可以是gaas晶片,并且该vcsel层结构可以包括gaas层、以及algaas层或ingaas层。可以将一种或多种覆盖材料选择为使得其适于被加工、优选地适于被抛光,尤其是使用浆料进行化学机械抛光。浆料可以包含该覆盖材料的小颗粒。

16.vcsel层结构可以在晶片上外延生长,然后被刻蚀以产生第一结构。该vcsel层结构可以包括分布式布拉格反射器、包括一个或多个量子阱的一个或多个有源区、一个或多个集成光电二极管层或光电晶体管层结构。一个或多个电接触区域设置用于对具有不同极性的vcsel层结构的层进行电接触、例如用于接触该vcsel层结构的p区和n区。

17.当覆盖材料层的施加和平坦化被重复一次或多次时,第二结构顶表面可以是最终vcsel装置的最上面的表面,或者可以是中间表面。

18.在下文中,将描述根据本发明的方法的有利实施例。

19.在实施例中,该平坦化包括抛光,尤其是对该第二结构顶表面进行化学机械抛光。

20.该方法还可以包括,在施加该一层或多层覆盖材料之前,施加加工停止层。可以将这种加工停止层施加在非平坦的第一结构顶表面上、优选地施加在vcsel层结构的高度水平最高的区域中。该加工停止层有利地避免了从vcsel层结构中不必要地去除材料。

21.该加工停止层优选地包括与待加工的覆盖材料不同的材料,使得在加工时、例如在用包含覆盖材料的小颗粒的浆料抛光该覆盖材料时,该浆料不会从该加工(抛光)停止层去除材料。

22.在加工覆盖材料期间,可以通过胶带、真空固定方式或通过将晶片布置在适当的载体衬底上来从背面固定该晶片,以防止对该晶片造成机械损坏。

23.在一个实施例中,平坦化可以包括:施加第一层覆盖材料,对第一覆盖材料顶表面进行加工以提供平坦的第一覆盖材料顶表面,以及在该平坦的第一覆盖材料顶表面上施加第二层覆盖材料以提供第二覆盖材料顶表面。

24.第二覆盖材料可以是电隔离的且导热的。该第二覆盖材料层可以提供vcsel芯片或晶片的电隔离、尤其是提供机械稳定性。第二层优选地是足够厚的、例如100-200nm,以提供足够的机械稳定性,但不应该太厚,以避免vcsel装置的高度过高。

25.在一些实施例中,这些层覆盖材料中的至少一层可以是电隔离的。这里的优点是该覆盖材料还可以提供对vcsel装置中具有不同极性的区域或区的电隔离,和/或提供vcsel阵列装置的台面之间的电隔离。

26.在其他实施例中,这些层覆盖材料中的至少一层可以是金属的,并且因此是导电的。通过加工、例如用合适的抛光剂对金属覆盖材料进行抛光,可以像电隔离覆盖材料的情况一样执行平坦化。使用金属作为覆盖材料的优点在于,从vcsel芯片的最终顶表面到位于较低高度水平的接触区域的至少部分通孔可以由金属层提供,从而可以简化加工。

27.应当理解的是,在非平坦的第一结构顶表面上施加一层或多层金属覆盖材料可以与施加一层或多层电隔离覆盖材料相结合。

28.此外,这些层覆盖材料中的至少一层可以是导热的。因此,散热和与散热器的连接可以简化并且更有效。

29.可以通过在该一层或多层覆盖材料中刻蚀一个或多个接触孔直到该一个或多个电接触区域、以及用导电材料、例如,金属填充该一个或多个接触孔直到该第二结构顶表面来产生这些第一电过孔。

30.可以通过刻蚀第二结构、例如通过等离子体辅助干法刻蚀(rie/icp)来执行产生这些接触孔,从而在这些接触孔的底部上暴露一个或多个电接触区域。因此,刻蚀化学品不会侵蚀底部接触区域,从而产生自终止封边工艺。清洁步骤可以用于清洁接触孔开口、例如使用利用hcl或h2so4的湿化学清洁,或使用利用o2/ar/nh3的等离子体清洁。

31.用导电材料填充接触孔可以以电镀方式执行。为此,可以施加用作电镀种子层的金属膜,以便为电镀接触孔填充提供导电性。在以电镀方式填充这些接触孔之前,可以用保护涂层填充这些接触孔、例如通过原子层沉积或溅射,以在接触孔的壁上产生厚度为几nm

的层。由于该层可以吸收由该电镀接触孔填充产生的残余应力,因此该层可能是有利的。此外,其可以提供粘附力并抑制材料从可选的后续施加的另外的材料扩散到第二结构。

32.根据本发明的方法具有允许在该vcsel芯片内部和顶部形成电链路或电布线的其他优点。具体地,可以通过重复平坦化序列两次或更多次来执行电链路的复杂内部布线。这允许例如在vcsel装置中集成光子部件(如光电二极管或光电晶体管)、将vcsel装置的多个台面中的一部分或全部彼此电连接、和/或为隧道二极管、耦合有源区、腔内部件等提供多级连接。

33.在实施例中,根据本发明的方法还可以包括,在产生该一个或多个第一电过孔之后,在该第二结构上施加至少一个另一层的覆盖材料以提供第三结构,该第三结构包括该第二结构和另外的覆盖材料,该第三结构具有第三结构顶表面。在该实施例中,第二结构顶表面是vcsel装置的中间表面。

34.该方法还可以包括产生穿过平坦的第三结构顶表面直到第一电过孔的至少一部分的另外的电过孔,这些第一电过孔的至少一部分用于将该一个或多个另外的电过孔与这些第一电过孔中的至少一部分电连接。

35.在前述实施例的情况下,该方法还可以包括,在施加另外的覆盖材料之前,将平坦的第一结构顶表面上的第一电接触部的至少一部分彼此电连接。因此,实现了在例如布置在vcsel芯片上的多个台面之间的内部电布线。

36.前述加工步骤可以重复若干次,以产生内部电连接、例如在多个台面之间的内部电连接,或产生集成到晶片之上多个高度水平中的vcsel芯片中的光子部件之间的内部电连接。因此,前述实施例对于生产具有大量vcsel或台面的vcsel阵列是尤其有利的。本发明允许在vcsel阵列中进行内部连接、例如将台面彼此连接,而与驱动器的外部链路则直接在vcsel芯片之上执行,因此产生了仅需要少量的接触部或接合区域的密集封装的vcsel阵列。

37.根据第二方面,提供了一种垂直腔表面发射激光器(vcsel)装置,该装置包括:

38.第一结构,该第一结构包括晶片上的vcsel层结构,该vcsel层结构、包括该晶片在内均包含一种或多种半导体材料,该第一结构具有非平坦的第一结构顶表面,该非平坦的第一结构顶表面具有沿非平坦的顶表面变化的高度水平,其中,该非平坦的第一结构顶表面包括位于不同高度水平处的一个或多个电接触区域;

39.沿该非平坦的第一结构顶表面布置在该非平坦的第一结构顶表面上的一层或多层与该一种或多种半导体材料不同的覆盖材料,其中,该vcsel装置的最上面的顶表面是平坦的,

40.一个或多个第一电过孔,该一个或多个第一电过孔从该最上面的顶表面穿过该一层或多层覆盖材料,以与该一个或多个接触区域电连接。

41.根据本发明的vcsel装置具有与根据第一方面的方法相同或相似的实施例和优点,尤其是在从属权利要求中指出的那些实施例和优点。

42.具体地,根据本发明的vcsel装置与传统的vcsel装置相比具有显著减小的占用空间、例如减小为1/2或更小。根据本发明的vcsel装置可以包括单个台面或多个台面,以提供密集封装的vcsel阵列。其他构造、如光电二极管/光电晶体管结构的集成、以及具有多波长发射的vcsel装置也是可能的。

43.一层或多层覆盖材料可以包括一个或多个电隔离层和/或一个或多个导电层。

44.vcsel装置可以包括一个或多个内部电链路,该一个或多个内部电链路在低于该最上面的顶表面且高于该晶片的高度水平处电连接这些通孔中的一个或多个通孔。

45.vcsel装置可以包括在该最上面的顶表面上的与该一个或多个电过孔电连接的一个或多个接合区域。

46.vcsel装置可以是底面发射器或顶面发射器。vcsel装置可以被由如上所述的一层或多层覆盖材料形成的电隔离且导热材料完全包围。

47.通过下文参考附图对示例性实施例的描述,进一步的特征和优点将变得显而易见。

附图说明

48.在附图中:

49.图1a至图1g示意性地示出了制造vcsel装置的方法的实施例的工艺序列的侧视图,其中,图1g以侧视图示出了所制造的vcsel装置;

50.图2a至图2c示意性地示出了制造vcsel装置的方法的另一实施例的工艺序列的侧视图,其中,图2c以侧视图示出了所制造的vcsel装置;

51.图3a至图3d示意性地示出了制造vcsel装置的方法的另一实施例的工艺序列的侧视图,其中,图3d以侧视图示出了所制造的vcsel装置;

52.图4a至图4j示意性地示出了制造vcsel装置的方法的另一实施例的工艺序列的侧视图,其中,图4j以侧视图示出了所制造的vcsel装置;

53.图5a至图5d示意性地示出了制造vcsel装置的方法的另一实施例的工艺序列,其中,图5a至图5c示出了侧视图,而图5d以俯视图示出了所制造的vcsel装置;

54.图6a至图6h示意性地示出了制造vcsel装置的方法的另一实施例的工艺序列,其中,图6a至图6g示出了侧视图,而图6h以俯视图示出了所制造的vcsel装置;

55.图7示出了根据本公开的原理制造的vcsel装置的另一实施例的侧视图;

56.图8a至图8b示出了根据本公开的原理制造的vcsel装置的另一实施例;其中,图8a是侧视图,而图8b是俯视图;

57.图9示出了根据本公开的原理制造的vcsel装置的另一实施例的侧视图;以及

58.图10示出了根据本公开的原理制造的vcsel装置的另一实施例的侧视图。

具体实施方式

59.在下文中,将描述vcsel装置的若干实施例和制造vcsel装置的方法的实施例。

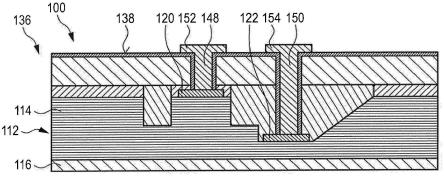

60.将参考图1a至图1g描述制造vcsel装置100的方法的第一实施例。图1g示出了根据该方法制造的vcsel装置100。

61.根据图1a,提供了第一结构112。第一结构112包括晶片116上的vcsel层结构114。vcsel层结构114、包括晶片116在内均包含一种或多种半导体材料。作为示例,晶片116可以是gaas晶片,并且vcsel层结构114可以包括gaas层和algaas层。选自ii-vi或iii-v化合物半导体组的其他半导体材料可设想作为用于第一结构112的材料。

62.根据已知技术,vcsel层结构114可以在晶片116上外延生长。如本领域已知的,

vcsel层结构114可以包括分布式布拉格反射器和包括一个或多个量子阱的一个或多个有源区。如图1a所示,vcsel层结构114可以设置为电功能vcsel结构、即如果该vcsel层结构与驱动器连接,则其准备好进行激光发射。在制造类似vcsel装置100的vcsel装置的工艺中,vcsel层结构114被刻蚀在外延层结构中,以分离vcsel层结构114的p-n结,由此产生第一结构的特定拓扑结构。因此,第一结构112具有非平坦的第一结构顶表面118,该第一结构顶表面具有沿非平坦的顶表面118变化的高度水平。第一结构112设置有一个或多个电接触区域120、122。接触区域120、122可以设置为具有不同极性的接触区域。例如,接触区域120可以是p接触区域,而接触区域122可以是n接触区域。该一个或多个电接触区域120、122设置用于电接触具有不同极性的vcsel层结构114的区、例如用于接触vcsel层结构114的p区和n区。

63.第一结构112的表面118的非平坦拓扑结构以及因此接触区域120、122在晶片116之上不同高度水平上的布置使得难以应用外部电链路来与电驱动器(未示出)连接。特别地,由于焊球的尺寸典型地为50-60μm,而vcsel的尺寸往往更小、例如20-30μm,因此在图1a所示的第一结构112的状态下,在接触区域120、122上施加焊球将需要很大的空间。这意味着将外部链路应用到第一结构112上将需要vcsel装置尺寸的3/4作为接合区域的占用空间,而vcsel本身将只占占用空间的1/4。

64.后文描述的制造方法解决了这个问题。

65.在前端工艺序列中达到第一结构的最终拓扑结构之后,第一结构112可以覆盖有一层覆盖材料124,该覆盖材料优选地是机械稳定的且电隔离的。如图1a所示,材料124沿非平坦的第一结构顶表面118的一部分施加。如图1a中可见,材料124被施加在非平坦的第一结构顶表面118上、被施加在顶表面118具有最高高度水平的区域中。材料124的顶表面126限定了非平坦的顶表面118的最高水平。当顶表面118在下面将描述的后续工艺步骤中被加工、尤其是被抛光时,材料124用作停止层。材料124可以是氮化物基的、例如aln或sin。

66.接下来,根据图1b,在包括材料124的顶表面126在内的非平坦的第一结构顶表面118上沿非平坦的第一结构顶表面118、126施加与vcsel层结构114和晶片116的一种或多种半导体材料不同的一层覆盖材料128。如图1b所示,覆盖材料128的施加厚度使得覆盖材料顶表面132的最低高度水平130至少等于或高于非平坦的第一结构顶表面118、126的最高水平134。

67.在本实施例中,覆盖材料128是电隔离的。覆盖材料128可以是氧化物基材料、例如al2o3或sio2。覆盖材料128可以通过共形溅射或化学气相沉积(cvd)来施加,从而在下面的vcsel层结构114中实施最小的应力。

68.下一个步骤是图1c所示的平坦化步骤。通过对覆盖材料顶表面132进行加工来执行平坦化,由此提供包括第一结构112和覆盖材料128的第二结构136。可以通过使用浆料的化学机械抛光来执行对覆盖材料顶表面132的加工。浆料可以包含覆盖材料128的小颗粒。如上所述,材料124用作抛光停止层,从而避免了vcsel层结构114的材料的不必要去除。第二结构136包括平坦的第二结构顶表面138。换言之,与第一结构112的非平坦拓扑结构相比,第二结构136具有平坦化的拓扑结构。

69.在本实施例中,将另一层的覆盖材料140施加到平坦的第二结构顶表面138上。覆盖材料140可以是电隔离材料。覆盖材料140的厚度应该是足够的、例如100-200nm,以提供

机械稳定性,但它不应该太厚以免在晶片116之上产生高拓扑结构。覆盖材料140可以是氮化物基的,并且例如可以包括aln或sin。在施加覆盖材料140之后,现在由覆盖材料140的顶表面形成平坦的第二结构顶表面138,该顶表面再次用附图标记138标记,如图1d所示。

70.在图1d的工艺状态中,将接触区域120、122掩埋或嵌入在第二结构136中。将在根据图1e的下一步骤中产生到接触区域120、122的电过孔。在该工艺中,通过刻蚀、例如通过等离子体辅助干法刻蚀(rie/icp)产生接触孔142、144,由此在接触孔142、144的底部处暴露接触区域120和122。优选地使用不会侵蚀接触区域120、122的刻蚀化学品,并且因此刻蚀工艺是自终止的。此后可以通过例如湿化学hcl或h2so4清洁,或通过利用o2/ar/nh3的等离子体清洁来对接触孔142、144进行清洁。

71.接下来,根据图1f,将一层保护材料146作为涂层施加到第二结构顶表面138上,该顶表面然后由保护涂层146的顶表面形成。保护涂层146还覆盖接触孔142、144的壁。保护涂层可以是基于氮化物的,并且例如可以包括aln或sin。保护涂层146的沉积应该是共形的,从而产生具有5-10nm厚度的层。材料沉积可以通过原子层沉积(ald)或溅射来执行。保护涂层146可以吸收由后续步骤产生的残余应力,提供粘附力并抑制在后续步骤中沉积的材料的扩散。

72.接下来,可以施加金属膜(未示出)作为电镀种子层,以便为用导电材料以电镀方式填充接触孔142、144提供导电性。然后,在电镀工艺中用导电材料填充接触孔142、144。通过用导电材料填充接触孔142、144,产生穿过平坦的第二结构顶表面138直到电接触区域120、122的通孔148、150。

73.如图1g所示,可以在平坦的第二结构顶表面138上提供接合区域152、154。在本实施例中,第二结构顶表面138形成vcsel装置100的最上面的顶表面。接合区域152、154可以设置有焊球(未示出),以用于将电链路连接到外部驱动器(未示出)。因此,制造了vcsel装置10,其中,vcsel装置10被电隔离且导热的材料128、140、146完全包围。具体地,用于将vcsel装置10接合到例如外部驱动器的接合区域152、154直接位于vcsel装置或芯片100之上,因此与现有技术的vcsel装置相比,接合区域的占用空间减小为1/2或更小。

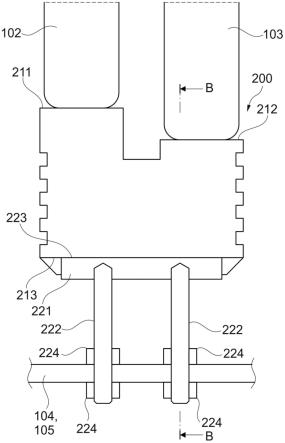

74.图2a至图2c示出了制造图2c所示的vcsel装置200的方法的另一实施例。图2a至图2c的实施例是前述实施例的修改。vcsel装置200包括第一结构212,该第一结构包括晶片216上的vcsel层结构214。层结构214包括两个台面202、204,每个台面形成vcsel。

75.图2a示出了制造vcsel装置200的方法的状态,该状态对应于上述方法的图1c中的状态,即,为了简化,这里省略了图1a和图1b中的工艺序列。因此,图2a示出了vcsel结构(第二结构)236,该结构之前已经如上所述被平坦化,使得它具有平坦的第二结构顶表面238。在此未示出加工(抛光)停止层,但可以如上所述提供该加工停止层。

76.在本实施例中,第一结构212包括电接触区域220a、220b、220c和220d。从图2a中的vcsel结构236的状态开始,通过刻蚀,在区256a和256b中去除电隔离的一层覆盖材料228的一部分,从而暴露vcsel结构236的旨在用于进一步加工的区域,而覆盖材料还电隔离和包封台面202、204。然后用导电材料填充或部分地填充区256a、256b直到平坦的第二结构顶表面238的高度水平,以提供通孔252b和252d。平坦的第二结构顶表面238形成vcsel装置200的最上面的顶表面。然后可以将接合区域252a和252c布置在接触区域220a、220c上,并且通孔252b和252d的上表面可以用作接合区域。因此,所有接合区域都以密集封装的方式布置

在vcsel装置200的顶部。

77.图3a至图3d示出了制造vcsel装置300的方法的另一实施例,作为先前实施例的修改。与先前实施例类似,vcsel装置300包括两个台面302、304。第一结构312包括晶片316上的vcsel层结构314。第一结构包括接触区域320a、320b、320c、320d。在根据图3a至图3d的实施例中,vcsel结构的平坦化被示出为具有一层金属覆盖材料,如将在下面描述的。

78.参考在该方法的工艺状态下的图3a开始描述,该工艺状态为图2b所示的工艺状态。即,具有一层覆盖材料328的第二结构336在之前已经被平坦化,并且然后在区356a和356b中被刻蚀,如上所述。

79.根据图3b,vcsel结构(第二结构)336覆盖有另一层覆盖材料340,该另一层覆盖材料的厚度使得覆盖材料顶表面332的最低高度水平330至少等于或高于图3a中所示的第二结构336的非平坦的顶表面的最高水平。第二结构336和覆盖材料340形成第三结构337。这里覆盖材料340是金属材料、例如au。接下来,对第三结构的顶表面332进行加工、尤其是进行抛光、例如使用利用浆料的化学机械抛光。浆料可以包括适于对金属覆盖材料340进行抛光的抛光液内的颗粒。如图3c所示,金属抛光在台面302、304的表面处停止,从而在区356a、356b中的较低高度区域与vcsel台面302、304的顶部之间通过电隔离材料328来产生固有的电隔离。然后可以在平坦vcsel装置最上面的顶表面335上施加图3d中所示的最终外部金属化区域或接合区域350a、350b、350c、350d,而用金属材料340来填充区356a、356b中的接触区域320b、320d。

80.参考图4a至图4j,将描述制造图4j所示的vcsel装置400的方法的另一实施例。

81.根据图4a,提供了包括晶片416上的vcsel层结构414的第一结构412。包括晶片416的vcsel层结构414包含一种或多种半导体材料。vcsel层结构414可以包括分布式布拉格反射器和具有一个或多个量子阱的有源区。vcsel层结构414可以具有p区和n区。第一结构412具有非平坦的第一结构顶表面418,该第一结构顶表面具有沿非平坦的顶表面418变化的高度水平。非平坦的第一结构顶表面418包括布置在第一结构顶表面418上不同高度水平的电接触区域420、422。根据图4a,加工停止层424被施加到第一结构顶表面418上具有最高高度水平的区中,如图4a所示。在这种情况下,加工停止层424的顶表面426形成第一结构412的顶表面。

82.如图4b所示,在非平坦的第一结构顶表面418、426上施加与第一结构412的半导体材料不同的一层覆盖材料428,该覆盖材料的厚度使得覆盖材料顶表面432的最低高度水平430至少等于或高于顶表面418、426的最高高度水平434。

83.如图4c所示,通过对覆盖材料顶表面432进行加工来对包括第一结构412和覆盖材料428的第二结构436进行平坦化,以提供具有平坦的第二结构顶表面438的第二结构436。对覆盖材料顶表面438的加工通过抛光来执行、尤其是对覆盖材料顶表面438进行化学机械抛光,如上所述。根据图4d,将一层覆盖材料440施加到平坦化的第二结构436上。关于层424、覆盖材料428和覆盖材料440的材料,参考对图1a至图1g中的实施例的描述。

84.根据图4e,直接在接触区域420、422上方产生接触孔442、444。如上所述,将保护涂层446施加到平坦的第二结构顶表面438上。然后通过用导电材料填充接触孔442、444来产生通孔448、450。在本实施例中,导电材料例如是以电镀方式填充到接触孔442、444中的au。

85.至此,图4a至图4f中所示的工艺序列可以与图1a至图1g的工艺序列相同,并且只

要没有另外指出,根据图1a至图1g的方法的描述也适用于图4a至图4f所示的方法步骤。

86.图4g至图4j示出了可以从图4f开始执行的另外的工艺序列。

87.根据图4g,通过用合适的浆料对形成通孔448、450的导电材料进行化学机械抛光来再次对第二结构顶表面438进行平坦化。抛光不会侵蚀保护涂层446。

88.接下来,如图4h所示,将具有扩散停止功能的材料451沉积在通孔448、450上。材料451可以是导电陶瓷材料,其中,tin可以有利地用作材料451。此外,如图4h所示,第二结构覆盖有电隔离材料453以提供现在具有平坦的顶表面438的第三结构437。vcsel层结构现在被包封。

89.在图4i中,在覆盖材料453中刻蚀接触孔455、457,使得包括扩散停止部451的通孔448、450被暴露。图4j示出了用导电材料、例如,铜填充接触孔455、457,以提供与通孔448、450电连接并因此与接触区域420、422电连接的通孔459、461。通孔459、461可以用作具有足够面积以将焊球施加到通孔459、461上的接合区域,以便提供到驱动器(未示出)的外部连接。同样,vcsel装置400的最上面的顶表面438是平坦的。

90.vcsel装置400是单台面vcsel装置。vcsel装置400是底面发射器,即,由vcsel生成的激光辐射是通过衬底或晶片16发射的。

91.参考图5a至图5d,将描述制造vcsel装置500的方法的实施例,该实施例示例性地示出了通过多次重复平坦化序列,可以实现处于不同高度水平或高度的多个vcsel或多个台面的电连接。在每个平坦化和金属化序列中,台面(vcsel)的另一部分可以连接在一起,而到驱动器的外部连接则在更高的高度完成。

92.图5c中所示的vcsel装置500包括例如三个台面或vcsel 570、572、574,它们各自都能够发射激光辐射。

93.图5a示出了制造vcsel装置500的方法的加工状态,其中,第一结构512已经被电隔离覆盖材料528覆盖(覆盖材料下方的停止层可能之前已经被施加(未示出),类似于在图1a至图1g中的第一实施例中)并且被平坦化以提供具有平坦的第二结构顶表面538的第二结构536,该第一结构包括晶片516上的vcsel层结构514并且具有带电接触区域520a至520e的非平坦的顶表面518。图5a中的方法的加工状态对应于例如图4c中所示的方法的加工状态。

94.如图5b所示,该方法继续施加另一层覆盖材料540、进行接触孔刻蚀并用导电材料填充接触孔,以提供穿过第二结构顶表面538直到接触区域520a至520e且直接在接触区域520a至520e正上方的通孔548a至548e。图5b中所示的方法的状态类似于图4f中所示的方法的状态。

95.接下来,如图5c所示,将另一层覆盖材料553施加到图5b所示的结构上,以提供具有第三结构顶表面532的第三结构537,该第三结构顶表面形成所制造的vcsel装置500的最上面的顶表面,并且重复接触孔刻蚀以及用导电材料填充接触孔。在第三结构顶表面532的顶部,产生接合区域或接合焊盘580、582、584。接合焊盘580与电接触区域520a、520c和520d电连接并将这些电接触区域并联电连接,而接触焊盘582与电接触区域520b电连接,并且接合焊盘584与接触区域520e电连接(也参见图5d)。该示例性实施例表明,根据本公开的原理的方法允许制造密集封装的vcsel阵列,并且接合区域的占用空间大大减小。

96.根据本文描述的原理的方法还允许在更深的高度的多个台面或vcsel之间进行电连接,即,在vcsel装置内进行内部连接。这将在下文中首先参考图6a至图6h进行描述。

97.图6g示出了vcsel装置600。vcsel装置600包括第一结构612,该第一结构包括晶片616上的vcsel层结构614,该vcsel层结构包括两个台面670、672。第一结构612包括电接触区域620a至620d。在vcsel装置600内,内部电链路669将布置在vcsel装置600中低高度处的电接触区域620b、620d并联电连接。在下文中,将参考图6a至图6f描述制造vcsel装置600的方法的实施例。

98.该描述从与上述图2a中的加工状态相对应的方法的加工状态开始。即,之前已经形成平坦化的第二结构636,该第二结构包括第一结构612,该第一结构包括晶片616上的vcsel层结构614。将接触区域620a至620c布置在第一结构612上。第一结构612具有非平坦的第一结构顶表面618,而第二结构636已经通过对施加到第一结构612上的覆盖材料628进行加工、尤其是通过化学机械抛光而被平坦化。覆盖材料628是电隔离的。

99.如图6b所示,对第二结构636进行刻蚀,使得更深的电接触区域620b和620d被暴露,而剩余覆盖材料628的一部分将vcsel层结构614的台面670、672电隔离。

100.如图6c所示,第二结构636覆盖有另一层覆盖材料640,该覆盖材料是电隔离材料。

101.如图6d所示,对第二结构636进行刻蚀,以再次暴露电接触区域620b和620d,而台面670、672也通过覆盖材料640与接触区域620b和620d电隔离。如图6e所示,第二结构636覆盖有金属材料或金属化物641,该金属材料或金属化物通过形成到电接触区域620b和620d的电过孔648、650而将电接触区域620b与电接触区域620d电连接。

102.如图6f所示,将另一层覆盖材料643施加在金属化物641的顶部,以产生第三结构637,该第三结构包括第二结构636和第一结构612,如图6f所示。另一覆盖材料643是电隔离材料,并且可以是类似于上面参考图1a至图1g描述的电隔离覆盖材料的材料。

103.第三结构637具有第三结构顶表面639,该第三结构顶表面是平坦的并且形成所制造的vcsel装置600的最上面的顶表面,其中,顶表面639可以已经通过化学机械抛光被平坦化。

104.接下来,如图6g所示,对第三结构637进行刻蚀,以提供接触孔642,然后用导电材料填充该接触孔,该导电材料可以与用于金属化物641的材料相同。金属化物641可以是au。

105.最后,将接合区域或接合焊盘680布置在通孔651上。

106.图6h示出了vcsel装置600的俯视图,该俯视图展示了接合区域680以及另外两个接合区域682、684,其中,接合区域682被布置用于与电接触区域620a电连接,而接合区域684被布置用于与电接触区域620c电连接。

107.因此,已经示出,可以用根据本公开的原理的方法来制作如链路669的内部电链路。

108.图7示出了根据本披露内容的原理制造的平坦化的vcsel装置700的实施例。vcsel装置700是在平坦化的vcsel装置700中集成光子部件(如光电二极管)的示例。

109.vcsel装置700包括第一结构712,该第一结构包括晶片716和形成在该晶片上的vcsel层结构714。第一结构712还包括光电二极管层结构715。第一结构712具有与上述实施例中一样为非平坦的第一结构顶表面718。第一结构顶表面718也部分地由光电二极管层结构715的表面形成。第一结构712还包括被布置在晶片716上方的不同高度水平的电接触区域720、721、722。vcsel装置700由如上所述制成的一层电隔离覆盖材料728包封。一层覆盖材料728与第一结构712一起形成第二结构736,该第二结构具有平坦化的第二结构顶表面

738,该第二结构顶表面形成vcsel装置700的最上面的顶表面。第二结构736已经如上所述那样制造。图7还示出了在施加一层覆盖材料728之前施加的加工(抛光)停止层724。如上所述,已经产生了保护涂层746以及电过孔748、749、750。图7中还示出了在各个通孔748、749、750的顶表面上的扩散停止部751。

110.接合区域759布置在第二结构顶表面738上,以与通孔748、749、750电连接。焊球780布置在接合区域759上以用于连接到外部驱动器(未示出)。

111.vcsel装置700是底面发射器,即,如箭头785所示,激光是由vcsel层结构714的有源区通过光电二极管层结构715发射的。光栅790或其他光学结构可以布置在vcsel装置700的发光侧。

112.图7示出了根据本披露内容的原理制造vcsel装置的方法也适于在vcsel装置700中集成光子部件、如光电二极管或光电晶体管,因为到外部装置的所有电连接都可以以节省空间的方式在vcsel装置700的平坦化表面(表面738)上制成。

113.虽然图7中的vcsel 700是单台面vcsel装置,但图8a和图8b示出了多台面vcsel装置800,其中,每个台面可以配备有集成光电二极管。在该示例中,vcsel 800包括第一结构812,该第一结构包括晶片816上的vcsel层结构814、并且包括光电二极管层结构815。第一结构812已经被刻蚀以获得四个台面801、802、803、804和对应数量的光电二极管805、806、807、808。包括对应光电二极管805、806、807、808的台面801、802、803、804中的每一个台面类似于图7中的vcsel装置700。然而,与vcsel装置700不同,vcsel装置800包括内部电链路831。通过根据本公开的原理的制造vcsel装置800的方法,这种内部电链路有利地是可能的。这种内部电链路可以通过重复平坦化序列来产生,该平坦化序列包括施加多层覆盖材料并且将它们平坦化若干次、例如参考上面的图6a至图6h所描述的。在第一平坦化步骤之后,产生直到台面801至804的层结构814上的电接触区域的第一电过孔848a至848d,并且通过施加导电材料、例如金属将这些第一电过孔彼此电连接,以产生电链路831。然后,在下一个平坦化工艺之后,在第三结构837中产生另外的电过孔870a至870e,该下一个平坦化工艺包括用另一层覆盖材料覆盖第二结构836以提供第三结构837并且对第三结构837进行平坦化以提供装置800的平坦的最上面的顶表面。如图8a所示,这些另外的通孔之一870a向下延伸到电链路831,而通孔870a到通孔848a、848b、848c、848d的电连接由电链路831完成。已经产生另外的电过孔870b至870e,这些电过孔从第三结构顶表面839向下延伸到布置在光电二极管805至808上的电接触部。另外的电过孔870f从第三结构顶表面839向下延伸到晶片816。因此,制造如vcsel装置800的vcsel装置的方法能够实现密集封装的多台面vcsel装置,从而避免或至少减少激光发射中的暗点。此外,如图8a所示,根据本发明的方法允许在vcsel装置内提供内部电链路、如内部电链路831。

114.如图8b中的vcsel装置800的俯视图所示,将包括焊球880a至880f的接合区域都布置在vcsel装置800的顶表面上,而不需要太多空间,从而减少了vcsel装置800的占用空间、尤其是电连接的占用空间。

115.图9示出了根据本公开的原理制造的级联vcsel装置900的实施例,其中,多个台面或vcsel彼此串联电连接。vcsel装置900包括第一结构912,该第一结构包括vcsel层结构914,该vcsel层结构具有第一极化类型、例如p型的区917,以及具有第二极化类型、例如n型区919的另一个区。vcsel装置900包括第二结构936,该第二结构由第一结构912通过如上所

述的平坦化工艺形成。第一结构912还包括晶片916。

116.vcsel装置9还包括第三结构,该第三结构包括另一层覆盖材料953。

117.在该示例中,vcsel装置900包括四个台面901至904。每个台面具有与上述图4j中所示的vcsel结构相当的结构。在覆盖材料层953中产生通孔959a至959e。通孔959b、959c和959d将相邻的台面彼此电连接。整个布置被制成使得台面串联电连接,从而形成台面级联。当将形成为焊球的接合区域980a与电压源的正极和负极连接时,电压(例如,12v)沿着vcsel装置900下降。电流流过串联的单个台面901、902、903、904,如虚线990所示。

118.另外的焊球980b、980c、980d以及焊球980a、980e也用作散热器,使得每个发射器(台面)具有其自己的散热器。

119.图10示出了vcsel装置1000的实施例,该vcsel装置布置用于以多个不同波长带进行激光发射、例如以峰值发射在980nm的第一波长带、峰值发射在960nm的第二波长带、以及峰值发射在940nm的第三波长带。

120.vcsel装置1000的以不同波长带发射的区域由箭头1001、1002、1003指示。具体地,vcsel装置1000是顶面发射器。

121.vcsel 1000可以根据本公开的原理制造、即通过根据激光发射的发射峰值波长的数量来提供包括vcsel层结构1014的第一结构,该vcsel层结构具有区1014a、1014b、1014c。vcsel层结构1014包括例如所有区1014a、1014b、1014c共有的n型掺杂层1017。第一结构1012还包括晶片或衬底1016。vcsel装置1000可以根据本公开的原理通过使用如上所述的平坦化序列和产生从结构顶表面直到电接触区域的电过孔来制造,如图10所示。vcsel装置1000具有用于将vcsel装置1000电连接到外部驱动器的接合区域1070、1071、1072、1073,其中,区1001、1002、1003是可单独寻址的。

122.从本文的描述可以明显看出,根据本发明的制造vcsel装置的方法能够以低制造成本实现多种不同配置的vcsel装置。具体地,该方法允许vcsel装置具有小占用空间的vcsel芯片。该方法允许以高密集封装的方式制造具有可单独寻址的vcsel或台面的vcsel装置,允许光子部件集成和复杂的内部电布线。

123.虽然已经在附图和前述说明中详细展示和描述了本发明,但是这种展示和说明被认为是说明性的或示例性的而不是限制性的;本发明不限于所披露的实施例。从对附图、披露内容和所附权利要求的研究中,本领域技术人员在实施要求保护的发明时可以理解和实现对所披露的实施例的其他变化。

124.在权利要求中,词语“包括”不排除其他要素或步骤,并且不定冠词“一个(a)”或“一种(an)”并不排除多个。单个元件或其他单元可以实现权利要求中记载的几个项的功能。在彼此不同的从属权利要求中陈述的某些措施的简单事实并不表明这些措施的组合不能被有利地使用。

125.权利要求中的任何附图标记不应被解释为限制范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。