瞬态降噪滤波系统

1.相关申请的交叉引用

2.本技术要求于2019年9月6日提交的、申请号为62/897,085的美国临时专利申请的权益,该申请通过引用整体并入本文。

背景技术:

3.功率半导体器件用于许多不同的行业。其中一些行业正在迅速发展,例如电信、计算和收费系统。这些行业将受益于改进的半导体器件特性,包括可靠性、切换速度、低噪声、高容错性和小型化。

4.宽带隙半导体(wide-bandgap semiconductor,wbg)器件(例如,碳化硅(silicon carbide,sic)器件)包括以高切换速度提供高电流和高电压能力的功率器件。wbg功率器件可以包括,例如,金属氧化物半导体场效应晶体管(metal-oxide-semiconductor field effect transistor,mosfet),绝缘栅双极晶体管(insulated gate bipolar transistor,igbt),双极结型晶体管(bipolar junction transistor,bjt)和结型场效应晶体管(junction field effect transistor,fet),还包括肖特基二极管等二极管。

5.wbg器件通常需要低阻抗栅极驱动器,该低阻抗栅极驱动器必须位于极为靠近wbg功率器件的位置。此外,在大功率应用中,wbg功率器件可能需要散发大量热量,这要求wbg功率器件受到控制电子设备的物理侵犯。

6.此外,wbg器件的高切换速度和高电流容量可能在单位时间内流经器件的电流中产生很大变化(即,大δi/δt)。由于电路中存在固有的寄生电感,大δi/δt可能会产生大的快速电压尖峰(即,δv/δt噪声)。如果允许该δv/δt噪声被传播到wbg器件的控制电子设备,其可能会导致控制电子设备发生故障或损坏。

7.同时,控制电子设备必须能够在关闭时对击穿条件做出快速反应,或在开启时对可能出现的过电流和短路条件做出快速反应,因为反应不够迅速,这种情况可能会损坏或破坏wbg器件。

8.因此,需要控制wbg器件而不干扰从wbg器件提取热量,需要保护控制wbg器件的电子设备免受wbg器件操作产生的δv/δt噪声的影响,而不会在控制电子设备和wbg器件之间传送的信号中引起不适当的延迟。

技术实现要素:

9.实施例涉及针对每单位时间电压变化大的噪声尖峰(δv/δt)提供保护,例如,500到2000伏/纳秒(v/ns)或更大的噪声尖峰。这种噪声尖峰通常由高速、大功率的切换设备产生,例如,由宽带隙(wbg)半导体制造的功率器件。提供上述保护的设备可以是共模瞬态降噪滤波器。

10.在一个实施例中,瞬态降噪滤波器包括一个或多个共模扼流圈(common mode choke,cmc)和包括一对或多对双绞线导体的电缆。该一个或多个cmc由各多匝电缆形成。

11.在一个实施例中,一个或多个cmc中的一个可以是磁性cmc,其中,各多匝电缆缠绕

在磁芯上。

12.在一个实施例中,一个或多个cmc中的一个可以是空芯cmc,其中,多匝电缆不缠绕在磁芯上,设置在非磁性材料(例如,空芯)周围。

附图说明

13.图1示出了根据实施例的系统,该系统包括wbg功率器件。

14.图2呈现了示出根据实施例的包括wbg功率器件的系统的特性的表格。

15.图3示出了根据实施例的功率模块(power module,pm)。

16.图4示出了根据实施例的pm的更多细节。

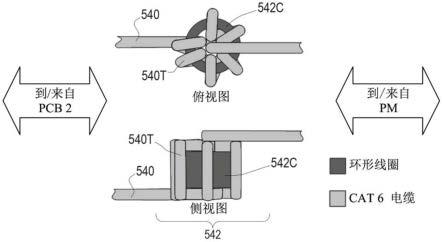

17.图5示出了根据实施例的共模扼流圈。

18.图6示出了根据实施例的第二cmc。

19.图7示出了根据实施例的包括第三cmc和隔离式电路的第二pcb。

20.图8示出了根据实施例的三个cmt和双绞线电缆。

21.图9示出了根据实施例的包括电源和控制电路的第一pcb。

22.图10示出了根据实施例的cmc的简化电路图。

23.图11示出了一个实施例中图10的电路对电压阶跃的响应。

24.图12示出了根据另一个实施例的cmc。

25.图13示出了图12的cmc的简化电路。

26.图14示出了根据另一个实施例的cmc。

27.图15示出了图14的cmc的简化电路。

28.图16示出了根据实施例的空芯cmc。

29.图17示出了根据另一个实施例的cmc。

30.图18示出了图17的cmc的简化电路。

31.图19示出了根据另一个实施例的cmc。

32.图20示出了图19的cmc的简化电路。

具体实施方式

33.本技术的实施例涉及为在宽带隙半导体上制造的器件(如碳化硅(sic)、氮化镓(gallium nitride,gan)、氧化镓(gallium oxide,ga2o3)和金刚石)实现高速切换、低噪声和高容错性。然而,实施例可以应用于使用在其他半导体上制造的器件的系统,例如硅、锗、砷化镓(gallium arsenide,gaas)等。

34.本公开涉及功率半导体器件,该功率半导体器件包括通用栅极驱动放大器(universal gate drive amplifier,ugda)和共模高(δv/δt)噪声干扰滤波器(即,共模瞬态降噪滤波器)。ugda将放大器管芯与功率器件的管芯一起放置在功率模块中。它将驱动和反馈要求从复杂的混合信号高电流和电压问题简化为简单的多通道标准数字输入和输出逻辑接口。数字输入和输出逻辑接口允许信号通过多导体双绞线电缆从功率模块传播到控制电子设备,例如,美国国家标准协会/电信行业协会标准ansi/tia-5686类(“cat 6”)电缆。

35.共模瞬态降噪滤波器将最新的高速wbg功率器件(例如,在sic或gan上制造的器

件)产生的200v/ns至高达约2000v/ns的极高δv/δt噪声降低至更合理的《50v/ns水平。共模瞬态降噪滤波器可以实现对高速wbg功率器件的无差错信号控制和反馈。

36.通用栅极驱动放大器(ugda)

37.功率模块可用于电动车辆(electric vehicle,ev)、ev快速充电器、数据中心、能量存储系统、航空航天等。实施例提供比相关技术的解决方案高得多的性能(高达10倍)和保护。更快、更安全的切换可以实现更高的电气效率、更少的散热以及更轻更小的pm。

38.此外,实施例为所有当前和未来的半导体功率器件提供这些性能和保护益处。

39.图1示出了根据实施例的系统100,该系统包括wbg功率器件136。系统100能够为当前和未来的wbg功率器件实现最快的切换,同时最小化过电压、意外故障和其他切换问题,并提供这些设备所需的极快的过流和/或去饱和保护,以在许多应用中实现可靠的性能。此外,实施例可以提供过电压或雪崩击穿检测,或两者都提供,并且可以作为响应,极快地开启wbg功率器件136,以防止损坏系统100的电路。

40.系统100包括第一、第二和第三印刷电路板(printed circuit board,pcb):第一pcb110(pcb 1)是控制板,第二pcb 120(pcb 2)是桥接子板,第三pcb 132(pcb 3)是包括在功率模块130中的通用栅极驱动放大器板(ugda)。pcb 110、pcb 120和pcb 132通过低电感屏蔽命令、控制、通信数据电缆140(下文中称为第一电缆140)连接。

41.第一pcb 110和第二pcb 120的左半部分使用接地标准进行工作。相反,第二pcb 120的右半部分和pm 130可以使用浮动接地标准进行工作,该浮动接地标准可能比接地标准高或低2000伏。

42.pm 130包括第三pcb 132、wbg肖特基二极管134和wbg功率器件136。在一个实施例中,肖特基二极管134是sic肖特基势垒二极管(sic schottky barrier diode,sbd),功率器件136是3.3kv sic mosfet管芯,但实施例不限于此。在一个实施例中,pm 130可以在25摄氏度的工作温度和150摄氏度的红线下工作。在另一个实施例中,pm 130的所有分立组件都是基于高温绝缘体上硅(silicon-on-insulator,soi)的组件,pm 130可在高达250摄氏度的温度下工作。在又一个实施例中,pm 130可以由全wbg组件组成,包括功率切换器件、肖特基二极管和wbg集成电路,它们均在高达900摄氏度的温度下工作。pm 130不包括位于pm顶部、用以限制电感的子板,在相关技术中经常这么做;这种子卡通常会限制wbg功率器件136的性能。

43.pm 130还包括第一cmc 142,用以实现超过500v/ns至2000v/nsdv/dt的共模瞬态抗扰度(common mode transient noise immunity,cmti)。图1所示的pm 130可以是应用中的低端或高端开关,电位范围从地电位到约2kv。所公开的技术似乎对高于或低于地电位的工作电位以及高于2000v/ns dv/dt的cmti没有任何实际限制。

44.在图1的实施例中,pm 130通过第一电缆140与第二pcb 120通信,其中第一电缆140可以是包括多对双绞线导体的标准cat 6电缆,也可以是耐高温cat 6电缆。第二pcb 120包括一个或多个浮动电源122来为第三pcb 132供电,还包括隔离式数字输入/输出(input/output,i/o)电路124,该隔离式数字输入/输出(i/o)电路124包括高速数字隔离式耦合器,用于向第三pcb 132提供(数字)栅极驱动信号并接收来自第三pcb 132的(数字)故障输出。来自第三pcb 132的故障输出被转换回接地标准信号,该接地标准信号被提供给第一pcb 110。可以由第一cmc 142、第二cmc 144和第三cmc 146为第二pcb 120和pm 130之间

的第一电缆140提供cmti保护。虽然图1示出了包括三个cmc的系统,实施例并不限于此,并且在实施例中,第一电缆140可以具有更多或更少的cmc来保护它。

45.第一pcb 110通过第二电缆116与第二pcb 120通信,第二电缆116也可以是cat 6电缆。第一pcb 110可以包括用于第二pcb 120的一个或多个电源112,并且还可以包括与第二pcb 120交换数字信号的控制器电路114。控制器电路114提供必要的数字和模拟信号处理存储器以及编程智能,用以实现任何最终应用,例如电动车辆、风车、电泵、电照明、功率转换装置或任何其他电操作和控制的电机。

46.在一个实施例中,在不牺牲切换速度或低延迟的情况下,第一pcb 110和第二pcb 120可以相隔5米(即,第二电缆116可以是5米或更长),并且pcb 2和pcb 3之间的距离可以是1米(即,第一电缆140可以是一米或更长)。因此,第一pcb 110可以在相对良性的环境(例如,0至 70摄氏度的环境温度)中工作,第二pcb 120在更具挑战性的环境(例如,-55至 85摄氏度的环境温度)中工作,pm 130在恶劣的环境(例如,今天的环境温度为-55至 250摄氏度,甚至 400摄氏度或更高)中工作。此外,虽然在pm 130上可能出现δv/δt高达2000v/纳秒的噪声电压瞬变,但第一pcb 110和第二pcb 120上的噪声电压瞬变可能已将δv/δt降低到10v/纳秒或更小。

47.图2呈现了示出根据实施例的包括wbg功率器件的系统的特性的表格。首先,cmti(共模瞬态噪声抗扰度)》500v/ns,远高于可用的商用栅极驱动器系统提供的值。其次,过流比较器的输出v

fbar

可以在不到20纳秒(ns)的时间内在第三pcb 132内提供局部过流故障保护和关断,并将检测到的故障输出回控制器以进行故障缓解处理。第三pcb 132内的这种低延迟和本地实现的保护允许将诸如自适应死区时间控制的功率控制技术用于大功率器件,从而提高整体系统效率。第三,根据实施例的pm的顶部不需要子板,其中,耐热性最低的组件可能会限制wbg功率器件的性能。相反,实施例将可能位于相关技术系统中的子板上的电子设备放置在可能长达3米或更长的电缆的另一端,远离wbg功率器件产生的热量。

48.实施例可以基于低成本半定制cmti电路实现超过500v/ns和高达2000v/ns的cmti。在一个实施例中,cmc使用缠绕在高频环形线圈上的cat 6电缆来提供cmti。实施例提供的cmti远高于在最近的sic mosfet pm或演示印刷电路板(pcb)中所示的切换波形中看到的cmti。将第三pcb 132定位在包括wbg功率器件136和wbg肖特基二极管134的同一pm 130内,这样可以最小化与驱动wbg功率器件136的栅极相关的寄生效应,并且还可以在电路和电源系统仿真中包含全套寄生参数,以优化和保护pm 130的预期切换性能。这使未来的最低能量路径设计和模拟成为可能。

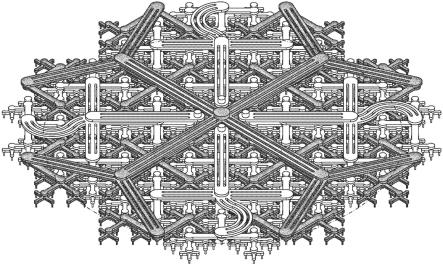

49.图3示出了根据实施例的功率模块330。pm 330可以体现在图1的pm 130中。

50.pm 330包括第一cmc 342、栅极驱动器pcb 332、肖特基二极管334和功率器件336,其可分别对应图1中的第一cmc 142、第三pcb 132、wbg肖特基二极管134和wbg功率器件136。在所示实施例中,肖特基二极管334和功率器件336是sic器件。

51.栅极驱动器pcb 332产生栅极驱动信号gdnn和过电流驱动信号ocdn。栅极驱动信号gdnn用于通过对功率器件336的栅极g的栅极电容进行充电和放电来开启和关闭功率器件336。过电流驱动信号ocdn用于通过对功率器件336的栅极g的栅极电容进行放电来关闭功率器件336,但是可以以不同于栅极驱动信号gdnn的速率来进行此操作。一般而言,功率元件336的栅极g对应于控制端,而功率器件336的漏极d和源极s对应于导电端。

52.pm 330经由双绞线电缆340接收第一高压(high voltage,hv)正电源电压v

hcc

、第二hv正电源电压v

hdd

和hv接地hgnd。pm 330还从电缆340接收差分hv栅极信号v

hg

和v

hgbr

,并向电缆340提供差分hv故障信号v

hf

和v

hfbr

。这里,“hv”指的是系统浮动接地端的电源电压,而不是所提供电压的绝对幅度。电缆340包括多对双绞线,第一双绞线和第二双绞线分别携带下列中的一个:第一hv正电源电压v

hcc

、一个导体上的第二hv正电源电压v

hdd

和另一个导体上的hv接地hgnd;第三双绞线携带差分hv栅极信号v

hg

和v

hgbr

;第四双绞线携带差分hv故障信号v

hf

和v

hfbr

。电缆340具有缠绕在铁氧体环形线圈342c上的多个长度的340t以形成第一cmc 342。

53.将第一cmc 342放置在pm 330中将在两个方向(从栅极驱动器pcb 332回到图1的第二pcb 120;从第二pcb 120到栅极驱动器pcb 332)上去耦基于浮动接地的切换瞬态噪声,该切换瞬态噪声耦合到栅极驱动器pcb 332上的差分hv栅极信号v

hg

和v

hgbr

。栅极驱动器pcb 332可以在高温pcb上实现,其中分立器件表面直接安装在直接键合的铜陶瓷基板(direct bonded cu ceramic substrate,dcb)上,而功率器件336和肖特基二极管334是芯片连接和引线键合的。栅极驱动器pcb 332与功率器件336紧密耦合,其设计和布局将栅极驱动器和被驱动功率器件336周围的寄生效应降至最低。使用开尔文源(kelvin source,ks)连接以确保完全直接测量功率器件336的栅极电压,而不受其源电流的影响。此外,物理布局集中于用于第一hv正电源电压v

hcc

的第一旁路电容器302和用于hv负电源电压v

ee

的第二旁路电容器302,以确保栅极驱动器切换电源回路中的低电感。

54.一些wbg功率器件(例如,当前一代的sic mosfet)无法承受超过约1μs的高故障电流事件。因此,需要在不到1μs的时间内检测到故障并软关闭设备。

55.图4示出了根据实施例的pm 430的栅极驱动器pcb 432的更多细节。第三pcb 432可以对应于图3中pm 330的第三pcb 332。pm 430还包括第一cmc 442、肖特基二极管434、功率器件436、v

hcc

去耦电容器402和v

ee

去耦电容器404,它们对应于图3中pm 330的类似编号的组件。因此,为简洁起见省略其详细描述。

56.在一个实施例中,第一cmc 442包括缠绕在高频铁氧体磁芯上的多匝双绞线电缆440。在另一个实施例中,cmc 442包括缠绕在空芯上的多匝电缆440。

57.栅极驱动器pcb 432包括有源器件,该有源器件包括第一n-通道mosfet(nmosfet)426、第二nmosfet 428、栅极驱动器放大器450、与非门452、第一比较器454、反相器456、第二比较器458和电荷泵(chargepump,cp)电路460。栅极驱动器pcb 432还包括无源器件,该无源器件包括第一电阻器410a、第二电阻器412、第三电阻器414、第四电阻器416、第五电阻器418、第六电阻器420、第七电阻器422、第八电阻器424和第九电阻器410b、v

hdd

去耦电容器444、cp电容器446和消隐电容器448。

58.第一电阻器410a和第九电阻器410b为通过第一cmc 442接收的差分hv栅极信号v

hg

和v

hgb

r提供阻抗匹配,以匹配双绞线电缆的阻抗440,该双绞线电缆440用于通过第一cmc 442将pm 430连接到其他板(例如,图1中的第二pcb 120)。例如,第一电阻器410a和第九电阻器410b可以各自具有50欧姆的电阻。第二比较器458接收差分hv栅极信号v

hg

和v

hgbr

,并且根据比较将输入信号in驱动到栅极驱动放大器450。

59.第七电阻器422可以具有1欧姆的电阻,以匹配由功率器件436的栅极电容和栅极驱动放大器450的输出与功率器件436的栅极g之间的寄生电感产生的阻抗。这种低阻抗使

得栅极驱动放大器450靠近功率器件436是有利的。

60.栅极驱动器pcb 432包括完全可编程的消隐电路,该电路包括与非门453、第一nmosfet 426、消隐电容器448和第六电阻器420。通过选择消隐电容448和第六电阻420,可以调整消隐电路以提供从远低于1μs到超过10μs的消隐周期。响应于栅极驱动信号gdnn开启功率器件436,消隐电路通过第一nmosfet 426将第一比较器454的反相输入接地短路,在消隐期间禁止第一比较器454进行去饱和/过电流检测。当消隐期期满时,即,当消隐电容器448已通过第六电阻器420被充分充电以被与非门452视为逻辑高信号时,第一nmosfet426被关闭,其次第一比较器454能够通过感测去饱和电压v

dsat

来执行去饱和/过电流检测。

61.在去饱和或过电流事件期间,功率器件436的漏极电压反向偏置肖特基二极管434。因此,当检测到去饱和或过流事件启用时,去饱和电压v

dsat

电压升高,将任何寄生电容(包括肖特基二极管434的反向偏置阳极到阴极电容)充电至由第四电阻器416和第五电阻器418的相应电阻值r

416

和r

418

定义的电压,v

dsat

=v

hcc

*r

418

/(r

416

r

418

)。响应于去饱和电压v

dsat

上升到去饱和电压阈值v

dsth

以上,该去饱和电压阈值vdsth是由第二电阻器412和第三电阻器412的各自电阻值r

412

和r

412

确定的,v

dsth

=v

hcc

*r

414

/(r

412

r

414

),在第一比较器454的比较器延迟之后(通常为10纳秒(ns)左右),第一比较器454的输出被驱动为低电平。第一比较器454的输出和逆变器456的输出分别作为差分hv故障信号v

hfbr

和v

hf

通过第一cmc 442传输回控制器,例如,图1中的第一pcb 110的控制器114。

62.第一比较器454的输出用于关闭功率器件436。第一比较器454的输出驱动栅极驱动放大器450的使能信号en,并通过将使能信号en驱动为低电平,使栅极驱动放大器450停止驱动耦合到功率器件436的栅极g的栅极驱动信号gdnn。同时,第一比较器454的输出通过反相器456来开启第二nmosfet 428。开启第二nmosfet 428使得功率器件436的栅极电容通过第八电阻器424放电到hgnd,从而关闭功率器件436。选择第八电阻器424的值以通过“缓慢地”关闭功率器件436来防止δv/δt引起的过电压过冲和雪崩击穿。因此,第八电阻器424的电阻值将高于第七电阻器422的电阻值,第七电阻器422用于在正常操作条件下打开和关闭功率器件436。使用第一比较器454,栅极驱动器pcb 432的去饱和/过电流检测电路被设计为在不到100ns内启动关闭周期,同时将hv故障信号v

hfbr

更快地发送回控制器(例如,图1中的第一pcb 110的控制器114)。

63.实施例还可以提供过电压条件、雪崩击穿条件或两者的检测和缓解。cmc 442和图1中的其他cmc产生的低噪声、低电磁干扰(electro-magnetic interference,emi)环境使这成为可能。低噪声允许对由于意外情况而存在于功率器件436的漏极或源极电感上的电压进行毫伏检测,例如高能粒子辐射导致漏极耗尽区的电离。这样的辐射可以在由粒子的轨迹引起的非常小的体积内引起高能等离子体放电。这种等离子体放电会导致意外的电流从受影响的功率器件的漏极流向源极(不仅包括sic半导体,还包括gaas或硅半导体)。如果不加以缓解,受影响的器件将在10纳秒(ns)内损坏。一个简单的缓解措施是打开受影响的功率器件,将由高能等离子体引起的电流从其小体积(小体积可以是具有原子或晶格横截面积和从功率器件的漏极到源极的大约为10微米到100微米的长度的路径)转移到功率器件的总面积。这可以分散热能,因此热能不会在原子的横截面上消散,而是在功率器件芯片的整个区域中消散。

64.pm 430可能能够承受从》500v/ns到2,000v/ns的nv/nt切换噪声。此外,通过使用

第一cmc 442,pm 430可以提供比相关技术中最好的商业栅极驱动器更好的δv/δt噪声抗扰度。相关技术只能提供δv/δt到150v/ns的抗扰度。

65.图1中的系统100包括三个cmc:pm 130中的第一cmc 142,其正好位于第三pcb 132之前或边缘上,与将第二pcb 120连接到第三pcb 132的第一电缆140串联放置的第二cmc 144,以及在第二pcb 120内的第三cmc 146。第一cmc 142、第二cmc 144和第三cmc 146的构造类似,但是每根电缆的匝数、芯材和物理尺寸都不同。

66.第一电缆140可以是cat 6电缆。cat 6电缆(具有四对双绞线,每对的特性阻抗为100)具有抵消周围外部磁场和电场的特性。信号通过cat 6电缆的传播速度是真空中光速的75%,或约为22.5cm/ns。因此,一米cat6电缆的延迟t

delay

为:tdelay=(100cm/22.5cm)*ns=4.4ns。

67.图5图示了根据实施例的共模扼流圈(cmc)542。cmc 542可以对应于图1的第一cmc 142、第二cmc 144或第三cmc 146中的任何一个。cmc 542的实施例不限于具有匝数。

68.cmc 542包括缠绕在磁芯542c上的多匝540t双绞线电缆540。双绞线电缆可以对应于图1的第一电缆140。在一个实施例中,双绞线电缆540是具有四对双绞线导体的cat 6电缆,但实施例不限于此。cmc 542的实施例不限于具有图5所示的匝数540t。

69.在对应于第一cmc 142的cmc 542的实施例中,磁芯542c为高频铁氧体磁芯,例如,fair-低磁导率67材料、ui=40、环形、magnetics kool环形等。例如,cmc 542可以使用fair-rite零件#5967003801,材料67高频环形线圈,具有多达17匝的cat 6电缆,al为55nh,为cmc 542创建多达(17)2*55nh=15.9μh的共模电感。

70.在对应于第二cmc 144的cmc 542的实施例中,磁芯542c为中等带宽铁氧体磁芯,如fair-rite 5943003801、ui=800材质的环形磁芯等。使用fair-rite 5943003801和17匝cat 6电缆,cmc 542可能具有310μh的共模电感。

71.在对应于第三cmc 146的cmc 542的实施例中,磁芯542c是低频高磁导率铁氧体磁芯,例如ui=5000的fair-rite 75材质核心等。使用fair-rite 75材料芯和17匝cat 6电缆,cmc 542的共模电感可能为1.97mh。

72.如图1所示,第一cmc 142正好在pm 130内部并且与第三pcb 132相邻,第二cmc 144可以沿着第一电缆140位于第二pcb 120附近,第三cmc 146位于第二pcb 120的边缘。

73.图6示意性地示出了根据实施例的第二cmc 644和电缆640。电缆640可以对应于图1中的第一电缆140。第二cmc 644可以对应于沿着第一电缆140位于图1中的第二pcb 120附近的第二cmc 144。

74.第二cmc 644包括缠绕在磁芯上的多匝双绞线电缆640。在一个实施例中,磁芯是中等带宽铁氧体磁芯。在另一个实施例中,磁芯是空芯。

75.图7示出了根据实施例的第二pcb 720,其包括第三cmc 746、浮动电源722、数据输入/输出隔离电路724和隔离电路。第二pcb 720还包括第一去耦电容器702、第二去耦电容器704、第三去耦电容器706和第四去耦电容器708,以及第一阻抗匹配电阻器710a和第二阻抗匹配电阻器710b。第二pcb 720可以对应于图1的第二pcb 120。

76.第二pcb 720在图7左侧的接地标准电路和图7右侧的浮动高压侧接地标准电路之间提供电流隔离。浮动电源722可以包括,例如,相关技术的变压器隔离电源。数据输入/输出(i/o)隔离电路724可以包括,例如,模拟设备ltm2810。

77.浮动电源722可以接收gnd标准的接地的电源电压v

cc

和v

dd

形式的电力,并使用它们产生gndh标准的浮动高端接地电源电压v

cch

和v

ddh

。

78.数据i/o隔离电路724可以根据接地标准栅极信号vg来驱动差分hv栅极信号v

hg

和v

hgbr

。数据i/o隔离电路724还可以根据差分hv故障信号v

hfbr

和v

hfbr

来驱动接地标准故障信号v

fbar

。

79.电源电压v

cch

和v

ddh

、浮动高端接地gndh、差分hv栅极信号v

hg

和v

hgbr

可以通过第三cmc 746提供给双绞线电缆740,并且可以通过第三cmc 746从电缆740接收差分hv故障信号v

hf

和v

hfbr

。第一阻抗匹配电阻器710a和第二阻抗匹配电阻器710b可以为差分hv故障信号v

hf

和v

hfbr

提供阻抗匹配,并且可以各自具有50欧姆的电阻。

80.第三cmc 746包括缠绕在磁芯上的多匝双绞线电缆740。在一个实施例中,磁芯是低频高磁导率铁氧体芯。在另一个实施例中,磁芯是空芯。

81.图8图示了根据实施例的第一cmt 842、第二cmt 844和第三cmt 846,以及双绞线电缆840。图8还示出了第二pcb 820和电源模块830。上面列出的图8的元素可分别对应于图1中的第一cmt 142、第二cmt 144和第三cmt 146、双绞线电缆140、第二pcb 120和电源模块130。

82.图8还示出了3个cmc相对于接地的寄生电容(parasitic capacitance,pac):第一cmc 842的第一pac 802、第二cmc 844的第二pac 804、第三cmc 842的第三pac 806。cmc及其各自的pac在各自的时间常数处创建双极,根据是:

[0083][0084]

其中,t

tdelay

是通过cmc的传播延迟,l

t

是cmc的开路电感,c是对接地的cmc寄生电容。

[0085]

因此,关于图8,第一cmc 842工作,以根据pm 830的第一pac 802相对于接地产生第一延迟t

tldelay

,第二cmc 844工作,以根据电缆840的第二pac 804相对于接地产生第二延迟t

t2delay

,第三cmc 846工作,以根据第二pcb 820的第三pac 806相对于接地产生第三延迟t

t3delay

。对于cmti噪声,这会影响δv/δt噪声从pm 830横穿到第二pcb 820的总时间,这是所有均方根延迟之和的平方根。

[0086]

如果选择核心材料,这样,第一cmc 842使用具有非常宽的带宽的非常低的渗透核心,然后极高的瞬态电流和电压会导致潜在的高b和h场,因此,第一cmc 842的开路电感l

t1

可以约为1微亨(microhenry,μh),并且与20微微法拉(picofarad,pf)的pm 830的第一pac 802对抗。第二cmc 844使用中等带宽核心,这样,第二cmc 844的开路电感l

t2

可以约为100μh,并且由于长度为1米,电缆840的第二pac 804可以是200pf。第三cmc 846采用低频高磁导率磁芯,这样,第三cmc 846的开路电感l

t3

可以约为10毫亨(millihenry,mh),而第二pcb 820的第三pac 806为100pf。使用下列值,

[0087][0088][0089][0090]

其中,c802、c804和c806分别是第一pac 802、第二pac 804和第三pac 806的电容。

因此,总共模延迟为:

[0091][0092]

作为参考,长度约200cm(2米)的cat 6电缆的潜在延迟等于4.4ns*2=8.8ns。这是共模噪声从pm 830传回第二pcb 820的时间的约1/50。

[0093]

图1中的系统100的实施例通过将栅极驱动器132与被驱动的wbg功率器件136共同封装来改善被驱动的wbg功率器件136(例如,sic mosfet)的切换行为。这导致栅极驱动器132和wbg功率器件136之间的栅极到源极电感较低,从而可以实现更快的切换,而不会产生相关的过压或杂散开启。

[0094]

pm 130可以包括功率器件136,例如功率sic mosfet和相关部件。将高电流栅极驱动器(例如,ixys ixd 614 14a栅极驱动器)放置在第三pcb 132(第三pcb 132直接安装到包含功率器件136的dcb基板上)上,可以大大降低功率器件的栅极驱动器输出之间的串联栅极电感,但更重要的是,它允许识别、确定、考虑、模拟和适应不可避免的寄生电容和电感,从而为驱动功率器件136实现临界阻尼阶跃响应要求。用于pm或分立sic mosfet的商用pcb子板栅极驱动器的最佳串联电感约为20nh至100nh ,其中,输入到sic mosfet pm的寄生电感为6nh及以上。

[0095]

供应商可能未定义或未指定这些值,或者如果今天从设备到设备以及从制造商到制造商的指定正常变化很大。由于sic mosfet栅极氧化物的过应力,在100%捕获或公开呈现的栅极波形中观察到不可避免的高速振铃,这会限制切换性能并导致场可靠性问题。

[0096]

参考图4,第三pcb 432可以包括通用栅极驱动放大器(ugda)。将ugda放置在pm 430内可简化驱动pm 430并显著改善被驱动pm和控制器之间的切换和通信反馈。由第一比较器454产生的hv故障信号v

hfbr

的输出通过第二pcb 720控制器反馈给控制器,作为故障信号v

fbr

,如图7所示。

[0097]

通过图4中的第一比较器454,从去饱和电压v

dsat

的传播延迟约为10ns的单个比较器延迟。由于电缆的信号延迟为每30cm约1ns,如果总电缆长度设置为约2米,那么预计电缆的总延迟不超过25ns。从驱动pm到控制器的高速信号允许对大功率系统(例如165kw系统)进行自适应死区时间控制,这样可以显著改善主电网和其他应用的电力电子设备的控制和效率。

[0098]

输出电流在 /-1a至 /-14a范围内的ugda将支持目前销售的大多数sic mosfet,并通过改变栅极电阻器的电阻值,即图4中的第七电阻器422的电阻值,适用于特定的功率器件。在实施例中,ugda的切换频率可以是从1khz到200khz,但实施例不限于此。

[0099]

根据实施例的ugda向输出延迟提供最小的输入。在将商业栅极驱动器的裸芯片与商业sic mosfet封装在功率模块中的实施例中,延迟限于以芯片形式可用的最佳商业栅极驱动器。200khz的切换频率限制主要由栅极驱动器输入与最终输出延迟的倒数决定。

[0100]

一个实施例可以使用3.3kv 50a sic mosfet作为功率器件436。ugda和dcb外部寄生参数(例如,引线键合和走线电感、层间pac和sic mosfet模型参数)可用于全瞬态仿真。可以使用从电磁模拟中提取的参数。因此,可以固定组件值,可以购买用于pm 430的组件,可以组装和测试pm430,以确保模型与实际设备的合规性和验证,并且改进的模型可用于改

进后续的pm。可能需要调整的组件的示例包括去饱和/过电流消隐时间、去饱和电压阈值v

dsth

,以及耦合在栅极驱动放大器450的输出端和功率器件436的栅极之间的串联电阻器422。

[0101]

与当前行业惯例一样,每个wbg si、sic或gan mosfet功率器件可能需要不同的ugda特定组件。主要或完全可编程的外部电源组件可以放置在dcb上。

[0102]

在一个实施例中,ugda可通过稳压中间电源和-5v至-10v的-vee电荷泵(必要时再次通过稳压中间电源)适应 12v至 30v的vdd。ugda可以使用商用电容式电荷泵ic(例如,maxim max889或同等产品)来实现电荷泵460。

[0103]

在一个实施例中,商用稳压电源仅为第二pcb 120提供正电源电压v

ddh

。可以使用具有25v/ns或更低cmtiδv/δt噪声性能的高速、低延迟数字数据耦合器提供4kv ac的全电流隔离,例如,可以从具有17ns的指定延迟的texas instruments或具有9ns的指定延迟的maxim获得。此外,模拟设备ltm2810是一款数字数据耦合器,可通过7500v的输入到输出隔离和50v/ns的cmtiδv/δt性能提供电源;但是,它的输入到输出延迟为100ns。这些具有δv/δt规格的商用光耦合器都应该能够适应5v/ns。或者,可以使用其他类型的高压数据耦合器,例如,德州仪器公司的电容数据耦合器和模拟设备公司的rf变压器数据耦合器。相应地,图1中的cmc746(或图7中的第三cmc 746)可以具有低频高磁导率核心材料,以充分利用信号链中预期的相对良性的δv/δt cmti噪声。

[0104]

图9示出了根据实施例的包括电源912和控制器914的第一pcb 910。第一pcb 910、电源912和控制器914可以分别对应于图1中的第一pcb110、电源112和控制器114。

[0105]

电源912使用来自电源v

buss

的能量提供电源电压v

cc

和v

dd

。控制器914根据硬件或软件程序控制和故障信号v

fbr

来控制栅极信号vg,该故障信号v

fbr

对应于在例如图4中的pm 430的功率模块中产生的hv故障信号v

hfbr

。

[0106]

提高共模瞬态抗扰度(cmti)

[0107]

使用最新宽带隙半导体的高速切换系统需要能够实现共模瞬态抗扰度、cmti大于200v/ns的高端隔离式栅极驱动器。cmti ip使用一个特别选择的磁环,该磁环缠绕有特殊构造的电缆。cmti(共模瞬态抗扰度)电路采用由最新的宽带隙半导体(如sic或gan)和c(金刚石)产生的非常高的dv/dt(约200v/ns至1000v/ns),并将δv/δt降低到更易于管理的约1v/ns至50v/ns。本发明最简单的形式是低通滤波器。然而,普通(非共模)滤波可能会在信号传播中引入不可接受的延迟。因此,可以使用用于差分信号的共模低通滤波器(例如共模扼流圈)。

[0108]

图10示出了共模扼流圈(cmc)的简化电路配置,从共模(即,非差分)中可以看出。v

hgnd

(t)是高端功率器件输出的来源,也是非常高的δv/δt共模阶跃的来源,v

gndh

(t)是经过cmc共模电感l

cmc

之后的高端共模阶跃,例如,可能存在于图1中的第二pcb 120的数据隔离器和浮动电源gndh电路处。cmc共模电感l

cmc

位于v

hgnd

(t)和v

gndh

(t)之间,并与cmc和电缆的杂散电容c

stry

形成一个简单的二阶双极滚降滤波器网络。

[0109]

图11示出了图10的电路在一个实施例中对电压阶跃的响应。为清楚起见,波形已被简化。

[0110]

首先,假设产生v

cm

(t)=v

hgnd

(t)的v

hgnd

(t)源是低阻抗源,从而可以忽略串联输出电阻。其次,经过cmc共模电感l

cmc

和杂散电容c

stri

的低通网络后得到的v

gndh

(t)是欠阻尼响

应,并假设v

gndh

(t)上的任何负载都很小,可以忽略不计。有了这些假设,并选择l

cmc

=300μh和c

stry

=40pf,通过图11中绘制的解决方案求解基本的二阶响应。使用双极滚降f

rolloff

的频率可以计算为:

[0111][0112]

所以一个完整的周期需要1/f

rolloff

=688ns。

[0113]

出于所有实际目的,v

gndh

的负载是开路的。然而,由于布局不佳和电磁干扰、emi实践,可以假设v

gndh

上的所有内容都辐射到自由空间中。自由空间的特性阻抗为zo=377欧姆。计算α=1/(377

·2·cstry

)=66μs,由于109.5ns《《66us,v

gndh

(t)仍然是一个非常欠阻尼的振荡,如图11所示,滚降频率f

rolloff

为1.45mhz,基于提供的l

cmc

和c

stry

的值。

[0114]

图11中所示的波形大致按比例绘制。因此,无需进行大量数学运算,波形的最大斜率以图形方式测量为35v/ns。35v/ns的共模瞬态抗扰度cmti是可以接受的,远低于1000v/ns的初始值。

[0115]

当然,将电感器与浮动栅极驱动器串联会出现一些相应的问题,其中,位于f

rolloff

的谐振极的低通滤波作用会导致如图11所示的大约的时间延迟。因此,如前所述,使用电感值为l

cmc

的共模扼流圈代替简单的电感器,如下面的图12-16所述。

[0116]

图12图示了根据另一个实施例的cmc 1242。cmc 1242包括环形芯1242c和多匝1240t屏蔽双绞线电缆1240,多匝1242c缠绕在环形芯1242c上。

[0117]

屏蔽双绞线电缆1240包括电介质1206内部的绝缘导体双绞线1204。电介质封装在法拉第屏蔽1202内,法拉第屏蔽1202可以由金属箔、金属丝或它们的组合制成。

[0118]

图13图示了图12中的cmc 1242的简化电路。如图12所示,在本示例中,双绞线1204的导体可以分别接收输入栅极信号v

gh

和输入接地gndh,输入栅极信号v

gh

和输入接地gndh通过cmc 1242后,分别成为输出栅极信号v

hg

和输出接地hgnd。此外,法拉第屏蔽1202在cmc 1242的一侧(仅一侧)接地。

[0119]

顾名思义,cmc 1242在扼流圈的两个端子之间产生相等但相反的信号,这样cmc 1242的l

cmc

的感应效应抵消了差分信号。对于双绞线1204上的信号,只有存在于输入栅极信号v

gh

和输入接地gndh之间的差分信号被传输到输出栅极信号v

hg

和输出接地hgnd,由于特定长度的电缆内信号的有限速度,可能存在大约3ns/米的信号延迟。sgnd是一个法拉第屏蔽连接,用于防止和绕过v

hg

侧存在的非常高的δv/δt,因此它不会电容耦合到v

gh

侧,而是直接耦合到系统接地。

[0120]

图12中的cmc 1242是基于环形磁芯的,但还有其他结构,例如,更适合扁平功率模块的“薄饼”扼流圈。内部和外部绝缘厚度可以根据预期工作电压的需要进行调整。

[0121]

图14示出了cmc 1442的实施例,该cmc 1442被设计为接受电缆1440,该电缆1440具有用于电力输送的多个绝缘导体、用于接地的多个裸导体和用于差分数据符号的多对双绞线(统称为导体1404)。除了导体1404之外,电缆1440还包括电介质1406和法拉第屏蔽1402,例如对图12中的电缆1240所进行的描述。cmc 1442包括缠绕在环形芯1442c上的多匝1440t电缆1440。

[0122]

图15示出了cmc 1442的电路图。在cmc 1442中,两组电源线和两对双绞线连接在gndh侧和hgnd侧之间。由于图15的显著特征可以从图13的描述中推导出来,为简洁起见,省略对图15的进一步描述。

[0123]

图16示出了根据另一个实施例的cmc 1642。cmc 1642接受包括一对或多对双绞线的电缆1640,在实施例中,电缆1640可以是上述电缆340、电缆440、电缆640、电缆1240或电缆1440中的一个。cmc 1642包括缠绕在非磁性线轴1642c上的多匝1640t电缆1640,非磁性线轴1642c可以由,例如,尼龙、聚酯、环氧树脂或酚醛树脂制成。在一个实施例中,cmc 1642不包括线轴1642c,并且多匝1640t改为通过粘合剂、灌封化合物、系带(例如“拉链系带”)等保持在适当位置。

[0124]

cmc 1642是不使用磁芯的空芯cmc。因此,在使用磁芯的cmc可能饱和的情况下,cmc 1642可能很有用。为了实现必要的电感l

cmc

,cmc 1642可以在多匝1640t中包括两米或更长的电缆1640。

[0125]

图17图示了根据另一个实施例的cmc 1742。当cmc 1742作为电缆共模扼流圈时,在单个屏蔽双绞线电缆上使用环形线圈(该电缆具有用于法拉第屏蔽的整体编织外部屏蔽)将gndh连接到hgnd。cmc 1742包括环形芯1742c和多匝1740t屏蔽双绞线电缆1740,多匝1742c缠绕在环形芯1742c上。

[0126]

屏蔽双绞线电缆1740包括电介质1706内部的绝缘导体双绞线1704。电介质被封装在法拉第屏蔽1702内,该屏蔽1702可以由金属箔、金属线或其组合制成。

[0127]

图18示出了图17中的cmc 1742的简化电路。如图17所示,在本示例中,双绞线1704的导体可以分别接收输入栅极信号v

gh

、其互补v

ghbr

和输入接地gndh,上述输入栅极信号v

gh

、其互补v

ghb

r和输入接地gndh在通过双绞线后,分别成为输出栅极信号v

hg

、v

hgbr

和输出接地hgnd。此外,在这里,cat 7电缆的编织外屏蔽层以及围绕每对双绞线的全导电箔包裹的屏蔽形成一个法拉第屏蔽1702,它与大地电隔离,但它是一个安静且低于10v/ns的低cmti环境。在一个实施例中,该电缆的另一侧穿过图1中的第一cmt 142而成为第一hgnd,该cmt 142使用cmc 1742中的cat 7电缆构建或使用没有法拉第屏蔽的cat 6电缆构建。

[0128]

顾名思义,cmc 1742在包含在该扼流圈内的两个双绞线导体之间产生相等但相反的信号,这样cmc 1742的l

cmc

的感应效应从gndh侧到hgnd侧被有效地抵消,用于这些双绞线对中包含的差分信号。对于双绞线1704上的信号,只有存在于输入v

gh

和v

ghbr

之间的这些信号的差分信号作为v

hg

和v

hgbr

传输到输出,由于特定长度的电缆内信号的有限速度,可能存在大约3ns/米的信号延迟。在图18中,左侧的gndh是图17中的编织屏蔽,其作为法拉第屏蔽与右侧的hgnd结合使用,以最小化v

hg

右侧和v

hgbr

侧存在的非常高共模δv/δt的电容耦合,以直接接地,但仅连接到法拉第屏蔽或hgnd。同样,防止v

gh

和v

ghbr

的任何直接耦合进行接地,相反,这些信号只直接耦合到法拉第屏蔽或系统接地gndh。这样,图17和图18的法拉第屏蔽用于保持右侧的v

hg

和v

hbr

以及左侧的v

gh

和v

ghbr

的差分性质。

[0129]

图17中的cmc 1742是基于环形磁芯的,但还有其他结构,例如,更适合扁平功率模块的“薄饼”扼流圈。内部和外部绝缘厚度可以根据预期工作电压的需要进行调整。

[0130]

图19示出了cmc 1942的实施例,该cmc 1942是一种电缆共模扼流圈,在具有整体屏蔽的cat 7电缆上使用环形线圈作为法拉第屏蔽,将gndh连接到hgnd。cmc 1942使用cat 7电缆,与非屏蔽cat 6电缆相比,cat 7电缆被设计用于接受电缆1940,电缆1940具有用于

差分数据符号的多对双绞线(统称为导体1904)。除了导体1904,电缆1940还包括电介质1906和法拉第屏蔽1902,例如,对图17中的电缆1240所进行的描述。cmc 1942包括缠绕在环形芯1942c上的多匝1940t电缆1940。

[0131]

图20示出了具有cat 7电缆的cmc 1942的电路图。在cmc 1942中,两组电线从左到右、从v

cch

到v

hcc

、从v

ddh

到v

hdd

以及它们各自的两对双绞线gndh和hgnd供电。由于图20的显着特征可以从图17和图18的描述中推导出来,为了简洁起见省略对图20的进一步描述。

[0132]

以下结合附图对实施例进行详细描述。本公开的范围仅由权利要求限制并且包括许多替代、修改和等同物。尽管各种过程的步骤以给定的顺序呈现,但实施例不必限于以列出的顺序执行。在一些实施例中,某些操作可以同时执行,以不同于所述顺序的顺序执行,或者根本不执行。

[0133]

在以下描述中阐述了许多具体细节。提供这些细节是为了通过具体示例促进对本公开的范围的全面理解,并且可以根据权利要求实施实施例而无需这些具体的细节。因此,本公开的具体实施例是说明性的,而不是排他性的或限制性的。为了清楚起见,没有详细描述与本公开相关的技术领域中已知的技术材料,以免不必要地模糊本公开。

[0134]

已经结合作为示例提出的具体实施例描述了本公开的各方面。不脱离下面阐述的权利要求的范围的情况下,可以对这里阐述的实施例进行许多替换、修改和变化。例如,功率器件可以在正面具有不同厚度的金属图案,在背面具有不同厚度的另一个金属图案,这样可以从两侧进行寿命控制处理。因此,本文阐述的实施例旨在是说明性的而非限制性的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。