显示装置

1.相关申请的交叉引用

2.本技术要求2020年7月31日提交至韩国知识产权局(kipo)的第10-2020-0096027号韩国专利申请的优先权,该申请的全部公开通过引用合并于此。

技术领域

3.本公开通常涉及一种显示装置。更具体地,本公开涉及一种能够防止像素收缩缺陷的显示装置。

背景技术:

4.显示装置包括多个金属层以及设置在金属层之间的绝缘层。设置在显示区域中的像素和设置在非显示区域中的线可以由金属层形成。绝缘层包括绝缘材料以防止金属层之间的短路。例如,绝缘层包括无机材料或有机材料。

5.同时,从有机材料产生的气体从包括有机材料的绝缘层中排出。例如,气体从设置在非显示区域中的线之间的绝缘层排出到像素。因此,与非显示区域邻近的像素可能劣化,并且可能出现像素的像素收缩缺陷。

6.在本背景技术部分中公开的以上信息仅用于理解本公开的背景,并且因此可能包含不构成现有技术的信息。

技术实现要素:

7.一些示例实施例提供了一种能够防止像素收缩缺陷的显示装置。

8.根据示例实施例的显示装置可以包括:像素部件,包括多个像素并且被设置在显示区域中;解复用电路部件,被设置在围绕显示区域的非显示区域中,并且被配置为将数据电压传送到像素部件;以及连接图案,被设置在非显示区域中,被配置为将恒定电压传送到像素部件,并且包括与解复用电路部件重叠的第一部分和被设置在第一部分与像素部件之间的第二部分。垂直贯穿第一部分的多个第一贯穿孔可以形成在第一部分中,并且垂直贯穿第二部分的多个第二贯穿孔可以形成在第二部分中。

9.根据示例实施例,从第一部分突出的第二部分可以包括第二贯穿孔和彼此间隔开的突出部分。

10.根据示例实施例,多个第二贯穿孔中的每个第二贯穿孔的面积可以大于多个第一贯穿孔中的每个第一贯穿孔的面积。

11.根据示例实施例,显示装置可以进一步包括设置在连接图案的第一部分之下的第一有机绝缘层以及设置在连接图案与第一有机绝缘层之间的第二有机绝缘层。多个第二贯穿孔中的每个第二贯穿孔可以暴露第二有机绝缘层的上表面和第二有机绝缘层的侧表面。

12.根据示例实施例,突出部分可以覆盖第二有机绝缘层的上表面和第二有机绝缘层的侧表面。

13.根据示例实施例,第一有机绝缘层可以接触第二有机绝缘层。

14.根据示例实施例,多个像素中的每个像素可以包括晶体管基板以及被设置在晶体管基板上的发射结构。晶体管基板可以包括基底基板、设置在基底基板上的有源图案、设置在有源图案上并且连接到有源图案的第一连接电极、设置在第一连接电极上并且连接到第一连接电极的第二连接电极。发射结构可以包括第一电极、在其中形成有暴露第一电极的上表面的开口的像素限定层、设置在第一电极上的发射层以及设置在发射层上的第二电极。连接图案可以与第一电极设置在同一层中。

15.根据示例实施例,晶体管基板可以进一步包括设置在第一连接电极上、包括有机材料并且覆盖第一连接电极的第一平坦化层以及设置在第一平坦化层上、包括有机材料并且覆盖第二连接电极的第二平坦化层。第一有机绝缘层可以与第一平坦化层设置在同一层中,并且第二有机绝缘层可以与第二平坦化层设置在同一层中。

16.根据示例实施例,显示装置可以进一步包括设置在突出部分之下并且与突出部分重叠的连接线。连接线可以包括与第一连接电极设置在同一层中的第一连接线以及设置在第一连接线上并且与第一连接线接触的第二连接线。

17.根据示例实施例,第二部分可以具有矩形形状,并且多个第二贯穿孔中的每个第二贯穿孔的面积可以等于多个第一贯穿孔中的每个第一贯穿孔的面积。

18.根据示例实施例,显示装置可以进一步包括设置在连接图案的第一部分之下的第一有机绝缘层以及设置在连接图案与第一有机绝缘层之间的第二有机绝缘层。多个第二贯穿孔中的每个第二贯穿孔可以暴露第二有机绝缘层的上表面或第二有机绝缘层的侧表面。

19.根据示例实施例,第一有机绝缘层可以接触第二有机绝缘层。

20.根据示例实施例,第二部分可以具有矩形形状,并且多个第二贯穿孔中的每个第二贯穿孔的面积可以大于多个第一贯穿孔中的每个第一贯穿孔的面积。

21.根据示例实施例,显示装置可以进一步包括设置在连接图案的第一部分之下的第一有机绝缘层以及设置在连接图案与第一有机绝缘层之间的第二有机绝缘层。多个第二贯穿孔中的每个第二贯穿孔可以暴露第二有机绝缘层的上表面和第二有机绝缘层的侧表面。

22.根据示例实施例,第一部分可以具有矩形形状。

23.根据示例实施例,恒定电压可以是初始化电压。

24.根据示例实施例,恒定电压可以是高电力电压。

25.根据示例实施例,恒定电压可以是低电力电压。

26.因此,根据示例实施例的显示装置可以包括像素部件以及将恒定电压传输到像素部件的连接图案。垂直贯穿连接图案的多个贯穿孔可以形成在连接图案中。例如,贯穿孔可以形成在与像素部件邻近的连接图案中。贯穿孔可以暴露设置在连接图案之下的有机绝缘层的上表面和侧表面。因此,从有机绝缘层排出的气体可以在与有机绝缘层垂直的方向上被排出。换句话说,从有机绝缘层排出的气体可以不被排出到像素部件。因此,与连接图案邻近的像素可以不劣化,并且可以防止像素的像素收缩缺陷。

27.应理解,前述概括描述和下面的详细描述两者是示例和说明性的,并且旨在提供所要求保护的本公开的进一步说明。

附图说明

28.被包括以提供本公开的进一步理解并且被并入本说明书中且构成本说明书的一

部分的附图图示本公开的示例实施例,并且与描述一起用来解释本公开。

29.图1是图示根据示例实施例的显示装置的框图。

30.图2是图示根据示例实施例的显示装置的平面图。

31.图3是图示图2的显示装置中包括的像素的电路图。

32.图4是图示图2的显示装置中包括的像素的截面图。

33.图5是图示图2的显示装置的解复用电路部件中包括的解复用器的电路图。

34.图6是图示图5的解复用器的布局图。

35.图7是沿图2的线i-i'截取的截面图。

36.图8是沿图2的线ii-ii'截取的截面图。

37.图9是图示根据另一示例实施例的显示装置的平面图。

38.图10是沿图9的线iii-iii'截取的截面图。

39.图11是沿图9的线iv-iv'截取的截面图。

40.图12是图示根据又一示例实施例的显示装置的平面图。

41.图13是沿图12的线v-v'截取的截面图。

42.图14是沿图12的线vi-vi'截取的截面图。

具体实施方式

43.从下面结合附图的详细描述,将更清楚地理解例示性的、非限制性的示例实施例。

44.图1是图示根据示例实施例的显示装置的框图。

45.参考图1,根据示例实施例的显示装置dd可以包括像素部件pxp、数据驱动器ddv、解复用电路部件dcp、栅驱动器gdv、发射驱动器edv、控制器con和电力提供器ppv。

46.像素部件pxp可以包括多个像素px。像素px可以沿第一方向d1布置,并且可以沿与第一方向d1交叉的第二方向d2布置。例如,像素部件pxp可以包括沿第一方向d1并排布置的第一像素px1和第二像素px2。

47.另外,多条栅线、多条发射控制线、多条数据线、多条高电力电压线和多条初始化电压线可以被设置在像素部件pxp中。例如,在第一方向d1上延伸的栅线gl、在第一方向d1上延伸的发射控制线eml以及在第二方向d2上延伸的数据线dl1和dl2可以被设置在像素部件pxp中。例如,栅线gl可以电连接到第一像素px1和第二像素px2,并且发射控制线eml可以电连接到第一像素px1和第二像素px2。第一数据线dl1可以电连接到第一像素px1,并且第二数据线dl2可以电连接到第二像素px2。

48.数据驱动器ddv可以基于输出图像数据odat和数据控制信号dctrl产生数据电压data(如图3中所示)。另外,数据驱动器ddv可以通过第一数据传输线dtl1将数据电压data输出到解复用电路部件dcp。例如,数据驱动器ddv可以产生与输出图像数据odat相对应的数据电压data,并且可以响应于数据控制信号dctrl输出数据电压data。数据控制信号dctrl可以包括输出数据使能信号、水平开始信号和负载信号。例如,数据驱动器ddv可以用一个或多个集成电路(“ic”)实现。

49.解复用电路部件dcp可以将数据电压data传输到像素部件pxp。例如,解复用电路部件dcp可以对数据电压data进行时分并且可以传输数据电压data。在示例实施例中,解复用电路部件dcp可以包括多个解复用器dmp。例如,解复用器dmp可以接收第一数据电压和第

二数据电压。解复用器dmp可以分别将第一数据电压和第二数据电压顺序地传送到第一数据线dl1和第二数据线dl2。

50.栅驱动器gdv可以基于栅控制信号gctrl产生栅信号gs(如图3中所示)。例如,栅信号gs可以包括第一栅信号gw(如图3中所示)、第二栅信号gc(如图3中所示)和第三栅信号gb(如图3中所示)。第一栅信号gw、第二栅信号gc和第三栅信号gb中的每个可以包括用于使晶体管导通的栅导通电压以及用于使晶体管截止的栅截止电压。栅控制信号gctrl可以包括垂直开始信号和时钟信号等。例如,栅驱动器gdv可以集成在像素部件pxp的外围部分中。

51.发射驱动器edv可以基于发射控制信号ectrl产生发射驱动信号em(如图3中所示)。发射驱动信号em可以包括栅导通电压和栅截止电压。发射驱动信号em可以包括垂直开始信号和时钟信号等。例如,发射驱动器edv可以集成在像素部件pxp的外围部分中。

52.控制器con(例如,时序控制器t-con)可以从外部主机处理器(例如,gpu)接收输入图像数据idat和控制信号ctrl。例如,输入图像数据idat可以是包括红色图像数据、绿色图像数据和蓝色图像数据的rgb数据。控制信号ctrl可以包括垂直同步信号、水平同步信号、输入数据使能信号和主时钟信号等。控制器con可以基于输入图像数据idat和控制信号ctrl产生发射控制信号ectrl、栅控制信号gctrl、数据控制信号dctrl和输出图像数据odat。

53.电力提供器ppv可以将恒定电压提供到像素部件pxp。例如,恒定电压可以包括初始化电压vint、高电力电压elvdd和低电力电压elvss等。

54.图2是图示根据示例实施例的显示装置的平面图。

55.参考图1和图2,根据示例实施例的显示装置dd1可以包括显示区域da以及围绕显示区域da的非显示区域nda。像素部件pxp可以被设置在显示区域da中。栅驱动器gdv、发射驱动器edv、解复用电路部件dcp、数据驱动器ddv、电力提供器ppv和连接图案可以被设置在非显示区域nda中。例如,连接图案可以包括第一连接图案1000、第二连接图案2000和第三连接图案3000。

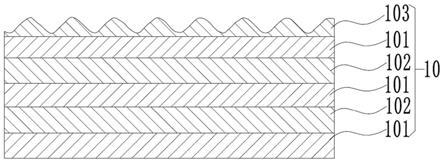

56.在示例实施例中,像素部件pxp可以具有矩形形状。栅驱动器gdv可以与矩形形状的第一短边邻近,并且发射驱动器edv可以与矩形形状的第二短边邻近。

57.在示例实施例中,数据驱动器ddv可以与矩形形状的长边邻近。解复用电路部件dcp可以被设置在像素部件pxp与数据驱动器ddv之间。解复用电路部件dcp可以从数据驱动器ddv接收数据电压data,并且可以将数据电压data传输到像素部件pxp。

58.在示例实施例中,电力提供器ppv可以与矩形形状的长边邻近。例如,数据驱动器ddv可以被设置在像素部件pxp与电力提供器ppv之间。第一连接图案1000、第二连接图案2000和第三连接图案3000可以被设置在像素部件pxp与电力提供器ppv之间。

59.在示例实施例中,第一连接图案1000可以被设置在第二连接图案2000与第三连接图案3000之间。第二连接图案2000可以被设置成与第一连接图案1000的左侧邻近,并且第三连接图案3000可以被设置成与第一连接图案1000的右侧邻近。另外,第一连接图案1000可以被设置成比第二连接图案2000和第三连接图案3000更靠近像素部件pxp。然而,第一连接图案1000、第二连接图案2000和第三连接图案3000的布置结构不限于以上。例如,第二连接图案2000可以被设置成比第一连接图案1000和第三连接图案3000更靠近像素部件pxp,或者第三连接图案3000可以被设置成比第一连接图案1000和第二连接图案2000更靠近像

素部件pxp。

60.在示例实施例中,第一连接图案1000、第二连接图案2000和第三连接图案3000中的每个可以从电力提供器ppv接收恒定电压,并且可以将恒定电压传输到像素部件pxp。例如,第一连接图案1000可以从电力提供器ppv接收第一恒定电压,并且可以将第一恒定电压传输到像素部件pxp。第二连接图案2000可以从电力提供器ppv接收第二恒定电压,并且可以将第二恒定电压传输到像素部件pxp。第三连接图案3000可以从电力提供器ppv接收第三恒定电压,并且可以将第三恒定电压传输到像素部件pxp。例如,第一恒定电压可以是初始化电压vint,第二恒定电压可以是高电力电压elvdd,并且第三恒定电压可以是低电力电压elvss。但是,第一恒定电压、第二恒定电压和第三恒定电压不限于以上描述的那些。

61.在示例实施例中,第一连接图案1000、第二连接图案2000和第三连接图案3000可以被设置在解复用电路部件dcp上。例如,第一连接图案1000、第二连接图案2000和第三连接图案3000可以与解复用电路部件dcp重叠,并且可以覆盖解复用电路部件dcp。例如,解复用电路部件dcp可以由解复用有源图案、设置在解复用有源图案上的第一金属层以及设置在第一金属层上的第二金属层形成,并且第一连接图案1000、第二连接图案2000和第三连接图案3000可以由设置在第二金属层上的第三金属层形成。解复用电路部件dcp可以由覆盖解复用电路部件dcp的第一至第三连接图案1000、2000和3000保护。例如,由于被提供有第一恒定电压的第一连接图案1000与解复用电路部件dcp重叠,因此第一连接图案1000可以保护解复用电路部件dcp免受解复用电路部件dcp周围产生的静电的影响。

62.在示例实施例中,第一连接图案1000可以包括第一部分100和第二部分200。第一部分100可以与解复用电路部件dcp重叠。第二部分200可以被设置在第一部分100与像素部件pxp之间。例如,第二部分200可以从第一部分100朝向像素部件pxp延伸。

63.在示例实施例中,包括有机材料的有机绝缘层可以被设置在解复用电路部件dcp上,并且第一连接图案1000可以被设置在有机绝缘层上。沿厚度方向(第三方向d3)垂直贯穿第一部分100的多个第一贯穿孔10可以形成在第一部分100中。第一贯穿孔10可以暴露有机绝缘层的上表面。另外,垂直贯穿第二部分200的多个第二贯穿孔20可以形成在第二部分200中。因此,第二部分200可以沿第二方向d2从第一部分100突出,以形成多个突出部分30,并且第二部分200的突出部分30可以沿第一方向d1彼此间隔开。第二贯穿孔20中的每个的面积可以大于第一贯穿孔10中的每个的面积。

64.在示例实施例中,第二贯穿孔20中的每个可以暴露有机绝缘层的上表面和有机绝缘层的侧表面。另外,突出部分30中的每个可以覆盖有机绝缘层的上表面和有机绝缘层的侧表面。将参考图7和图8描述第一贯穿孔10、第二贯穿孔20和突出部分30。

65.显示装置dd1可以包括在其中形成有第一贯穿孔10和第二贯穿孔20的第一连接图案1000。设置在第一连接图案1000之下的有机绝缘层的脱气可以通过第一贯穿孔10和第二贯穿孔20平稳地执行。例如,显示装置dd1可以包括在其中形成有第二贯穿孔20的第二部分200。因此,从有机绝缘层排出的气体可以在与有机绝缘层垂直的方向上被排出。换句话说,从有机绝缘层排出的气体可以不被排出到像素部件pxp。因此,与第二部分200邻近的像素px(例如,设置在图2中所示的区域a中的像素)可以不劣化,并且可以防止像素收缩缺陷。

66.图3是图示图2的显示装置中包括的像素的电路图。图4是图示图2的显示装置中包括的像素的截面图。

67.参考图2和图3,像素px可以包括像素电路pc和至少一个有机发光二极管oled。像素电路pc可以将驱动电流提供到有机发光二极管oled。

68.在示例实施例中,像素电路pc可以包括多个晶体管和至少一个存储电容器。例如,像素电路pc可以包括第一晶体管t1、第二晶体管t2、第三晶体管t3、第四晶体管t4、第五晶体管t5、第六晶体管t6、第七晶体管t7和存储电容器cst。第一晶体管t1可以被称为驱动晶体管,第二晶体管t2可以被称为开关晶体管,第三晶体管t3可以被称为补偿晶体管,第四晶体管t4可以被称为初始化晶体管,第五晶体管t5和第六晶体管t6可以被称为发射控制晶体管,并且第七晶体管t7可以被称为阳极初始化晶体管。

69.第一晶体管t1可以包括栅端子、第一端子(例如,源端子)和第二端子(例如,漏端子)。第一晶体管t1的栅端子可以连接到存储电容器cst。第一晶体管t1的第一端子可以接收高电力电压elvdd。第一晶体管t1的第二端子可以连接到第六晶体管t6。第一晶体管t1可以基于高电力电压elvdd和数据电压data产生驱动电流。

70.第二晶体管t2可以包括栅端子、第一端子(例如,源端子)和第二端子(例如,漏端子)。第二晶体管t2的栅端子可以通过栅线gl(如图1中所示)接收第一栅信号gw。第二晶体管t2的第一端子可以接收数据电压data。第二晶体管t2的第二端子可以将数据电压data提供到第一晶体管t1。

71.第二晶体管t2可以响应于第一栅信号gw被导通或截止。例如,当第二晶体管t2是pmos晶体管时,第二晶体管t2可以在第一栅信号gw具有正电压电平时被截止,并且可以在第一栅信号gw具有负电压电平时被导通。

72.第三晶体管t3可以包括栅端子、第一端子(例如,源端子)和第二端子(例如,漏端子)。第三晶体管t3的栅端子可以接收第一栅信号gw。第三晶体管t3的第一端子可以连接到第一晶体管t1的第二端子,并且第三晶体管t3的第二端子可以连接到第一晶体管t1的栅端子。

73.第三晶体管t3可以响应于第一栅信号gw被导通或截止。例如,当第三晶体管t3是pmos晶体管时,第三晶体管t3可以在第一栅信号gw具有负电压电平时被导通,并且可以在第一栅信号gw具有正电压电平时被截止。在第三晶体管t3响应于第一栅信号gw被导通的时段期间,第三晶体管t3可以将第一晶体管t1二极管连接。因此,第三晶体管t3可以补偿第一晶体管t1的阈值电压。

74.第四晶体管t4可以包括栅端子、第一端子(例如,源端子)和第二端子(例如,漏端子)。第四晶体管t4的栅端子可以接收第二栅信号gc。第四晶体管t4可以将初始化电压vint传输到第一晶体管t1的栅端子。

75.第四晶体管t4可以响应于第二栅信号gc被导通或截止。例如,当第四晶体管t4是pmos晶体管时,第四晶体管t4可以在第二栅信号gc具有负电压电平时被导通,并且可以在第二栅信号gc具有正电压电平时被截止。

76.当第四晶体管t4响应于第二栅信号gc被导通时,初始化电压vint可以被提供到第一晶体管t1的栅端子。因此,第一晶体管t1的栅端子可以被初始化为初始化电压vint。

77.第五晶体管t5可以包括栅端子、第一端子(例如,源端子)和第二端子(例如,漏端子)。第五晶体管t5的栅端子可以接收发射驱动信号em。第五晶体管t5的第一端子可以接收高电力电压elvdd。第五晶体管t5的第二端子可以连接到第一晶体管t1。当第五晶体管t5响

应于发射驱动信号em被导通时,第五晶体管t5可以将高电力电压elvdd提供到第一晶体管t1。

78.第六晶体管t6可以包括栅端子、第一端子(例如,源端子)和第二端子(例如,漏端子)。第六晶体管t6的栅端子可以接收发射驱动信号em。第六晶体管t6的第一端子可以连接到第一晶体管t1。第六晶体管t6的第二端子可以连接到有机发光二极管oled。当第六晶体管t6响应于发射驱动信号em被导通时,第六晶体管t6可以将驱动电流提供到有机发光二极管oled。

79.第七晶体管t7可以包括栅端子、第一端子(例如,源端子)和第二端子(例如,漏端子)。第七晶体管t7的栅端子可以接收第三栅信号gb。第七晶体管t7的第二端子可以接收初始化电压vint。第七晶体管t7的第一端子可以连接到有机发光二极管oled。当第七晶体管t7响应于第三栅信号gb被导通时,第七晶体管t7可以将初始化电压vint提供到有机发光二极管oled。因此,第七晶体管t7可以将有机发光二极管oled的第一端子初始化为初始化电压vint。

80.存储电容器cst可以包括第一端子和第二端子。存储电容器cst的第一端子可以连接到第一晶体管t1,并且存储电容器cst的第二端子可以接收高电力电压elvdd。存储电容器cst可以在第一栅信号gw的非激活时段期间保持第一晶体管t1的栅端子的电压电平。

81.有机发光二极管oled可以包括第一端子(例如,阳极端子)和第二端子(例如,阴极端子)。有机发光二极管oled的第一端子可以接收驱动电流,并且第二端子可以接收低电力电压elvss。有机发光二极管oled可以产生具有与驱动电流相对应的亮度的光。

82.同时,图3中所示的像素电路pc与有机发光二极管oled之间的连接结构是示例,并且可以被各种改变。

83.参考图2和图4,像素px可以包括晶体管基板t-sub以及设置在晶体管基板t-sub上的发射结构les。

84.晶体管基板t-sub可以包括基底基板sub、缓冲层bfr、有源图案act、第一栅绝缘层gi1、栅电极gat、第二栅绝缘层gi2、存储电容器电极cste、层间绝缘层ild、第一连接电极bce1、第二连接电极bce2、第一平坦化层bvin、第三连接电极tce和第二平坦化层tvin。

85.发射结构les可以包括第一电极ade、像素限定层pdl、发射层el和第二电极cte。

86.基底基板sub可以包括玻璃、石英或塑料等。在示例实施例中,当显示装置dd1是刚性显示装置时,基底基板sub可以包括玻璃。在另一示例实施例中,当显示装置dd1是柔性显示装置时,基底基板sub可以包括塑料。

87.缓冲层bfr可以被设置在基底基板sub上。缓冲层bfr可以包括无机材料。缓冲层bfr可以防止杂质扩散到有源图案act中,并且有源图案act可以均匀地形成。

88.有源图案act可以被设置在缓冲层bfr上。有源图案act可以包括非晶硅半导体、多晶硅半导体或氧化物半导体等。有源图案act可以被部分地掺杂,并且因此可以具有导电性。

89.第一栅绝缘层gi1可以被设置在有源图案act上。第一栅绝缘层gi1可以覆盖有源图案act。在示例实施例中,第一栅绝缘层gi1可以包括无机材料。例如,第一栅绝缘层gi1可以包括氧化硅(“sio

x”)或氮化硅(“sin

x”)等。

90.栅电极gat可以被设置在第一栅绝缘层gi1上。栅电极gat可以与有源图案act重

叠。在示例实施例中,栅电极gat可以包括金属、合金、导电金属氧化物或透明导电材料等。例如,栅电极gat可以包括银(“ag”)、包含银的合金、钼(“mo”)、包含钼的合金、铝(“al”)、包含铝的合金、氮化铝(“aln”)、钨(“w”)、氮化钨(“wn”)、铜(“cu”)、镍(“ni”)、铬(“cr”)、氮化铬(“crn”)、钛(“ti”)、钽(“ta”)、铂(“pt”)、钪(“sc”)、氧化铟锡(“ito”)或氧化铟锌(“izo”)等。

91.第二栅绝缘层gi2可以被设置在栅电极gat上。第二栅绝缘层gi2可以覆盖栅电极gat。在示例实施例中,第二栅绝缘层gi2可以包括无机材料。

92.存储电容器电极cste可以被设置在第二栅绝缘层gi2上。存储电容器电极cste可以与栅电极gat重叠。存储电容器电极cste可以与栅电极gat一起构成存储电容器cst。在示例实施例中,存储电容器电极cste可以包括金属、合金、导电金属氧化物或透明导电材料等。

93.层间绝缘层ild可以被设置在存储电容器电极cste上。层间绝缘层ild可以覆盖存储电容器电极cste。在示例实施例中,层间绝缘层ild可以包括无机材料。

94.第一连接电极bce1和第二连接电极bce2可以被设置在层间绝缘层ild上。第一连接电极bce1和第二连接电极bce2可以分别通过接触孔接触有源图案act。在示例实施例中,第一连接电极bce1和第二连接电极bce2可以包括金属、合金、导电金属氧化物或透明导电材料等。例如,第一连接电极bce1和第二连接电极bce2可以包括银(“ag”)、包含银的合金、钼(“mo”)、包含钼的合金、铝(“al”)、包含铝的合金、氮化铝(“aln”)、钨(“w”)、氮化钨(“wn”)、铜(“cu”)、镍(“ni”)、铬(“cr”)、氮化铬(“crn”)、钛(“ti”)、钽(“ta”)、铂(“pt”)、钪(“sc”)、氧化铟锡(“ito”)或氧化铟锌(“izo”)等。

95.第一平坦化层bvin可以被设置在层间绝缘层ild上。第一平坦化层bvin可以覆盖第一连接电极bce1和第二连接电极bce2。在示例实施例中,第一平坦化层bvin可以包括有机材料。例如,第一平坦化层bvin可以包括光刻胶、聚丙烯酸树脂、聚酰亚胺树脂、丙烯酸树脂等。

96.第三连接电极tce可以被设置在第一平坦化层bvin上。第三连接电极tce可以通过接触孔接触第一连接电极bce1。第三连接电极tce可以包括金属、合金、导电金属氧化物或透明导电材料等。然而,第三连接电极tce可以不接触第二连接电极bce2。

97.第二平坦化层tvin可以被设置在第一平坦化层bvin上。第二平坦化层tvin可以覆盖第三连接电极tce。在示例实施例中,第二平坦化层tvin可以包括有机材料。

98.发射结构les可以对应于有机发光二极管oled。

99.第一电极ade可以被设置在第二平坦化层tvin上。第一电极ade可以通过接触孔接触第三连接电极tce。在示例实施例中,第一电极ade可以包括金属、合金或导电金属氧化物等。例如,第一电极ade可以包括金(“au”)、银(“ag”)、铜(“cu”)、镍(“ni”)、铬(“cr”)、铝(“al”)、钨(“w”)、钼(“mo”)、钛(“ti”)、钽(“ta”)、氧化铟锡(“ito”)、氧化铟锌(“izo”)或其合金。

100.像素限定层pdl可以被设置在第二平坦化层tvin上。暴露第一电极ade的上表面的开口可以形成在像素限定层pdl中。暴露第二电极cte的底表面的开口可以形成在像素限定层pdl中。第二电极cte与第一电极ade重叠,并且第一电极ade与有源图案act、栅电极gat和存储电容器电极cste重叠。

101.发射层el可以被设置在第一电极ade上。发射层el可以位于形成在像素限定层pdl中的开口中。发射层el被设置在第一电极ade与第二电极cte之间,并且可以发光。

102.第二电极cte可以被设置在发射层el上。第二电极cte可以包括金属、合金或导电金属氧化物。例如,第二电极cte可以包括金(“au”)、银(“ag”)、铜(“cu”)、镍(“ni”)、铬(“cr”)、铝(“al”)、钨(“w”)、钼(“mo”)、钛(“ti”)、钽(“ta”)、氧化铟锡(“ito”)、氧化铟锌(“izo”)或其合金。

103.图5是图示图2的显示装置的解复用电路部件中包括的解复用器的电路图。图6是图示图5的解复用器的布局图。

104.参考图1、图2和图5,解复用器dmp可以包括第一解复用晶体管dt1和第二解复用晶体管dt2。解复用器dmp可以将数据电压data顺序地传输到第一数据线dl1和第二数据线dl2。

105.第一解复用晶体管dt1可以包括栅端子、第一端子(例如,源端子)和第二端子(例如,漏端子)。第一解复用晶体管dt1的栅端子可以连接到第一解复用栅线dcl1。第一解复用晶体管dt1的第一端子可以连接到第一数据传输线dtl1。第一解复用晶体管dt1的第二端子可以连接到第一数据线dl1。第一解复用晶体管dt1可以响应于从第一解复用栅线dcl1提供的第一解复用栅信号被导通或截止。当第一解复用晶体管dt1被导通时,数据电压data可以从第一数据传输线dtl1传送到第一数据线dl1。

106.第二解复用晶体管dt2可以包括栅端子、第一端子(例如,源端子)和第二端子(例如,漏端子)。第二解复用晶体管dt2的栅端子可以连接到第二解复用栅线dcl2。第二解复用晶体管dt2的第一端子可以连接到第一数据传输线dtl1。第二解复用晶体管dt2的第二端子可以连接到第二数据线dl2。第二解复用晶体管dt2可以响应于从第二解复用栅线dcl2提供的第二解复用栅信号被导通或截止。当第二解复用晶体管dt2被导通时,数据电压data可以从第一数据传输线dtl1传送到第二数据线dl2。

107.随着第一解复用晶体管dt1和第二解复用晶体管dt2被顺序地导通,第一数据传输线dtl1的数据电压data可以被顺序地传输到数据线dl1和dl2。

108.参考图1、图2和图6,解复用器dmp可以包括解复用有源图案dact、第一解复用栅电极dgat1、第二解复用栅电极dgat2、第一解复用连接电极dce1、第二解复用连接电极dce2和第三解复用连接电极dce3。

109.解复用有源图案dact可以与有源图案act(如图4中所示)设置在同一层中。解复用有源图案dact可以接触第一解复用连接电极dce1、第二解复用连接电极dce2和第三解复用连接电极dce3。

110.第一解复用栅电极dgat1可以被设置在解复用有源图案dact上。第一解复用栅电极dgat1可以与栅电极gat(如图4中所示)设置在同一层中。第一解复用栅电极dgat1可以连接到第一解复用栅线dcl1。第一解复用栅信号可以通过第一解复用栅线dcl1被提供到第一解复用栅电极dgat1。

111.第二解复用栅电极dgat2可以被设置在解复用有源图案dact上。第二解复用栅电极dgat2可以与第一解复用栅电极dgat1设置在同一层中。第二解复用栅电极dgat2可以连接到第二解复用栅线dcl2。第二解复用栅信号可以通过第二解复用栅线dcl2被提供到第二解复用栅电极dgat2。

112.第一解复用连接电极dce1可以被设置在解复用有源图案dact上。第一解复用连接电极dce1可以与第一连接电极bce1(如图4中所示)设置在同一层中。第一解复用连接电极dce1可以从解复用有源图案dact接收数据电压data。另外,第一解复用连接电极dce1可以连接到第一数据线dl1。第一解复用连接电极dce1可以将数据电压data提供到第一数据线dl1。

113.第二解复用连接电极dce2可以被设置在解复用有源图案dact上。第二解复用连接电极dce2可以与第一解复用连接电极dce1设置在同一层中。第二解复用连接电极dce2可以从解复用有源图案dact接收数据电压data。另外,第二解复用连接电极dce2可以连接到第二数据线dl2。第二解复用连接电极dce2可以将数据电压data提供到第二数据线dl2。

114.第三解复用连接电极dce3可以被设置在解复用有源图案dact上。第三解复用连接电极dce3可以与第一解复用连接电极dce1和第二解复用连接电极dce2设置在同一层中。第三解复用连接电极dce3可以从第一数据传输线dtl1接收数据电压data。另外,第三解复用连接电极dce3可以连接到解复用有源图案dact。第三解复用连接电极dce3可以通过解复用有源图案dact提供数据电压data。

115.图7是沿图2的线i-i'截取的截面图。图8是沿图2的线ii-ii'截取的截面图。

116.参考图2和图7,显示装置dd1可以包括基底基板sub、缓冲层bfr、第一栅绝缘层gi1、第二栅绝缘层gi2、层间绝缘层ild、第一连接线cl1、第二连接线cl2、第一有机绝缘层bvia、第二有机绝缘层tvia、第一部分100、突出部分30以及像素限定层pdl。

117.第一连接线cl1可以电连接到电力提供器ppv。第一连接线cl1可以将恒定电压从电力提供器ppv传输到第一部分100。

118.第一连接线cl1可以包括第一下连接线bcl1和第一上连接线tcl1。第一下连接线bcl1和第一上连接线tcl1可以彼此接触。第一下连接线bcl1可以与第一连接电极bce1(如图4中所示)设置在同一层中,并且第一上连接线tcl1可以与第三连接电极tce(如图4中所示)设置在同一层中。

119.第二连接线cl2可以电连接到像素部件pxp。例如,第二连接线cl2可以被设置在突出部分30之下,并且可以与突出部分30重叠。第二连接线cl2可以将恒定电压从突出部分30传输到像素部件pxp。

120.第二连接线cl2可以包括第二下连接线bcl2和第二上连接线tcl2。第二下连接线bcl2和第二上连接线tcl2可以彼此接触。第二下连接线bcl2可以与第一连接电极bce1(如图4中所示)设置在同一层中,并且第二上连接线tcl2可以与第三连接电极tce(如图4中所示)设置在同一层中。

121.第一有机绝缘层bvia可以与第一平坦化层bvin(如图4中所示)设置在同一层中,并且可以包括有机材料。第二有机绝缘层tvia可以接触第一有机绝缘层bvia,可以与第二平坦化层tvin(如图4中所示)设置在同一层中,并且可以包括有机材料。因此,被设置在第二有机绝缘层tvia上的第一连接图案1000和第二连接图案2000可以与被设置在第二平坦化层tvin上的第一电极ade设置在同一层中。第一有机绝缘层bvia和第二有机绝缘层tvia可以使解复用电路部件dcp和第一连接图案1000电绝缘。

122.第一部分100可以接触第一连接线cl1,并且可以与解复用电路部件dcp重叠。例如,与解复用电路部件dcp重叠的区域可以被定义为重叠区域dma。换句话说,第一部分100

可以与重叠区域dma重叠。

123.突出部分30可以从第一部分100延伸,并且可以接触第二连接线cl2。突出部分30可以与重叠区域dma不重叠。另外,突出部分30可以覆盖第二有机绝缘层tvia的上表面和第二有机绝缘层tvia的侧表面。因此,突出部分30可以电连接第一部分100和第二连接线cl2。恒定电压可以通过第一连接线cl1、第一部分100、突出部分30和第二连接线cl2传输到像素部件pxp。

124.像素限定层pdl可以覆盖第一部分100和突出部分30。

125.参考图2和图8,显示装置dd1可以包括基底基板sub、缓冲层bfr、第一栅绝缘层gi1、第二栅绝缘层gi2、层间绝缘层ild、第一连接线cl1、第一有机绝缘层bvia、第二有机绝缘层tvia、第一部分100和第二部分200。第一贯穿孔10可以形成在第一部分100中,并且第二贯穿孔20可以形成在第二部分200中。

126.第一贯穿孔10可以垂直贯穿第一部分100。第一贯穿孔10可以暴露第二有机绝缘层tvia的上表面。在第二有机绝缘层tvia中产生的气体可以通过第一贯穿孔10在与第二有机绝缘层tvia垂直的方向上被排出。

127.第二贯穿孔20可以垂直贯穿第二部分200。第二贯穿孔20可以暴露第二有机绝缘层tvia的上表面和第二有机绝缘层tvia的侧表面。因此,从第二有机绝缘层tvia产生的气体可以在与第二有机绝缘层tvia垂直的方向上被排出。换句话说,在第二有机绝缘层tvia中产生的气体可以不被排出到像素部件pxp。因此,与第二部分200邻近的像素px(例如,设置在图2中所示的区域a中的像素)可以不劣化,并且可以防止像素收缩缺陷。

128.图9是图示根据另一示例实施例的显示装置的平面图。图10是沿图9的线iii-iii'截取的截面图。图11是沿图9的线iv-iv'截取的截面图。

129.参考图9,根据另一示例实施例的显示装置dd2可以包括像素部件pxp、栅驱动器gdv、发射驱动器edv、解复用电路部件dcp、数据驱动器ddv、电力提供器ppv和连接图案。例如,连接图案可以包括第一连接图案1001、第二连接图案2000和第三连接图案3000。然而,显示装置dd2可以与参考图2描述的显示装置dd1基本相同,除了第一连接图案1001之外。在下文中,将描述第一连接图案1001。

130.在示例实施例中,第一连接图案1001可以被设置在第二连接图案2000与第三连接图案3000之间。第二连接图案2000可以被设置成与第一连接图案1001的左侧邻近,并且第三连接图案3000可以被设置成与第一连接图案1001的右侧邻近。另外,第一连接图案1001可以被设置成比第二连接图案2000和第三连接图案3000更靠近像素部件pxp。然而,第一至第三连接图案1001、2000和3000的布置结构不限于以上。例如,第二连接图案2000可以被设置成比第一连接图案1001和第三连接图案3000更靠近像素部件pxp,或者第三连接图案3000可以被设置成比第一连接图案1001和第二连接图案2000更靠近像素部件pxp。

131.在示例实施例中,第一连接图案1001、第二连接图案2000和第三连接图案3000中的每个可以从电力提供器ppv接收恒定电压,并且可以将恒定电压传输到像素部件pxp。例如,第一连接图案1001可以从电力提供器ppv接收第一恒定电压,并且可以将第一恒定电压传输到像素部件pxp。第二连接图案2000可以从电力提供器ppv接收第二恒定电压,并且可以将第二恒定电压传输到像素部件pxp。第三连接图案3000可以从电力提供器ppv接收第三恒定电压,并且可以将第三恒定电压传输到像素部件pxp。例如,第一恒定电压可以是初始

化电压vint,第二恒定电压可以是高电力电压elvdd,并且第三恒定电压可以是低电力电压elvss。但是,第一恒定电压、第二恒定电压和第三恒定电压不限于以上描述的那些。

132.在示例实施例中,第一连接图案1001、第二连接图案2000和第三连接图案3000可以被设置在解复用电路部件dcp上。例如,第一连接图案1001、第二连接图案2000和第三连接图案3000可以与解复用电路部件dcp重叠,并且可以覆盖解复用电路部件dcp。例如,解复用电路部件dcp可以由解复用有源图案、设置在解复用有源图案上的第一金属层以及设置在第一金属层上的第二金属层形成,并且第一连接图案1001、第二连接图案2000和第三连接图案3000可以由设置在第二金属层上的第三金属层形成。解复用电路部件dcp可以由覆盖解复用电路部件dcp的第一连接图案1001、第二连接图案2000和第三连接图案3000保护。例如,由于被提供有第一恒定电压的第一连接图案1001与解复用电路部件dcp重叠,因此第一连接图案1001可以保护解复用电路部件dcp免受解复用电路部件dcp周围产生的静电的影响。

133.在示例实施例中,第一连接图案1001可以包括第一部分100和第二部分201。第一部分100可以与解复用电路部件dcp重叠。第二部分201可以被设置在第一部分100与像素部件pxp之间。例如,第二部分201可以从第一部分100朝向像素部件pxp延伸。

134.在示例实施例中,包括有机材料的有机绝缘层可以被设置在解复用电路部件dcp上,并且第一连接图案1001可以被设置在有机绝缘层上。沿厚度方向(第三方向d3)垂直贯穿第一部分100的多个第一贯穿孔10可以形成在第一部分100中。第一贯穿孔10可以暴露有机绝缘层的上表面。另外,沿厚度方向(第三方向d3)垂直贯穿第二部分201的多个第二贯穿孔21可以形成在第二部分201中。第二贯穿孔21中的每个的面积可以等于第一贯穿孔10中的每个的面积。

135.在示例实施例中,第二贯穿孔21中的每个可以暴露有机绝缘层的上表面或有机绝缘层的侧表面。

136.显示装置dd2可以包括在其中形成有第一贯穿孔10和第二贯穿孔21的第一连接图案1001。设置在第一连接图案1001之下的有机绝缘层的脱气可以通过第一贯穿孔10和第二贯穿孔21平稳地执行。例如,显示装置dd2可以包括在其中形成有第二贯穿孔21的第二部分201。因此,从有机绝缘层排出的气体可以在与有机绝缘层垂直的方向上被排出。换句话说,从有机绝缘层排出的气体可以不被排出到像素部件pxp。因此,与第二部分201邻近的像素px(例如,布置在图9中所示的区域a中的像素)可以不劣化,并且可以防止像素收缩缺陷。

137.参考图9和图10,显示装置dd2可以包括基底基板sub、缓冲层bfr、第一栅绝缘层gi1、第二栅绝缘层gi2、层间绝缘层ild、第一连接线cl1、第二连接线cl2、第一有机绝缘层bvia、第二有机绝缘层tvia、第一部分100、第二部分201和像素限定层pdl。然而,基底基板sub、缓冲层bfr、第一栅绝缘层gi1、第二栅绝缘层gi2、层间绝缘层ild、第一连接线cl1、第一有机绝缘层bvia、第二有机绝缘层tvia、第一部分100和像素限定层pdl可以与以上描述的相同。在下文中,将描述第二连接线cl2和第二部分201。

138.第二连接线cl2可以电连接到像素部件pxp。例如,第二连接线cl2可以被设置在第二部分201之下,并且可以接触第二部分201。第二连接线cl2可以将恒定电压从第二部分201传输到像素部件pxp。

139.第一部分100可以延伸以接触第一连接线cl1。第二部分201可以从第一部分100延

伸,并且可以接触第二连接线cl2。第二部分201可以与重叠区域dma不重叠。另外,第二部分201可以覆盖第二有机绝缘层tvia的上表面和第二有机绝缘层tvia的侧表面。因此,第二部分201可以将第一部分100和第二连接线cl2彼此电连接。恒定电压可以通过第一连接线cl1、第一部分100、第二部分201和第二连接线cl2被提供到像素部件pxp。

140.参考图9和图11,显示装置dd2可以包括基底基板sub、缓冲层bfr、第一栅绝缘层gi1、第二栅绝缘层gi2、层间绝缘层ild、第一连接线cl1、第一有机绝缘层bvia、第二有机绝缘层tvia、第一部分100和第二部分201。第一贯穿孔10可以形成在第一部分100中,并且第二贯穿孔21可以形成在第二部分201中。

141.第一贯穿孔10可以垂直贯穿第一部分100。第一贯穿孔10可以暴露第二有机绝缘层tvia的上表面。在第二有机绝缘层tvia中产生的气体可以通过第一贯穿孔10在与第二有机绝缘层tvia垂直的方向上被排出。

142.第二贯穿孔21可以垂直贯穿第二部分201。第二贯穿孔21可以暴露第二有机绝缘层tvia的上表面或第二有机绝缘层tvia的侧表面。因此,在第二有机绝缘层tvia中产生的气体可以在与第二有机绝缘层tvia垂直的方向上被排出。换句话说,在第二有机绝缘层tvia中产生的气体可以不被排出到像素部件pxp。因此,与第二部分201邻近的像素px(例如,布置在图9中所示的区域a中的像素)可以不劣化,并且可以防止像素收缩缺陷。

143.图12是图示根据又一示例实施例的显示装置的平面图。图13是沿图12的线v-v'截取的截面图。图14是沿图12的线vi-vi'截取的截面图。

144.参考图12,根据又一示例实施例的显示装置dd3可以包括像素部件pxp、栅驱动器gdv、发射驱动器edv、解复用电路部件dcp、数据驱动器ddv、电力提供器ppv和连接图案。例如,连接图案可以包括第一连接图案1002、第二连接图案2000和第三连接图案3000。然而,显示装置dd3可以与参考图2描述的显示装置dd1基本相同,除了第一连接图案1002之外。在下文中,将描述第一连接图案1002。

145.在示例实施例中,第一连接图案1002可以被设置在第二连接图案2000与第三连接图案3000之间。第二连接图案2000可以被设置成与第一连接图案1002的左侧邻近,并且第三连接图案3000可以被设置成与第一连接图案1002的右侧邻近。另外,第一连接图案1002可以被设置成比第二连接图案2000和第三连接图案3000更靠近像素部件pxp。然而,第一至第三连接图案1002、2000和3000的布置结构不限于以上。例如,第二连接图案2000可以被设置成比第一连接图案1002和第三连接图案3000更靠近像素部件pxp,或者第三连接图案3000可以被设置成比第一连接图案1002和第二连接图案2000更靠近像素部件pxp。

146.在示例实施例中,第一至第三连接图案1002、2000和3000中的每个可以从电力提供器ppv接收恒定电压,并且可以将恒定电压传输到像素部件pxp。例如,第一连接图案1002可以从电力提供器ppv接收第一恒定电压,并且可以将第一恒定电压传输到像素部件pxp。第二连接图案2000可以从电力提供器ppv接收第二恒定电压,并且可以将第二恒定电压传输到像素部件pxp。第三连接图案3000可以从电力提供器ppv接收第三恒定电压,并且可以将第三恒定电压传输到像素部件pxp。例如,第一恒定电压可以是初始化电压vint,第二恒定电压可以是高电力电压elvdd,并且第三恒定电压可以是低电力电压elvss。但是,第一恒定电压、第二恒定电压和第三恒定电压不限于以上描述的那些。

147.在示例实施例中,第一连接图案1002、第二连接图案2000和第三连接图案3000可

以被设置在解复用电路部件dcp上。例如,第一连接图案1002、第二连接图案2000和第三连接图案3000可以与解复用电路部件dcp重叠,并且可以覆盖解复用电路部件dcp。例如,解复用电路部件dcp可以由解复用有源图案、设置在解复用有源图案上的第一金属层以及设置在第一金属层上的第二金属层形成,并且第一连接图案1002、第二连接图案2000和第三连接图案3000可以由设置在第二金属层上的第三金属层形成。解复用电路部件dcp可以由覆盖解复用电路部件dcp的第一至第三连接图案1002、2000和3000保护。例如,由于被提供有第一恒定电压的第一连接图案1002与解复用电路部件dcp重叠,因此第一连接图案1002可以保护解复用电路部件dcp免受解复用电路部件dcp周围产生的静电的影响。

148.在示例实施例中,第一连接图案1002可以包括第一部分100和第二部分202。第一部分100可以与解复用电路部件dcp重叠。第二部分202可以被设置在第一部分100与像素部件pxp之间。例如,第二部分202可以从第一部分100朝向像素部件pxp延伸。

149.在示例实施例中,包括有机材料的有机绝缘层可以被设置在解复用电路部件dcp上,并且第一连接图案1002可以被设置在有机绝缘层上。垂直贯穿第一部分100的第一贯穿孔10可以形成在第一部分100中。第一贯穿孔10可以暴露有机绝缘层的上表面。另外,垂直贯穿第二部分202的多个第二贯穿孔22可以形成在第二部分202中。第二贯穿孔22中的每个的面积可以大于第一贯穿孔10中的每个的面积。

150.在示例实施例中,第二贯穿孔22中的每个可以暴露有机绝缘层的上表面和有机绝缘层的侧表面。

151.显示装置dd3可以包括在其中形成有第一贯穿孔10和第二贯穿孔22的第一连接图案1002。设置在第一连接图案1002之下的有机绝缘层的脱气可以通过第一贯穿孔10和第二贯穿孔22平稳地执行。例如,显示装置dd3可以包括在其中形成有第二贯穿孔22的第二部分202。因此,从有机绝缘层排出的气体可以在与有机绝缘层垂直的方向上被排出。换句话说,从有机绝缘层排出的气体可以不被排出到像素部件pxp。因此,与第二部分202邻近的像素px(例如,设置在图12中所示的区域a中的像素)可以不劣化,并且可以防止像素收缩缺陷。

152.参考图12和图13,显示装置dd3可以包括基底基板sub、缓冲层bfr、第一栅绝缘层gi1、第二栅绝缘层gi2、层间绝缘层ild、第一连接线cl1、第二连接线cl2、第一有机绝缘层bvia、第二有机绝缘层tvia、第一部分100、第二部分202和像素限定层pdl。然而,基底基板sub、缓冲层bfr、第一栅绝缘层gi1、第二栅绝缘层gi2、层间绝缘层ild、第一连接线cl1、第一有机绝缘层bvia、第二有机绝缘层tvia、第一部分100和像素限定层pdl可以与以上描述的相同。在下文中,将描述第二连接线cl2和第二部分202。

153.第二连接线cl2可以电连接到像素部件pxp。例如,第二连接线cl2可以被设置在第二部分202之下,并且可以接触第二部分202。第二连接线cl2可以将恒定电压从第二部分202传输到像素部件pxp。

154.第一部分100可以延伸以接触第一连接线cl1。第二部分202可以从第一部分100延伸,并且可以接触第二连接线cl2。第二部分202可以与重叠区域dma不重叠。另外,第二部分202可以覆盖第二有机绝缘层tvia的上表面和第二有机绝缘层tvia的侧表面。因此,第二部分202可以电连接第一部分100和第二连接线cl2。恒定电压可以通过第一连接线cl1、第一部分100、第二部分202和第二连接线cl2被提供到像素部件pxp。

155.参考图12和图14,显示装置dd3可以包括基底基板sub、缓冲层bfr、第一栅绝缘层

gi1、第二栅绝缘层gi2、层间绝缘层ild、第一连接线cl1、第一有机绝缘层bvia、第二有机绝缘层tvia、第一部分100和第二部分202。第一贯穿孔10可以形成在第一部分100中,并且第二贯穿孔22可以形成在第二部分202中。

156.第一贯穿孔10可以垂直贯穿第一部分100。第一贯穿孔10可以暴露第二有机绝缘层tvia的上表面。在第二有机绝缘层tvia中产生的气体可以通过第一贯穿孔10在与第二有机绝缘层tvia垂直的方向上被排出。

157.第二贯穿孔22可以垂直贯穿第二部分202。第二贯穿孔22可以暴露第二有机绝缘层tvia的上表面和第二有机绝缘层tvia的侧表面。因此,在第二有机绝缘层tvia中产生的气体可以在与第二有机绝缘层tvia垂直的方向上被排出。换句话说,在第二有机绝缘层tvia中产生的气体可以不被排出到像素部件pxp。因此,与第二部分202邻近的像素px(例如,设置在图12中所示的区域a中的像素)可以不劣化,并且可以防止像素收缩缺陷。

158.根据示例实施例的显示装置可以包括像素部件以及将恒定电压传输到像素部件的第一连接图案。第一连接图案可以包括第一部分以及设置在第一部分与像素部件之间的第二部分。垂直贯穿第二部分的多个第二贯穿孔可以形成在第二部分中。第二贯穿孔可以暴露第二有机绝缘层的上表面和/或第二有机绝缘层的侧表面。因此,从第二有机绝缘层排出的气体可以在与第二有机绝缘层垂直的方向上被排出。换句话说,从第二有机绝缘层排出的气体可以不被排出到像素部件。因此,与第一连接图案邻近的像素可以不劣化,并且可以防止像素收缩缺陷。

159.另外,第一连接图案可以被设置在解复用电路部件上,并且可以与解复用电路部件重叠。解复用电路部件可以由覆盖解复用电路部件的第一连接图案保护。例如,由于被提供有恒定电压的第一连接图案与解复用电路部件重叠,因此第一连接图案可以保护解复用电路部件免受解复用电路部件周围产生的静电的影响。

160.尽管本文已经描述了本公开的特定的实施例和实施方式,但其它实施例和修改将从本描述中显而易见。因此,本公开不限于这样的实施例,而是受限于随附权利要求以及如对本领域普通技术人员将是显而易见的各种明显的修改和等同布置的更广泛的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。