半导体元件的制造方法及半导体元件

1.本发明是2018年3月27日所提出的申请号为201880089952.1、发明名称为《半导体元件的制造方法》的发明专利申请的分案申请。

技术领域

2.本发明涉及一种半导体元件的制造方法及半导体元件。

背景技术:

3.以往已知有一种将半导体磊晶层自母材基板拆下并移至其他基板的技术(例如参照专利文献1)。

4.现有技术文献

5.专利文献

6.专利文献1:日本专利第3813123号公报

技术实现要素:

7.发明所要解决的问题

8.图22是用以说明现有技术的图。图22示出了包括母材基板3001、牺牲层3002、半导体磊晶层3003、以及支撑体3004的半导体结构。牺牲层3002设置于半导体磊晶层3003与母材基板3001之间,且因蚀刻而变得小于半导体磊晶层3003。符号3010示出了牺牲层3002受到蚀刻的区域。

9.支撑体3004的水平方向的剖面与半导体磊晶层3003为同一形状,且设置于半导体磊晶层3003之上。支撑体3004是将半导体磊晶层3003自母材基板3001拆下时用以支撑半导体磊晶层3003的构件。在图22所示的现有技术中,通过利用蚀刻将牺牲层3002去除而将半导体磊晶层3003自母材基板3001上剥离。

10.在图22所示的现有技术中,半导体磊晶层3003及支撑体3004在牺牲层3002的蚀刻结束的时间点自母材基板3001剥离。因此存在如下课题:在牺牲层3002被完全蚀刻而母材基板3001与半导体磊晶层3003相离的时间点,需要将半导体磊晶层3003移动并载置于与母材基板3001不同的暂时位置。

11.因此,本发明是鉴于所述方面而成,其目的在于通过将半导体磊晶层接合于其他基板而使制造半导体元件的方法效率化。

12.解决问题的技术手段

13.本发明的第一实施方式的半导体元件的制造方法是将形成于第一基板的上方的半导体薄膜层自所述第一基板分离并接合于与所述第一基板不同的第二基板上的半导体元件的制造方法,且包括:形成作为薄膜的固定层的步骤,所述固定层将所述半导体薄膜层的与所述第一基板一侧为相反侧的主面的至少一部分与所述第一基板中的所述半导体薄膜层一侧的面的至少一部分结合;通过将所述半导体薄膜层或所述第一基板的一部分区域、或者所述半导体薄膜层与所述第一基板之间的层的一部分区域去除而形成空隙的步

骤;在形成所述空隙后,在所述半导体薄膜层的所述主面将形成于第三基板的有机材料层与所述固定层及所述半导体薄膜层的至少一部分结合区域结合的步骤;在所述有机材料层结合于所述结合区域的状态下将所述第三基板沿与所述第一基板相离的方向移动,由此将所述半导体薄膜层自所述第一基板分离的步骤;以及将自所述第一基板分离后的所述半导体薄膜层接合于所述第二基板的步骤。

14.所述制造方法可在将所述半导体薄膜层接合于所述第二基板的步骤后还包括:通过将所述有机材料层去除而将所述半导体薄膜层自所述第三基板分离的步骤。

15.在将所述半导体薄膜层自所述第三基板分离的步骤中,可通过溶解而将所述有机材料层去除。

16.在形成所述固定层的步骤中可形成如下厚度的所述固定层,即,通过移动所述第三基板的力而将形成于所述第一基板上的所述固定层与形成于所述半导体薄膜层的侧面的所述固定层之间切断的厚度。

17.在形成所述固定层的步骤中,可以在所述半导体薄膜层的所述主面上的第一方向上在所述半导体薄膜层的两端间延伸存在,且在与所述第一方向正交的第二方向上的所述半导体薄膜层的两侧面中的至少一部分区域中所述半导体薄膜层露出的方式形成所述固定层。

18.在形成所述固定层的步骤中,可以相较于在所述第一方向上延伸存在的所述固定层对所述半导体薄膜层中的所述第一方向上的两侧面的被覆率,在所述第二方向上延伸存在的所述固定层对所述半导体薄膜层中的所述第二方向上的两侧面的被覆率变小的方式形成所述固定层。

19.在形成所述固定层的步骤中,可以相较于所述半导体薄膜层的短边的侧面的被覆率,所述半导体薄膜层的长边的侧面的被覆率变小的方式形成所述固定层。

20.所述制造方法可包括:形成多个所述半导体薄膜层的岛的步骤,以及在形成所述固定层的步骤中,形成与多个所述岛对应的多个所述固定层的步骤。

21.将所述有机材料层与所述固定层结合的步骤可包括:准备在与多个所述岛对应的位置分别形成有所述有机材料层的所述第三基板的步骤;以及将形成于所述第三基板的多个所述有机材料层结合于多个所述结合区域的步骤。

22.在形成所述固定层的步骤中,可在所述固定层与所述半导体薄膜层之间设置电极,所述制造方法可在将所述半导体薄膜层接合于所述第二基板的步骤之后还包括:在所述固定层中形成开口的步骤;以及经由所述开口而形成连接于所述电极的配线层的步骤。

23.所述半导体元件的制造方法可在将所述半导体薄膜层接合于所述第二基板的步骤之后还包括:在所述固定层中形成开口的步骤;在所述开口中设置电极的步骤;形成包含所述固定层的至少一部分的层间绝缘层的步骤;以及经由所述开口而形成连接于所述电极的配线层的步骤。

24.还包括形成与所述第一基板相同的大小或较所述第一基板小的所述半导体薄膜层的岛的步骤,且在形成所述半导体薄膜层的岛的步骤中,可以所述半导体薄膜层的岛的边的方向与作为所述第一基板的si(111)基板的<112>方向的角度成为

±

45

°

以下的角度范围的方式形成所述半导体薄膜层的岛。在形成所述半导体薄膜层的岛的步骤中,可以所述半导体薄膜层的岛中的最长边的方向与作为所述第一基板的si(111)基板的<112>方

向的角度成为

±

45

°

以下的角度范围的方式形成所述半导体薄膜层的岛。

25.在形成所述半导体薄膜层的岛的步骤中,可以由六方晶构成的所述半导体薄膜层的岛中的最长边的方向相对于六方晶的<1

‑

100>方向而成为

±

45

°

以下的角度范围的方式形成所述半导体薄膜层的岛。

26.在形成所述固定层的步骤中,可在所述固定层与所述半导体薄膜层之间设置电极,所述半导体元件的制造方法可在将所述半导体薄膜层接合于所述第二基板的步骤之后还包括:在所述固定层中形成开口的步骤;以及经由所述开口而形成连接于所述电极的配线层的步骤。

27.所述制造方法在形成所述固定层的步骤之前可还包括:在所述第一基板上形成由与所述半导体薄膜层不同的材料形成的异种材料层的步骤;以及在所述异种材料层上形成所述半导体薄膜层的步骤,且所述第一基板与所述半导体薄膜层的晶格常数的差小于所述半导体薄膜层与所述异种材料层的晶格常数的差。

28.所述第一基板与所述半导体薄膜层的热膨胀系数的差例如小于所述半导体薄膜层与所述异种材料层的热膨胀系数的差。另外,所述异种材料层相对于既定的蚀刻方法的蚀刻速度可大于所述第一基板及所述半导体薄膜层相对于所述既定的蚀刻方法的蚀刻速度。

29.所述制造方法在将所述半导体薄膜层接合于所述第二基板的步骤之前可还包括:准备由热传导率高于所述第一基板的材料构成的所述第二基板的步骤。在所述情况下,可包括:形成多个所述半导体薄膜层的岛的步骤,且在接合于所述第二基板的步骤中,将多个所述半导体薄膜层的岛接合于所述第二基板,在接合于所述第二基板的步骤之后可还包括形成用以连接接合于所述第二基板的多个所述半导体薄膜层的岛的至少任一个的配线的步骤。

30.所述制造方法可在形成所述固定层的步骤之前,还包括形成所述半导体薄膜层的步骤,且可在形成所述半导体薄膜层的步骤中,形成未露出至所述半导体薄膜层的外周的阶差结构。

31.本发明的第二实施方式的半导体元件包括:第二基板,与形成有半导体薄膜层的第一基板不同;所述半导体薄膜层,接合于所述第二基板;以及与所述半导体薄膜层不同的固定层,形成于所述半导体薄膜层的第一方向上的所述半导体薄膜层的两端间的至少一部分的区域。所述固定层可形成于所述半导体薄膜层的上表面及所述半导体薄膜层的所述第一方向上的两侧的侧面。所述固定层中,相较于所述半导体薄膜层的所述第一方向上的两侧面的被覆率,所述半导体薄膜层的与所述第一方向正交的第二方向上的两侧面的被覆率小。

32.所述半导体元件可还包括:电极,设置于所述固定层与所述半导体薄膜层之间;以及配线层,经由形成于所述固定层的开口部结合于所述电极。

33.所述半导体元件中,由六方晶构成为岛状的所述半导体薄膜层的多个边中的最长边的方向成为六方晶的<1

‑

100>方向的角度可为

±

45

°

以下。

34.所述半导体薄膜层可具有未露出至外周的阶差结构。另外,所述的半导体元件可包括:接合于所述第二基板的多个所述半导体薄膜层的岛;配线,用以连接多个所述半导体薄膜层的岛的至少任一个。

35.发明的效果

36.根据本发明,起到可使将所移动的半导体磊晶层接合于其他基板的步骤效率化的效果。

附图说明

37.图1a是用以说明将半导体薄膜层的岛自母材基板拆下的方法的图。

38.图1b是用以说明将半导体薄膜层的岛自母材基板拆下的方法的图。

39.图1c是用以说明将半导体薄膜层的岛自母材基板拆下的方法的图。

40.图1d是用以说明将半导体薄膜层的岛自母材基板拆下的方法的图。

41.图1e是用以说明将半导体薄膜层的岛自母材基板拆下的方法的图。

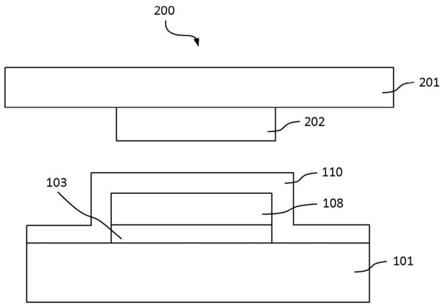

42.图2a是表示作为第三基板的拾取(pick up)基板的图。

43.图2b是图2a的a

‑

a剖面。

44.图2c是表示拾取基板的变形例的图。

45.图3a是示意性地表示自母材基板将半导体薄膜层的岛分离的步骤的图。

46.图3b是示意性地表示自母材基板将半导体薄膜层的岛分离的步骤的图。

47.图3c是示意性地表示自母材基板将半导体薄膜层的岛分离的步骤的图。

48.图3d是示意性地表示将分离后的半导体薄膜层的岛接合于移动目的地基板为止的步骤的图。

49.图3e是示意性地表示将分离后的半导体薄膜层的岛接合于移动目的地基板为止的步骤的图。

50.图3f是示意性地表示将分离后的半导体薄膜层的岛接合于移动目的地基板为止的步骤的图。

51.图4a是示意性地表示使多个半导体薄膜层的岛移动的步骤的图。

52.图4b是示意性地表示使多个半导体薄膜层的岛移动的步骤的图。

53.图4c是示意性地表示使多个半导体薄膜层的岛移动的步骤的图。

54.图4d是示意性地表示使多个半导体薄膜层的岛移动的步骤的图。

55.图4e是示意性地表示使多个半导体薄膜层的岛移动的步骤的图。

56.图5a是用以说明使多个半导体薄膜层的岛移动的方法的图。

57.图5b是用以说明使多个半导体薄膜层的岛移动的方法的图。

58.图5c是用以说明使多个半导体薄膜层的岛移动的方法的图。

59.图5d是用以说明使多个半导体薄膜层的岛移动的方法的图。

60.图5e是用以说明使多个半导体薄膜层的岛移动的方法的图。

61.图6是表示本实施方式的半导体元件的制造方法的步骤流程的图。

62.图7a是半导体元件的制造方法的变形例的一例。

63.图7b是半导体元件的制造方法的变形例的一例。

64.图7c是半导体元件的制造方法的变形例的一例。

65.图7d是半导体元件的a

‑

a线剖面图。

66.图8a是表示半导体元件的结构的图。

67.图8b是表示半导体元件的结构的图。

68.图8c是表示半导体元件的结构的图。

69.图9a是表示固定层的形状的变形例的图。

70.图9b是表示固定层的形状的变形例的图。

71.图9c是表示固定层的形状的变形例的图。

72.图9d是表示固定层的形状的变形例的图。

73.图10是示意性地例示用作母材基板的半导体磊晶晶片的图。

74.图11a是表示角度θ与垂直于半导体薄膜层的岛的长边的方向上的si(111)基板表面区域的蚀刻速度的关系的图。

75.图11b是用以说明角度θ的图。

76.图12是表示六角形状的半导体薄膜层的岛的图。

77.图13a是作为母材基板的si(111)基板上所形成的gan半导体薄膜层的岛的显微镜照片。

78.图13b是相对于母材基板的结晶方向的半导体薄膜层的岛的长边的方向与图13a不同的、gan半导体薄膜层的岛的显微镜照片。

79.图14是将长边与<1

‑

100>方向大致平行的半导体薄膜层的岛接合于移动目的地基板的状态的显微镜照片。

80.图15a是用以说明使固定层容易断裂的方法的图。

81.图15b是用以说明使固定层容易断裂的方法的图。

82.图16是表示实际的实验中对固定层的分离状态进行观察而得的结果的显微镜照片。

83.图17是将自母材基板分离后的半导体薄膜层的岛接合于移动目的地基板的状态的显微镜照片。

84.图18a是表示具有在短边方向上延伸的区域的固定层的例子的图。

85.图18b是表示具有在短边方向上延伸的区域的固定层的例子的图。

86.图19a是示意性地表示将母材基板上所形成的半导体薄膜层分割成各别的半导体薄膜层的岛的状态的图,且是母材基板及半导体薄膜层的岛的顶视图。

87.图19b是母材基板及半导体薄膜层的岛的剖面图。

88.图20a是半导体元件的顶视图,所述半导体元件包括形成有未露出至半导体薄膜层的岛的外周的阶差结构的半导体薄膜层。

89.图20b是图20a所示的半导体元件的a

‑

a线剖面图。

90.图20c是图20a所示的半导体元件的b

‑

b线剖面图。

91.图21a是用以说明制造半导体元件的方法的图。

92.图21b是用以说明制造半导体元件的方法的图。

93.图21c是用以说明制造半导体元件的方法的图。

94.图21d是用以说明制造半导体元件的方法的图。

95.图21e是用以说明制造半导体元件的方法的图。

96.图21f是用以说明制造半导体元件的方法的图。

97.图21g是用以说明制造半导体元件的方法的图。

98.图21h是用以说明制造半导体元件的方法的图。

99.图21i是用以说明制造半导体元件的方法的图。

100.图22是用以说明现有技术的图。

101.附图标号说明

102.101、401、501、701、801、901、1001、3001:母材基板

103.102:预定去除层

104.103、117、403a、403b、403c、503a~503c、703a、703b、703c、703d、803:空隙

105.104:半导体薄膜层

106.106:预定去除区域

107.108、109、408a、408b、408c、508a、508b、508c、708a、708b、708c、708d、718a、718b、808、920:半导体薄膜层的岛/岛

108.110、112、114、410a、410b、410c、414a、414b、414c、416a、416b、416c、510a、510b、510c、514a、514c、516a、516c、705a、705b、705c、705d、714a、714b、814、928:固定层130、131、921、922、1002a、1002b:区域

109.200、200'、420、520、710、930:拾取基板

110.201、421、521、711:基底基板

111.202、422a、422b、422c、522a、522c:拾取凸块

112.204、712:拾取层

113.210、430、530:结构

114.301、451、531、731、831、931:移动目的地基板

115.302、551:表面

116.308、558a、558c:面

117.742、744:元件等搭载区域

118.800:半导体元件

119.816a、816b:开口部

120.822、824、924、925:电极

121.842、926:层间绝缘膜

122.854、856、927:配线层

123.923:外周壁

124.1003:槽

125.3002:牺牲层

126.3003:半导体磊晶层

127.3004:支持体

128.3010:牺牲层受到蚀刻的区域

129.a、b:侧面

130.l1、l2、l3、l4:长度

131.l2a、l2b:宽度

132.θ:角度

具体实施方式

133.[半导体元件的制造方法的概要]

[0134]

在本实施方式的半导体元件的制造方法中,使作为第一基板的母材基板上的半导体薄膜层的岛移动至作为第二基板的移动目的地基板,从而制造具有移动目的地基板及半导体薄膜层的半导体元件。“半导体薄膜层的岛”是与母材基板相同大小的半导体薄膜层的区域、或较母材基板小的半导体薄膜层的区域。在一块母材基板上可形成有一个半导体薄膜层的岛,也可形成有多个半导体薄膜层的岛。

[0135]

本实施方式的半导体元件的制造方法的特征在于:形成在半导体薄膜层的岛自母材基板分离的状态下对半导体薄膜层的岛进行支撑的固定层,以使得在为了将半导体薄膜层的岛自母材基板移动至移动目的地基板而将半导体薄膜层的岛自母材基板分离的状态下,半导体薄膜层的岛能够在母材基板上维持稳定的状态。通过所述方式,可在使半导体薄膜层的岛连结于作为第三基板的拾取基板上所形成的有机物层之后,将半导体薄膜层的岛自母材基板分离,并使分离后的半导体薄膜层的岛移动至第二基板。

[0136]

[将半导体薄膜层的岛自母材基板拆下的步骤]

[0137]

图1a~图1e是用以说明将半导体薄膜层的岛自母材基板拆下的方法的图。以下,参照图1a~图1e来说明将半导体薄膜层的岛自母材基板拆下的方法的概要。

[0138]

首先,如图1a所示,在作为第一基板的母材基板101上形成预定去除层102,并在预定去除层102上形成作为半导体磊晶层的半导体薄膜层104。预定去除层102是在之后的步骤中通过蚀刻而去除的区域。

[0139]

预定去除层102例如是由当使用既定的蚀刻方法(使用既定的蚀刻液的湿式蚀刻或使用既定的气体的干式蚀刻)进行蚀刻时的蚀刻速度与母材基板101及半导体薄膜层104不同的材料而形成。预定去除层102也可由与母材基板101相同的材料形成。例如,预定去除层102可为母材基板101的表面附近的一部分区域。

[0140]

半导体薄膜层104例如为通过磊晶成长而形成的半导体薄膜层或通过晶片接合(wafer bonding)而形成的半导体薄膜层。半导体薄膜层104也可为通过其他方法而形成的半导体薄膜层。

[0141]

半导体薄膜层104例如为iii

‑

v族化合物半导体材料(例如gaas、algaas、ingaas、inp、inalgap等)、iii族氮化物半导体材料(例如gan、inn、algan、ingan、aln等)、氧化物半导体材料(例如zno、ga2o3等)、iv族化合物半导体材料(sic等)、金刚石、si或sige等。母材基板101例如为iii

‑

v族化合物半导体材料基板(例如gaas基板、inp基板等)、iii族氮化物半导体材料基板(例如gan基板)、氧化物半导体材料基板(例如zno基板、ga2o3基板等)、iv族化合物半导体基板(例如sic等)、金刚石基板、或si、sige等。

[0142]

继而,如图1b所示,将半导体薄膜层104分割成多个岛区域而形成半导体薄膜层的岛108(以下有时将“半导体薄膜层的岛108”称为“岛108”)。岛108的形状并无限定,在以下的说明中例示岛108为长方形的情况。岛108例如可为正方形或六角形。再者,也可代替将半导体薄膜层104分割成多个岛区域而通过在母材基板101的上方使半导体薄膜层104选择成长来形成单独的或多个岛108。

[0143]

另外,形成岛108的方法为任意的,可例示以下的方法。

[0144]

1)通过光刻/蚀刻步骤对半导体薄膜层104进行加工而形成岛108的方法

[0145]

2)在母材基板101的上方使半导体薄膜层104选择成长的方法

[0146]

3)沿母材基板101上的横向(水平方向)使半导体薄膜层104横向成长的方法

[0147]

以下,对多个半导体薄膜层的岛108中的一个半导体薄膜层的岛108进行说明。在所述步骤中,如图1b所示,包括预定去除层102在内也可形成为岛108。预定去除层102中包含于岛108的区域为图1b所示的预定去除区域106。

[0148]

继而,如图1c及图1d所示,形成作为薄膜的固定层110,所述固定层110将岛108中的与母材基板101一侧为相反侧的主面的至少一部分与母材基板101中的岛108侧的面的至少一部分结合。固定层110例如是在岛108的上表面至母材基板101之间延伸存在的形状,但固定层110只要可将岛108与母材基板101结合,则也可为其他形状。例如,固定层110也可由将岛108的包含长度方向上的两侧面的区域与母材基板101结合的两个薄膜构成。另外,固定层110也可为在岛108的短边方向上以将母材基板101作为起点及终点而跨越岛108的方式延伸存在的薄膜。另外,固定层110可与岛108的边平行,也可形成为在与岛108的边的方向不同的方向上延伸。

[0149]

在形成在岛108的长度方向上延伸存在的固定层110的情况下,在形成固定层110的步骤中,以在半导体薄膜层104的主面上的第一方向(所述方向例如是将半导体薄膜层104的被覆率高的两侧面连结的方向)上在半导体薄膜层104的两端间延伸存在,且在与第一方向正交的第二方向上的半导体薄膜层104的两侧面中的至少一部分区域中半导体薄膜层104露出的方式形成固定层110。在岛108为长方形的情况下,固定层110对岛108的长边的侧面的被覆率小于对短边的侧面的被覆率。通过所述方式,当实施后述的蚀刻时,可缩短为了将岛108与母材基板101分离而将岛108或母材基板101的一部分区域、或者将岛108与母材基板101之间的层的一部分区域去除为止的时间。

[0150]

图1d为与图1c对应的顶视图。固定层110发挥如下功能:以岛108的在至少正下方的母材基板101上的位置不变的方式,将岛108留存于母材基板101的上方。固定层110为包含如下材料的薄膜层:所述材料相对于用以对预定去除区域106进行蚀刻的蚀刻手段而具备耐蚀刻性能。

[0151]

作为固定层110的材料,例如可使用氧化膜(例如si

x

o

y

、si

x

o

y

n

z

、al

x

o

y

、al

x

o

y

n

z

等)、或氮化膜(例如si

x

n

y

、al

x

n

y

等)等无机绝缘膜。无机绝缘膜可为单层或不同材料的层叠。例如使用化学气相沉积(chemical vapor deposition,cvd)法形成无机绝缘膜,并通过标准的光刻及蚀刻的工艺将无机绝缘膜的一部分去除,由此可形成所期望的固定层110。当形成固定层110时,若具有相对于用以对预定去除区域106进行蚀刻的既定的蚀刻手段的耐性,则作为固定层110的材料,也可使用有机膜(例如感光性涂布膜、感光性有机片材等)。

[0152]

固定层110的厚度可根据半导体薄膜层的岛108的尺寸及厚度而选择最适合的厚度。固定层110的薄膜厚度例如为较半导体薄膜层的岛108的厚度(即形成于母材基板101上的半导体薄膜层104的厚度)薄的厚度。固定层110的厚度优选为如下厚度:通过在将后述的作为第三基板的拾取基板200结合于固定层110及半导体薄膜层104的至少一部分结合区域的状态下沿与母材基板101相离的方向移动拾取基板200的力,将形成于母材基板101上的固定层110与形成于半导体薄膜层的侧面的固定层110之间切断的厚度。

[0153]

图1d所示的半导体薄膜层的岛108具有长度为l1与l2的边,且l1>l2。固定层110具有被覆岛108的上表面的第一区域、被覆岛108的右侧面的第二区域、以及被覆岛108的左

侧面的第三区域。固定层110在具有第二区域及第三区域之前还具有被覆母材基板101的区域。在图1d所示的例子中,固定层110未被覆岛108的四个侧面中的长边的侧面(即长度为l1的边的侧面),且被覆短边的侧面(即长度为l2的边的侧面)的一部分。

[0154]

继而,如图1e所示,通过将岛108或母材基板101的一部分区域、或者岛108与母材基板101之间的预定去除区域层的一部分区域去除而形成空隙103。例如,将岛108的与至少正下方的母材基板101连接的区域蚀刻去除,从而在岛108与母材基板101之间的至少岛108的正下方区域中形成空隙103。当形成空隙103时,理想的是使用岛108相对于所使用的蚀刻液或蚀刻气体的蚀刻速度至少小于预定去除区域106的蚀刻速度的蚀刻液或蚀刻气体。

[0155]

在所述蚀刻步骤中,例如在预定去除区域层的蚀刻各向同性地进行且蚀刻速度不受方向影响的情况下,因垂直于岛108的长边的方向上的蚀刻距离短,故相较于垂直于短边的方向上的蚀刻而蚀刻结束得早。因此,通过开放长边的侧面,或者通过以相较于短边上的固定层110的被覆率而长边上的固定层110的被覆率变小的方式形成固定层110,可更快地结束蚀刻而形成空隙103。通过所述方式,在用以去除预定去除区域106的蚀刻步骤中,可降低在岛108中产生蚀刻损伤的风险。

[0156]

再者,在以上的说明中,例示了通过利用蚀刻而去除预定去除层102来形成空隙103的情况,但也可通过在不形成预定去除层102的情况下利用各向异性蚀刻而将母材基板101的表面区域去除来形成空隙。

[0157]

在通过利用各向异性蚀刻而将母材基板101的表面的区域去除来形成空隙的情况下,在形成固定层的步骤中,优选为将蚀刻速度大的方向上的两侧面设为第二方向。第二方向上的两侧面可整体完全露出,也可由固定层110被覆一部分区域。而且,优选为以相较于在第一方向上延伸存在的固定层110对半导体薄膜层104中的第一方向上的两侧面的被覆率,在第二方向上延伸存在的固定层110对半导体薄膜层104中的第二方向上的两侧面的被覆率变小的方式形成固定层110。通过所述方式,可通过实施蚀刻而容易地形成空隙103。

[0158]

另外,在以上的说明中,例示了半导体薄膜层的岛108为长方形的情况,但在如下情况下岛108也可为正方形。

[0159]

1)通过利用蚀刻将预定去除层102去除而将半导体薄膜层自母材基板分离的情况

[0160]

2)使用用以将母材基板101的表面区域去除的各向异性蚀刻的情况

[0161]

3)岛108的尺寸非常小的情况(例如为20μm以下的情况)

[0162]

[将半导体薄膜层的岛108分离的步骤]

[0163]

图2a是表示用以将半导体薄膜层的岛108自母材基板101分离的作为第三基板的拾取基板200的图。图2b是图2a的a

‑

a剖面。如图2b所示,拾取基板200具有基底基板201、以及形成于基底基板201上的包含有机材料的拾取凸块202。作为基底基板201,例如可选择石英、蓝宝石、玻璃等的透明基板;si等的半导体基板;陶瓷基板;或金属基板等。基底基板201可为单一材料,也可为层叠材料。另外,基底基板201也可为利用其他材料对表面进行了涂敷的基板。

[0164]

拾取凸块202例如为有机材料层,且可在基底基板201上涂布感光性有机材料并利用标准的光刻工艺而形成。有机材料层例如可通过利用旋涂法、浸渍法等而在拾取基底基板上进行涂敷来形成,也可通过将有机材料膜贴附于拾取基底基板上来形成。

[0165]

拾取基板的结构可根据所拾取的岛108的形状或尺寸而进行各种变形。例如,拾取

基板可具有插入至基底基板201与拾取凸块202之间的其他结构。另外,拾取基板也可如图2c所示的拾取基板200'那样,不具有与作为自母材基板101分离的对象的岛108的形状相对应的拾取凸块202,而具有面积较岛108大且平坦的拾取层204。

[0166]

图3a~图3c是示意性地表示使用拾取基板200而将岛108自母材基板101分离的步骤的图。

[0167]

首先,如图3a所示,使拾取基板200的拾取凸块202的位置对准岛108。具体而言,将拾取基板200配置于固定层110及岛108的至少一部分区域与拾取凸块202的至少一部分区域重合的位置。

[0168]

接着,如图3b所示,使拾取凸块202接触或压接于固定层110及岛108的至少一部分区域。由此,将拾取凸块202连结于固定层110及岛108的至少一部分区域。若在岛108与母材基板101之间形成有空隙103的状态下,使拾取基板200接触固定层110及岛108并向下施力,则在岛108与空隙103的边界线的附近(图3b的虚线部分),固定层110中产生龟裂或固定层110断裂。

[0169]

在固定层110中产生了龟裂的状态或固定层110断裂的状态下,如图3c所示,通过将与固定层110的一部分区域连结的状态下的拾取基板200提起,固定层110分离成与岛108相接的固定层114、以及与母材基板101相接的固定层112,从而可将半导体薄膜层的岛108及作为固定层110的一部分区域的固定层114自母材基板101分离。

[0170]

再者,也可在自母材基板101分离后的岛108的母材基板101侧的面上伴有与半导体薄膜层104不同材料的半导体层的状态下,将岛108自母材基板101分离。例如,自母材基板101分离后的岛108也可伴有设置于母材基板101上的、用以使半导体薄膜层104选择成长或横向成长的掩模膜或介电体层。

[0171]

[将半导体薄膜层的岛108接合于其他基板的步骤]

[0172]

图3d~图3f是示意性地表示将分离后的岛108接合于移动目的地基板301为止的步骤的图。如图3d所示,将在拾取基板200上连结有岛108及固定层114的状态的结构210定位于作为第二基板的移动目的地基板301的上方的既定位置。

[0173]

其后,如图3e所示,将结构210中的固定层114下方的岛108的面308压接于移动目的地基板301,从而将岛108接合于移动目的地基板301。也可在将岛108压接于移动目的地基板301的步骤之前,对所接合的面(半导体薄膜层的岛108的面308与移动目的地基板301的表面302)适当进行表面处理。

[0174]

接着,如图3f所示,自固定层114将拾取凸块202及基底基板201去除。例如,可通过浸渍于溶解构成拾取凸块202的有机材料的有机溶剂等药液中以使拾取凸块202溶解,而将固定层114与基底基板201分离。

[0175]

再者,在将岛108压接于移动目的地基板301上的步骤中,在移动目的地基板301与岛108的接合牢固的情况下,可在利用有机溶剂等药液使拾取凸块202溶解之前将拾取基板200提起。所述情况下,在将拾取基板200提起后,可追加利用有机溶剂等药液对接合有岛108的移动目的地基板301上进行清洁的步骤。

[0176]

再者,在接合于所述移动目的地基板301的岛108中,也可在形成固定层110的步骤之前形成既定的元件结构或元件结构的一部分。另外,在将岛108接合于所述移动目的地基板301上之后,可对固定层110进行加工,或者在半导体薄膜层上形成层间绝缘膜或形成与

外部结构的电性连接的配线结构等。

[0177]

另外,在以上的说明中,将岛108接合于移动目的地基板301的表面,但也可在移动目的地基板301与岛108之间设置其他层(无机材料薄膜层或有机材料薄膜层等)。另外,也可在接合步骤之后设置热处理步骤。

[0178]

另外,在将自母材基板101分离后的岛108接合于移动目的地基板301的情况下,也可在岛108中的接合于移动目的地基板301一侧的面上伴有与半导体薄膜层104不同材料的半导体层的状态下接合于移动目的地基板301。例如,也可将伴有设置于母材基板101上的、用于半导体薄膜层104的选择成长或横向成长的掩模膜或介电体层的状态下的岛108接合于移动目的地基板301。

[0179]

[移动多个岛108的方法]

[0180]

在以上的说明中,对移动一个半导体薄膜层的岛108的方法进行了说明,但在本实施方式的半导体元件的制造方法中,也可如图4a~图4e所示移动多个半导体薄膜层的岛408a、408b、408c。在将多个岛408a、408b、408c成批地自母材基板401分离的情况下,准备包括与多个岛408a、408b、408c对应的多个拾取凸块422a、422b、422c的拾取基板420。然后,通过与所述步骤相同的步骤而使拾取基板420接触或压接于固定层410a、410b、410c及岛408a、408b、408c,将多个岛408a、408b、408c自母材基板401分离,并将多个岛408a、408b、408c接合于移动目的地基板451上。

[0181]

图4a~图4e是示意性地表示使多个岛408a、408b、408c移动的步骤的图。在图4a~图4e中,母材基板401、多个空隙403a、403b、403c、多个岛408a、408b、408c、多个固定层410a、410b、410c、多个固定层414a、414b、414c、多个固定层416a、416b、416c、拾取基板420、基底基板421、多个拾取凸块422a、422b、422c、结构430以及移动目的地基板451分别与图3a~图3f中的母材基板101、空隙103、岛108、固定层110、固定层114、固定层112、拾取基板200、基底基板201、拾取凸块202、结构210以及移动目的地基板301对应。在将多个岛408a、408b、408c自母材基板401分离的情况下,也可使用如图2c所示的、不具有拾取凸块且包括包含有机材料的拾取层的拾取基板。

[0182]

[多个半导体薄膜层的移动]

[0183]

图5a~图5e是用以说明使多个半导体薄膜层的岛移动的方法的图。在图5a~图5e中,母材基板501、多个空隙503a、503b、503c、多个岛508a、508b、508c、多个固定层510a、510b、510c、多个固定层514a、514c、多个固定层516a、516c、拾取基板520、基底基板521、多个拾取凸块522a、522c、结构530、移动目的地基板531以及表面551分别与图3a~图3f中的母材基板101、空隙103、岛108、固定层110、固定层114、固定层112、拾取基板200、基底基板201、拾取凸块202、结构210、移动目的地基板301以及表面302对应。以下,对选择母材基板上所形成的多个半导体薄膜层的岛中的一部分岛并移动至移动目的地基板的方法进行说明。

[0184]

如图5a所示,在半导体薄膜层的岛的至少正下方形成空隙503a~空隙503c后,仅在与所选择的半导体薄膜层的岛508a及岛508c对应的位置,在拾取基板520的基底基板521上设置有机材料的拾取凸块522a、拾取凸块522c。继而,使拾取凸块522a与拾取凸块522c接触或压接于岛508a与岛508c,从而将拾取基板520连结于所选择的岛508a及岛508c。图5b为图5a的俯视图,图5b的a

‑

a剖面相当于图5a。

[0185]

接着,如图5c所示,将连结有所选择的岛508a及岛508c的拾取基板520提起,从而仅将所选择的岛508a及岛508c自母材基板501分离。图5c是表示通过拾取基板520而将所选择的岛508a及岛508c提起的状态的图。如图5c所示,未选择的岛508b残留于母材基板501上。

[0186]

接着,如图5d所示,将在拾取基板520上连结有岛508a、岛508c、固定层514a及固定层514c的结构(图5c所示的结构530)配置于移动目的地基板531上的既定位置。继而,将岛508a及岛508c中的与固定层514a及固定层514c为相反侧的面558a及面558c压接于移动目的地基板531的表面551,从而将所选择的岛508a及岛508c接合于移动目的地基板531。

[0187]

接着,自移动目的地基板531将拾取凸块522a、拾取凸块522c及基底基板521去除,由此可制造如图5e所示那样在移动目的地基板531上接合有半导体薄膜层的岛508a及岛508c的半导体元件。

[0188]

[半导体元件的制造方法的步骤流程]

[0189]

图6是表示本实施方式的半导体元件的制造方法的步骤流程的图。如图6所示,在本实施方式的半导体元件的制造方法中,可使用包括与母材基板501上的既定的所选择的半导体薄膜层的岛508a、508c对应的、有机材料的拾取凸块522a、522c的拾取基板520,将所选择的岛508a、508c自母材基板501分离并接合于移动目的地基板531。通过所述方式,起到可自母材基板501上的多个岛508a、508b、508c中选择所期望的岛508a、508c而接合于移动目的地基板531的效果。

[0190]

关于用以将母材基板501上的多个岛508a、508b、508c中的所期望的岛508a、508c自母材基板501分离的分离图案,显然可进行各种变形。

[0191]

[本实施方式的半导体元件的制造方法所带来的效果]

[0192]

根据以上所说明的半导体元件的制造方法,使用包括在基底基板201上通过光刻并利用有机材料而形成的拾取凸块202的拾取基板200,将通过固定层110而固定于母材基板101上的半导体薄膜层的岛108自母材基板101分离,并将连结于拾取基板200的半导体薄膜层的岛108压接并接合于移动目的地基板301。通过所述方式,可将自母材基板101分离的半导体薄膜层104容易地移动至其他基板。

[0193]

另外,对本领域技术人员而言显而易见的是,可对应于自母材基板101分离的半导体薄膜层的岛108而容易地制作包括最适合的形状与尺寸的拾取凸块202的拾取基板200。根据本实施方式的半导体元件的制造方法,能够使用可容易地制作的拾取基板200来将半导体薄膜层的岛108自母材基板101分离并接合于移动目的地基板301,因此可以低成本来实现半导体薄膜层的岛108的移动。

[0194]

进而,在将半导体薄膜层的岛108接合于移动目的地基板301后,自移动目的地基板301上将包含有机材料的拾取凸块202及拾取基板200的基底基板201去除,因此也起到可对基底基板201进行重复再利用的效果。

[0195]

另外,如上所述,在形成在岛108的长度方向上延伸存在的固定层110的情况下,产生如下所述的效果。

[0196]

(1)于在半导体薄膜层的岛108与母材基板101之间形成空隙的步骤中使用蚀刻液或蚀刻气体的情况下,可保护半导体薄膜层表面、形成于半导体薄膜层的岛108的电极、配线等元件结构。

[0197]

(2)在形成半导体薄膜层的岛108与母材基板101之间的空隙之后接合于移动目的地基板301上为止的步骤中,可减少因施加于半导体薄膜层的岛108的应力而造成的半导体薄膜层的岛108的翘曲量。若如此那样通过以减少应力的方式进行调整而半导体薄膜层的岛108的翘曲得到减少,则例如在形成有空隙的状态下,也容易通过固定层110而在母材基板101上保持半导体薄膜层的岛108。其结果,容易进行通过拾取基板200的对半导体薄膜层的岛108的分离,并且于在移动目的地基板301上的接合步骤中,容易使半导体薄膜层的岛108保持于移动目的地基板301上。

[0198]

(3)在接合于移动目的地基板301上之后的元件形成步骤中,可将固定层110用作配线层与半导体薄膜层之间的层间绝缘膜等。

[0199]

(4)在接合于移动目的地基板301上之后的元件形成步骤中在固定层110上形成配线层的情况下,可防止当固定层110不连续时所存在的阶差处的配线层的断线。

[0200]

(5)容易确保使用接合于移动目的地基板301上的半导体薄膜层的岛108而形成的半导体元件的特性的均一性。通过半导体薄膜层的岛108的表面经连续的固定层110被覆,例如自发光元件上表面出射的光的强度分布变得均一。在由不连续的固定层110被覆的情况下,在固定层110的不连续区域中光强度发生变化。

[0201]

再者,在以上的说明中,以矩形形状对半导体薄膜层的形状进行了说明,但除矩形形状以外,也可为圆形或具有复杂的形状的形状。另外,在以上的说明中,例示(图示)了不具有元件结构的单纯的半导体薄膜层,但半导体薄膜层也可具有元件结构。另外,半导体薄膜层表面也可不平坦而包括与元件结构对应的介电体材料或金属材料的薄膜结构。

[0202]

[半导体元件的制造方法的变形例]

[0203]

图7a~图7d为半导体元件的制造方法的变形例的一例。在图7a~图7d中,母材基板701、多个空隙703a、703b、703c、703d、多个岛708a、708b、708c、708d、718a、718b、多个固定层705a、705b、705c、705d、多个固定层714a、714b、拾取基板710、基底基板711、拾取层712以及移动目的地基板731分别与图2c、图3a~图3f中的母材基板101、空隙103、岛108、固定层110、固定层114、拾取基板200、基底基板201、拾取层204以及移动目的地基板301对应。如图7a及图7b(图7b为图7a的a

‑

a剖面图)所示,也可将母材基板701上的多个半导体薄膜层的岛(例如岛708a、岛708b、岛708c、岛708d、岛718a、岛718b)中的、既定的一部分多个岛自母材基板分离。另外,如图7c及图7d(图7d为图7c的a

‑

a剖面图)所示,可将自母材基板701分离后的岛(图7c的708a、708b、718a、718b)良好地接合于在一部分区域(图7c中的元件等搭载区域742、元件等搭载区域744)中搭载有其他元件的移动目的地基板731上的既定位置。

[0204]

[复合材料元件的制作顺序]

[0205]

图8a~图8c是表示使用所述半导体元件的制造方法而制造的半导体元件800的结构的图。半导体元件800是通过所述制造方法而制造的复合材料元件。半导体元件800可通过如下方式制造:将在母材基板上形成了元件结构的半导体薄膜层的岛808自母材基板801分离而接合于移动目的地基板831,并形成连接至半导体薄膜层外的配线。此处所示的例子为一例,可适用于各种种类、材料、结构的半导体元件。

[0206]

图8a示出了半导体元件800的剖面结构。在图8a中示出了半导体薄膜层的岛808;形成于岛808的电极822、电极824;在电极位置处包括开口部816a、816b的固定层814;层间绝缘膜842、配线层854及配线层856。

[0207]

当制造半导体元件800时,在母材基板上形成用以形成既定的元件的半导体薄膜层后,形成电极822及电极824、或者进行向半导体薄膜层的岛808的分割(元件分离),由此形成元件结构。其后如图8b所示那样形成固定层814。进而,至少在母材基板801与岛808之间形成空隙803。在空隙803的形成中,通过将预定去除区域蚀刻去除来形成。

[0208]

其后,将包括包含有机材料的拾取凸块或拾取层的拾取基板连结于岛808及固定层814的一部分区域后,将岛808自母材基板801分离。其后,接合于移动目的地基板831上的既定的位置。移动目的地基板831例如也可设为与母材基板801或岛808不同的材料。在接合之前,视需要也可进行所接合的面(岛的接合面及移动目的地基板表面)的用于接合的表面处理。虽未图示,但也可在移动目的地基板831与岛808之间设置其他薄膜层。

[0209]

在将岛808接合于移动目的地基板831之后,如图8c所示,在用作绝缘膜的固定层814中的、岛808上的电极822及电极824的位置处形成开口部。其后,形成用于配线形成的层间绝缘膜842,并如图8a所示那样形成配线层854及配线层856,将配线层854及配线层856分别结合于电极822及电极824。如此那样,固定层814在岛808的上表面、以及在岛808的第一方向上的两侧面延伸存在的半导体元件800的制作结束。

[0210]

如上所述,根据本实施方式的半导体元件的制造方法,可将形成于母材基板上的包括元件的半导体薄膜层的岛良好地自母材基板分离,并可良好地接合于移动目的地基板,从而可获得具有高性能、高可靠性的复合材料元件。所述制造方法中可适用半导体元件所包括的半导体薄膜层的尺寸、结构等的各种形态。拾取基板所包括的包含有机材料的拾取凸块例如通过标准的光刻而制作,因此可与元件结构及半导体薄膜层的形态的各种变更、以及移动目的地基板的形态的各种变更对应地且容易地准备最适合的拾取基板。如此,根据本实施方式的半导体元件的制造方法,可容易地实现最适合的半导体薄膜层的自母材基板的分离及在移动目的地基板上的接合。

[0211]

[固定层110的形状的变形例]

[0212]

图9a~图9d是表示固定层110的形状的变形例的图。

[0213]

如图9a所示,可使设置于母材基板101的固定层110的宽度l2b及被覆半导体薄膜层的岛108的侧面的固定层110的宽度l2b较被覆岛108的上表面的固定层的宽度l2a窄。通过所述方式,当通过拾取基板200将岛108自母材基板101拆下时,设置于母材基板101的固定层110与设置于岛108的固定层110容易分离。

[0214]

所述情况下,如图9b所示,在接合于移动目的地基板301的复合材料元件的形态中,被覆半导体薄膜层的岛108的短边的侧面的固定层114的宽度l2b也较被覆上表面的固定层114的宽度l2a窄。

[0215]

另外,如图9c所示,也可在被覆半导体薄膜层的岛108的固定层110的长边区域中,设置被覆半导体薄膜层的岛108的长边的侧面的一部分且向母材基板101延伸存在的区域130。此时,优选设为固定层110对长边的侧面的被覆率小于对短边的被覆率。所述情况下,如图9d所示,在将半导体薄膜层的岛108接合于移动目的地基板301的形态下,成为形成有对半导体薄膜层的岛108的长边的侧面的一部分进行被覆的固定层110的区域131的状态。所述状态下,固定层110对长边的侧面的被覆率小于对短边的被覆率。

[0216]

[半导体薄膜层104的晶格缺陷的减少]

[0217]

在si晶片上形成gan磊晶层的过程中,有时会因母材基板101的材料与半导体薄膜

层的材料的晶格不匹配、及母材基板101的材料与半导体薄膜层的材料的热膨胀系数的不匹配(热膨胀系数的差异)而在半导体薄膜层104中导入结晶缺陷。

[0218]

为解决此种课题,作为母材基板101,可使用与半导体薄膜层相同系统的材料。所述情况下,难以利用蚀刻来将半导体薄膜层自母材基板101分离,因此,可将在母材基板101与半导体薄膜层104之间设置有与母材基板101及半导体薄膜层104的材料的蚀刻速度的差大的异种材料层的半导体晶片用作第一基板。另外,也可将在母材基板101与半导体薄膜层104之间设置有由晶格常数及热膨胀系数不同的材料构成的异种材料层的半导体晶片用作第一基板。作为异种材料层的材料,例如可使用si。所述情况下,优选为将设置于母材基板101与半导体薄膜层104之间的异种材料层的厚度的上限设为与半导体薄膜层104的厚度相同。

[0219]

母材基板101与半导体薄膜层104的晶格常数的差例如小于半导体薄膜层104与异种材料层的晶格常数的差。另外,母材基板101与半导体薄膜层104的热膨胀系数的差例如小于半导体薄膜层104与异种材料层的热膨胀系数的差。

[0220]

在母材基板101例如为gan基板,异种材料层例如由si(111)形成,半导体薄膜层104例如由gan形成的情况下,gan的热膨胀系数2.59ppm小于si(111)的热膨胀系数5.59ppm,因此有时在母材基板101中产生在下侧翘曲的应力(凸出至上侧的方向的应力),在半导体薄膜层104中,与母材基板101相反地,产生在上侧翘曲的应力(凸出至下侧的方向的应力)。如此,通过在母材基板101及半导体薄膜层104中分别产生相反方向的应力,可使得母材基板101及半导体薄膜层104不易翘曲。

[0221]

进而,通过将设置于母材基板101与半导体薄膜层104之间的异种材料层的厚度的上限设为与半导体薄膜层104相同,即便设置于母材基板101与半导体薄膜层104之间的异种材料层的热膨胀系数与半导体薄膜层104的热膨胀系数不同,但基板(母材基板101与薄的异种材料层的层叠结构)的热应力对半导体薄膜层104的影响中,与半导体薄膜层104的热膨胀系数差小的母材基板101的影响为支配性的。因此,可将异种材料层对半导体薄膜层104带来的热应力的影响抑制得小。其结果,可减少半导体薄膜层104的晶格缺陷。

[0222]

另外,异种材料层相对于既定的蚀刻方法的蚀刻速度大于母材基板101及半导体薄膜层104相对于既定的蚀刻方法的蚀刻速度。通过所述方式,可形成晶格缺陷少的半导体薄膜层104,并且通过利用异种材料层来形成图1c所示的预定去除区域106,可有效率地形成空隙103。

[0223]

[移动目的地基板301的材料的变形例]

[0224]

在半导体元件的芯片尺寸大的情况下会产生如下课题:因作为半导体元件芯片的基底的基板材料的热传导特性而在芯片内产生热分布,当半导体元件芯片运行时,在芯片的中央区域,芯片的温度上升大。尤其在作为半导体元件芯片的基底的基板的热传导率小的情况下,会产生所述温度分布大的课题。

[0225]

因此,作为移动目的地基板301的材料,可选择具有较母材基板101的热传导率高的热传导率的材料。作为移动目的地基板301,例如可使用:sic、aln、sin等的陶瓷基板;cu或al等的金属基板;包含由w、cr、cu、mo等多种金属构成的复合金属材料、金属材料层与陶瓷材料的复合材料基板或层叠材料基板;包含碳的材料的基板等。通过使移动目的地基板301的热传导率大于母材基板101的热传导率,可制造容易散热的半导体元件。

[0226]

通过将半导体薄膜层分割成多个岛,并将分别形成于分割后的多个岛上的多个要素元件相互连接,可使要素元件的散热性提高,因此可抑制由多个要素元件构成的半导体元件的温度上升。尤其通过作为移动目的地基板301而使用热传导率高的材料,即便在流动大电流的运行中也可抑制各要素元件的温度上升。

[0227]

当制造由多个要素元件构成的集合半导体元件时,可使形成于母材基板101的半导体薄膜层的多个岛108同时移动至移动目的地基板301。通过在移动至移动目的地基板301的多个岛108上形成电极,或者形成将多个岛108的至少任一个之间加以连接的配线图案,可制造多个要素元件联合运行的集合半导体元件。

[0228]

[结晶方向的最佳化]

[0229]

图10是示意性地例示用作母材基板101的半导体磊晶晶片的图。在图10中,示出了形成于作为母材基板101的si基板上的多个iii族氮化物半导体薄膜层的岛108。为以良好的状态将iii族氮化物半导体薄膜层的岛108自母材基板101拆下,岛108的边的方向优选为相对于作为母材基板101的si(111)基板的<112>方向而为

±

45

°

以下的角度范围。岛108的长边的方向优选为作为母材基板101的si(111)基板的<112>方向。

[0230]

si(111)相对于特定的蚀刻液而显示出各向异性蚀刻特性。通过利用si(111)的各向异性蚀刻特性,无需对晶片整体进行蚀刻去除,通过利用蚀刻而将si(111)的表面区域去除,便可将在si(111)上进行磊晶成长而得的半导体薄膜层自si(111)分离。以前,在使用si(111)作为母材基板101的情况下,并不知晓在母材基板101上进行磊晶成长而形成的半导体薄膜层的岛108的方向的优选方向。相对于此,发明人发现,优选为将岛108的一条边(例如较长的边)的方向设为相对于si基板的<112>方向而为

±

45

°

以下的角度范围。尤其发明人发现,进而优选为将岛108的长边的方向设为与si基板的<112>方向大致平行。

[0231]

另外,发明人发现,在由六方晶形成半导体薄膜层的岛108的情况下,优选为将半导体薄膜层的岛108的长边的方向设为相对于如gan等iii族氮化物半导体单结晶那样的六方晶材料的<1

‑

100>方向而成为

±

45

°

以下的角度范围。尤其发明人发现,进而优选为将半导体薄膜层的岛108的长边的方向设为与六方晶材料的<1

‑

100>方向大致平行。

[0232]

如图10所示,岛108具有长度为l3的边与长度为l4的边。在以下的说明中,例示为边的长度l3较边的长度l4长的长方形的情况,但在l3=l4的情况下(即岛108为正方形的情况下),将任一边设为长边而也可适用本发明。

[0233]

在岛108为长方形的情况下,优选为以使具有l3的长度的边(较长的边)与si(111)基板的<112>方向大致平行的方式形成岛108。此处,所谓大致平行,是指在某一定的误差或偏差的范围内平行,且不会极端大幅地偏离平行(例如相对于平行而不会超过

±

10

°

)。

[0234]

若在si(111)基板上使c面((0001)面)的iii族氮化物半导体薄膜层进行结晶成长,则si的<112>方向与iii族氮化物半导体薄膜层的结晶方向<1

‑

100>方向平行。所述情况下,优选为以使岛108的长度为l3的边与iii族氮化物半导体磊晶层的结晶的<1

‑

100>方向大致平行的方式形成岛108。

[0235]

如已述那样,作为形成岛108的方法而可采用多种方法,例如,通过对结晶成长而得的半导体薄膜层实施蚀刻,可形成一条边的方向与iii族氮化物半导体磊晶层的结晶的<1

‑

100>方向大致平行的半导体薄膜层的岛108。

[0236]

另外,也可通过在母材基板101上由sio2、si

x

n

y

等的无机绝缘膜形成具有开口的掩

模层,并在开口区域中使半导体薄膜层选择成长,从而形成岛108的最长的边的方向与si(111)的<112>方向或六方晶的<1

‑

100>方向大致平行的半导体薄膜层的岛108。另外,也可通过自选择成长而得的半导体薄膜层沿横向在掩模层上进行结晶成长,而形成岛108的最长的边的方向与si(111)的<112>方向或六方晶的<1

‑

100>方向大致平行的半导体薄膜层的岛108。在掩模层上进行结晶成长而得的半导体薄膜层的岛108与在掩模层之外的区域进行结晶成长而得的半导体薄膜层相比,缺陷少,可获得高品质的结晶成长区域。

[0237]

根据发明人进行的验证实验,在使半导体薄膜层的岛108的长边(l3的长度的边)大致平行于si(111)基板的<110>方向的情况下(将图10所示的矩形的岛108旋转90

°

后的情况),元件区域的正下方的si(111)基板表面的蚀刻未进行,无法进行遍及岛108的正下方整个面的、si基板表面的蚀刻去除。其结果,无法自用作母材基板101的si(111)基板以良好的状态将岛108拆下。

[0238]

图11a~图11b是发明人通过实验调查而得的、表示半导体薄膜层的岛108的长边的方向与si(111)的<112>方向或六方晶的<1

‑

100>方向所成的角度θ、与垂直于半导体薄膜层的岛108的长边的方向上的si(111)基板表面区域的蚀刻速度之间的关系的图。图11a的纵轴示出了设为θ=0

°

、45

°

、90

°

的情况下的蚀刻速度除以0

°

的情况下的蚀刻速度而得的值。图11b是用以说明角度θ的图。

[0239]

如图11a所示,若θ超过45

°

而趋向90

°

,则相对于与长边垂直的方向而言的蚀刻速度大幅降低。如图11a~图11b所示,为使岛108与si(111)基板之间的蚀刻良好地进行而在岛108与si(111)基板之间的、岛108的正下方区域整体中形成空隙,理想的是岛108的长边的方向与si(111)的<112>方向或六方晶的<1

‑

100>方向所成的角度θ至少不超过45

°

。

[0240]

根据所述结果可确认,当遍及岛108的正下方的整个面而将si(111)基板的表面区域蚀刻去除时,为进行遍及岛108的正下方整个面的、si基板表面的蚀刻去除而以良好的状态将岛108自si(111)基板拆下,理想的是将矩形形状的岛108的长边(长度为l1的边)的方向与si(111)基板的<112>方向的角度设定成

±

45

°

以下的角度范围。

[0241]

在半导体薄膜层为iii族氮化物或sic那样的六方晶系的结晶的情况下,理想的是使矩形的半导体薄膜层的岛108的长边(图10的l3)的方向与六方晶的<1

‑

100>的方向所成的角度θ为

±

45

°

以下的角度范围。再者,半导体薄膜层的岛108也可为具有iii族氮化物半导体或sic以外的六方晶系的材料,例如为zno。

[0242]

在以上的说明中,以半导体薄膜层的岛108为矩形形状的情况为例进行了说明,在半导体薄膜层的岛108为其他形状的情况下,可将半导体薄膜层的岛108中最长的边设为与si(111)基板的<112>方向大致平行的方向(使最长的边的方向与半导体磊晶层的结晶的<1

‑

100>方向大致平行)。

[0243]

图12是表示si(111)基板的母材基板101上所设置的六角形状的半导体薄膜层的岛109的图。岛109具有长度为l1、l2、l3的边,且满足l1>l2、l3的关系。即,长度为l1的边为最长的边。如图12所示,使半导体薄膜层的岛109的l1长度的边与si(111)的<112>方向大致平行。所述情况下,在将由六方晶构成的半导体薄膜层的岛109接合于移动目的地基板301上的形态下,半导体薄膜层的岛109的l1长度的边(即最长的边)与六方晶的<1

‑

100>方向大致平行。

[0244]

再者,母材基板101也可为绝缘体上硅(silicon on insulator,soi)基板。另外,

也可为将母材基板101与半导体薄膜层设为同种材料的基板。例如,在半导体薄膜层为iii族氮化物半导体的情况下,母材基板101可为例如在gan基板上设置有si(111)层的基板。在将在gan基板上设置有si(111)的基板设为母材基板101的情况下,gan可为绝缘基板(半绝缘性基板或高电阻基板),也可为导电性基板(掺杂有杂质的基板)。

[0245]

作为其他例子,母材基板101可为例如将si(111)层晶片接合于石英基板或蓝宝石基板等包含氧化物材料、sin或aln等氮化物材料、或者半导体材料的基板上而成的基板。

[0246]

(实验例)

[0247]

图13a是作为母材基板101的si(111)基板上所形成的gan半导体薄膜层的岛的显微镜照片。图13a是将半导体薄膜层的岛的至少正下方的si(111)基板的表面区域蚀刻去除后的状态的显微镜照片,所述半导体薄膜层的岛在与si(111)的<112>方向大致平行或者与gan半导体薄膜层的<1

‑

100>方向大致平行的方向上具有长边。在半导体薄膜层的岛的至少正下方区域中,在半导体薄膜层的岛与si(111)基板之间形成有空隙。

[0248]

图13b是相对于母材基板101的结晶方向的半导体薄膜层的岛的长边的方向与图13a不同的、gan半导体薄膜层的岛的显微镜照片。图13b示出了经过对半导体薄膜层的岛的至少正下方的si(111)基板的表面区域进行蚀刻的步骤之后的状态,所述半导体薄膜层的岛在与si(111)的<112>方向大致垂直或者与gan半导体薄膜层的<1

‑

100>方向大致垂直的方向上具有长边。如图13b所示,在半导体薄膜层的岛的至少正下方区域中,残存有在半导体薄膜层的岛与si(111)基板之间未形成空隙的区域。

[0249]

再者,图13b所示的样本的蚀刻时间为图13a所示的样本的蚀刻时间的约3倍。图13b的由(1)表示的区域的颜色看起来深,所述颜色看起来深的区域为未形成空隙的区域。如图13b所示,即便对图13b所示的样本进行相当长时间的蚀刻,在半导体薄膜层的岛的正下方区域中,也残存有在半导体薄膜层的岛与si(111)基板之间未形成空隙的区域。

[0250]

图13b的由(2)表示的区域为固定层。图13b的由(3)表示的区域为半导体薄膜层。在图13b的由(4)表示的区域中,可确认到在半导体薄膜层的岛中产生了蚀刻损伤。

[0251]

如以上所说明那样,通过发明人的实验可确认到,为了将六方晶的半导体薄膜层(例如gan、inn、aln、gan/al

x

ga1‑

x

n/in

x

ga1‑

x

n等的层叠;sic、zno等的半导体薄膜层)的岛自第一基板(si(111)基板)分离而在六方晶的半导体薄膜层的岛的正下方的整个区域中,在半导体薄膜层的岛与第一基板之间形成空隙,为此,理想的是使半导体薄膜层的岛的长边的方向至少与si(111)的<112>的方向大致平行,或者与六方晶(gan磊晶层)的<1

‑

100>的方向大致平行。

[0252]

图14是在发明人所进行的实验中,将长边与<1

‑

100>方向大致平行的半导体薄膜层的岛接合于移动目的地基板301的状态的显微镜照片。如图14所示,在半导体薄膜层的岛上残留有固定层114的一部分(被覆半导体薄膜层的岛的上表面及短边的侧面的一部分区域的固定层)。

[0253]

在图14所示的显微镜照片中,接合于移动目的地基板301的半导体薄膜层的岛中未观察到干涉条纹或色不均,能够确认半导体薄膜层的岛可良好地接合于移动目的地基板301。认为如此那样半导体薄膜层的岛可以良好的状态接合于移动目的地基板301的理由在于:可形成<1

‑

100>方向与半导体薄膜层的岛的长边的方向大致平行的半导体薄膜层的岛,且可在半导体薄膜层的岛与母材基板101之间,至少在半导体薄膜层的岛的正下方区域

中形成空隙,并且在面向空隙的半导体薄膜层的表面未产生由蚀刻步骤造成的损伤。且认为原因在于:通过在半导体薄膜层的岛的正下方区域中形成有空隙的状态下将半导体薄膜层的岛自母材基板101分离,可以良好的状态将半导体薄膜层的岛自母材基板101分离。

[0254]

[使固定层110容易断裂的方法]

[0255]

图15a~图15b是用以说明使固定层110容易断裂的方法的图。如图15a所示,在半导体薄膜层的岛108与母材基板101之间形成空隙的蚀刻步骤中,也可形成遍及较图1e所示的空隙103更广的区域而形成的空隙117。在图15a所示的例子中,在母材基板101上形成有固定层110的区域的一部分中,在固定层110与母材基板101之间形成有空隙117。

[0256]

若在所述状态下对固定层110施加向下的力,则会对固定层110中的、与母材基板101之间存在空隙117的区域的角部(图15a的虚线的椭圆部分)附加大的应力,从而在图15b所示的虚线的部分容易产生龟裂或断裂。

[0257]

图16是表示实际的实验中对固定层110的分离状态进行观察而得的结果的显微镜照片。图16是对自母材基板101分离后的半导体薄膜层的岛108自背面(预定接合面)进行观察而得的显微镜照片。在图16的由a表示的部位具有被覆半导体薄膜层的岛108的侧面的一部分区域的固定层110。图16是自半导体薄膜层的岛的背面进行观察,因此难以观察到固定层110的上表面部分,但图16的由a附近的括号表示的宽度的固定层110是自半导体薄膜层的岛108的侧面a经由半导体薄膜层的岛108的上表面(与图16中所观察到的面为相反侧的面)而到达侧面b。

[0258]

如图16所示,未观察到自半导体薄膜层的岛108的侧面向半导体薄膜层的岛108的外侧延伸存在的固定层110。另外,未观察到超出图16所示的半导体薄膜层的岛108的背面(利用显微镜观察到的面)的高度而延展的固定层110。

[0259]

图17是将图16所示的自母材基板分离后的半导体薄膜层的岛108接合于移动目的地基板301的状态的显微镜照片。在图17所示的半导体薄膜层的岛108的上表面及侧面中残留有固定层110的一部分。如图17所示,自母材基板101分离后的半导体薄膜层的岛108可良好地接合于移动目的地基板301。

[0260]

在图16及图17所示的显微镜观察照片中,设置于半导体薄膜层的岛108的固定层的位置形成于自半导体薄膜层的岛108的中心位置稍向上方偏移的位置,但相对于半导体薄膜层的岛108而形成固定层110的位置也可为半导体薄膜层的岛108的中心线上,也可形成于自中心线偏移的位置。另外,形成固定层110的位置也可为相对于岛108的中心线而倾斜的方向。

[0261]

另外,固定层110也可具有自在相当于第一方向的长度方向上延伸存在的区域的至少一部分区域起,在相当于第二方向的短边方向上延伸的区域。图18a~图18b是表示具有在短边方向上延伸的区域的固定层110的例子的图。图18a所示的固定层110具有自固定层110的长度方向中的同一位置起向两侧延伸的区域。图18b所示的固定层110具有自固定层110的长度方向中的不同位置起向两侧延伸的区域。

[0262]

[半导体薄膜层中的阶差结构的形成]

[0263]

于在半导体薄膜层中形成元件结构的情况下,根据元件结构的功能而在半导体薄膜层中形成阶差。图19a~图19b是示意性地表示将母材基板1001上所形成的半导体薄膜层分割成各别的半导体薄膜层的岛的状态的图。图19a是母材基板1001及半导体薄膜层的岛

的顶视图,图19b是剖面图。半导体薄膜层的岛具有高度各不相同的多个区域(1002a、1002b)。

[0264]

在将形成有此种半导体薄膜层的岛的母材基板1001的表面蚀刻去除而将半导体薄膜层的岛自母材基板分离的步骤中,因区域1002b的厚度小于区域1002a的厚度,故母材基板1001中的区域1002b的周边也因蚀刻而被去除。因在蚀刻前形成抗蚀剂掩模开口部时的掩模开口部的对准精度不为

±

0,故在掩模开口部与岛的外周线之间产生偏移。因此,为确保余裕(margin),需要使抗蚀剂掩模开口部的外周线位于岛的外周线的外侧。其结果,如19b所示那样,在区域1002b的周边的区域中形成槽1003。

[0265]

若形成槽1003,则在槽1003的区域中露出的、区域1002b的正下方的母材基板1001的表面区域的侧面的面积大于区域1002a正下方的母材基板1001的表面区域的侧面的面积。其结果,接触蚀刻液的侧面的面积大的母材基板1001的一部分区域(区域1002b的正下方区域)的通过蚀刻的去除更快速地进行,由此在区域1002b的正下方的母材基板1001中产生阶差。若在半导体薄膜层的岛的正下方具有阶差,则当将半导体薄膜层的岛压向下方(母材基板方向)时,可产生因所述阶差而半导体薄膜层的岛呈锐角弯折而发生龟裂的课题。因此,为解决此种课题,在通过将半导体薄膜层自母材基板分离而制造半导体元件的方法中,优选为在形成半导体薄膜层的步骤中形成未露出至半导体薄膜层的外周的阶差结构。

[0266]

图20a~图20c是表示包括形成有未露出至半导体薄膜层的岛的外周的阶差结构的半导体薄膜层的岛920的半导体元件的图。图20a是半导体元件的顶视图,图20b是a

‑

a线剖面图,图20c是b

‑

b线剖面图。在图20a~图20c中,在移动目的地基板931上接合有半导体薄膜层的岛920,所述半导体薄膜层的岛920中形成有在表面露出有p型半导体层的区域921、在表面露出有n型半导体层的凹状的区域922、及在表面露出有p型半导体层的外周壁923。

[0267]

图21a~图21i是用以说明制造图20a~图20c所示的半导体元件的方法的图。此处,以发光二极管(light emitting diode,led)结构为例进行说明,但本制造方法并不限定于制造具有led结构的半导体元件的方法,可适用于制造包括各种元件结构的半导体元件的方法。

[0268]

图21a中的母材基板901是用以使led半导体层(例如gan等的iii族氮化物半导体层的层叠结构)进行磊晶成长的母材基板,且例如为si基板。图21a中的虚线的区域是预定形成半导体薄膜层的多个岛920的区域。

[0269]

图21b是图21a的a

‑

a线剖面图。如图21b所示,半导体薄膜层的岛920具有在表面露出有p型半导体层的区域921、将p型半导体层蚀刻去除而在表面露出有n型半导体层的区域922、及在表面露出有p型半导体层的外周壁923。

[0270]

如图21c所示,在母材基板901上分割成各别的半导体薄膜层的岛920。继而,以将露出有p型半导体层的区域921、露出有n型半导体层的区域922及外周壁923的表面的至少一部分区域与母材基板901结合的方式形成固定层928。图21d是经分割形成的岛920的周边的剖面图,且示出了形成有将岛920与母材基板901结合的固定层928的状态。在图21c中图示了6个半导体薄膜层的岛920,但半导体薄膜层的岛920的个数、间距、形状、尺寸等可适当设计。在露出有n型半导体层的区域922中,以阶差未露出至半导体薄膜层的岛920的外周的方式设置有外周壁923,因此在半导体薄膜层的岛920的周围的母材基板901的区域中,未形

成反映出半导体薄膜层的岛920所包括的元件结构的阶差。

[0271]

在对形成半导体薄膜层的岛920的预定区域以外的半导体薄膜层进行蚀刻而形成半导体薄膜层的岛920的步骤中,可应用标准的光刻及蚀刻步骤。虽未图示,但在所述步骤后,也可在露出有p型半导体层的区域921的表面的一部分区域及露出有n型半导体层的区域922的表面的一部分区域中形成电极触点。在电极触点的形成中,例如形成可形成欧姆接触(ohmic contact)的金属薄膜层,且为了形成低电阻的电极触点,可适当地执行电极触点烧结(sinter)步骤。

[0272]

继而,如图21e所示,在母材基板901的表面中,通过蚀刻而至少将半导体薄膜层的岛920的正下方的母材基板901的表面区域去除。在将半导体薄膜层的岛920的正下方的母材基板901的表面区域蚀刻去除的步骤中,理想的是使用母材基板901的表面区域的蚀刻速度较半导体薄膜层的蚀刻速度快的蚀刻液或蚀刻气体。在所述蚀刻步骤中,在半导体薄膜层的岛920与母材基板901之间形成空隙(图21e中的斜线区域)。

[0273]

继而,如图21f所示,将半导体薄膜层的岛920自第一基板分离。虽省略图示,但在所述步骤中可使用对半导体薄膜层的岛进行暂时接着或吸附的结构体(例如所述拾取基板)。在图21f所示的例子中,将岛920分离后,固定层928的一部分残留于母材基板901。

[0274]

继而,如图21g所示,将自母材基板901分离后的半导体薄膜层的岛920接合于移动目的地基板931上。在将半导体薄膜层的岛920接合于移动目的地基板931上的步骤中,不使用接着剂而将半导体薄膜层的岛920压接于移动目的地基板931上。在将半导体薄膜层的岛920接合于移动目的地基板931上的步骤之前,也可执行对半导体薄膜层的岛920的接合面及移动目的地基板931的表面的表面处理步骤。虽未图示,但也可在半导体薄膜层的岛920与移动目的地基板931之间(至少半导体薄膜层的正下方区域)设置其他材料层。再者,在将半导体薄膜层的岛920接合于移动目的地基板931上的步骤中,理想的是不使用接着剂的接合,但也可使用包含接着剂的膏或片材来进行接合。

[0275]

继而,如图21h所示,在将半导体薄膜层的岛920接合于移动目的地基板931之后,形成层间绝缘膜及配线等半导体元件所必需的结构。例如在不需要用以降低电极与半导体薄膜层的岛920的表面的接触电阻的烧结的情况下、或烧结温度低的情况下,在将半导体薄膜层的岛920接合于移动目的地基板931之后在固定层928中形成开口,在开口内的露出有p型半导体层的区域921中形成电极924,在露出有n型半导体层的区域922中形成电极925,并形成与电极924及电极925连接的配线层927。进而,也可形成包含所述固定层928的一部分的层间绝缘膜926。例如,也可在固定层928的一部分上设置层间绝缘膜926。

[0276]

在将多个岛920接合于移动目的地基板931的情况下,也可通过配线层927而将多个岛920上分别所形成的电极924及电极925加以连接。多个岛920可为将既定尺寸的一个半导体元件分割成多个小尺寸的要素半导体元件(多个小尺寸的岛)而成。多个小尺寸要素半导体元件可全部包括相同的结构,也可全部为相同尺寸。通过所述方式,如下所述那样抑制温度上升故而优选。

[0277]

在大尺寸的一个半导体元件中,运行时的发热大,尤其在中心区域中产生的热的逸散差,因此中心区域中的元件的温度上升大。相对于此,在将一个半导体元件分割成多个小尺寸要素半导体元件的情况下,分割出的要素半导体元件为小尺寸,且各要素半导体元件通过热传导性高的金属材料的配线层927而连接,由此,各要素半导体元件中所产生的热

经由移动目的地基板931及配线层927而效率良好地逸散。其结果,各小尺寸要素半导体元件的温度上升得到抑制。

[0278]

另外,因将作为半导体薄膜层的多个要素半导体元件接合于移动目的地基板931上,可通过金属薄膜配线层而将各小尺寸要素半导体元件加以连接,因此可实现高密度集成。其结果,即便将一个半导体元件分割成多个要素半导体元件,也可获得紧凑的半导体元件。此种形态尤其对于流动大电流的半导体元件、例如使用si、sic、gan、ga2o3、金刚石等半导体材料的功率半导体元件而言为优选的形态。

[0279]

再者,在参照图21a~图21h进行了说明的制造半导体元件的方法中,在图21d中例示了形成固定层928的情况,但也可不形成固定层928而执行图21e及以后的步骤。所述情况下,例如也可如图21i所示,在将拾取基板930固定于岛920的表面(例如露出有p型半导体层的区域921及外周壁923的表面)的状态下,形成由斜线表示的空隙,并在形成空隙后将拾取基板930提起,由此将岛920自母材基板901分离。在图21i的状态中,也可通过拾取基板930以外的外部装置来固定岛920。

[0280]

如此,在未形成固定层928的情况下,将半导体薄膜层的岛920接合于移动目的地基板931之后,在露出有p型半导体层的区域921中形成电极924,在露出有n型半导体层的区域922中形成电极925。另外,形成对露出有p型半导体层的区域921及露出有n型半导体层的区域922的至少一部分区域进行覆盖,并且具有使电极924及电极925的一部分露出的开口部的层间绝缘膜926,并形成与电极924及电极925连接的配线层927。

[0281]

以上,使用实施方式对本发明进行了说明,但本发明的技术范围并不限定于所述实施方式所记载的范围,在其主旨的范围内可进行各种变形及变更。另外,通过多个实施方式的任意组合而产生的新的实施方式也包含于本发明的实施方式中。通过组合而产生的新的实施方式的效果兼具原本的实施方式的效果。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。