1.本发明涉及显示装置。

背景技术:

2.近年来,作为显示元件,使用了微小尺寸的发光二极管(微型led(micro led))的显示器备受关注(例如,参照专利文献1)。多个发光二极管与阵列基板(在专利文献1中为驱动器背板)连接,阵列基板具备用于驱动发光二极管的像素电路(在专利文献1中为电子控制电路)。作为微小尺寸的发光二极管已知有纳米线led(例如,参照专利文献2)。纳米线led由在半导体基板上成长的多条半导体纳米线构成。

3.现有技术文献

4.专利文献

5.专利文献1:日本特表2017

‑

529557号公报

6.专利文献2:日本特表2011

‑

527519号公报

技术实现要素:

7.发明要解决的技术问题

8.纳米线led在相对于与半导体基板垂直的方向倾斜的方向上具有光强度的峰值。因此,当将纳米线led应用于显示装置时,存在从纳米线led射出的光的取出效率降低的可能性。

9.本发明的目的在于提供可以提高光的取出效率的显示装置。

10.用于解决技术问题的手段

11.本发明的一方式的显示装置具有:基板;设置于所述基板的多个像素;以及设置于多个所述像素中的各个像素的多个无机发光元件,所述无机发光元件具有:半导体基板,具有与所述基板对置的第一面、以及凸状地设置于所述第一面的相反侧的第二面;以及多条半导体纳米线,设置于所述第一面,并在垂直于所述第一面的方向上延伸。

附图说明

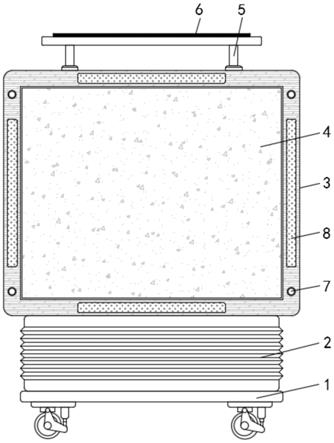

12.图1是示意性地示出第一实施方式所涉及的显示装置的俯视图。

13.图2是示出多个像素的俯视图。

14.图3是示出像素电路的电路图。

15.图4是图1的iv

‑

iv’剖视图。

16.图5是发光元件的俯视图。

17.图6是图5的vi

‑

vi’剖视图。

18.图7是示意性地示出相邻的两个发光元件的剖视图。

19.图8是第一变形例所涉及的发光元件的俯视图。

20.图9是第二变形例所涉及的发光元件的俯视图。

21.图10是示意性地示出第三变形例所涉及的发光元件的剖视图。

22.图11是示意性地示出第四变形例所涉及的发光元件的剖视图。

23.图12是示意性地示出第五变形例所涉及的发光元件的剖视图。

24.图13是示意性地示出第六变形例所涉及的发光元件的剖视图。

25.图14是示意性地示出第二实施方式所涉及的发光元件的剖视图。

具体实施方式

26.参照附图对用于实施本发明的方式(实施方式)进行详细说明。本发明并不限定于下面的实施方式中记载的内容。此外,下面记载的构成要素包括本领域技术人员容易想到的要素、实质上相同的要素。而且,下面记载的构成要素可以适当组合。需要指出,公开仅为一个例子,本领域技术人员能够容易地想到的保持了发明的宗旨的适当变更当然包含在本发明的范围内。此外,为了更清楚地进行说明,附图存在和实际的情况相比示意性地示出各部的宽度、厚度、形状等的情况,但是,这仅为一个例子,并非对本发明的解释进行限定。此外,在本说明书和各图中,关于上述的附图,对与前述的要素相同的要素标注相同的标记,并适当省略详细的说明。

27.(第一实施方式)

28.图1是示意性地示出第一实施方式所涉及的显示装置的俯视图。如图1所示,显示装置1包括阵列基板2、像素pix、驱动电路12、驱动ic(integrated circuit:集成电路)210、以及阴极布线60。阵列基板2是用于驱动各像素pix的驱动电路基板,也被称为背板或有源矩阵基板。阵列基板2具有基板21、多个晶体管、多个电容及各种布线等。

29.如图1所示,显示装置1具有显示区域aa、以及周边区域ga。显示区域aa是与多个像素pix重叠配置并显示图像的区域。周边区域ga是与多个像素pix不重叠的区域,配置于显示区域aa的外侧。

30.多个像素pix在基板21的显示区域aa中排列于第一方向dx及第二方向dy。在本说明书中,第一方向dx及第二方向dy是相对于基板21的表面平行的方向。第一方向dx与第二方向dy正交。其中,第一方向dx与第二方向dy也可以非正交地交叉。第三方向dz是与第一方向dx及第二方向dy正交的方向。第三方向dz例如与基板21的法线方向对应。需要指出,下面,俯视图示出从第三方向dz观察时的位置关系。

31.驱动电路12是基于来自驱动ic210的各种控制信号驱动多条栅极线(例如,发光控制扫描线bg、复位控制扫描线rg、初始化控制扫描线ig及写入控制扫描线sg(参照图3))的电路。驱动电路12依次或同时选择多条栅极线,并向所选择的栅极线供给栅极驱动信号。由此,驱动电路12选择栅极线所连接的多个像素pix。

32.驱动ic210是控制显示装置1的显示的电路。驱动ic210作为cog(chip on glass:玻璃基板芯片)被安装于基板21的周边区域ga。并不限定于此,驱动ic210也可以作为cof(chip on film:覆晶薄膜)被安装于基板21的周边区域ga所连接的布线基板之上。需要指出,基板21所连接的布线基板例如是柔性印刷基板、刚性基板。

33.阴极布线60设置于基板21的周边区域ga。阴极布线60设置为包围显示区域aa的多个像素pix及周边区域ga的驱动电路12。多个发光元件3的阴极与共用的阴极布线60电连接,并被供给固定电位(例如,接地电位)。更具体而言,发光元件3的阴极端子38(参照图4)

经由阴极电极23而与阴极布线60连接。需要指出,阴极布线60在局部具有狭缝,在基板21上也可以由两条不同的布线形成。

34.图2是示出包括多个像素的像素的俯视图。如图2所示,一个像素pix包括多个像素11。例如,像素pix具有第一像素11r、第二像素11g、以及第三像素11b。第一像素11r显示作为第一色的原色的红色。第二像素11g显示作为第二色的原色的绿色。第三像素11b显示作为第三色的原色的蓝色。下面,在无需分别区分第一像素11r、第二像素11g、以及第三像素11b的情况下,称为像素11。

35.像素11分别具有发光元件3r、3g、3b、以及反射板rf。需要指出,在下面的说明中,在无需区别说明发光元件3r、3g、3b的情况下,仅表示为发光元件3。显示装置1通过在第一像素11r、第二像素11g及第三像素11b中对应于发光元件3r、3g、3b而射出不同的光(例如,红色、绿色、蓝色的光)来显示图像。

36.发光元件3设置于多个像素pix中的各个像素pix。在俯视图中,发光元件3是具有数μm以上、300μm以下左右的大小的无机发光二极管(led:light emitting diode:发光二极管)芯片,一般而言,一个芯片尺寸为100μm以上的元件是迷你led(mini led),数μm以上且小于100μm的尺寸的元件是微型led(micro led)。在本发明中,也可以使用任意尺寸的led,只要根据显示装置1的画面尺寸(一像素的大小)来区分使用即可。在各像素具备微型led的显示装置1也称为微型led显示装置。需要指出,微型led的微型并不限定发光元件3的大小。

37.如图2所示,在一个像素pix中,第一像素11r和第三像素11b排列于第一方向dx上。此外,第二像素11g和第三像素11b排列于第二方向dy上。需要指出,第一色、第二色、第三色分别不限于红色、绿色、蓝色,也可以选择互补色等的任意的颜色。需要指出,多个发光元件3r、3g、3b也可以射出四种颜色以上的不同的光。此外,多个像素11的配置并不限定于图2所示的构成。例如,第一像素11r也可以与第二像素11g在第一方向dx上相邻。此外,第一像素11r、第二像素11g及第三像素11b也可以按该顺序在第一方向dx上反复排列。

38.图3是示出像素电路的电路图。图3所示的像素电路pica设置于各个第一像素11r、第二像素11g及第三像素11b。像素电路pica是设置于基板21并将驱动信号(电流)向发光元件3r、3g、3b供给的电路。需要指出,在图3中,关于像素电路pica的说明可以应用于第一像素11r、第二像素11g及第三像素11b分别具有的像素电路pica。

39.如图3所示,像素电路pica包括发光元件3(发光元件3r、3g、3b)、五个晶体管、以及两个电容。具体而言,像素电路pica包括发光控制晶体管bct、初始化晶体管ist、写入晶体管sst(第二晶体管)、复位晶体管rst及驱动晶体管drt(第一晶体管)。一部分的晶体管也可以被邻接的多个像素11共享。

40.像素电路pica具有的多个晶体管分别由n型tft(thin film transistor:薄膜晶体管)构成。但是,并不限定于此,各晶体管也可以分别由p型tft构成。

41.发光控制扫描线bg与发光控制晶体管bct的栅极连接。初始化控制扫描线ig与初始化晶体管ist的栅极连接。写入控制扫描线sg与写入晶体管sst的栅极连接。复位控制扫描线rg与复位晶体管rst的栅极连接。

42.发光控制扫描线bg、初始化控制扫描线ig、写入控制扫描线sg及复位控制扫描线rg分别与驱动电路12(参照图1)连接。驱动电路12向发光控制扫描线bg、初始化控制扫描线

ig、写入控制扫描线sg及复位控制扫描线rg分别供给发光控制信号vbg、初始化控制信号vig、写入控制信号vsg及复位控制信号vrg。

43.驱动ic210(参照图1)向第一像素11r、第二像素11g及第三像素11b的各自的像素电路pica时分地供给影像信号vsig。复用器等的开关电路设置在第一像素11r、第二像素11g及第三像素11b的各列与驱动ic210之间。影像信号vsig经由影像信号线l2而被供给至写入晶体管sst。此外,驱动ic210经由复位信号线l3将复位电源电位vrst供给至复位晶体管rst。驱动ic210经由初始化信号线l4将初始化电位vini供给至初始化晶体管ist。

44.发光控制晶体管bct、初始化晶体管ist、写入晶体管sst、以及复位晶体管rst作为选择两节点间的导通和非导通的开关元件而发挥功能。驱动晶体管drt作为根据栅极与漏极之间的电压而控制流动至发光元件3的电流的电流控制元件而发挥功能。

45.发光元件3的阴极(阴极端子38)与阴极电源线l10连接。此外,发光元件3的阳极(接触层37)经由驱动晶体管drt及发光控制晶体管bct与阳极电源线l1连接。在阳极电源线l1被供给阳极电源电位pvdd。在阴极电源线l10被供给阴极电源电位pvss。阳极电源电位pvdd是高于阴极电源电位pvss的电位。阴极电源线l10包括阴极布线60。

46.此外,像素电路pica包括电容cs1及电容cs2。电容cs1是形成于驱动晶体管drt的栅极与源极之间的电容。电容cs2是形成于驱动晶体管drt的源极及发光元件3的阳极与阴极电源线l10之间的附加电容。

47.在复位期间,根据发光控制扫描线bg及复位控制扫描线rg的电位,发光控制晶体管bct成为断开(非导通状态),复位晶体管rst成为接通(导通状态)。由此,驱动晶体管drt的源极固定于复位电源电位vrst。复位电源电位vrst是复位电源电位vrst与阴极电源电位pvss的电位差小于发光元件3开始发光的电位差的电位。

48.然后,根据初始化控制扫描线ig的电位,初始化晶体管ist成为接通。经由初始化晶体管ist,驱动晶体管drt的栅极被固定于初始化电位vini。此外,驱动电路12使发光控制晶体管bct成为接通、使复位晶体管rst成为断开。驱动晶体管drt的源极电位成为(vini

‑

vth)时变为断开,各像素11各自的驱动晶体管drt的阈值电压vth的偏差被抵消。

49.然后,在影像信号写入动作期间,发光控制晶体管bct成为断开,初始化晶体管ist成为断开,写入晶体管sst成为接通。影像信号vsig被输入驱动晶体管drt的栅极。

50.然后,在发光动作期间,发光控制晶体管bct成为接通,写入晶体管sst成为断开。从阳极电源线l1经由发光控制晶体管bct向驱动晶体管drt供给阳极电源电位pvdd。驱动晶体管drt向发光元件3供给对应于栅极源极间的电压的电流。发光元件3以对应于该电流的亮度发光。

51.需要指出,上述的图3所示的像素电路pica的构成仅为一例,可以适当变更。例如一个像素11上的布线的数量及晶体管的数量也可以不同。

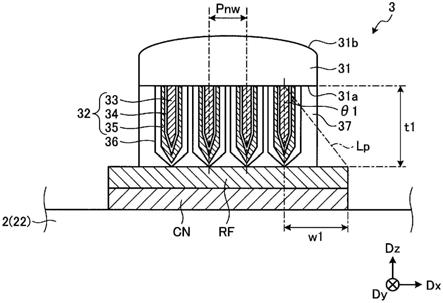

52.然后,对显示装置1的剖面构成进行说明。图4是图1的iv

‑

iv’剖视图。如图4所示,在显示装置1中,发光元件3设置于阵列基板2之上。阵列基板2具有基板21、阳极电极22、对置电极24、连接电极24a、反射板rf、连接层cn、各种晶体管、各种布线及各种绝缘膜。

53.基板21是绝缘基板,例如使用石英、无碱玻璃等的玻璃基板、或聚酰亚胺等的树脂基板。

54.需要指出,在本说明书中,在垂直于基板21的表面的方向上,将从基板21朝向发光

元件3的方向设为“上侧”或仅设为“上”。此外,将从发光元件3朝向基板21的方向设为“下侧”或仅设为“下”。此外,在表现在某结构体之上配置其它结构体的方式时,在仅记载为“之上”的情况下,只要没有特别的限定,则包括以与某结构体相接的方式在正上方配置其它结构体的情况、以及在某结构体的上方还隔着另外的结构体来配置其它结构体的情况的双方。

55.底涂膜90设置于基板21之上。底涂膜90、绝缘膜91、92、93及绝缘膜95、96是无机绝缘膜,例如是氧化硅(sio2)、氮化硅(sin)等。

56.驱动晶体管drt设置于底涂膜90之上。需要指出,在图4中,示出了多个晶体管中的驱动晶体管drt及写入晶体管sst,但是,像素电路pica所包括的发光控制晶体管bct、初始化晶体管ist及复位晶体管rst也具有与驱动晶体管drt同样的层叠结构。此外,在周边区域ga设置有驱动电路12所包括的晶体管tr。

57.驱动晶体管drt具有半导体层25、第一栅极电极26、第二栅极电极27、源电极28及漏电极29。第一栅极电极26设置于底涂膜90之上。绝缘膜91覆盖第一栅极电极26而设置于底涂膜90之上。半导体层25设置于绝缘膜91之上。半导体层25例如使用多晶硅。但是,半导体层25并不限定于此,也可以是微晶氧化物半导体、无定形氧化物半导体、低温多晶硅等。

58.绝缘膜92覆盖半导体层25而设置于绝缘膜91之上。第二栅极电极27设置于绝缘膜92之上。在半导体层25,沟道区域25a设置于被第一栅极电极26和第二栅极电极27夹着的部分。

59.此外,第一布线27a设置于与第二栅极电极27同层。第一栅极电极26、第二栅极电极27及第一布线27a例如由铝(al)、铜(cu)、银(ag)、钼(mo)或它们的合金膜构成。驱动晶体管drt是设置有第一栅极电极26及第二栅极电极27的双栅结构。但是,并不限定于此,驱动晶体管drt也可以是仅设置有第一栅极电极26的底栅结构,也可以是仅设置有第二栅极电极27的顶栅结构。

60.源电极28及漏电极29经由分别设置于绝缘膜92、93的接触孔与半导体层25连接。源电极28及漏电极29例如是作为钛和铝的层叠结构的tialti或tial的层叠膜。

61.通过隔着绝缘膜93而对置的第一布线27a和源电极28形成电容cs1。此外,电容cs1还包括隔着绝缘膜92而对置的半导体层25和第一布线27a所形成的电容。

62.需要指出,在图4中,对多个晶体管中的驱动晶体管drt的构成进行了说明,但是,写入晶体管sst等的像素电路pica所包括的晶体管以及设置于周边区域ga的晶体管tr也是与驱动晶体管drt同样的剖面构成,在此省略其详细说明。

63.绝缘膜94覆盖驱动晶体管drt而设置于绝缘膜93之上。绝缘膜94使用感光性丙烯酸等的有机材料。绝缘膜94是平坦化膜,可以使由驱动晶体管drt、各种布线所形成的凹凸平坦化。

64.在绝缘膜94之上依次层叠对置电极24、绝缘膜95、阳极电极22、绝缘膜96。对置电极24例如由ito(indium tin oxide:铟锡氧化物)等的具有透光性的导电性材料构成。连接电极24a设置于与对置电极24同层。连接电极24a在设置于绝缘膜94的接触孔的底部与源电极28连接。

65.阳极电极22经由设置于绝缘膜95的接触孔与连接电极24a及源电极28电连接。由此,阳极电极22与驱动晶体管drt电连接。阳极电极22例如为钼(mo)、铝(al)的层叠结构。

66.在隔着绝缘膜95对置的阳极电极22与对电极24之间形成电容cs2。绝缘膜96覆盖阳极电极22而设置。绝缘膜96覆盖阳极电极22的周缘部,使相邻的像素11的阳极电极22绝缘。

67.绝缘膜96在与阳极电极22重叠的位置具有用于安装发光元件3的开口。在绝缘膜96的开口的区域,连接层cn及反射板rf设置于阳极电极22之上。

68.连接层cn例如是锡(sn)、铟(in)等的低熔点金属,电连接反射板rf和阳极电极22。反射板rf为银(ag)或铝(al)。但是,连接层cn及反射板rf的材料并不限定于此,也可以使用其它金属或合金。

69.发光元件3具有半导体基板31、半导体纳米线32、接触层37及阴极端子38。需要指出,多条半导体纳米线32均具有俯视图中的尺寸为1μm以下的纳米结构,第三方向dz上的长度与第一方向dx的宽度相比足够大。各发光元件3被安装为接触层37与反射板rf相接。阳极电极22经由连接层cn、反射板rf、接触层37向多条半导体纳米线32的p型半导体35供给阳极电源电位pvdd。

70.元件绝缘膜97设置于多个发光元件3之间。元件绝缘膜97由树脂材料形成。元件绝缘膜97至少覆盖发光元件3的侧面,在发光元件3的阴极端子38之上未设置元件绝缘膜97。元件绝缘膜97的上表面与阴极端子38的外缘连接并平坦地形成。

71.阴极电极23覆盖多个发光元件3及元件绝缘膜97,与多个发光元件3电连接。更具体而言,阴极电极23跨元件绝缘膜97的上表面、以及阴极端子38的上表面而设置。阴极电极23向阴极端子38供给阴极电源电位pvss。阴极电极23为透光性导电膜,例如使用ito等。由此,可以将来自发光元件3的射出光高效地取出到外部。

72.阴极电极23经由设置于显示区域aa的外侧的接触孔h11与设置于阵列基板2侧的阴极布线60连接。具体而言,接触孔h11设置于元件绝缘膜97及绝缘膜94,阴极布线60设置于接触孔h11的底面。阴极布线60设置于绝缘膜93之上。也就是说,阴极布线60与源电极28及漏电极29设置于同层,由相同材料形成。阴极电极23从显示区域aa至周边区域ga连续地设置,在接触孔h11的底部与阴极布线60连接。

73.在阴极电极23之上,隔着粘结层84设置圆偏振板7。换言之,在垂直于基板21的方向上,多个发光元件3设置在基板21与圆偏振板7之间。圆偏振板7具备例如直线偏振板、以及设置于直线偏振板的一个表面侧的1/4相位差板(也称为1/4波长板)。与直线偏振板相比,1/4相位差板设置于更靠近基板21的位置。

74.例如,外部光(入射光)通过直线偏振板,从而被变更为直线偏振光。直线偏振光通过1/4相位差板,从而被变更为圆偏振光。圆偏振光被阵列基板2的布线反射,成为与入射光方向相反的圆偏振光(反射光)。反射光再次通过1/4相位差板,从而成为与入射时正交的直线偏振光,被直线偏振板吸收。由此,在显示装置1中,外部光的反射得以抑制。

75.然后,对发光元件3的详细构成进行说明。图5是发光元件的俯视图。如图5所示,发光元件3的半导体基板31在俯视图中具有四边形形状。半导体基板31例如由n型gan构成。多条半导体纳米线32在俯视图中均具有的六边形形状。多条半导体纳米线32通过在n型gan的c面上成长,从而形成具有与n型gan的m面对应的六个侧面32s的六棱柱状。需要指出,在图5中,为了易于观察附图,示出了25个半导体纳米线32的排列,但是,配置于一个发光元件3的半导体纳米线32的数量并不限定于此,只要设置有两条以上的半导体纳米线32即可。

76.这里,在图5中,示意性地示出了半导体纳米线32的各自的配光特性lcx、lcy。配光特性lcx表示由第一方向dx和第三方向dz所规定的平面中的半导体纳米线32的配光特性。配光特性lcy表示由第二方向dy和第三方向dz所规定的平面中的半导体纳米线32的配光特性。半导体纳米线32在相对于第三方向dz倾斜的方向d1、d2上具有发光强度的峰值。

77.多条半导体纳米线32以侧面32s对置的方式而交错配置。换言之,多条半导体纳米线32排列为三角栅格状。通过这样的配置,一条半导体纳米线32的第三方向dz的光与其它半导体纳米线32的具有发光强度的峰值的方向d1、d2的光相互重叠。由此,发光元件3对多条半导体纳米线32的第三方向dz的光进行补偿,作为整体在半导体基板31的中央部分具有发光强度的峰值。

78.图6是图5的vi

‑

vi’剖视图。如图6所示,半导体基板31具有第一面31a、以及第一面31a的相反侧的第二面31b。第一面31a与阵列基板2对置。换言之,第一面31a与基板21对置。第二面31b凸状地设置于第一面31a的相反侧。第二面31b是具有向第三方向dz凸状地弯曲的曲面的形状。从多条半导体纳米线32向第三方向dz射出的光透过半导体基板31的第二面31b。光的前进方向根据半导体基板31与阴极电极23的折射率的差而朝向平行于第三方向dz的方向。由此,可以抑制在从半导体基板31的中央部分朝向周缘部分的方向上扩散的光,多条半导体纳米线32作为整体可以抑制在半导体基板31的中央部分发光强度的降低。

79.需要指出,半导体基板31的第二面31b的制造方法并没有特别的限定。例如,在表面被图案化的蓝宝石基板之上形成半导体基板31,并去除蓝宝石基板,从而可以形成第二面31b的凸形状。此外,第二面31b的形状可以适当变更。例如,第二面31b的整体由曲面构成,但是,也可以在第二面31b的局部设置具有曲面的凸部。

80.多条半导体纳米线32设置于半导体基板31的第一面31a,并在第三方向dz上延伸。多条半导体纳米线32分别具有n型半导体33、活性层34及p型半导体35。多条半导体纳米线32分别作为发光元件而发挥功能,与共用的阳极电极22及阴极电极23电连接,作为整体构成为一个发光元件3。

81.n型半导体33是在半导体基板31之上生长的柱状的纳米线,例如n型gan。活性层34覆盖n型半导体33的至少侧面,并设置于n型半导体33与p型半导体35之间。作为活性层34,为了高效化,也可以采用周期性地层叠由多个原子层构成的阱层和障壁层的多量子阱结构(mqw结构)。此外,活性层34优选设置为覆盖n型半导体33的侧面及下端部。由此,可以确保活性层34的面积。

82.p型半导体35设置为与n型半导体33及活性层34的至少侧面对置。需要指出,p型半导体35优选设置为覆盖活性层34的侧面及下端部。p型半导体35例如是p型gan。需要指出,多条半导体纳米线32的材料并不限定于gan,也可以是铝铟镓磷(alingap)或铝镓砷(algaas)或镓砷磷(gaasp)等的化合物半导体。

83.保护层36设置为覆盖各p型半导体35。接触层37覆盖多条半导体纳米线32及保护层36,并设置于半导体基板31的第一面31a。多条半导体纳米线32的p型半导体35隔着保护层36及接触层37与反射板rf电连接。需要指出,在图6中,保护层36的下端部与反射板rf相接,但是,并不限定于此。接触层37也可以设置为覆盖保护层36的下端部。

84.作为保护层36的材料可以使用过渡金属氧化物。作为过渡金属氧化物,例如可以列举出包括氧化钨(wo3)、氧化钼(moo3)、氧化钒(v2o5)、氧化镍(niox)、氧化铼(reo3)、氧

化钌(ruo2)中的一种或两种以上的材料。接触层37例如可以使用ito等的透光性导电材料。构成保护层36的过渡金属氧化物具有比构成接触层37的ito高的功函数。因此,抑制作为金属层的反射板rf与p型半导体35的接触电阻,可以良好地电连接发光元件3与反射板rf。

85.将多条半导体纳米线32的在第一方向dx上的配置间距设为配置间距pnw。配置间距pnw是n型半导体33的底面(与第一面31a相接的面)的中心之间的间隔。此外,虚拟线lp是通过n型半导体33的底面的中心且平行于具有半导体纳米线32的发光强度的峰值的方向(例如,图5所示的d1方向)的虚拟线。

86.角度θ1是第三方向dz与虚拟线lp所成的角度。即、角度θ1是半导体纳米线32的发光强度为最大的角度。角度θ1例如是23

°

以上且33

°

以下左右。其中,角度θ1可以根据保护层36、接触层37及元件绝缘膜97等设置于半导体纳米线32的周边的材料的折射率而成为不同的值。

87.反射板rf的第一方向dx的宽度为(配置间距pnw)

×

(半导体纳米线32的数量

‑

1) (2

×

w1)。这里,宽度w1通过w1=t1

×

tanθ1来表示。其中,高度t1为半导体纳米线32的高度,是半导体基板31的第一面31a与反射板rf的上表面之间的在第三方向dz上的距离。由此,从多条半导体纳米线32向阵列基板2侧的倾斜方向射出的光被反射板rf反射而朝向显示面侧射出。由此,显示装置1除了从多条半导体纳米线32向上侧射出的光之外,也可以将朝向阵列基板2侧射出的光取出为显示光。

88.图7是示意性地示出相邻的两个发光元件的剖视图。如图7所示,半导体基板31的第二面31b比元件绝缘膜97的上表面向第三方向dz突出。元件绝缘膜97的上表面平坦地设置于相邻的发光元件3之间。需要指出,元件绝缘膜97并不限定于覆盖接触层37及半导体基板31的侧面的构成,也可以覆盖第二面31b的周缘部。阴极电极23沿第二面31b的凸形状而设置,具有向第三方向dz凸起的形状。

89.保护层36、接触层37、元件绝缘膜97及阴极电极23的各自的折射率小于构成发光元件3的半导体基板31、n型半导体33及p型半导体35的gan的折射率。例如,gan的折射率为2.4左右。保护层36的折射率为2.0以上且2.1以下左右。接触层37的折射率为1.7以上且1.9以下左右。元件绝缘膜97的折射率为1.45以上且1.55以下左右。阴极电极23的折射率为1.7以上且1.9以下左右。

90.即、保护层36的折射率小于半导体基板31及半导体纳米线32的折射率。接触层37的折射率小于保护层36的折射率。元件绝缘膜97的折射率小于接触层37的折射率。在本实施方式中,沿着从多条半导体纳米线32向阵列基板2侧射出的光的路径,折射率按照gan、保护层36、接触层37、元件绝缘膜97的顺序而变小。

91.由此,各层间的折射率的差小于gan与空气(折射率为1)的折射率的差。假设与gan设置为与空气相接的情况相比,可以使各层之间的界面的发生全反射的临界角变大。因此,显示装置1可以抑制从半导体纳米线32射出的光被各层之间的界面全反射。其结果是,显示装置1可以提高发光元件3的光的取出效率。

92.(第一变形例)

93.图8是第一变形例所涉及的发光元件的俯视图。需要指出,在下面的说明中,对和在上述的实施方式中已经说明的要素相同的构成要素标注相同的标记,并省略重复说明。

94.如图8所示,在第一变形例的发光元件3a中,多条半导体纳米线32排列为矩阵状。

即、多条半导体纳米线32排列配置于第一方向dx,并且,排列配置于第二方向dy。即使在这样的配置的情况下,发光元件3a也对多条半导体纳米线32的第三方向dz的光进行补偿,作为整体,在半导体基板31的中央部分具有发光强度的峰值。

95.(第二变形例)

96.图9是第二变形例所涉及的发光元件的俯视图。如图9所示,第二变形例的发光元件3b具有第一组的半导体纳米线32a、以及第二组的半导体纳米线32b。第一组的半导体纳米线32a由设置于半导体基板31的第一面31a的中央部的多条半导体纳米线32构成。第一组的半导体纳米线32a具有交错配置的多条半导体纳米线32。

97.第二组的半导体纳米线32b由配置于半导体基板31的外缘的多条半导体纳米线32构成。具体而言,第二组的半导体纳米线32b具有配置于半导体基板31的四角的四条半导体纳米线32。

98.根据这样的构成,发光元件3b可以通过第一组的半导体纳米线32a确保半导体基板31的中央部处的发光强度。此外,发光元件3b可以通过第二组的半导体纳米线32b抑制半导体基板31的中央部与周缘部的发光强度的差。

99.需要指出,第一组的半导体纳米线32a也可以由配置为矩阵状的多条半导体纳米线32构成。此外,第二组的半导体纳米线32b也可以具有沿着半导体基板31的四边配置的多条半导体纳米线32。

100.(第三变形例)

101.图10是示意性地示出第三变形例所涉及的发光元件的剖视图。如图10所示,在第三变形例的发光元件3c中,第二面31b的剖面形状具有梯形形状。具体而言,第二面31b具有上表面31ba、以及倾斜面31bb。上表面31ba是与第一面31a平行的面。上表面31ba在俯视图中为圆形形状或四边形形状。倾斜面31bb设置为相对于上表面31ba倾斜,并连接上表面31ba与发光元件3c的侧面。

102.即使在本变形例中,透过半导体基板31的倾斜面31bb的光的前进方向也是根据半导体基板31与阴极电极23的折射率的差及阴极电极23与空气的折射率的差,而朝向与第三方向dz平行的方向。

103.(第四变形例)

104.图11是示意性地示出第四变形例所涉及的发光元件的剖视图。如图11所示,第四变形例的发光元件3d与上述的第三变形例相比不同之处在于倾斜面31bb连接上表面31ba与第一面31a的构成。换言之,半导体基板31不具有侧面,且为去除了圆锥形或棱锥形的前端部的形状。上表面31ba在俯视图中为圆形形状或四边形形状。

105.在本变形例中,与第三变形例相比,可以实现半导体基板31的薄型化。需要指出,元件绝缘膜97的上表面设置在与第一面31a相同高度的位置。但是,并不限定于此,元件绝缘膜97也可以设置为覆盖倾斜面31bb的下端侧的局部。

106.(第五变形例)

107.图12是示意性地示出第五变形例所涉及的发光元件的剖视图。如图12所示,在第五变形例的显示装置1中,元件绝缘膜97的上表面97a在多个发光元件3之间设置为朝向阵列基板2凹陷的凹状。阴极电极23跨凸状的半导体基板31的第二面31b及凹状的元件绝缘膜97的上表面97a而连续设置。

108.被反射板rf反射且透过元件绝缘膜97的上表面97a的光的前进方向根据阴极电极23与空气的折射率的差,朝向与第三方向dz平行的方向。由此,在第五变形例中,可以抑制相邻的发光元件3之间的光的混色。此外,显示装置1除了透过半导体基板31的光之外也可以高效地将反射板rf所反射的光提取至显示面侧。

109.(第六变形例)

110.图13是示意性地示出第六变形例所涉及的发光元件的剖视图。如图13所示,在第六变形例的显示装置1中,在相邻的发光元件3之间设置有分隔壁51。分隔壁51是使用折射率高于元件绝缘膜97的感光性透明绝缘材料通过光刻技术而形成的。或者,分隔壁51是使用遮光性材料通过光刻技术及化学铣切而形成的。通过分隔壁51遮蔽多个发光元件3之间的光,因此,可以抑制从多个发光元件3射出的光的混色。

111.分隔壁51的上端部设置于比半导体基板31的第一面31a高的位置。元件绝缘膜97设置于发光元件3与分隔壁51之间,并覆盖发光元件3的侧面和分隔壁51的侧面。元件绝缘膜97的上表面97a在相邻的发光元件3之间设置为将分隔壁51的上端部作为顶部的凸状。阴极电极23覆盖凸状的第二面31b、凸状的元件绝缘膜97的上表面97a及分隔壁51的上端部。元件绝缘膜97的上表面97a设置为凸状,因此,被反射板rf反射且透过元件绝缘膜97的上表面97a的光被聚光。

112.需要指出,可以适当组合上述的第一变形例至第六变形例的构成。第一变形例及第二变形例可以与第三变形例至第六变形例的任一项的构成组合。此外,第三变形例及第四变形例可以与第五变形例或第六变形例的构成组合。

113.(第二实施方式)

114.图14是示意性地示出第二实施方式所涉及的发光元件的剖视图。如图14所示,在第二实施方式的显示装置1a中,发光元件3e的第二面31b设置为向第一面31a侧凹陷的凹状。显示装置1a还具有设置于各发光元件3e的透镜部件52。透镜部件52是由玻璃形成的球透镜。

115.透镜部件52隔着阴极电极23设置于第二面31b之上。第二面31b具有以沿着透镜部件52的曲面而弯曲的曲面,并具有与透镜部件52相同程度的曲率。透镜部件52在俯视图中设置在与多条半导体纳米线32重叠的位置。透镜部件52的外径与发光元件3e的宽度为相同程度。其中,透镜部件52的外径也可以与发光元件3e的宽度不同。透镜部件52的折射率为1.45以上且1.55以下左右。

116.由此,从多条半导体纳米线32向第三方向dz射出的光透过半导体基板31的第二面31b及透镜部件52。光的前进方向根据透镜部件52与空气的折射率的差而朝向与第三方向dz平行的方向。此外,第二面31b设置为凹状,因此,可以容易地实现透镜部件52相对于发光元件3e的定位。

117.以上,对本发明的优选实施方式进行了说明,但是,本发明并不限定于这样的实施方式。在实施方式中公开的内容仅以一例,在不脱离本发明的宗旨的范围内可以进行各种变更。关于在不脱离本发明的宗旨的范围内进行的适当的变更,当然也属于本发明的技术范围。在不脱离上述的各实施方式及各变形例的宗旨的范围内,可以进行构成要素的各种省略、替换及变更中的至少一种。

118.附图标记说明

119.1,1a 显示装置

120.2 阵列基板

121.3,3a、3b、3c、3d、3e、3r、3g、3b 发光元件

122.7 圆偏振板

123.11,pix 像素

124.11r 第一像素

125.11g 第二像素

126.11b 第三像素

127.12 驱动电路

128.21 基板

129.22 阳极电极

130.23 阴极电极

131.31 半导体基板

132.32 半导体纳米线

133.33 n型半导体

134.34 活性层

135.35 p型半导体

136.36 保护层

137.51 分隔壁

138.52 透镜部件

139.rf 反射板

140.cn 连接层

141.sst 写入晶体管

142.drt 驱动晶体管

143.pvdd 阳极电源电位

144.pvss 阴极电源电位

145.l1 阳极电源线

146.l2 影像信号线

147.l3 复位信号线

148.l4 初始化信号线

149.l10 阴极电源线。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。