1.本发明实施例涉及半导体制造领域,尤其涉及一种掩膜版版图和半导体结构。

背景技术:

2.在光刻工艺开始之前,晶圆版图会先通过特定的设备复制到掩膜版上,然后通过光刻设备产生特定波长的光(例如为248纳米的紫外光),将掩膜版上的图形复制到生产所用的物理晶圆上。

3.光刻技术(lithograph)是实现集成电路图案的关键工艺技术。在光刻技术中,将感光材料(光刻胶)涂覆于基底的薄膜上,采用与光刻胶感光特性相应的波段的光,透过具有特定图案的掩膜板照射至光刻胶表面,经显影后形成与掩膜板上的图案相对应的光刻胶图形。在集成电路的后续工艺中,以此光刻胶图形作为阻挡层对其下的薄膜进行选择性刻蚀,便可以将掩膜板上的图案完整地转移到基底的薄膜上。集成电路的图案线宽越细,要求光刻胶的成像分辨率越高,而光刻胶的成像分辨率与曝光光源的波长成反比,因此,缩小曝光光源的波长成为实现细线宽图案的主要途径。

4.随着集成电路的集成度不断提高,集成电路向亚微米、深亚微米方向快速发展,其图案线宽也将越来越细,原先一次曝光的图形,现在需要通过多次曝光来实现,这对半导体工艺的精度提出了更高的要求,且在多层结构中,上层图形和下层图形之间略微的偏差会导致最终的半导体结构存在桥接或者断开的缺陷。

技术实现要素:

5.本发明实施例解决的问题是提供一种掩膜版版图和半导体结构,提高半导体结构的电学性能。

6.为解决上述问题,本发明实施例提供一种掩膜版版图,包括:第一掩膜版版图,包括多个互连层图形,所述互连层图形包括第一子图形、以及位于所述第一子图形一侧的第二子图形和第三子图形;所述第二子图形和第三子图形位于同一版图中,且所述第一子图形,与第二子图形和第三子图形间隔排列,所述第一子图形沿第一方向延伸;所述第二子图形沿第二方向延伸,所述第一方向和第二方向相垂直,且所述第二子图形的延伸方向与所述第一子图形的延伸方向相交;在所述第一方向上,所述第三子图形位于所述第二子图形的至少一侧,且所述第三子图形与所述第二子图形靠近所述第一子图形一侧的端部相连;第二掩膜版版图,包括多个孔图形,所述孔图形位于所述互连层图形所在的区域中,其中,在所述第二子图形中,所述孔图形位于所述第二子图形靠近所述第一子图形一侧的端部。

7.可选的,所述互连层图形还包括:第四子图形,在所述第一方向上与所述第二子图形相间隔,在所述第二方向上与所述第一子图形相间隔,且所述第四子图形位于所述第二子图形背向所述第三子图形的一侧。

8.可选的,在所述第一方向上,所述第三子图形位于所述第二子图形的两侧;所述互连层图形还包括:第四子图形,位于所述第二子图形的一侧,在所述第一方向上与所述第三

子图形相间隔,所述第四子图形在所述第二方向上与所述第一子图形相间隔;第五子图形,位于所述第二子图形的另一侧,在所述第一方向上与所述第三子图形相间隔,所述第五子图形在所述第二方向上与所述第一子图形相间隔。

9.可选的,在所述第一方向上,所述第二子图形至所述第四子图形的距离小于或等于30纳米;在所述第二方向上,所述第四子图形和第一子图形的间距大于50纳米且小于60纳米。

10.可选的,在所述第一方向上,所述第三子图形的长度至少为96纳米。

11.可选的,所述互连层图形还包括:第五子图形,在所述第一方向上,所述第五子图形位于所述第二子图形背向所述第四子图形的一侧,且与所述第三子图形相间隔,在所述第二方向上,所述第五子图形与所述第一子图形相间隔;在所述第一方向上,所述第三子图形至所述第五子图形的距离大于或等于24纳米。

12.可选的,在所述第一方向上,所述第三子图形的长度大于或等于10纳米。

13.可选的,在所述第一方向上,所述第四子图形至相邻第三子图形的距离大于或等于20纳米;所述第五子图形至相邻第三子图形的距离大于或等于20纳米。

14.可选的,在所述第二方向上,所述第一子图形至第二子图形的距离小于或等于50纳米。

15.可选的,在所述第二方向上,所述第二子图形中的孔图形具有朝向所述第一子图形的第一边,所述第二子图形具有朝向所述第二子图形的第二边,所述第一边至所述第二边的距离大于或等于6纳米。

16.相应地,本发明实施例还提供一种半导体结构,包括:基底;互连层,位于所述基底上,所述互连层包括:第一子互连层,所述第一子互连层沿第一方向延伸;第二子互连层,位于所述第一子互连层的一侧的所述基底上,所述第二子互连层与所述第一子互连层间隔排布,所述第二子互连层沿第二方向延伸,所述第一方向与第二方向相垂直,且所述第二子互连层的延伸方向与所述第一子互连层的延伸方向相交;第三子互连层,在所述第一方向上,位于所述第二子互连层的至少一侧,且所述第三子互连层与所述第二子互连层靠近所述第一子互连层一侧的端部相连;多个接触插塞,位于所述互连层上,且所述接触插塞与第二子互连层的顶部接触,其中,在所述第二子互连层上,所述接触插塞位于所述第二子互连层靠近所述第一子互连层一侧的端部。

17.可选的,所述互连层还包括:第四子互连层,位于所述基底上,在所述第一方向上与所述第二子互连层相间隔,在所述第二方向上与所述第一子互连层相间隔,且所述第四子互连层位于所述第二子互连层背向所述第三子互连层的一侧。

18.可选的,在所述第一方向上,所述第三子互连层位于所述第二子互连层的两侧;所述互连层图形还包括:第四子互连层,位于所述第二子互连层的一侧的所述基底上,在所述第一方向上与所述第三子互连层相间隔,所述第四子互连层在所述第二方向上与所述第一子互连层相间隔;第五子互连层,位于所述第二子互连层的另一侧的所述基底上,在所述第一方向上与所述第三子互连层相间隔,所述第五子互连层在所述第二方向上与所述第一子互连层相间隔。

19.可选的,在所述第一方向上,所述第二子互连层至所述第四子互连层的距离小于或等于30纳米;所述第四子互连层至第一子互连层的距离大于50纳米且小于60纳米。

20.可选的,在所述第一方向上,所述第三子互连层的长度至少为96纳米。

21.可选的,所述互连层还包括:第五子互连层,在所述第一方向上,所述第五子互连层位于所述第二子互连层背向所述第四子互连层的一侧,且与所述第三子互连层相间隔,在所述第二方向上,所述第五子互连层与所述第一子互连层相间隔;在所述第一方向上,所述第三子互连层至所述第五子互连层的距离大于或等于24纳米。

22.可选的,在所述第一方向上,所述第三子互连层的长度大于或等于10纳米。

23.可选的,在所述第一方向上,所述第四子互连层至相邻第三子互连层的距离大于或等于20纳米;所述第五子互连层至相邻第三子互连层的距离大于或等于20纳米。

24.可选的,在所述第二方向上,所述第一子互连层至第二子互连层的距离小于或等于50纳米。

25.可选的,在所述第二方向上,所述第二子互连层具有朝向所述第二子互连层的第一面,所述接触插塞的底部至所述第一面的距离大于或等于6纳米。

26.与现有技术相比,本发明实施例的技术方案具有以下优点:

27.本发明实施例提供一种掩膜版版图,所述第二子图形和第三子图形位于同一版图中,后续在同一步骤中,依据所述第二子图形,曝光形成第一开口(图中未示出),依据第三子图形,曝光形成第二开口,在所述第一开口和第二开口中填充导电材料,分别在所述第一开口中形成第二子互连层,在所述第二开口中形成第三子互连层,所述孔图形用于形成与第二互连层连接的接触插塞,其中,在所述第二子图形中,所述孔图形位于所述第二子图形靠近所述第一子图形一侧的端部。本发明实施例中,所述第三子图形与第二子图形相连,且所述第三子图形与第二子图形位于同一版图中,所述第三子图形与所述第二子图形靠近所述第一子图形的一端相连,与没有第三子图形的情况相比,所述第三子图形和第二子图形的总面积更大,在曝光过程中,根据光学邻近效应,使得形成的第一开口在第二方向上的尺寸易与设计相符,相应的形成的所述第二子互连层更满足设计要求,形成的接触插塞易形成在第二子互连层上,所述接触插塞与第二子互连层接触良好,所述半导体结构不易出现桥接或短路,有利于提高半导体结构的电学性能。

附图说明

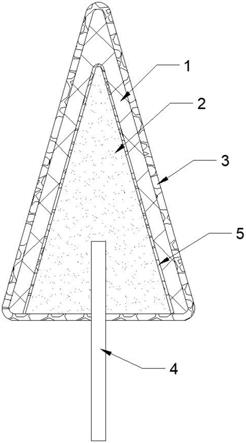

28.图1至图3是一种半导体结构对应的结构示意图;

29.图4是本发明掩膜版版图第一实施例的结构示意图;

30.图5是本发明掩膜版版图第二实施例的结构示意图;

31.图6和图7是本发明半导体结构第一实施例的结构示意图;

32.图8是本发明本发明半导体结构第二实施例的结构示意图。

具体实施方式

33.目前所形成的器件仍有性能不佳的问题。现结合一种半导体结构分析半导体结构性能不佳的原因。

34.参考图1至图3,是一种半导体结构对应的结构示意图。

35.所述半导体结构包括:底层互连结构,所述底层互连结构包括:基底(图中未示出);第一子互连层1,位于所述基底上,所述第一子互连层1具有延伸方向;第二子互连层2,

位于所述第一子互连层1的一侧的所述基底上,所述第二子互连层2与所述第一子互连层1间隔排布,所述第二子互连层2沿第二方向延伸,所述第二子互连层2的延伸方向与所述第一子互连层1的延伸方向相垂直,且所述第二子互连层2延伸方向与所述第一子互连层1的延伸方向相交;第三子互连层3,位于所述基底上,在所述第一方向上与所述第二子互连层2相间隔,在所述第二方向上与所述第一子互连层1相间隔;第四子互连层4,位于所述第二子互连层2的另一侧的所述基底上,在所述第一方向上与所述第二子互连层2相间隔,所述第四子互连层4在所述第二方向上与所述第一子互连层1相间隔;顶层互连结构,位于所述底层互连结构上,所述顶层互连结构包括所述接触插塞5,且接触插塞5的底部与第二子互连层2的顶部接触,所述接触插塞5位于所述第二子互连层2延伸方向上靠近所述第一子互连层1的一端。

36.图1为俯视图,图2为图1在aa处的剖面图,为了使得所述接触插塞5能够与第二子互连层2中靠近所述第一子互连层1的一端接触,会将所述第二子互连层2向第一子互连层1延伸,相应的,所述第一子互连层1的掩膜与第二子互连层的掩膜的设计间隔较小,且通常所述第一子互连层1的掩膜与第二子互连层的掩膜在同一版图中,导致在依据第一子互连层1的掩膜,曝光形成第一开口(图中未示出),依据第二子互连层的掩膜,曝光形成第二开口的步骤中,因为光学邻近效应的原因,导致第一开口和第二开口挨得过近,在所述第一开口和第二开口中填充导电材料,分别形成第一子互连层1和第二子互连层2,所述第二子互连层2与第一子互连层1易发生桥接(如图2中b处所示),导致半导体结构的电学性能较差。

37.图3为图1在aa处的剖面图,为避免第二子互连层2与第一子互连层1发生桥接,扩大所述第二子互连层2与第一子互连层1之间的间隔,这会导致接触插塞5不易与第二子互连层2中靠近所述第一子互连层1的一端接触,导致接触插塞5和第二子互连层2之间存在断路(如图3中c处所示),导致半导体结构的电学性能较差。

38.为了解决所述技术问题,本发明实施例提供一种掩膜版版图,包括:第一掩膜版版图,包括多个互连层图形,所述互连层图形包括第一子图形、以及位于所述第一子图形一侧的第二子图形和第三子图形;所述第二子图形和第三子图形位于同一版图中,且所述第一子图形,与第二子图形和第三子图形间隔排列,所述第一子图形沿第一方向延伸;所述第二子图形沿第二方向延伸,所述第一方向和第二方向相垂直,且所述第二子图形的延伸方向与所述第一子图形的延伸方向相交;在所述第一方向上,所述第三子图形位于所述第二子图形的至少一侧,且所述第三子图形与所述第二子图形靠近所述第一子图形一侧的端部相连;第二掩膜版版图,包括多个孔图形,所述孔图形位于所述互连层图形所在的区域中,其中,在所述第二子图形中,所述孔图形位于所述第二子图形靠近所述第一子图形一侧的端部。

39.本发明实施例提供一种掩膜版版图,所述第二子图形和第三子图形位于同一版图中,后续在同一步骤中,依据所述第二子图形,曝光形成第一开口(图中未示出),依据第三子图形,曝光形成第二开口,在所述第一开口和第二开口中填充导电材料,分别在所述第一开口中形成第二子互连层,在所述第二开口中形成第三子互连层,所述孔图形用于形成与第二互连层连接的接触插塞,其中,在所述第二子图形中,所述孔图形位于所述第二子图形靠近所述第一子图形一侧的端部。本发明实施例中,所述第三子图形与第二子图形相连,且所述第三子图形与第二子图形位于同一版图中,所述第三子图形与所述第二子图形靠近所

述第一子图形的一端相连,与没有第三子图形的情况相比,所述第三子图形和第二子图形的总面积更大,在曝光过程中,根据光学邻近效应,使得形成的第一开口在第二方向上的尺寸易与设计相符,相应的形成的所述第二子互连层更满足设计要求,形成的接触插塞易形成在第二子互连层上,所述接触插塞与第二子互连层接触良好,所述半导体结构不易出现桥接或短路,有利于提高半导体结构的电学性能。

40.为使本发明实施例的上述目的、特征和优点能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

41.图4是本发明掩膜版版图第一实施例的结构示意图。结合图4对本发明掩膜版版图的结构进行详细的说明。

42.所述掩膜版版图包括:第一掩膜版版图,包括多个互连层图形,所述互连层图形包括第一子图形101、以及位于所述第一子图形101一侧的第二子图形102和第三子图形103;所述第二子图形102和第三子图形103位于同一版图中,且所述第一子图形101,与第二子图形102和第三子图形103间隔排列,所述第一子图形101沿第一方向延伸;所述第二子图形102沿第二方向延伸,所述第一方向和第二方向相垂直,且所述第二子图形102的延伸方向与所述第一子图形101的延伸方向相交;在所述第一方向上,所述第三子图形103位于所述第二子图形102的至少一侧,且所述第三子图形103与所述第二子图形102靠近所述第一子图形101一侧的端部相连;第二掩膜版版图,包括多个孔图形201,所述孔图形201位于所述互连层图形所在的区域中,其中,在所述第二子图形102中,所述孔图形201位于所述第二子图形102靠近所述第一子图形101一侧的端部。

43.本发明实施例提供的掩膜版版图中,所述第二子图形102和第三子图形103位于同一版图中,后续在同一步骤中,依据所述第二子图形102,曝光形成第一开口(图中未示出),依据第三子图形103,曝光形成第二开口,在所述第一开口和第二开口中填充导电材料,分别在所述第一开口中形成第二子互连层,在所述第二开口中形成第三子互连层,所述孔图形201用于形成与第二互连层连接的接触插塞,其中,在所述第二子图形102中,所述孔图形201位于所述第二子图形102靠近所述第一子图形101一侧的端部。本发明实施例中,所述第三子图形103与第二子图形102相连,且所述第三子图形103与第二子图形102位于同一版图中,所述第三子图形103与所述第二子图形102靠近所述第一子图形101的一端相连,与没有第三子图形的情况相比,所述第三子图形103和第二子图形102的总面积更大,在曝光过程中,根据光学邻近效应,使得形成的第一开口在第二方向上的尺寸易与设计相符,相应的形成的所述第二子互连层更满足设计要求,形成的接触插塞易形成在第二子互连层上,所述接触插塞与第二子互连层接触良好,所述半导体结构不易出现桥接或短路,有利于提高半导体结构的电学性能。

44.本实施例中,所述第一掩膜版版图,包括多个互连层图形,所述互连层图形用于形成互连层,所述互连层为后段(beol)的金属连线。

45.具体的,所述第一子图形101用于后续形成第一子互连层,所述第二子图形102用于后续形成第二子互连层,第三子图形103用于后续形成第三子互连层。

46.本实施例中,在所述第二方向上,所述第一子图形101至第二子图形102的距离d6不宜过大,也不宜过小。若所述第一子图形101至第二子图形102的距离d6过大,会导致后续形成的半导体结构中第一子互连层至第二子互连层之间的距离过大,半导体结构的平面面

积利用率低,不利于提高半导体结构的集成度,导致半导体结构的能耗较大。若所述第一子图形101至第二子图形102的距离d6过小,所述第一子图形101和第二子图形102在同一版图中,导致依据第一子图形101,曝光形成第一开口(图中未示出),依据第二子图形102,曝光形成第二开口的步骤中,因为光学邻近效应的原因,导致第一开口和第二开口挨得过近,相应的后续在所述第一开口中形成的第一子互连层,和在第二开口中形成的第二子互连层易发生接触,导致半导体结构的电学性能较差。本实施例中,在所述第二方向上,所述第一子图形101至第二子图形102的距离d6小于或等于50纳米。

47.所述孔图形201用于形成接触插塞,在半导体结构中,所述接触插塞的底部与所述互连层接触。

48.本实施例中,在所述第二方向上,所述第二子图形102中的孔图形201具有朝向所述第一子图形101的第一边2011,所述第二子图形102具有朝向所述第一子图形102的第二边1021。需要说明的是,第一边2011至所述第二边1021的距离d1不宜过小。若所述距离d1过小,在根据孔图形201形成接触插塞的过程中,即使是微小的套刻误差也易导致形成的接触插塞与第二子互连层的接触面积过小,或者接触插塞直接与第二子互连层断路,导致半导体结构的电学性能不佳。本实施例中,所述第一边2011至所述第二边1021的距离d1大于或等于6纳米。

49.需要说明的是,所述第二子图形102和第三子图形103位于同一版图中,相应的所述第二子图形102和第三子图形103在一步骤中被曝光。

50.本实施例中,所述互连层图形还包括:第四子图形104,在所述第一方向上与所述第二子图形102相间隔,在所述第二方向上与所述第一子图形101相间隔,且所述第四子图形104位于所述第二子图形102背向所述第三子图形103的一侧。

51.所述第四子图形104用于形成第四子互连层。

52.需要说明的是,在所述第一方向上,所述第二子图形102至所述第四子图形104的距离d2不宜过大。若所述第二子图形102至所述第四子图形104的距离d2过大,会导致形成的半导体结构中第二子互连层至第四子互连层之间的距离d2过大,半导体结构的平面面积利用率低,不利于提高半导体结构的集成度,导致半导体结构的能耗较大。本实施例中,所述第二子图形102至所述第四子图形104的距离d2小于或等于30纳米。

53.需要说明的是,在所述第二方向上,所述第四子图形104至第一子图形101的距离d3不宜过大也不宜过小。若所述第四子图形104至第一子图形101的距离d3过大,半导体结构的平面面积利用率低,不利于提高半导体结构的集成度,导致半导体结构的能耗较大。若所述第四子图形104至第一子图形101的距离d3过小,在根据第一子图形101,形成第一子互连层,根据所述第四子图形104,形成第四子互连层的过程中,即使是微小的套刻误差也易导致形成的第一子互连层和第四子互连层发生桥接,导致半导体结构的电学性能较差。本实施例中,在所述第二方向上,所述第四子图形104和第一子图形101的间距d3为大于50纳米且小于60纳米。

54.需要说明的是,在所述第一方向上,所述第三子图形103的长度d4不宜过短。所述第二子图形102和第三子图形103在一步骤中被曝光,与没有第三子图形的情况相比,所述第三子图形103和第二子图形102的总面积更大,本发明实施例,在曝光过程中,根据光学邻近效应,使得形成的第一开口在第二方向上的尺寸易与设计相符。若所述第三子图形103过

短,也就是说所述第三子图形103在第一方向上过短,所述第三子图形103和第二子图形102总面积增长不显著,在光学邻近效应的作用下,曝光形成的第一开口在第二方向上较短,相应的形成的第二子互连层在第二方向的尺寸较短,相应的,形成的接触插塞不易形成在第二子互连层上,所述接触插塞与第二子互连层接触接触面积较小甚至断路,导致半导体结构的电学性能。本实施例中,在所述第一方向上,所述第三子图形103的长度d4至少为96纳米。

55.本实施例中,所述互连层图形还包括:第五子图形105,在所述第一方向上,所述第五子图形105位于所述第二子图形102背向所述第四子图形104的一侧,且与所述第三子图形103相间隔,在所述第二方向上,所述第五子图形105与所述第一子图形101相间隔。

56.所述第五子图形105用于形成第五子互连层。

57.在所述第一方向上,所述第三子图形103至所述第五子图形105的距离d5不宜过小。若在所述第一方向上,所述第三子图形103至所述第五子图形105的距离d5过小,在根据第三子图形103形成第三子互连层,以及根据所述第五子图形105形成第五子互连层的过程中,即使是微小的套刻误差也易导致形成的第三子互连层和第五子互连层发生桥接,导致半导体结构的电学性能较差。若在所述第一方向上,所述第三子图形103至所述第五子图形105的距离d5过大,导致半导体结构的平面面积利用率低,不利于提高半导体结构的集成度,导致半导体结构的能耗较大。本实施例中,在所述第一方向上,所述第三子图形103至所述第五子图形105的距离d5大于或等于24纳米。

58.需要说明的是,所述第五子图形105中对应的区域也对应有孔图形201,所述第五子图形105中的孔图形201为后续形成与第五子互连层连接的接触插塞做准备。

59.图5是本发明掩膜版版图第二实施例的结构示意图。本发明实施例与第一实施例的相同之处在此不再赘述,不同之处在于:第三子图形303位于所述第二子图形302的两侧。所述第一实施例和第二实施例为不同工艺需求下的不同设计方案。

60.本发明实施例提供一种掩膜版版图,所述第二子图形302和第三子图形303位于同一版图中,后续在同一步骤中,依据所述第二子图形302,曝光形成第一开口(图中未示出),依据第三子图形303,曝光形成第二开口,在所述第一开口和第二开口中填充导电材料,分别在所述第一开口中形成第二子互连层,在所述第二开口中形成第三子互连层,所述孔图形401用于形成与第二互连层连接的接触插塞,其中,在所述第二子图形302中,所述孔图形401位于所述第二子图形302靠近所述第一子图形301一侧的端部。本发明实施例中,所述第三子图形303与第二子图形302位于同一版图中,所述第三子图形303与所述第二子图形302靠近所述第一子图形301的一端相连,与没有第三子图形的情况相比,所述第三子图形303和第二子图形302的总面积更大,本发明实施例,在曝光过程中,根据光学邻近效应,使得形成的第一开口在第二方向上的尺寸易与设计相符,相应的形成的所述第二子互连层更满足设计要求,相应的,形成的接触插塞不易形成在第二子互连层上,所述接触插塞与第二子互连层接触良好,所述半导体结构不易出现桥接或短路,有利于提高半导体结构的电学性能。

61.本实施例中,在所述第一方向上,所述第三子图形303位于所述第二子图形302的两侧;所述互连层图形还包括:第四子图形304,位于所述第二子图形302的一侧,在所述第一方向上与所述第三子图形相间隔,所述第四子图形304在所述第二方向上与所述第一子图形101相间隔;第五子图形305,位于所述第二子图形302的另一侧,在所述第一方向上与

所述第三子图形相间隔,所述第五子图形305在所述第二方向上与所述第一子图形301相间隔。

62.需要说明的是,在所述第一方向上,所述第三子图形303的长度e3不宜过小。若在所述第一方向上,所述第三子图形303的长度过小,所述第三子图形303和所述第二子图形302的总面积增大不显著,在曝光过程中,根据光学邻近效应,导致形成的第一开口在第二方向的尺寸较短,相应的形成的第二子互连层在第二方向的尺寸较短,相应的,形成的接触插塞不易形成在第二子互连层上,所述接触插塞与第二子互连层接触接触面积较小甚至断路,导致半导体结构的电学性能。本实施例中,在所述第一方向上,所述第三子图形303的长度e3大于或等于10纳米。

63.需要说明的是,在所述第一方向上,所述第四子图形304至相邻第三子图形303的距离e5不宜过小。在所述第一方向上,所述第四子图形304至相邻第三子图形303的距离e5过小,在根据第三子图形303形成第三子互连层,以及依据所述第四子图形304形成第四子互连层的过程中,即使是微小的套刻误差也易导致形成的第三子互连层和第四子互连层发生桥接,导致半导体结构的电学性能较差。本实施例中,在所述第一方向上,所述第四子图形304至相邻第三子图形303的距离e5大于或等于20纳米。

64.还需要说明的是,在所述第一方向上,所述第五子图形至相邻第三子图形的距离e4不宜过小。在所述第一方向上,所述第五子图形305至相邻第三子图形303的距离e4过小,在根据第三子图形303形成第三子互连层,依据所述第五子图形305形成第五子互连层的过程中,即使是微小的套刻误差也易导致形成的第三子互连层和第五子互连层发生桥接,导致半导体结构的电学性能较差。本实施例中,在所述第一方向上,所述第五子图形305至相邻第三子图形303的距离e4大于或等于20纳米。

65.需要说明的是,所述第五子图形305中对应的区域也对应有孔图形401,所述第五子图形305中的孔图形401为后续形成与第五子互连层连接的接触插塞做准备。

66.相应的,本发明实施例还提供一种半导体结构。参考图6和图7,示出了本发明半导体结构一实施例的结构示意图。

67.所述半导体结构包括:基底(图未示);互连层,位于所述基底上,所述互连层包括:第一子互连层501,所述第一子互连层501沿第一方向延伸;第二子互连层502,位于所述第一子互连层501的一侧的所述基底上,所述第二子互连层502与所述第一子互连层501间隔排布,所述第二子互连层502沿第二方向延伸,所述第一方向与第二方向相垂直,且所述第二子互连层502的延伸方向与所述第一子互连层501的延伸方向相交;所述第三子互连层503,在所述第一方向上,位于所述第二子互连层502的至少一侧,且所述第三子互连层503与所述第二子互连层502靠近所述第一子互连层501一侧的端部相连;多个接触插塞601,位于所述互连层上,且所述接触插塞601与第二子互连层502的顶部接触,其中,在所述第二子互连层502,所述接触插塞601位于所述第二子互连层502靠近所述第一子互连层501一侧的端部。

68.本发明实施例中,所述第三子互连层503与第二子互连层502分别依据第二子图形和第三子图形形成,所述第二子图形和第三子图形位于同一版图中,形成所述第二子互连层502和第三子互连层503的步骤包括:同一步骤中,依据第二子图形,曝光形成第一开口(图中未示出),依据第三子图形,曝光形成第二开口,在所述第一开口和第二开口中填充导

电材料,分别在所述第一开口中形成第二子互连层502,在所述第二开口中形成第三子互连层503,与没有第三子图形的情况相比,所述第三子图形和第二子图形的总面积更大,相应的,在曝光过程中,根据光学邻近效应,使得形成的第一开口在第二方向上的尺寸易与设计相符,形成的所述第二子互连层502在第二方向上的尺寸更满足设计要求,形成的接触插塞601更易形成在第二子互连层502上,所述接触插塞601与第二子互连层502接触良好,所述半导体结构不易出现桥接或短路,有利于提高半导体结构的电学性能。

69.本实施例中,所述互连层为后段(beol)的金属连线。所述互连层的材料包括:cu、co、ni、pt、al中的一种或多种。

70.在所述第二方向上,所述第一子互连层501至第二子互连层502的距离d6不宜过大,也不宜过小。若所述第一子互连层501至第二子互连层502的距离d6过大,半导体结构的平面面积利用率低,不利于提高半导体结构的集成度,导致半导体结构的能耗较大。若所述第一子互连层501至第二子互连层502的距离d6过小,所述第一子互连层501和第二子互连层502易发生桥接,导致半导体结构的电学性能较差。本实施例中,在所述第二方向上,所述第一子互连层501至第二子互连层502的距离d6小于或等于50纳米。

71.在所述第二方向上,所述第二子互连层502具有朝向所述第一子互连层501的第一面5021,所述接触插塞601的底部至所述第一面5021的距离f不宜过小。若所述距离过小,所述接触插塞601易形成在所述第一子互连层501与所述第二子互连层502之间,导致接触插塞601与第二子互连层502断路,或者导致接触插塞601与第二子互连层502的接触面积过小,导致半导体结构的电学性能不佳。本实施例中,所述接触插塞601的底部至所述第一面5021的距离f大于或等于6纳米。

72.本实施例中,所述互连层还包括:第四子互连层504,位于所述基底上,在所述第一方向上与所述第二子互连层502相间隔,在所述第二方向上与所述第一子互连层501相间隔,且所述第四子互连层504位于所述第二子互连层502背向所述第四子互连层504的一侧。

73.需要说明的是,在所述第一方向上,所述第二子互连层502至所述第四子互连层504的距离d2不宜过大。若所述第二子互连层502至所述第四子互连层504的距离d2过大,半导体结构的平面面积利用率低,不利于提高半导体结构的集成度,导致半导体结构的能耗较大。本实施例中,在所述第一方向上,所述第二子互连层502至所述第四子互连层504的距离d2小于或等于30纳米。

74.还需要说明的是,在所述第二方向上,所述第四子互连层504至第一子互连层501的距离d3不宜过大,也不宜过小。若所述第四子互连层504至第一子互连层501的距离d3过大,半导体结构的平面面积利用率低,不利于提高半导体结构的集成度,导致半导体结构的能耗较大。若所述第四子互连层504至第一子互连层501的距离d3过小,所述第一子互连层501和第四子互连层504发生桥接,导致半导体结构的电学性能较差。本实施例中,在所述第二方向上,所述第四子互连层504和第一子互连层501的间距d3为大于50纳米且小于60纳米。

75.需要说明的是,在所述第一方向上,所述第三子互连层503的长度d4不宜过短。所述第三子互连层503是依据第三子图形形成的,所述第二子互连层502是依据第二子图形形成的,与没有第三子图形的情况相比,所述第三子图形和第二子图形的总面积更大,本发明实施例在曝光过程中,根据光学邻近效应,使得形成的第一开口在第二方向上的尺寸易与

设计相符。若所述第三子互连层503过短,也就是说所述第三子图形在第一方向上过短,所述第三子图形和第二子图形总面积增长不显著,在依据第二子图形和第三子图形,分别形成第二子互连层502和第三子互连层503的过程中,在光学邻近效应的作用下,曝光形成的第一开口在第二方向上尺寸增大不显著,相应的形成的第二子互连层502在第二方向的尺寸增大不显著,相应的,接触插塞601不易形成在第二子互连层502上,所述接触插塞601与第二子互连层502接触接触面积较小甚至断路,导致半导体结构的电学性能。本实施例中,在所述第一方向上,所述第三子互连层503的长度d4至少为96纳米。

76.本实施例中,所述互连层还包括:第五子互连层505,在所述第一方向上,所述第五子互连层505位于所述第二子互连层502背向所述第四子互连层504的一侧,且与所述第三子互连层503相间隔,在所述第二方向上,所述第五子互连层505与所述第一子互连层501相间隔。

77.本实施例中,在所述第一方向上,所述第三子互连层503至所述第五子互连层505的距离d5不宜过小。若在所述第一方向上,所述第三子互连层503至第五子互连层505的距离d5过小,所述第三子互连层503和第五子互连层505易发生桥接,导致半导体结构的电学性能较差。若在所述第一方向上,所述第三子互连层503至所述第五子图形105的距离d5过大,半导体结构的平面面积利用率低,不利于提高半导体结构的集成度,导致半导体结构的能耗较大。在所述第一方向上,所述第三子互连层503至所述第五子互连层505的距离d5大于或等于24纳米。

78.需要说明的是,所述第五子互连层505中对应的区域也对应有接触插塞601,所述第五子互连层505中的接触插塞601与第五子互连层505连接。

79.图8是本发明半导体结构第二实施例的结构示意图,本发明实施例与第一实施例的相同之处在此不再赘述,不同之处在于:第三子互连层703位于所述第二子互连层702的两侧。

80.本发明实施例中,所述第三子互连层703与第二子互连层702分别依据第二子图形和第三子图形形成,所述第二子图形和第三子图形位于同一版图中,形成所述第二子互连层702和第三子互连层703的步骤包括:同一步骤中,依据第二子图形,曝光形成第一开口(图中未示出),依据第三子图形,曝光形成第二开口,在所述第一开口和第二开口中填充导电材料,分别在所述第一开口中形成第二子互连层702,在所述第二开口中形成第三子互连层703,与没有第三子图形的情况相比,所述第三子图形和第二子图形的总面积更大,相应的,在曝光过程中,根据光学邻近效应,使得形成的第一开口在第二方向上的尺寸易与设计相符,形成的所述第二子互连层702在第二方向上的尺寸更满足设计要求,形成的接触插塞801更易形成在第二子互连层702上,所述接触插塞801与第二子互连层702接触良好,所述半导体结构不易出现桥接或短路,有利于提高半导体结构的电学性能。

81.在所述第一方向上,所述第三子互连层703位于所述第二子互连层702的两侧;所述互连层图形还包括:第四子互连层704,位于所述第二子互连层702的一侧的所述基底上,在所述第一方向上与所述第三子互连层703相间隔,所述第四子互连层704在所述第二方向上与所述第一子互连层701相间隔;第五子互连层705,位于所述第二子互连层702的另一侧的所述基底上,在所述第一方向上与所述第三子互连层703相间隔,所述第五子互连层705在所述第二方向上与所述第一子互连层701相间隔。

82.需要说明的是,在所述第一方向上,所述第三子互连层703的长度e3不宜过小。所述第三子互连层703是依据第三子图形形成的,所述第二子互连层702是依据第二子图形形成的,所述第二子图形和第三子图形位于同一版图中,且同时曝光。若在所述第一方向上,所述第三子互连层703的长度过小,在依据第三子图形和第二子图形,形成第三子互连层和第二子互连层的过程中,在光学邻近效应的作用下,形成的第一开口在第二方向增长不显著,相应的形成的第二子互连层702在第二方向的尺寸增大不显著,相应的,形成的接触插塞801易形成在第二子互连层702和所述第一子互连层701之间,导致接触插塞801与第二子互连层702断路,或者,所述接触插塞801与第二子互连层702接触接触面积较小,导致半导体结构的电学性能。本实施例中,在所述第一方向上,所述第三子互连层703的长度e3大于或等于10纳米。

83.还需要说明的是,在所述第一方向上,所述第四子互连层704至相邻第三子互连层703的距离e5不宜过小。在所述第一方向上,所述第四子互连层704至相邻第三子互连层703的距离e5过小,所述第三子互连层703和第四子互连层704易发生桥接,导致半导体结构的电学性能较差。在所述第一方向上,所述第四子互连层704至相邻第三子互连层703的距离e5大于或等于20纳米。

84.此外,在所述第一方向上,所述第五子图形705至相邻第三子互连层703的距离e4不宜过小。在所述第一方向上,所述第五子互连层705至相邻第三子互连层703的距离e4过小,所述第三子互连层703和第五子互连层705易发生桥接,导致半导体结构的电学性能较差。本实施例中,在所述第一方向上,所述第五子互连层705至相邻第三子互连层703的距离e4大于或等于20纳米。

85.对所公开的实施例的上述说明,使本领域技术人员能够实现或使用本发明。对这些实施例的多种修改对本领域技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其他实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是符合与本文所公开的原理和新颖特点相一致的最宽的范围。

86.虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。