一种pwm输出电路和液晶显示装置

技术领域

1.本发明实施例涉及显示技术领域,尤其涉及一种pwm输出电路和液晶显示装置。

背景技术:

2.近年来,液晶显示技术已经广泛应用于诸如笔记本电脑(note book,nb)等电子产品的生产制造过程。由于液晶显示器(liquid crystal display,lcd)不发光,为了实现nb产品的背光亮,lcd大多需要配备由脉冲宽度调制(pulse width modulation,pwm)信号控制背光的逆变器。为了实现背光的精准控制,pwm信号的占空比测试是lcd系统匹配性测试项目的重中之重,在占空比测试环节中,pwm信号的上升和下降时间是测试人员的重点关注对象。

3.具体地,tcon芯片将pwm输入信号进行信号处理和逻辑控制,然而,现有的pwm输入信号存在上升时间(rising time,tr)和/或下降时间(falling time,tf)超规应用的情况。图1为现有的一种pwm输入信号的波形示意图。如图1所示,pwm输入信号的上升时间tr为0.380μs,下降时间tf为15.307μs,其中,下降时间超出了tcon芯片的应用要求。这种超规应用不仅会产生pwm信号上升和/或下降占空比失真现象,还会影响系统输出精度,并使得后端内容适应背光(content adaptive brightness control,cabc)电路无法正常实现动态背光调节功能。

技术实现要素:

4.本发明实施例提供一种pwm输出电路和液晶显示装置,以提高pwm信号精度,降低pwm信号的上升和/或下降时间超规应用风险。

5.第一方面,本发明实施例提供了一种pwm输出电路,包括:

6.上升沿控制模块,包括输入端、第一输出端和第二输出端,所述上升沿控制模块的输入端接入pwm输入信号;所述上升沿控制模块用于根据所述pwm输入信号生成信号相反的第一上升沿比较信号和第二上升沿比较信号,所述第一上升沿比较信号由所述第一输出端输出,所述第二上升沿比较信号由所述第二输出端输出;

7.下降沿控制模块,包括输入端和输出端,所述下降沿控制模块的输入端接入所述pwm输入信号;所述下降沿控制模块用于根据所述pwm输入信号生成下降沿比较信号,并由所述输出端输出;

8.输出控制模块,包括第一输入端、第二输入端、第三输入端和输出端;所述输出控制模块的第一输入端与所述上升沿控制模块的第一输出端电连接,所述输出控制模块的第二输入端与所述下降沿控制模块的输出端电连接,所述输出控制模块的第三输入端与所述上升沿控制模块的第二输出端电连接,所述输出控制模块的输出端作为所述pwm输出电路的输出端;所述输出控制模块根据所述第一上升沿比较信号、第二上升沿比较信号和所述下降沿比较信号生成pwm输出信号。

9.可选地,所述上升沿控制模块包括:

10.第一参数设定单元,所述第一参数设定单元用于提供第一参考电压;

11.第一比较单元,所述第一比较单元包括第一输入端、第二输入端和输出端;所述第一比较单元的第一输入端接入所述pwm输入信号,所述第一比较单元的第二输入端与所述第一参数设定单元电连接,所述第一比较单元用于将所述pwm输入信号和所述第一参考电压比较,得到所述第一上升沿比较信号。

12.可选地,所述第一参数设定单元包括:

13.第一电阻,所述第一电阻的第一端接入电源电压,所述第一电阻的第二端与所述第一比较单元的第二输入端电连接;

14.第二电阻,所述第二电阻的第一端接地,所述第二电阻的第二端与所述第一电阻的第二端电连接;

15.所述第一电阻与所述第二电阻的阻值比大于1。

16.可选地,所述第一比较单元包括:

17.第一比较器,所述第一比较器的第一输入端接入所述pwm输入信号,所述第一比较器的第二输入端与所述第一参数设定单元电连接,所述第一比较器的输出端输出所述第二上升沿比较信号;

18.第一反相器,所述第一反相器的输入端与所述第一比较器的输出端电连接,所述第一反相器的输出端作为所述上升沿控制模块的第一输出端。

19.可选地,所述下降沿控制模块包括:

20.第二参数设定单元,所述第二参数设定单元用于提供第二参考电压;

21.第二比较单元,所述第二比较单元包括第一输入端、第二输入端和输出端;所述第二比较单元的第一输入端接入所述pwm输入信号,所述第二比较单元的第二输入端与所述第二参数设定单元电连接,所述第二比较单元用于将所述pwm输入信号和所述第二参考电压比较,得到所述下降沿比较信号。

22.可选地,所述第二参数设定单元包括:

23.第三电阻,所述第三电阻的第一端接入电源电压,所述第三电阻的第二端与所述第二比较单元的第二输入端电连接;

24.第四电阻,所述第四电阻的第一端接地,所述第四电阻的第二端与所述第三电阻的第二端电连接;

25.其中,所述第三电阻与所述第四电阻的阻值比小于1。

26.可选地,所述输出控制模块包括:

27.脉冲触发单元,包括第一输入端、第二输入端和输出端;所述脉冲触发单元的第一输入端与所述上升沿控制模块的第一输出端电连接,所述脉冲触发单元的第二输入端与所述下降沿控制模块的输出端电连接;

28.逻辑比较单元,包括第一输入端、第二输入端和输出端;所述逻辑比较单元的第一输入端与所述脉冲触发单元的输出端电连接,所述逻辑比较单元的第二输入端与所述上升沿控制模块的第二输出端电连接,所述逻辑比较单元的输出端输出所述pwm输出信号。

29.可选地,所述脉冲触发单元包括:

30.d触发器,所述d触发器的复位端与所述上升沿控制模块的第一输出端电连接,所述d触发器的时钟端与所述下降沿控制模块的输出端电连接,所述d触发器的触发端接入器

件电压,所述d触发器的清除端接地,所述d触发器的输出端作为所述脉冲触发单元的输出端。

31.可选地,所述逻辑比较单元包括:

32.异或门,所述异或门的第一输入端与所述脉冲触发单元的输出端电连接,所述异或门的第二输入端与所述上升沿控制模块的第二输出端电连接,所述异或门的输出端输出所述pwm输出信号。

33.第二方面,本发明实施例还提供了一种液晶显示装置,包括:背光模组和本发明任意实施例提供的pwm输出电路,所述pwm输出电路与所述背光模组电连接,用于向所述背光模组提供pwm输出信号。

34.本发明实施例提供的pwm输出电路设置上升沿控制模块、下降沿控制模块和输出控制模块,其中,上升沿控制模块生成信号相反的第一上升沿比较信号和第二上升沿比较信号,以确定pwm输出信号的上升位置;下降沿控制模块生成下降沿比较信号,以确定pwm输出信号的下降位置;输出控制模块基于第一上升沿比较信号、第二上升沿比较信号和下降沿比较信号,生成pwm输出信号。与pwm输入信号相比,pwm输出信号的上升时间和下降时间较短,解决了现有pwm输出电路因pwm信号精度不足而产生上升和/或下降时间超规应用情况的问题,提高了pwm信号的精度。

附图说明

35.图1为现有的一种pwm输入信号的波形示意图;

36.图2是本发明实施例提供的一种pwm输出电路的结构示意图;

37.图3是本发明实施例提供的一种pwm输出电路的信号波形示意图;

38.图4是本发明实施例提供的一种pwm输入信号和pwm输出信号的波形示意图;

39.图5是本发明实施例提供的另一种pwm输出电路的结构示意图;

40.图6是本发明实施例提供的又一种pwm输出电路的结构示意图;

41.图7是本发明实施例提供的另一种pwm输出电路的波形示意图。

42.附图中,各附图标记所代表的特征列表如下:

43.100

‑

上升沿控制模块;200

‑

下降沿控制模块;300

‑

输出控制模块;110

‑

第一参数设定单元;120

‑

第一比较单元;121

‑

第一比较器;122

‑

第一反相器;210

‑

第二参数设定单元;220

‑

第二比较单元;221

‑

第二比较器;222

‑

第二反相器;310

‑

脉冲触发单元;320

‑

逻辑比较单元;r1

‑

第一电阻;r2

‑

第二电阻;vcc

‑

电源电压;vdd

‑

器件电压;r3

‑

第三电阻;r4

‑

第四电阻;r5

‑

第一上拉电阻;r6

‑

第二上拉电阻。

具体实施方式

44.下面结合附图和实施例对本发明实施例作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅用于解释本发明实施例,而非对本发明实施例的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本发明实施例相关的部分而非全部结构。

45.图2是本发明实施例提供的一种pwm输出电路的结构示意图。如图2所示,pwm输出电路包括:上升沿控制模块100、下降沿控制模块200和输出控制模块300。

46.上升沿控制模块100包括输入端、第一输出端和第二输出端。上升沿控制模块100

的输入端接入pwm输入信号pwmi。上升沿控制模块100用于根据pwm输入信号pwmi生成信号相反的第一上升沿比较信号s1’和第二上升沿比较信号s1,第一上升沿比较信号s1’由第一输出端输出,第二上升沿比较信号s1由第二输出端输出。

47.下降沿控制模块200包括输入端和输出端。下降沿控制模块200的输入端接入pwm输入信号pwmi。下降沿控制模块200用于根据pwm输入信号pwmi生成下降沿比较信号s2’,并由输出端输出。

48.输出控制模块300包括第一输入端、第二输入端、第三输入端和输出端。输出控制模块300的第一输入端与上升沿控制模块100的第一输出端电连接,输出控制模块300的第二输入端与下降沿控制模块200的输出端电连接,输出控制模块300的第三输入端与上升沿控制模块100的第二输出端电连接,输出控制模块300的输出端作为pwm输出电路的输出端。输出控制模块300根据第一上升沿比较信号s1’、第二上升沿比较信号s1和下降沿比较信号s2’生成pwm输出信号pwmo。

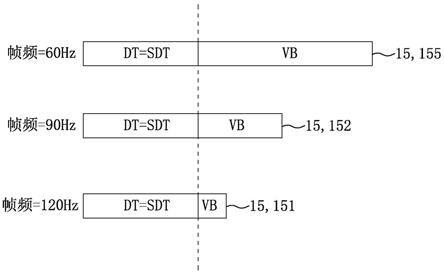

49.图3是本发明实施例提供的一种pwm输出电路的信号波形示意图。参见图3,第一上升沿比较信号s1’和第二上升沿比较信号s1信号相反,即第一上升沿比较信号s1’和第二上升沿比较信号s1的幅值、频率和占空比相同,但高低电平相反。下降沿比较信号s2’的脉冲宽度小于第一上升沿比较信号s1’的脉冲宽度。

50.示例性地,该pwm输出电路的工作原理为:当pwm输入信号pwmi开始由低电平变为高电平时,存在较长的上升时间,当pwm输入信号pwmi上升至第一阈值时,上升沿控制模块100控制第一上升沿比较信号s1’由高电平变为低电平,同时,第二上升沿比较信号s1由低电平变为高电平。输出控制模块300控制pwm输出信号pwmo由低电平变为高电平,以使pwm输出信号pwmo的高电平脉冲起始时间与pwm输入信号pwmi的高电平脉冲起始时间契合。其中,通过调整第一阈值的大小,可以调整pwm输出信号pwmo的高电平脉冲起始时间。

51.随着pwm输入信号pwmi的继续升高,升高至第二阈值时,下降沿控制模块200控制下降沿比较信号s2’由高电平变为低电平。当pwm输入信号pwmi开始由高电平变为低电平时,存在较长的下降时间,当pwm输入信号pwmi下降至第二阈值时,下降沿控制模块200控制下降沿比较信号s2’由低电平变为高电平。输出控制模块300控制pwm输出信号pwmo由高电平变为低电平,以使pwm输出信号pwmo的高电平脉冲终止时间与pwm输入信号pwmi的高电平脉冲终止时间契合。其中,通过调整第二阈值的大小,可以调整pwm输出信号pwmo的高电平脉冲终止时间。

52.随着pwm输入信号pwmi的继续降低,降低至第一阈值时,上升沿控制模块100控制第一上升沿比较信号s1’由低电平变为高电平,同时,第二上升沿比较信号s1由高电平变为低电平,输出控制模块300仍控制pwm输出信号pwmo为低电平。

53.图4是本发明实施例提供的一种pwm输入信号和pwm输出信号的波形示意图。参见图4,pwm输出信号pwmo的高电平脉冲起始时间与pwm输入信号pwmi的高电平脉冲起始时间契合,pwm输出信号pwmo的高电平脉冲终止时间与pwm输入信号pwmi的高电平脉冲终止时间契合。即pwm输出信号pwmo与pwm输入信号pwmi的占空比相同,可以以pwm输出信号pwmo代替pwm输入信号pwmi作为tcon芯片的输入。不同的是,第一上升沿比较信号s1’、第二上升沿比较信号s1和下降沿比较信号s2’的上升时间/下降时间均小于pwm输入信号pwmi的上升时间/下降时间,因此,pwm输出信号pwmo的上升时间/下降时间小于pwm输入信号pwmi。

54.本发明实施例提供的pwm输出电路设置上升沿控制模块100、下降沿控制模块200和输出控制模块300,其中,上升沿控制模块100生成信号相反的第一上升沿比较信号s1’和第二上升沿比较信号s1,以确定pwm输出信号pwmo的上升位置;下降沿控制模块200生成下降沿比较信号s2’,以确定pwm输出信号pwmo的下降位置;输出控制模块基于第一上升沿比较信号s1’、第二上升沿比较信号s1和下降沿比较信号s2’,生成pwm输出信号pwmo。与pwm输入信号pwmi相比,pwm输出信号pwmo的上升时间和下降时间较短,解决了现有pwm输出电路因pwm信号精度不足而产生上升和/或下降时间超规应用情况的问题,提高了pwm信号的精度。

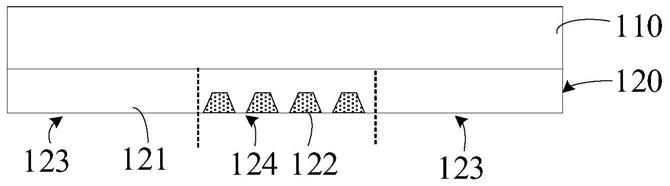

55.图5是本发明实施例提供的另一种pwm输出电路的结构示意图。如图5所示,在上述各实施例的基础上,可选地,上升沿控制模块100包括第一参数设定单元110和第一比较单元120。第一参数设定单元110用于提供第一参考电压。第一比较单元120包括第一输入端、第二输入端和输出端。第一比较单元120的第一输入端接入pwm输入信号pwmi,第一比较单元120的第二输入端与第一参数设定单元110电连接,第一比较单元120用于将pwm输入信号pwmi和第一参考电压比较,得到第一上升沿比较信号s1’。

56.其中,第一参考电压的数值可以根据pwm输入信号pwmi的幅值进行适应性改变,例如,pwm输入信号pwmi的幅值为3.3v,设置第一参考电压为0.1v,以在pwm输入信号pwmi开始由低电平变化为高电平时,第一上升沿比较信号s1’翻转。

57.继续参见图5,在上述各实施例的基础上,可选地,下降沿控制模块200包括第二参数设定单元210和第二比较单元220。第二参数设定单元210用于提供第二参考电压。第二比较单元220包括第一输入端、第二输入端和输出端,第二比较单元220的第一输入端接入pwm输入信号pwmi,第二比较单元220的第二输入端与第二参数设定单元210电连接,第二比较单元220用于将pwm输入信号pwmi和第二参考电压比较,得到下降沿比较信号s2’。

58.其中,第二参考电压的数值可以根据pwm输入信号pwmi的幅值进行适应性改变,例如pwm输入信号pwmi的幅值为3.3v,设置第二参考电压为3.2v,以在pwm输入信号pwmi开始由高电平变化为低电平时,下降沿比较信号s2’翻转。

59.继续参见图5,在上述各实施例的基础上,可选地,第一参数设定单元110包括第一电阻r1和第二电阻r2。第一电阻r1的第一端接入电源电压vcc,第一电阻r1的第二端与第一比较单元120的第二输入端电连接。第二电阻r2的第一端接地,第二电阻r2的第二端与第一电阻r1的第二端电连接。第一电阻r1与第二电阻r2的阻值比大于1。

60.其中,第一电阻r1和第二电阻r2根据电阻阻值比对电源电压vcc分压,设置第一电阻r1与第二电阻r2的阻值比大于1,以使第一参考电压的值较小,有利于在pwm输入信号pwmi开始由低电平变化为高电平时,第一上升沿比较信号s1’翻转。示例性地,当电源电压vcc为3.3v,pwm输入信号pwmi的幅值为3.3v时,设定第一参考电压为0.1v,则第一电阻r1与第二电阻r2的阻值比为32,远大于1。本领域技术人员可以理解,第一电阻r1与第二电阻r2的阻值比越大,第一参考电压的值越小,在实际应用中可以根据需要进行设定。

61.继续参见图5,在上述各实施例的基础上,可选地,第一比较单元120包括第一比较器121和第一反相器122。第一比较器121的第一输入端接入pwm输入信号pwmi,第一比较器121的第二输入端与第一参数设定单元100电连接。第一反相器122的输入端与第一比较器121的输出端电连接,第一比较器121的输出端输出第二上升沿比较信号s1至第二输出端以

及第一反相器122的输入端,第一反相器122的输出端作为上升沿控制模块100的第一输出端输出第一上升沿比较信号s1’。本发明实施例这样设置,以简单的电路结构实现了第一比较单元120的比较功能,易于实现,实用性较强。

62.继续参见图5,在上述各实施例的基础上,可选地,第二参数设定单元210包括第三电阻r3和第四电阻r4。第三电阻r3的第一端接入电源电压vcc,第三电阻r3的第二端与第二比较单元220的第二输入端电连接。第四电阻r4的第一端接地,第四电阻r4的第二端与第三电阻r3的第二端电连接。其中,第三电阻r3与第四电阻r4的阻值比小于1。

63.其中,第三电阻r3和第四电阻r4根据电阻阻值比对电源电压vcc分压,设置第三电阻r3与第四电阻r4的阻值比小于1,以使第二参考电压的值较大,有利于在pwm输入信号pwmi开始由高电平变化为低电平时,下降沿比较信号s2’翻转。示例性地,当电源电压vcc为3.3v,pwm输入信号pwmi的幅值为3.3v时,设定第二参考电压为3.2v,则第三电阻r3与第四电阻r4的阻值比为1/32,远小于1。本领域技术人员可以理解,第三电阻r3与第四电阻r4的阻值比越小,第二参考电压的值越大,在实际应用中可以根据需要进行设定。

64.继续参见图5,在上述各实施例的基础上,可选地,第二比较单元220包括第二比较器221和第二反相器222。第二比较器221的第一输入端接入pwm输入信号pwmi,第二比较器221的第二输入端与第二参数设定单元210电连接,第二比较器221的输出端输出待反相信号s2。第二反相器222的输入端与第二比较器221的输出端电连接,第二反相器222的输出端作为下降沿控制模块200的输出端输出下降沿比较信号s2’。本发明实施例这样设置,以简单的电路结构实现了第二比较单元220的比较功能,易于实现,实用性较强。

65.继续参见图5,在上述各实施例的基础上,可选地,第一比较单元120还包括第一上拉电阻r5,第一上拉电阻r5的第一端接入器件电压vdd,第一上拉电阻r5的第二端与第一反相器122的输入端电连接。第二比较单元220还包括第二上拉电阻r6,第二上拉电阻r6的第一端接入器件电压vdd,第二上拉电阻r6的第二端与第二反相器222的输入端电连接。

66.图6是本发明实施例提供的又一种pwm输出电路的结构示意图。如图7所示,在上述各实施例的基础上,可选地,输出控制模块300包括脉冲触发单元310和逻辑比较单元320。

67.脉冲触发单元310包括第一输入端、第二输入端和输出端。脉冲触发单元的310第一输入端与上升沿控制模块100的第一输出端电连接,脉冲触发单元310的第二输入端与下降沿控制模块200的输出端电连接。

68.逻辑比较单元320包括第一输入端、第二输入端和输出端。逻辑比较单元320的第一输入端与脉冲触发单元310的输出端电连接,逻辑比较单元320的第二输入端与上升沿控制模块100的第二输出端电连接,逻辑比较单元320的输出端输出pwm输出信号pwmo。

69.其中,脉冲触发单元310的第一输入端用于接入第一上升沿比较信号s1’,脉冲触发单元310的第二输入端用于接入下降沿比较信号s2’,脉冲触发单元310的输出端用于输出待比较信号q。脉冲触发单元310用于根据第一上升沿比较信号s1’和下降沿比较信号s2’生成待比较信号q。

70.逻辑比较单元320的第一输入端用于接入待比较信号q,逻辑比较单元320的第二输入端用于接入第二上升沿比较信号s1。逻辑比较单元320用于根据待比较信号q和第二上升沿比较信号s1生成pwm输出信号pwmo。

71.继续参见图6,在上述各实施例的基础上,可选地,脉冲触发单元310包括d触发器。

d触发器的复位端与上升沿控制模块100的第一输出端电连接,接入第一上升沿比较信号s1’;d触发器的时钟端与下降沿控制模块200的输出端电连接,接入下降沿比较信号s2’;d触发器的触发端接入器件电压vdd,d触发器的清除端接地,d触发器的输出端作为脉冲触发单元的输出端,输出待比较信号q。

72.本发明实施例通过设置第一反相器122和d触发器,能够实现pwm输出信号pwmo的持续输出。其原因在于:由于d触发器在正常情况下仅能触发一次,本发明实施例通过将第一上升沿比较信号s1’输入到d触发器的复位端,能够实现d触发器的连续触发输出,进而实现了pwm输出信号pwmo的持续输出。

73.继续参见图6,在上述各实施例的基础上,可选地,逻辑比较单元320包括异或门。异或门的第一输入端与脉冲触发单元310的输出端电连接,接入待比较信号q;异或门的第二输入端与上升沿控制模块100的第二输出端电连接,接入第二上升沿比较信号s1;异或门的输出端输出pwm输出信号pwmo。

74.图7是本发明实施例提供的另一种pwm输出电路的波形示意图。参见图6和图7,示例性地,该pwm输出电路的工作原理为:当pwm输入信号pwmi开始由低电平变为高电平时,存在较长的上升时间,当pwm输入信号pwmi上升至第一阈值时,第一比较器121控制第二上升沿比较信号s1由低电平变为高电平,同时,第一反相器122控制第一上升沿比较信号s1’由高电平变为低电平。此时,由于下降沿控制模块200处于待触发状态,因而下降沿比较信号s2’保持高电平状态,与之相反地,待反相信号s2保持低电平状态。与此同时,由于第二上升沿比较信号s1由低电平变为高电平,d触发器控制待比较信号q保持低电平状态,因而异或门控制pwm输出信号pwmo由低电平变为高电平,以使pwm输出信号pwmo的高电平脉冲起始时间与pwm输入信号pwmi的高电平脉冲起始时间契合。其中,通过调整第一阈值的大小,可以调整pwm输出信号pwmo的高电平脉冲起始时间。

75.随着pwm输入信号pwmi的继续升高,升高至第二阈值时,第二比较器221控制待反相信号s2由低电平变为高电平,同时,第二反相器222控制下降沿比较信号s2’由高电平变为低电平。当pwm输入信号pwmi开始由高电平变为低电平时,存在较长的下降时间,当pwm输入信号pwmi下降至第二阈值时,第二比较器221控制待反相信号s2由高电平变为低电平,同时,第二反相器222控制下降沿比较信号s2’由低电平变为高电平。此时,第一比较器121控制第二上升沿比较信号s1仍保持于高电平状态,与之相反地,第一反相器122控制第一上升沿比较信号s1’仍保持于低电平状态。与此同时,由于下降沿比较信号s2’由低电平变为高电平,d触发器控制待比较信号q由低电平变为高电平,因而异或门控制pwm输出信号pwmo由高电平变为低电平以使pwm输出信号pwmo的高电平脉冲终止时间与pwm输入信号pwmi的高电平脉冲终止时间契合。其中,通过调整第二阈值的大小,可以调整pwm输出信号pwmo的高电平脉冲终止时间。

76.随着pwm输入信号pwmi的继续降低,降低至第一阈值时,第一比较器121控制第二上升沿比较信号s1由高电平变为低电平,同时,第一反相器122控制第一上升沿比较信号s1’由低电平变为高电平。此时,由于第一上升沿比较信号s1’输入到d触发器的复位端,当第一上升沿比较信号s1’由低电平变为高电平时,d触发器复位,因而待比较信号q由高电平变为低电平,异或门仍控制pwm输出信号pwmo为低电平。

77.本发明实施例提供的输出控制模块300设置d触发器和异或门,d触发器基于第一

上升沿比较信号s1’和下降沿比较信号s2’,生成待比较信号q;异或门基于待比较信号q和第二上升沿比较信号s1,生成pwm输出信号pwmo。与pwm输入信号pwmi相比,pwm输出信号pwmo的上升时间和下降时间较短,解决了现有pwm输出电路因pwm信号精度不足而产生上升和/或下降时间超规应用情况的问题,提高了pwm信号的精度。

78.本发明实施例还提供了一种液晶显示装置,包括背光模组和本发明任意实施例所提供的pwm输出电路,pwm输出电路与背光模组电连接,用于向背光模组提供pwm输出信号,其技术原理和实现的效果类似,不再赘述。

79.在上述各实施例的基础上,可选地,背光模组可以是任意一种前光式(front light)或背光式(back light)背光模组,本发明实施例对此不进行限制。示例性地,背光模组的具体结构可以是侧光式结构、直下型结构或中空型结构等。

80.注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。