半导体装置及半导体装置的制造方法

1.[相关申请的交叉参考]

[0002]

本技术是基于2021年7月15日提出申请的现有日本专利申请第2021-117108号的优先权而主张优先权利益,并通过引用将其全部内容并入本文中。

技术领域

[0003]

本发明涉及一种半导体装置及半导体装置的制造方法。

背景技术:

[0004]

例如,已知有封装着半导体存储器及存储器控制器的半导体装置。这种半导体装置中,如果半导体存储器的高速化发展,那么存储器控制器的发热量会增加,因此可能会产生存储器控制器温度变高导致动作停止的可能性。特别是在具备不容易散热的覆晶连接的半导体元件的半导体装置中,期待一种用来有效地进行散热的构成。

技术实现要素:

[0005]

本发明提供一种半导体装置及半导体装置的制造方法,该半导体装置是具备覆晶连接的半导体元件的半导体装置,其中具备用来散热的构成。

[0006]

本发明的半导体装置具备:衬底,形成着配线;第1半导体元件,设置在所述衬底;第2半导体元件,设置在所述第1半导体元件上;第1树脂,设置在所述第1半导体元件与所述衬底间的区域的至少一部分;第2树脂,设置在所述第2半导体元件与所述衬底间的区域的至少一部分;及构件,具有比所述第1树脂的热导率及所述第2树脂的热导率大的热导率,设置在所述第1树脂与所述第2树脂之间,且在俯视下,一部分与所述第1半导体元件的上表面重叠并且另一部分与作为所述配线的一部分的第1配线部重叠。

[0007]

本发明的半导体装置具备:衬底,在上表面形成配线,在下表面设置着连接于所述配线的电极;第1半导体元件,设置在所述衬底;第1间隔件,设置在所述衬底的所述配线上;第1构件,设置在所述衬底与所述第1间隔件之间;第2半导体元件,设置在所述第1半导体元件及所述第1间隔件上;第2构件,设置在所述第1半导体元件及所述第1间隔件与所述第2半导体元件之间;及密封树脂,将所述第1半导体元件、所述第1间隔件及所述第2半导体元件密封,且具有比所述第1构件的热导率及所述第2构件的热导率低的热导率。

[0008]

本发明的半导体装置的制造方法包括:将第1树脂配设在形成着配线的衬底上,将所述第1半导体元件设置在所述衬底,将所述第1树脂配设在所述第1半导体元件与所述衬底间的区域的至少一部分,将构件配设在所述第1树脂上,该构件具有比所述第1树脂的热导率大的热导率,且在俯视下,一部分与所述第1半导体元件的上表面重叠并且另一部分与作为所述配线的一部分的第1配线部重叠,将第2半导体元件配设在所述第1半导体元件上,且将具有比所述构件的所述热导率小的热导率的树脂配设在所述第2半导体元件与所述衬底间的区域的至少一部分。

[0009]

本发明的半导体装置的制造方法包括:将第1半导体元件设置在衬底的上表面,该

衬底在上表面形成配线且在下表面设置着连接于所述配线的电极,将第1构件配设在所述衬底的所述配线上,将第1间隔件配设在所述第1构件上,将第2构件配设在第2半导体元件的下表面,将配设在所述第2半导体元件的下表面的所述第2构件配设在所述第1半导体元件及所述第1间隔件上,且利用具有比所述第1构件的热导率及所述第2构件的热导率低的热导率的密封树脂,将所述第1半导体元件、所述第1间隔件及所述第2半导体元件密封。

[0010]

根据所述构成,能够提供一种半导体装置及半导体装置的制造方法,该半导体装置是具备覆晶连接的半导体元件的半导体装置,其中具备用来散热的构成。

附图说明

[0011]

图1是表示一实施方式的半导体装置在侧视下的截面的示意图。

[0012]

图2是表示一实施方式的第1半导体元件覆晶连接于配线衬底的时间点的构成在俯视及侧视下的截面的示意图。

[0013]

图3是一实施方式的散热片的一例。

[0014]

图4是表示一实施方式的半导体装置的制造工艺的示意图。

[0015]

图5是表示一实施方式中用来将散热片设置在fab膜上的工艺的示意图。

[0016]

图6是一实施方式中用于覆晶连接的附件的示意图。

[0017]

图7是表示侧视下的半导体存储器装置110的截面的示意图。

[0018]

图8是表示另一实施方式的第1半导体元件覆晶连接于配线衬底的时间点的构成在俯视及侧视下的截面的示意图。

[0019]

图9是表示又一实施方式的第1半导体元件覆晶连接于配线衬底的时间点的构成在俯视及侧视下的截面的示意图。

[0020]

图10是表示侧视下的半导体存储器装置410的截面的示意图。

[0021]

图11是表示半导体存储器装置410的制造工艺的示意图。

具体实施方式

[0022]

以下,参照附图对本实施方式进行说明。为了易于理解说明,对各附图中同一构成要素尽可能标注同一符号,并省略重复说明。

[0023]

[第1实施方式]以下,对本实施方式的半导体存储器装置10(“半导体装置”的一例)的构成进行说明。

[0024]

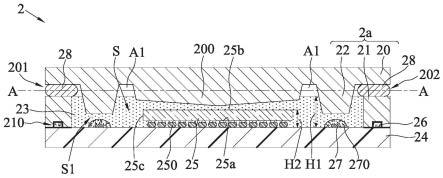

图1是表示侧视下的半导体存储器装置10的截面的示意图,图2是表示存储器控制器芯片20(“第1半导体元件”的一例;以下,有时称为控制器20)覆晶连接于配线衬底70(“衬底”的一例)的时间点的半导体存储器装置10在俯视及侧视下的剖视图的示意图。

[0025]

该半导体存储器装置10具备:配线衬底70,形成着配线76;控制器20,覆晶连接于配线衬底70;存储器芯片30(“第2半导体元件”的一例;以下,有时称为存储器30),设置在控制器20上;底部填充内圆角40(“第1树脂”的一例;以下,有时称为底部填充胶40),设置在包含控制器20与配线衬底70间的区域的区域中;及模具树脂50(“第2树脂”的一例),设置在包含存储器30与配线衬底70间的区域的区域中。进而,在半导体存储器装置10的底部填充胶40与模具树脂50之间设置散热片60(“构件”的一例)。

[0026]

散热片60以在俯视下一部分与控制器20上表面的至少一部分重叠的方式设置。如

图1及图2所示,本实施方式中的散热片60以覆盖控制器20的整个上表面的方式设置。

[0027]

另一方面,散热片60的另一部分以在俯视下与作为配线76的一部分的第1配线部76a重叠的方式设置。如图1及图2所示,本实施方式中的散热片60的另一部分以与第1配线部76a连接的方式设置。

[0028]

此外,第1配线部76a只要构成为能够散热即可,因此也可以不连接于用来收发信号的配线。进而,第1配线部76a也可以连接于用来供给vcc或vss等基准电位的配线(“电源线”的一例)。此外,第1配线部76a也可以连接于在与配线衬底70的表面平行的方向上延伸且形成为二维面状的配线区域(有时也称为实体部)。在本实施方式中,第1配线部76a经由通孔72连接于配线衬底70的下表面或背面所形成的二维的配线区域78及成为nc(non connection,非连接)端子的球形电极74。

[0029]

如上所述,半导体存储器装置10是封装着混载芯片的半导体存储器装置,该混载芯片是在控制器20上积层一个或多个nand(not and,与非)闪速型存储器30所得。如下所述,半导体存储器装置10具备由一个或多个间隔件32支撑存储器30的间隔件构造。半导体存储器装置10中也可以搭载dram(dynamic random access memory,动态随机存取存储器)或lsi(large-scale integration,大规模集成电路)等其他半导体元件。

[0030]

控制器20控制信息向存储器30的写入及信息从存储器30的读出。控制器20例如包含硅衬底,它是半导体存储器装置10中发热量最大的半导体元件。在控制器20的下表面形成着排列为阵列状的多个电极22、24。在电极22的端部形成着电极24。可以电极22含有ni、cu等,且电极24含有sn、au。也可以将这些电极22、24设为凸块电极。通过将多个凸块电极22、24与配线衬底70的配线76连接,控制器20覆晶连接于配线衬底70。控制器20发挥对存储器30与外部主机装置进行中介的功能,因此有时称为接口芯片。与凸块电极22、24连接的半导体电路形成在控制器20的下表面。

[0031]

存储器30例如为包含硅衬底的nand闪速型半导体存储器。存储器30形成为在俯视下大于控制器20。为了扩大存储容量,半导体存储器装置10也可以具备例如呈阶梯状地积层的多个存储器30。半导体存储器装置10也可以具备导线38,该导线38将形成在存储器30的上表面的电极与形成在配线衬底70的上表面或表面的电极连接。半导体存储器装置10也可以具备通过tsv(through-silicon via,硅通孔)连接的多个存储器30。

[0032]

半导体存储器装置10具备用来支撑存储器30的一个或多个间隔件32、及用来将间隔件32粘接于阻焊剂80的粘接膜34,进而具备设置在间隔件32上及控制器20上的daf(die attach film,芯片粘结膜)36。在本实施方式中,控制器20的上表面由散热片60覆盖,因此daf36通过在下表面粘接于间隔件32的上表面及散热片60的上表面,且在上表面粘接于存储器30的下表面,来支撑存储器30。此外,粘接膜34也可以是daf(die attach film)。

[0033]

底部填充胶40是填充在控制器20的多个凸块间以缓和对控制器20的凸块的应力的树脂。本实施方式中的底部填充胶40按照下述制造时所使用的附件94(图6)的形状而形成,因此以如下方式形成,即,覆盖控制器20的侧面,并且包含控制器20周围的底部填充胶40的上表面具有与控制器20的上表面为大致同一高度的部分(有时称为肩部)。但是,本发明并不限定于本实施方式的底部填充胶40的形状。例如,底部填充胶40也可以被具有其他形状的树脂代替,该树脂设置在控制器20与配线衬底70间的区域的至少一部分且填充在控制器20的凸块电极间。

[0034]

此外,如下所述,底部填充胶40有时会溢出到散热片60的外侧。此时,在某些情况下,溢出到散热片60外侧的底部填充胶40会在散热片60的外侧向上蔓延,因此有时在散热片60的外侧及内侧均局部地设置底部填充胶40。

[0035]

模具树脂50是用来将控制器20及存储器30密封的树脂,例如由环氧树脂等热硬化性树脂构成。在本实施方式中,控制器20配设在由散热片60覆盖的区域中。因此,模具树脂50设置在存储器30的周围及散热片60的外侧且存储器30与配线衬底70间的区域中。但是,模具树脂50有时会进入到散热片60的内侧。在该情况下,有时在散热片60的外侧及内侧均局部地设置模具树脂50。模具树脂50中,成为填料的玻璃纤维或无机物粒子的含量比底部填充胶40多。模具树脂50的弹性模量或杨氏模量比底部填充胶40大。

[0036]

配线衬底70是一层或多层印刷配线衬底,形成着用来进行控制器20与外部装置的信号收发的配线图案且由例如玻璃环氧衬底构成。

[0037]

在配线衬底70的上表面,形成着包含散热片60所连接的第1配线部76a的配线图案。第1配线部76a是用来将散热片60的热从配线衬底70释放的配线。在本实施方式中,第1配线部76a与散热片60连接。然而,第1配线部76a只要构成为能够散热即可,因此也可以未必与散热片60连接。如图2所示,本实施方式中的第1配线部76a在俯视下包围控制器20地形成。然而,如下所述,第1配线部76a并非必须以包围控制器20的方式形成,只要形成在配线衬底70上表面的一部分即可。但是,第1配线部76a优选在俯视下设置在控制器20的外侧。通过这种构成,能够使第1配线部76a容易与散热片60接近。

[0038]

在配线衬底70的背面或下表面,形成排列为阵列状的多个球形电极74以连接于安装衬底。如上所述,球形电极74包括散热片60所电连接的成为nc端子的球形电极74。

[0039]

在配线衬底70的下表面进而形成二维的配线区域78,该二维的配线区域78电连接于第1配线部76a,且在与配线衬底70的表面平行的方向上延伸。通过设置配线区域78,能够促进散热。但是,配线区域78也可以形成在配线衬底70的内层。

[0040]

在配线衬底70,进而形成着用来将第1配线部76a与下表面的球形电极74连接的通孔72(“第2配线部”的一例)。通孔72包含贯通配线衬底70的贯通孔及形成在贯通孔的内壁的配线。但是,也可以通过不贯通配线衬底70的通孔等,将第1配线部76a与下表面的球形电极74连接。

[0041]

在配线衬底70的上表面及下表面,分别设置用来保护配线衬底70的阻焊剂80。在阻焊剂80中,形成着用来使第1配线部76a的至少一部分向上方露出的开口80a。在本实施方式中,如图2所示,开口80a在俯视下包围控制器20地形成在与第1配线部重叠的区域。散热片60通过开口80a连接于第1配线部76a。第1配线部76a具有利用开口80a从阻焊剂80露出的露出部。

[0042]

散热片60经由配线衬底70将由控制器20产生的热释放。如上所述,在俯视下,散热片60的一部分与控制器20上表面的至少一部分重叠。进而,在俯视下,散热片60的另一部分与作为配线76的一部分的第1配线部76a重叠。因此,散热片60能够使从控制器20接收到的热逸出到第1配线部76a。

[0043]

本实施方式中的散热片60在侧视下连接于控制器20的上表面,且在连接于控制器20的上表面的部分具有从配线衬底70的表面到控制器20的上表面的高度(“第1高度”的一例)而设置,以随着接近第1配线部76a而接近配线衬底70的表面的方式下降,在与第1配线

部76a连接的部分具有与配线衬底70的表面大致相同的高度(“第2高度”的一例)而设置。但是,散热片60也可以未必与第1配线部76a连接。即便散热片60不与第1配线部76a连接,通过使散热片60与第1配线部76a接近,也能够使从控制器20接收到的热逸出到第1配线部76a。例如,散热片60也可以设置为将形成在阻焊剂80的开口80a封闭。

[0044]

散热片60具有至少比底部填充胶40及模具树脂50的热导率大的热导率。散热片60优选具有10w/m

·

k以上的热导率,进而优选具有50w/m

·

k以上的热导率。例如,散热片60可以由700w/m

·

k的结晶性石墨片构成。表1中,表示各种材料的热导率。

[0045]

[表1]

[0046][0047]

如表1所示,通常树脂的热导率为1w/m

·

k以下。构成本实施方式的底部填充胶40、模具树脂50、粘接膜34及daf36的任一种树脂的热导率也为1w/m

·

k以下。因此,散热片60具有散热片60内侧所配设的树脂及外侧所配设的树脂的热导率的10倍以上的热导率。

[0048]

散热片60可以不具有导电性(可以具有绝缘性),也可以具有导电性。与具有导电性的情况相比,不具有导电性的散热片60较少需要考虑对控制器20及存储器30产生的电气影响,因此能够提高设计自由度。具有导电性的散热片60例如通过连接于具有vss或接地等基准电位的配线,能够提高基准电位的稳定性。

[0049]

图3是表示具有绝缘性的散热片60的一例的示意图。图3(a)表示包含树脂膜60r的单层构造的散热片60的一例,该树脂膜60r混入了金属粉体60m且具有绝缘性及粘接性,图3(b)及(c)分别示出双层构造的散热片60b及双层构造的散热片60c,所述双层构造的散热片60b包含混入了金属粉体60m且具有绝缘性及粘接性的树脂膜60r以及无机材料膜62b,所述双层构造的散热片60c包含混入了金属粉体60m且具有绝缘性及粘接性的树脂膜60r以及散热性高的有机材料膜62c。通过这种构成,能够设置具有50w/m

·

k以上的热导率的散热片。

[0050]

根据如上构成的半导体存储器装置10,除了设置经由形成在控制器20下表面的凸块电极的第1散热路径以外,还设置经由散热片60的第2散热路径作为由控制器20产生的热的散热路径。因此,能够提高半导体存储器装置10的散热性能。

[0051]

进而,通过将设置在配线衬底70的下表面的球形电极74与散热片60连接的构成,能够使由控制器20产生的热逸出到供安装半导体存储器装置10的安装衬底,因此能够进一步提高散热性能。

[0052]

[半导体装置的制造方法]以下,将半导体存储器装置10的制造方法作为本发明的半导体装置的制造方法的一例,对此进行说明。

[0053]

图4是表示半导体存储器装置10的制造工艺的示意图。如该图所示,将硬化前的液状底部填充胶40(non conductive paste,非导电膏)滴加在形成着配线图案的配线衬底70的上表面上。

[0054]

接着,将散热片60与fab(film assist bonding,膜辅助接合)膜90积层。fab膜90是指覆晶连接时用来防止底部填充胶40向上蔓延的膜。

[0055]

图5是表示用来将散热片60设置在fab膜90上的工艺的示意图。如图5(a)所示,将散热片60与fab膜90积层后,可以构成为使用切割用辅具92将散热片60切断成所需形状,也可以取而代之地,如图5(b)所示,使用安装用辅具95,使已切断成所需形状的散热片60积层于fab膜90。此外,散热片60具有例如10~30μm的厚度。

[0056]

图6是覆晶连接用附件94的示意图。如该图所示,在覆晶连接用附件94的表面上设置fab膜90与散热片60的积层体。

[0057]

如该图所示,在附件94中设置端部94a、及从端部94a凹陷地形成的凹部94b。端部94a相当于从附件94突出到最下方的部位,在后视下,形成为包围凹部94b的矩形状。端部94a由具有弹性的弹性构件设置,凹部94b由具有刚性的例如陶瓷形成。在附件94中,进而分别形成将端部94a表面与上表面连通的吸附孔94c及将凹部94b表面与上表面连通的吸附孔94c。

[0058]

控制器20在面朝下地配设在这种附件94的凹部94b内的状态下,使端部94a表面及凹部94b表面与配线衬底70的上表面对向地向配线衬底70压抵,由此覆晶连接于配线衬底70。形成在控制器20的下表面的多个凸块电极(安装端子的一例,例如铜柱凸块电极)通过覆晶连接而与配线衬底70的配线76(包括电极)连接时,同时,位于附件94的端部94a的散热片60压抵于阻焊剂80中所形成的开口80a,由此,具有粘接性的散热片60通过开口80a连接于第1配线部76a。底部填充胶40由散热片60压出,按照散热片60或附件94的凹部94b的形状而成形。

[0059]

此后,通过施加热,使底部填充胶40硬化。底部填充胶40由于按照附件94的凹部94b的形状来硬化,因此,如上所述,能够以包含肩部的方式形成。因此,能够稳定地支撑控制器20及存储器30。图2中,示意性地表示控制器20覆晶连接于配线衬底70的时间点的构成。

[0060]

此后,通过已知工艺,将间隔件32设置在配线衬底70上,接着,使上表面粘接着存储器30的daf36的下表面粘接在间隔件32的上表面及散热片60的上表面,由此将存储器30积层在控制器20上。接着,通过引线接合并使用导线38,将设置在存储器30的上表面的电极与配线衬底70的电极连接。此外,也可以进一步积层第2片以下的存储器30。

[0061]

最后,通过模具树脂50,将存储器30密封。模具树脂50从间隔件32间进入到达散热片60的外表面的位置。

[0062]

根据如上工艺,能够制造散热性能高的半导体存储器装置10。另外,也能够按照附件94凹部的形状来控制底部填充胶40的形状。

[0063]

[第2实施方式]以下,对第2实施方式的半导体存储器装置110进行说明。此外,对于本领域技术人员能够理解到具有与包括第1实施方式在内的其他实施方式所揭示的构成

相同或类似的构成的部分,标注相同或类似符号并且省略说明,而以不同部分为中心进行说明。

[0064]

图7是表示侧视下的半导体存储器装置110的截面的示意图。

[0065]

该半导体存储器装置110在如下方面与第1实施方式的半导体存储器装置10共通,即,具备:配线衬底70,形成着配线76;控制器20,覆晶连接于配线衬底70;存储器30,设置在控制器20上;底部填充胶40,设置在包含控制器20与配线衬底70间的区域的区域中;及散热片60,设置在底部填充胶40上。在如下方面也与半导体存储器装置10共通,即,散热片60以在俯视下一部分与控制器20的上表面的至少一部分重叠的方式设置,且另一部分以在俯视下与作为配线76的一部分的第1配线部76a重叠的方式设置。

[0066]

然而,与半导体存储器装置10采用由间隔件32支撑存储器30的间隔件构造的情况相比,半导体存储器装置110在如下方面有所不同,即,采用由厚的daf136(“第2树脂”的一例)将控制器20埋入的fod(film on die,膜覆芯片)构造。

[0067]

即,除了所述构成以外,半导体存储器装置110具备设置在存储器30与配线衬底70间的区域中的daf136,且散热片60设置在daf136与底部填充胶40之间。daf136可以在俯视下,与存储器30全部重叠。也可以在俯视下,daf136的面积大于存储器30的面积。

[0068]

因此,模具树脂50以将存储器30的周围及daf136的外侧区域密封的方式设置。

[0069]

此外,图7中,也示出将设置在存储器30的上表面的电极与配线衬底70的配线76连接的导线38。

[0070]

根据如上构成的半导体存储器装置110,也除了设置经由形成在控制器20下表面的凸块电极的第1散热路径以外,还设置经由散热片60的第2散热路径作为由控制器20产生的热的散热路径。因此,能够提高半导体存储器装置110的散热性能。

[0071]

对于通过具备与其他实施方式同样的构成来发挥同样技术效果的部分省略说明。在其他实施方式中,也同样省略说明。

[0072]

此外,第1实施方式及第2实施方式所记载的半导体装置可以进而以如下方式进行变化。

[0073]

散热片60的内侧及外侧分别所设置的树脂可以由同一材质构成。例如,通过调整底部填充胶40的滴加量,构成为在覆晶连接时底部填充胶40向上蔓延到散热片60的外侧,能够实现由同一材质设置内侧树脂(“第1树脂”的一例)与外侧树脂(“第2树脂”的一例)的构成。

[0074]

另外,也可以在散热片60的外侧设置与树脂不同的绝缘体。例如,可以将半导体装置设置为在散热片60的外侧填充空气(air)。即便是这种构成,通过使用散热片60等具有10w/m

·

k以上的热导率的材料也能够提供散热效果得到提高的半导体装置。

[0075]

进而,散热片60也可以不覆盖控制器20的整个上表面。例如,也可以采用如下构成,即,设置具有小于控制器20上表面的长边及短边的宽度的带状构件来代替散热片60,并将控制器20上表面的一部分与第1配线部76a等连接。在这种构成中,也可能使树脂进入该散热构件的内侧,因此该散热构件的内侧及外侧分别所设置的树脂能够由同一材质构成。

[0076]

此外,也可以通过溅镀等设置相当于散热片的构成。例如,通过以控制器20、底部填充胶40到第1配线部76a连续地连接,并利用金属掩模等隐藏除此以外的部分的方式,使金属膜成膜,能够设置相当于散热片的构成。也可以代替金属掩模而通过光刻法利用光阻

剂进行遮蔽。或者,也可以在整个面成膜金属膜后,通过湿式蚀刻或干式蚀刻,去除不需要的部分。

[0077]

[第3实施方式]以下,对第3实施方式的半导体存储器装置210进行说明。此外,对于本领域技术人员能够理解到具有与包括第1实施方式在内的其他实施方式所揭示的构成相同或类似的构成的部分,标注相同或类似符号并且省略说明,而以不同部分为中心进行说明。

[0078]

图8是与第1实施方式的半导体存储器装置10的图2对应的附图,它是表示控制器20覆晶连接于配线衬底270(“衬底”的一例)的时间点的半导体存储器装置210在俯视及侧视下的剖视图的示意图。此外,在该图中,半导体存储器装置210所具备的存储器30等从图中省略。对图8所示的构成可以采用如图1所示的间隔件构造,也可以采用如图7所示的fod构造。

[0079]

该半导体存储器装置210在如下方面与第1实施方式的半导体存储器装置10共通,即,具备:配线衬底270,形成着配线276;控制器20,覆晶连接于配线衬底270;存储器30,设置在控制器20上;及底部填充胶40,设置在包含控制器20与配线衬底70间的区域的区域中;进而在半导体存储器装置210的底部填充胶40上设置散热片60。

[0080]

如图2所示,第1实施方式中的配线76的第1配线部76a在俯视下包围控制器20地形成。另一方面,如图8所示,第3实施方式中的配线276的第1配线部276a以在俯视下不包围控制器20的方式形成。进而,配线276具备3个第3配线部276c,这些第3配线部276c与第1配线部276a分开且绝缘地设置。

[0081]

即,在俯视下,第1配线部276a设置在控制器20的纸面右下的角部外侧,第一个第3配线部276c设置在控制器20的纸面右上的角部外侧,第二个第3配线部276c设置在控制器20的纸面左上的角部外侧,第三个第3配线部276c设置在控制器20的纸面左下的角部外侧。

[0082]

如图2所示,第1实施方式中的形成在阻焊剂80的开口80a在俯视下包围控制器20地形成在与第1配线部76a重叠的区域。如图8所示,第3实施方式中的形成在阻焊剂280的开口280a在俯视下以不包围控制器20的方式形成在与第1配线部276a重叠的区域。进而,三个开口280c相互分开地形成在分别与第3配线部276c重叠的区域。

[0083]

散热片60通过开口280a连接于第1配线部276a,且通过三个开口280c分别连接于第3配线部276c。散热片60的其他周边部连接于阻焊剂280。

[0084]

根据如上构成的半导体存储器装置210,除了设置经由形成在控制器20下表面的凸块电极的第1散热路径以外,还设置经由散热片60的第2散热路径作为由控制器20产生的热的散热路径。因此,能够提高半导体存储器装置210的散热性能。

[0085]

此外,由于第1配线部276a以不包围控制器20的方式形成,因此能够在第1配线部276a与第3配线部276c的间隙及第3配线部276c与其他第3配线部276c的间隙的区域形成配线图案。例如,能够在配线衬底270的上表面(l1)设置用来与控制器20连接的配线图案。

[0086]

[第4实施方式]以下,对第4实施方式的半导体存储器装置310进行说明。此外,对于本领域技术人员能够理解到具有与包括其他实施方式在内的其他实施方式所揭示的构成相同或类似的构成的部分,标注相同或类似符号并且省略说明,而以不同部分为中心进行说明。

[0087]

图9是与第1实施方式的半导体存储器装置10的图2对应的附图,它是控制器20覆

晶连接于配线衬底70的时间点的半导体存储器装置310在俯视及侧视下的剖视图的示意图。此外,在该图中,半导体存储器装置310所具备的存储器30等从图中省略。对图9所示的构成可以采用如图1所示的间隔件构造,也可以采用如图7所示的fod构造。

[0088]

该半导体存储器装置310在如下方面与第1实施方式的半导体存储器装置10共通,即,具备:配线衬底70,形成着配线76;控制器20,覆晶连接于配线衬底70;存储器30,设置在控制器20上;及底部填充内圆角340(“第1树脂”的一例;以下,有时称为底部填充胶340),设置在包含控制器20与配线衬底70间的区域的区域中;进而在半导体存储器装置310的底部填充胶340上设置散热片360。

[0089]

然而,与散热片60连接于第1配线部76a的情况相比,在如下方面有所不同,即,半导体存储器装置310的散热片360介隔底部填充胶340而分开地设置在第1配线部76a的上方。

[0090]

进而,与底部填充胶40在俯视下设置在散热片60内部的情况相比,在如下方面有所不同,即,半导体存储器装置310的底部填充胶340具有在俯视下溢出到散热片360外侧的部分。即,底部填充胶340从控制器20与配线衬底70间的区域经由散热片360与第1配线部76a间的区域延伸到散热片360的外侧。

[0091]

半导体存储器装置310的散热片360设置在底部填充胶340与模具树脂50或daf136等第2树脂之间。该散热片360以如下方式设置,即,在侧视下,以配线衬底70的上表面为基准在设置在控制器20的上表面的上端部分具有第1高度,以越接近第1配线部76a则越接近配线衬底70的上表面的方式下降,且在相当于与第1配线部76a的上方分开的位置的下端部分具有第2高度。底部填充胶340也设置在散热片360与第1配线部76a间。

[0092]

如该图所示,底部填充胶340的端部蔓延到散热片360的外侧。

[0093]

根据这种半导体存储器装置310,通过在与第1配线部76a的上方分开的位置设置散热片360,也能够将散热片360的热传递到第1配线部76a。因此,在半导体存储器装置310中,也除了设置经由形成在控制器20下表面的凸块电极的第1散热路径以外,还设置经由散热片60的第2散热路径作为由控制器20产生的热的散热路径。因此,能够提高半导体存储器装置310的散热性能。

[0094]

[第5实施方式]

[0095]

以下,对第5实施方式的半导体存储器装置410进行说明。此外,对于本领域技术人员能够理解到具有与包括第1实施方式在内的其他实施方式所揭示的构成相同或类似的构成的部分,标注相同或类似符号并且省略说明,而以不同部分为中心进行说明。

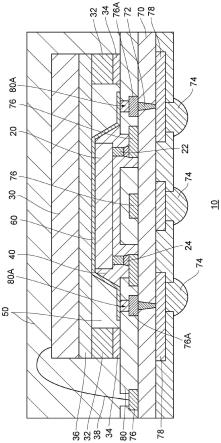

[0096]

图10是表示侧视下的半导体存储器装置410的截面的示意图。图11是表示半导体存储器装置410的制造工艺的示意图。

[0097]

该半导体存储器装置410在如下方面与半导体存储器装置10共通,即,具备:配线衬底70,形成着配线76;控制器20,覆晶连接于配线衬底70;存储器30,设置在控制器20上;一个或多个间隔件32(“第1间隔件”的一例),用来支撑存储器30;及模具树脂50,将存储器30及间隔件32密封,且设置在存储器30与配线衬底70间的区域的至少一部分。

[0098]

然而,与半导体存储器装置10的daf36及粘接膜34具有1w/m

·

k以下的热导率的情况相比,在如下方面有所不同,即,半导体存储器装置410的导热性daf436(“第2构件”的一例)及导热性粘接构件434(“第1构件”的一例)各自具有1w/m

·

k以上50w/m

·

k以下的热导

率。更优选为10w/m

·

k以上。另外,在如下方面也有所不同,即,半导体存储器装置410不具备相当于散热片60的构成。

[0099]

导热性daf436构成为使控制器20上表面的热逸出到间隔件32的上表面。因此,导热性daf436具有导热性及粘接性。在本实施方式中,导热性daf436包含绝缘性树脂及树脂436r所含的例如氧化铝的金属粉体436m。氧化铝具有30/m

·

k以上40/m

·

k以下的热导率,因此通过使氧化铝混入到具有粘接性的树脂中,能够设置具有绝缘性及导热性的构件。同样地,通过设置导热性粘接构件434,能够设置具有绝缘性及导热性的构件。

[0100]

这些导热性daf436及导热性粘接构件434具有比具有1w/m

·

k以下的热导率的模具树脂50大的热导率。因此,如图10中箭头所示,能够设置第2散热路径,该第2散热路径用来使由控制器20产生的热从控制器20的上表面经由导热性daf436、间隔件32及导热性粘接构件434再经由第1配线部76a逸出到配线衬底70的配线76。

[0101]

此外,间隔件32含有具有100w/m

·

k以上的高导热性的硅。

[0102]

进而,在本实施方式中,在俯视下与间隔件32重叠的位置形成着通孔72,因此能够进一步提高散热效果。

[0103]

另外,由于配线76经由通孔72电连接于二维的配线区域78(实体部)及球形电极74,因此能够使热从配线衬底70的下表面或背面侧逸出。

[0104]

此外,本实施方式的半导体存储器装置410进而具备粘接于daf436的上表面及存储器30的下表面的粘接片439。

[0105]

通过设置这种粘接片439,能够抑制控制器20的热传递到存储器30侧。

[0106]

进而,粘接片439优选包含可粘接温度低于daf436的可粘接温度的热硬化树脂。通过设为这种构成,将图11(a)所示的粘接片439粘接于存储器30时,能够以比daf436的可粘接温度低的温度(“第1温度”的一例)将粘接片439粘接于存储器30,因此能够抑制daf436变形。此时,粘接片439热硬化,因此在将图11(b)所示的daf436粘接于控制器20及间隔件32的上表面时,即便以相对高的温度(“第2温度”的一例)粘接,也能够抑制粘接片439软化。进而,通过使用软化时的daf436的粘性低的树脂,也能够补偿控制器20与间隔件32的高度差异。

[0107]

以上,参照具体例对本实施方式进行了说明。然而,本发明并不限定于这些具体例。本领域技术人员对这些具体例适当施加设计变更所得的内容也包括在本发明的范围内,只要具备本发明的特征即可。所述各具体例所具备的各要素及其配置、条件、形状等并不限定于例示内容,可以适当进行变更。所述各具体例所具备的各要素可以适当改变组合,只要不产生技术上的矛盾即可。

[0108]

(a)例如,也可以将图1所示的daf36及粘接膜34分别设为daf436及导热性粘接构件434。通过采用这种构成,能够进一步提高散热效果。(b)例如,在第5实施方式中,也可以采用底部填充胶40,进而形成散热片60。此时,第1配线部76a不仅设置在间隔件32之下,而且也设置在与散热片60重叠的位置。在散热片之上设置导热性daf436及第2半导体元件。通过采用这种构成,能够进一步提高散热效果。

[0109]

(c)本发明的半导体装置具备:衬底,形成着配线;第1半导体元件,设置在所述衬底;第2半导体元件,设置在所述第1半导体元件上;导线,将所述第2半导体元件与所述衬底连接;第1树脂,设置在所述第1半导体元件与所述衬底间的区域的至少一部分;第2树脂,设

置在所述第2半导体元件与所述衬底间的区域的至少一部分;及构件,具有比所述第1树脂的热导率及所述第2树脂的热导率大的热导率,设置在所述第1树脂与所述第2树脂之间,且在俯视下,一部分与所述第1半导体元件的上表面重叠并且另一部分与作为所述配线的一部分的第1配线部重叠。

[0110]

(d)本发明的半导体装置具备:衬底,形成着配线;第1半导体元件,设置在所述衬底;第2半导体元件,设置在所述第1半导体元件上;第1树脂,设置在所述第1半导体元件与所述衬底间的区域的至少一部分;绝缘体,配设在所述第2半导体元件与所述衬底间的区域的至少一部分;及构件,具有比所述第1树脂的热导率及所述绝缘体的热导率大的热导率,设置在所述第1树脂与所述绝缘体之间,且在俯视下,一部分与所述第1半导体元件的上表面重叠并且另一部分与作为所述配线的一部分的第1配线部重叠。

[0111]

(e)本发明的半导体装置具备:衬底,形成着配线;第1半导体元件,设置在所述衬底,且设置在下表面的电极连接于所述衬底;第2半导体元件,设置在所述第1半导体元件上,在俯视下大于所述第1半导体元件,且发热量比所述第1半导体元件小;导线,将所述第2半导体元件的上表面与所述衬底连接;底部填充胶,在所述第1半导体元件与所述衬底间的区域将所述电极密封;第2树脂,配设在所述第2半导体元件与所述衬底间的区域;及构件,具有10w/m

·

k以上的热导率,设置在所述底部填充胶与所述第2树脂之间,且在俯视下,一部分与所述第1半导体元件的上表面重叠并且另一部分与作为所述配线的一部分的第1配线部重叠,在侧视下,所述一部分在从所述衬底的上表面起的第1高度的位置连接于所述第1半导体元件的上表面,所述另一部分在从所述衬底的上表面起的小于所述第1高度的第2高度的位置设置在所述第1配线部上。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。