1.本发明涉及半导体封装领域,尤其涉及一种封装结构及其形成方法。

背景技术:

2.在半导体制程中,封装是指将通过测试的晶圆按照产品型号及功能需求加工得到独立芯片的过程,是制造芯片的最后一环。

3.具体的,现有技术的封装过程中,首先,将来自晶圆前道工艺的晶圆通过划片工艺切割为若干小的晶片(die),接着,将切割好的晶片固定在引线框架上,并且,利用超细的金属导线或导电性树脂将晶片的接合焊盘外接,然后,再对独立的晶片用塑料外壳加以封装保护。

4.然而,现有的封装方法所形成的封装结构外接方式单一,应用局限性较大、集成度较差。

技术实现要素:

5.是提供一种封装结构及其形成方法,以提高封装结构外接方式的灵活性,减少应用局限性、提高集成度。

6.为解决上述技术问题,本发明的技术方案提供一种封装结构,包括:第一半封装结构,所述第一半封装结构包括:若干第一晶片,所述第一晶片具有相对的第一面和第二面;位于若干所述第一晶片的侧壁面和第二面的第一钝化层,所述第一钝化层具有相对的第三面和第四面,所述第四面高于所述第二面;位于所述第一钝化层内的第一连接层,所述第一连接层包括若干第一导电结构和若干第二导电结构,所述第一导电结构自所述第四面朝向第三面贯穿所述第一钝化层,所述第二导电结构接触所述第二面;位于所述第四面上且与所述第一连接层电连接的第二连接结构;固定于所述第三面的若干第二电子部件,所述第二电子部件与所述第一导电结构电连接。

7.可选的,若干第二电子部件焊接于所述第三面;若干第二电子部件包括若干电阻、若干电容、以及第二半封装结构中的至少一种。

8.可选的,若干第二电子部件包括:第三晶片和若干导线,所述第三晶片键合于所述第一面和第三面中的至少一者,所述导线与第三面暴露的第一导电结构表面接触并连接所述第三晶片的电路。

9.可选的,还包括:固定于所述第二连接结构上的第三半封装结构。

10.可选的,所述第一半封装结构还包括:位于所述若干第一晶片中的至少1个第一晶片内的若干第三导电结构,所述第三导电结构自所述第二面朝向所述第一面贯穿所述至少1个第一晶片。

11.可选的,所述第二连接结构包括:再布线层、以及位于所述再布线层上的焊接层;所述再布线层包括:再布线导电层、以及位于所述再布线导电层侧壁面的绝缘层。

12.相应的,本发明的技术方案还提供一种封装结构的形成方法,包括:形成第一半封

装结构,所述第一半封装结构的形成方法包括:提供承载基底;提供若干第一晶片,所述第一晶片具有相对的第一面和第二面;将若干所述第一晶片固定在所述承载基底上,所述第一面朝向承载基底;将若干所述第一晶片固定在所述承载基底上之后,形成第一钝化层、以及位于所述第一钝化层内的第一连接层,所述第一钝化层位于部分所述承载基底、以及若干所述第一晶片的侧壁和第二面上,所述第一钝化层具有相对的第三面和第四面,所述第三面固定于所述承载基底,所述第四面高于所述第二面,所述第一连接层包括若干第一导电结构和若干第二导电结构,所述第一导电结构自所述第四面朝向第三面贯穿所述第一钝化层,所述第二导电结构接触所述第二面;在所述第四面上形成与所述第一连接层电连接的第二连接结构;在形成所述第二连接结构之后,去除所述承载基底;提供若干第二电子部件;在去除所述承载基底后,将若干第二电子部件固定于所述第三面,所述第二电子部件与所述第一导电结构电连接。

13.可选的,若干第二电子部件包括:第三晶片和若干导线;将若干第二电子部件固定于所述第三面的方法包括:将所述第三晶片与所述第一面和第三面中的至少一者键合;使所述导线与第三面暴露的第一导电结构表面接触并连接第三晶片的电路。

14.可选的,还包括:提供第三半封装结构;在去除所述承载基底后,将所述第三半封装结构固定于所述第二连接结构上。

15.可选的,将若干所述第一晶片固定在所述承载基底上的方法包括:在所述承载基底上形成粘合层;将若干所述第一晶片的第一面粘附于所述粘合层。

16.可选的,所述第一钝化层和第一连接层的形成方法包括:在所述承载基底上形成钝化材料层,所述钝化材料层的表面高于所述第二面;对所述钝化材料层进行刻蚀,形成位于若干所述第一晶片的侧壁和第二面、以及部分所述承载基底上的第一钝化层,所述第一钝化层内具有若干第一开口和若干第二开口,所述第一开口的底部暴露出所述承载基底的表面,所述第二开口的底部暴露出所述第二面;在若干所述第一开口内、若干所述第二开口内、以及所述第四面形成第一连接材料层;平坦化所述第一连接材料层直至暴露出所述第四面,形成所述第一连接层。

17.可选的,所述第一半封装结构的形成方法还包括:在形成所述第一钝化层和第一连接层的过程中,在所述若干第一晶片中的至少1个第一晶片内形成若干第三导电结构,所述第三导电结构自所述第二面朝向所述第一面贯穿所述至少1个第一晶片;所述第一钝化层、第一连接层和若干第三导电结构的形成方法包括:在所述承载基底上形成表面高于所述第二面的钝化材料层;对所述钝化材料层和所述若干第一晶片中的至少1个第一晶片进行刻蚀,形成位于若干所述第一晶片的侧壁和第二面、以及部分所述承载基底上的第一钝化层,所述第一钝化层内具有若干第一开口和若干第二开口,所述第一开口的底部暴露出所述承载基底的表面,所述第二开口的底部暴露出所述第二面,并且,在所述至少1个第一晶片内形成若干第三开口,所述第三开口自所述第二面朝向所述第一面贯穿所述至少1个第一晶片;在若干所述第一开口内、若干所述第二开口内、若干所述第三开口内、以及所述第四面形成第一连接材料层;平坦化所述第一连接材料层直至暴露出所述第四面,形成所述第一连接层和若干所述第三导电结构。

18.可选的,所述第二连接结构包括:再布线层、以及位于所述再布线层上的焊接层;所述再布线层包括:再布线导电层、以及位于所述再布线导电层侧壁面的再布线绝缘层;所

述再布线层的形成方法包括:在所述第四面和第一连接层的表面形成再布线导电材料层;在所述再布线导电材料层表面形成再布线图形化层;以所述再布线图形化层为掩膜,刻蚀所述再布线导电材料层,直至暴露出所述第四面,形成与所述第一连接层电连接的再布线导电层;在所述再布线导电层的侧壁面形成再布线绝缘层;所述焊接层的形成方法包括:在所述再布线层上形成牺牲层;在所述牺牲层内形成若干焊接凹槽,所述焊接凹槽的底部暴露出所述再布线导电层的表面;在若干所述焊接凹槽内形成初始焊接层;形成所述初始焊接层之后,去除所述牺牲层;去除所述牺牲层之后,对所述初始焊接层进行流平处理,形成位于所述再布线层上的焊接层。

19.可选的,还包括:在去除所述承载基底的过程中,自所述第一面减薄若干所述第一晶片、所述第一钝化层和若干所述第一导电结构。

20.与现有技术相比,本发明实施例的技术方案具有以下有益效果:

21.本发明的技术方案提供的封装结构中,第一半封装结构包括:位于若干所述第一晶片的侧壁面和第二面的第一钝化层,所述第一钝化层具有相对的第三面和第四面,所述第四面高于所述第二面;位于所述第一钝化层内的第一连接层,所述第一连接层包括若干第一导电结构和若干第二导电结构,所述第一导电结构自所述第四面朝向第三面贯穿所述第一钝化层,所述第二导电结构接触所述第二面;位于所述第四面上且与所述第一连接层电连接的第二连接结构。因此,所述第一半封装结构相对两侧中的一侧(所述第三面所在的一侧)暴露出所述第一导电结构的表面,所述第一半封装结构相对两侧中的另一侧(所述第四面所在的一侧)具有与所述第一连接层电连接的第二连接结构,使得所述第一半封装结构可根据应用需求,在所述第三面固定与所述第一导电结构电连接的若干第二电子部件,同时,可根据应用需求,自由选择是否通过所述第一半封装结构的第二导电结构连接其他半封装结构。从而,实现了若干电子元件和若干半封装结构之间的灵活堆叠与连接,由此,所述封装结构的外接灵活性高,且能够增加单位面积内的半封装结构的数量、减小封装结构的面积,以提高集成度。

附图说明

22.图1至图2是一种封装结构形成过程的示意图;

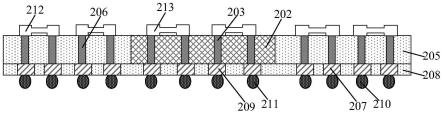

23.图3至图12是本发明一实施例的封装结构的形成过程中各步骤的剖面结构示意图;

24.图13是本发明又一实施例的封装结构的剖面结构示意图;

25.图14是本发明又一实施例的封装结构的剖面结构示意图;

26.图15至图22是本发明另一实施例的封装结构的形成过程中各步骤的剖面结构示意图;

27.图23是本发明又一实施例的封装结构的剖面结构示意图;

28.图24是本发明又一实施例的封装结构的剖面结构示意图。

具体实施方式

29.如背景技术所述,现有的封装方法所形成的封装结构外接方式单一,应用局限性较大。现结合一具体的实施例进行分析说明。

30.图1至图2是一种封装结构形成过程的示意图。

31.请参考图1,提供承载基板100;在所述承载基板100上形成粘合层101。

32.请继续参考图1,提供晶片102,所述晶片102具有相对的功能面和非功能面;将所述晶片102固定于所述粘合层101上,所述非功能面朝向所述承载基板100。

33.请参考图2,在所述承载基板100和所述晶片102上形成第一钝化层110;在所述第一钝化层110内形成与晶片102电连接的布线层120;在所述第一钝化层110和布线层120上形成第二钝化层130;在所述第二钝化层130内形成连接所述布线层的焊接层140,所述第二钝化层130的表面暴露出所述焊接层140的表面。

34.然而,上述方法所形成的封装结构外接方式单一,仅能通过所述焊接层140所在的一侧与其他半封装结构、电子元件连接,应用起来具有较大的局限性且集成度较差。

35.为解决上述技术问题,本发明的技术方案提供一种封装结构及其形成方法,由于第一半封装结构包括:位于若干所述第一晶片的侧壁面和第二面的第一钝化层,所述第一钝化层具有相对的第三面和第四面,所述第四面高于所述第二面;位于所述第一钝化层内的第一连接层,所述第一连接层包括若干第一导电结构和若干第二导电结构,所述第一导电结构自所述第四面朝向第三面贯穿所述第一钝化层,所述第二导电结构接触所述第二面;位于所述第四面上且与所述第一连接层电连接的第二连接结构。因此,实现了若干电子元件和若干半封装结构之间的灵活堆叠与连接,由此,所述封装结构的外接灵活性高,且能够增加单位面积内的半封装结构的数量、减小封装结构的面积,以提高集成度。

36.为使本发明的上述目的、特征和有益效果能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

37.图3至图12是本发明一实施例的封装结构的形成过程中各步骤的剖面结构示意图。

38.首先,形成第一半封装结构。具体形成所述第一半封装结构的方法请参考图3至图11。

39.请参考图3,提供承载基底200。

40.所述承载基底200的材料包括半导体材料或无机材料。

41.具体的,所述半导体材料包括硅板,所述无机材料包括钢化玻璃。

42.相比一些现有技术采用的承载框架(mold frame),由于所述承载基底200的材料包括半导体材料或无机材料,因此,后续形成封装结构的过程中,所述承载基底200不易弯曲和形变,且易被去除,从而,可简化封装工艺、减短封装流程、提高封装结构的良率。

43.请参考图4,提供第一晶片210,所述第一晶片210具有相对的第一面211和第二面212。

44.请参考图5,将所述第一晶片210固定在所述承载基底200上,所述第一面211朝向所述承载基底200。

45.在本实施例中,将所述第一晶片210固定在所述承载基底200上的方法包括:在所述承载基底200上形成粘合层205;将所述第一晶片210的第一面211粘附于所述粘合层205。

46.所述粘合层205的材料具有粘性,因此,通过所述粘合层205能够将所述第一晶片210固定在所述承载基底200上。

47.在本实施例中,所述粘合层205为daf膜(die attach film)。具体的,所述daf膜为

高导热的树脂胶。

48.接着,形成第一钝化层、以及位于所述第一钝化层内的第一连接层,所述第一钝化层位于部分所述承载基底200、以及所述第一晶片210的侧壁和第二面212上。

49.其中,所述第一钝化层具有相对的第三面和第四面,所述第三面固定于所述承载基底200,所述第四面高于所述第二面212。所述第一连接层包括若干第一导电结构和若干第二导电结构,所述第一导电结构自所述第四面朝向所述第三面贯穿所述第一钝化层,所述第二导电结构接触所述第二面212。

50.在本实施例中,在形成所述第一钝化层和第一连接层的过程中,在所述第一晶片210内形成若干第三导电结构,所述第三导电结构自所述第二面212朝向所述第一面211贯穿所述第一晶片210。

51.通过在所述第一晶片210内形成若干第三导电结构,且所述第三导电结构自所述第二面212朝向所述第一面211贯穿所述第一晶片210,进一步增加了自第一晶片210向外引线的灵活性、以及后续形成的封装结构的外接方式的灵活性。

52.在一些其他实施例中,不在第一晶片内形成若干第三导电结构。

53.具体的,所述第一钝化层、所述第一连接层和若干所述第三导电结构的形成过程请参考图6至图8。

54.请参考图6,在所述承载基底200上形成钝化材料层220a,所述钝化材料层220a的表面高于所述第二面212。

55.具体而言,所述钝化材料层覆盖所述第一晶片210。

56.在本实施例中,所述钝化材料层220a的材料包括有机材料,所述有机材料包括聚亚酰胺(polyimide,pi)或聚对苯撑苯并二恶唑(poly-p-phenylene benzobisoxazole,pbo)。

57.在本实施例中,形成所述钝化材料层220a之后,对所述钝化材料层220a进行固化处理。

58.具体的,所述固化处理的工艺包括:热固化处理。

59.请参考图7,对所述钝化材料层220a和所述第一晶片210进行刻蚀,形成第一钝化层220b,并在所述第一晶片210内形成若干第三开口213。

60.所述第一钝化层220b位于所述第一晶片210的侧壁和第二面212、以及部分所述承载基底200上,所述第一钝化层220b具有相对的第三面223和第四面224,所述第三面223固定于所述承载基底200,所述第四面224高于所述第二面212。

61.使所述第一钝化层220b位于部分所述承载基底200上的目的在于:将所述第一钝化层220b与承载基底200的其他区域上的钝化材料隔开,或者,去除承载基底200的其他区域上的钝化材料,以在后续去除所述承载基底200之后,能够直接形成独立的封装结构。

62.所述第一钝化层220b内具有若干第一开口221和若干第二开口222,所述第一开口221的底部暴露出所述承载基底200的表面,所述第二开口222的底部暴露出所述第二面212。

63.相应的,在本实施例中,所述第一钝化层220b的材料包括有机材料,所述有机材料包括聚亚酰胺或聚对苯撑苯并二恶唑。

64.所述第三开口213自所述第二面212朝向第一面211贯穿所述第一晶片210。

65.所述第一开口221为后续形成第一导电结构提供空间,所述第二开口222为后续形成第二导电结构提供空间,所述第三开口213为后续形成第三导电结构提供空间。

66.本实施例中,对所述钝化材料层220a和所述第一晶片210进行刻蚀的方法包括:在所述钝化材料层220a的表面形成掩膜层(未图示),所述掩膜层暴露出部分所述钝化材料层220a的表面;以所述掩膜层为掩膜,对所述钝化材料层220a和所述第一晶片210进行刻蚀,形成所述第一钝化层220b和所述第三开口213。

67.请参考图8,在若干所述第一开口221内、若干所述第二开口222内、若干所述第三开口213内、以及所述第四面224形成第一连接材料层(未图示);接着,平坦化所述第一连接材料层直至暴露出所述第四面224,形成第一连接层230和若干第三导电结构240。

68.在本实施例中,所述第一连接层230与所述第一晶片210中的电路耦合。

69.在本实施例中,所述第一连接层230包括:若干第一导电结构231和若干第二导电结构232,所述第一导电结构231自所述第四面224朝向所述第三面223贯穿所述第一钝化层220b,所述第二导电结构232接触所述第二面212。

70.在本实施例中,所述第一连接层230的材料包括金属,具体的,所述金属包括铜。

71.在本实施例中,若干所述第三导电结构240与所述第一连接层230和所述第一晶片210中的电路中的至少一者耦合。

72.具体的,所述第三导电结构240自所述第二面212朝向所述第一面211贯穿所述第一晶片210。

73.在本实施例中,所述第三导电结构240的材料包括金属,具体的,所述金属包括铜。

74.一些其他实施例中,在第一晶片内形成若干第三导电结构,接着,在承载基底上形成第一钝化层、以及位于所述第一钝化层内的第一连接层。具体的,所述第三导电结构、第一钝化层和第一连接层的形成方法包括:在承载基底和第一晶片上形成第一掩膜层,所述第一掩膜层暴露出第一晶片的部分第二面;以所述第一掩膜层为掩膜刻蚀所述第一晶片,形成贯通所述第一晶片的若干第三开口;形成若干第三开口之后,去除所述第一掩膜层;去除所述第一掩膜层之后,在每个第三开口内形成第三导电结构;形成若干第三导电结构之后,在所述承载基底上形成钝化材料层,所述钝化材料层的表面高于第一晶片的第二面;在所述钝化材料层的表面形成第二掩膜层,所述第二掩膜层暴露出部分钝化材料层的表面;以所述第二掩膜层为掩膜,刻蚀所述钝化材料层,在所述第一晶片的侧壁和第二面、以及部分所述承载基底上形成第一钝化层,所述第一钝化层内具有若干第一开口和若干第二开口,所述第一开口的底部暴露出所述承载基底的表面,所述第二开口的底部暴露出所述第一晶片的第二面或所述第三导电结构的顶面;在若干第一开口、若干第二开口和第一钝化层的第四面上形成第一连接材料层;平坦化所述第一连接材料层,直至暴露出所述第一钝化层的第四面,形成第一连接层。

75.另一些其他实施例中,在后续形成第二连接结构之前,在第一钝化层和第一连接层上形成若干层堆叠的中间第一钝化层、以及位于每层中间第一钝化层内且贯穿所述中间第一钝化层的中间导电结构。每层中间第一钝化层和中间导电结构的形成方法请参考图6至图8中的第一钝化层220b及第一导电结构231的形成方法,在此不在赘述。

76.接着,在所述第四面224上形成与所述第一连接层230电连接的第二连接结构。本实施例中的第二连接结构包括:再布线层、以及位于所述再布线层上的焊接层。具体形成所

述第二连接结构的过程请参考图9和图10。

77.请参考图9,在所述第四面224上形成再布线层250。

78.在本实施例中,所述再布线层250包括:再布线导电层251、以及位于所述再布线导电层251侧壁面的再布线绝缘层252。

79.在本实施例中,所述再布线导电层251的材料包括金属,具体的,所述金属包括铜。

80.在本实施例中,所述再布线绝缘层252的材料包括介电材料,具体的,所述介电材料包括有机材料,所述有机材料包括聚亚酰胺(polyimide,pi)或聚对苯撑苯并二恶唑(poly-p-phenylene benzobisoxazole,pbo)。

81.在本实施例中,所述再布线层250的形成方法包括:在所述第四面224和第一连接层230的表面形成再布线导电材料层(未图示);在所述再布线导电材料层表面形成再布线图形化层(未图示);以所述再布线图形化层为掩膜,刻蚀所述再布线导电材料层,直至暴露出所述第四面224,形成与所述第一连接层230电连接的再布线导电层251;在所述再布线导电层251的侧壁面形成再布线绝缘层252。

82.请参考图10,在所述再布线层250上形成焊接层260。

83.由此,形成第二连接结构270,并且,所述第二连接结构270包括:再布线层250、以及位于所述再布线层250上的焊接层260。

84.在本实施例中,所述焊接层260的材料包括焊锡、锡铅合金焊锡、加锑焊锡、加镉焊锡、加银焊锡或加铜焊锡。

85.在本实施例中,所述焊接层260的形成方法包括:在所述再布线层250上形成牺牲层(未图示);在所述牺牲层内形成若干焊接凹槽(未图示),所述焊接凹槽的底部暴露出所述再布线导电层251的表面;在若干所述焊接凹槽内形成初始焊接层(未图示);形成所述初始焊接层之后,去除所述牺牲层;去除所述牺牲层之后,对所述初始焊接层进行流平处理,形成位于所述再布线层250上的焊接层260。

86.请参考图11,在形成所述第二连接结构270之后,去除所述承载基底200。

87.在本实施例中,去除所述承载基底200的工艺包括:背磨工艺(back-grinding)。

88.在本实施例中,在去除所述承载基底200的过程中,去除所述粘合层205。

89.在一些其他实施例中,在去除所述承载基底200的过程中,还通过背磨工艺自所述第一面211对所述第一晶片210、所述第一钝化层220b和若干所述第一导电结构231进行减薄。从而进一步节约了第一半封装结构所占的空间。

90.至此,形成第一半封装结构。

91.接着,请参考图12,提供若干第二电子部件。

92.在本实施例中,若干第二电子部件包括:第二半封装结构410。

93.在本实施例中,所述第二半封装结构410包括:若干第二晶片411;位于若干所述第二晶片411顶面、底面和侧壁面的第二钝化层412;位于所述第二钝化层412内且与所述第二晶片411耦合的第二布线层413;位于所述第二布线层413上的第二焊接层414。

94.在其他实施例中,第二半封装结构还可以是与第一半封装结构相同的半封装结构,以通过所述第三面所在的一侧实现多个半封装结构的堆叠。

95.在又一实施例中,若干第二电子部件包括:若干电容420(如图13所示)。

96.在一些其他实施例中,若干第二电子部件包括:若干电阻。

97.在另一些其他实施例中,若干第二电子部件包括:若干电阻、若干电容和第二半封装结构中的至少二者。

98.在又一实施例中,若干第二电子部件包括:第三晶片430(如图14所示)和若干导线431(如图14所示)。

99.请继续参考图12,在去除所述承载基底200后,将若干第二电子部件固定于所述第三面223,所述第二电子部件与所述第一导电结构231电连接。

100.具体的,本实施例中,将所述第二半封装结构410固定于第三面223的工艺包括焊接。

101.在又一实施例中,如图13中所示,将所述电容420固定于第三面223的工艺包括焊接。

102.在一些其他实施例中,将所述电阻固定于第三面的工艺包括焊接。

103.在又一实施例中,如图14中所示,将若干第二电子部件固定于所述第三面223的方法包括:将所述第三晶片430与所述第一面211和第三面223中的至少一者键合;使所述导线431与第三面223暴露的第一导电结构231表面接触,并且,使所述导线431连接第三晶片430的电路。

104.在本实施例中,所述第二电子部件还与第三导电结构240电连接。

105.在一些其他实施例中,第二电子部件不与第三导电结构电连接。

106.在本实施例中,所述封装结构的形成方法还包括:提供第三半封装结构(未图示);在去除所述承载基底200后,将所述第三半封装结构固定于所述第二连接结构270上。

107.需要理解的是,根据实际的工艺制造需求,若干所述第二电子部件可先于或者后于所述第三半封装结构与所述第一半封装结构进行固定及连接。

108.在本实施例中,所述第三半封装结构是与所述第一半封装结构相同的半封装结构,以通过所述第二连接结构270所在的一侧实现多个半封装结构的堆叠外接。

109.在一些其他实施例中,第三半封装结构也可以是与所述第二半封装结构相同的半封装结构。

110.在另一些其他实施例中,第一半封装结构不外接第三半封装结构。

111.相应的,本发明一实施例还提供一种上述封装结构的形成方法所形成的封装结构,请继续参考图12,包括:第一半封装结构和若干第二电子部件。

112.所述第一半封装结构包括:第一晶片210,所述第一晶片210具有相对的第二面211和第二面212;位于所述第一晶片210的侧壁面和所述第二面212的第一钝化层220b,所述第一钝化层220b具有相对的第三面223和第四面224,所述第四面224高于所述第二面212;位于所述第一钝化层220b内的第一连接层230,所述第一连接层230包括若干第一导电结构231和若干第二导电结构232,所述第一导电结构231自所述第四面224朝向所述第三面223贯穿所述第一钝化层220b,所述第二导电结构232接触所述第二面212;位于所述第四面224上且与所述第一连接层230电连接的第二连接结构270。

113.若干所述第二电子部件固定于所述第三面223,所述第二电子部件与所述第一导电结构231电连接。

114.由于所述封装结构中,第一半封装结构包括:位于所述第一晶片210的侧壁面和所述第二面212的第一钝化层220b,所述第一钝化层220b具有相对的第三面223和第四面224,

所述第四面224高于所述第二面212;位于所述第一钝化层220b内的第一连接层230,所述第一连接层230包括若干第一导电结构231和若干第二导电结构232,所述第一导电结构231自所述第四面224朝向所述第三面223贯穿所述第一钝化层220b,所述第二导电结构232接触所述第二面212;位于所述第四面224上且与所述第一连接层230电连接的第二连接结构270。因此,所述第一半封装结构相对两侧中的一侧(所述第三面223所在的一侧)暴露出所述第一导电结构231的表面,所述第一半封装结构相对两侧中的另一侧(所述第四面224所在的一侧)具有与所述第一连接层230电连接的第二连接结构270,使得所述第一半封装结构可根据应用需求,在所述第三面223固定与所述第一导电结构270电连接的若干第二电子部件,同时,可根据应用需求,自由选择是否通过所述第一半封装结构的第二导电结构270连接其他半封装结构。从而,实现了若干电子元件和若干半封装结构之间的灵活堆叠与连接,由此,所述封装结构的外接灵活性高,且能够增加单位面积内的半封装结构的数量、减小封装结构的面积,以提高集成度。

115.在本实施例中,所述第一钝化层220b的材料包括有机材料,所述有机材料包括聚亚酰胺或聚对苯撑苯并二恶唑。

116.在本实施例中,所述第一连接层230与所述第一晶片210中的电路耦合。

117.在本实施例中,所述第一连接层230的材料包括金属,具体的,所述金属包括铜。

118.在本实施例中,所述第一半封装结构还包括:位于第一晶片210中的若干第三导电结构240,所述第三导电结构240自所述第二面212朝向所述第一面211贯穿所述第一晶片210,所述第一面211暴露出所述第三导电结构240的表面。若干所述第三导电结构240与所述第一连接层230和所述第一晶片210中的电路中的至少一者耦合。通过所述第一晶片210内的所述第三导电结构240,进一步增加了自第一晶片210向外引线的灵活性、以及后续形成的封装结构的外接方式的灵活性。

119.在本实施例中,所述第三导电结构240的材料包括金属,具体的,所述金属包括铜。

120.在一些其他实施例中,第一晶片内不具有第三导电结构。

121.在本实施例中,所述第二连接结构270包括:再布线层250、以及位于所述再布线层250上的焊接层260。

122.在本实施例中,所述再布线层250包括:再布线导电层251、以及位于所述再布线导电层251侧壁面的再布线绝缘层252。

123.在本实施例中,所述再布线导电层251的材料包括金属,具体的,所述金属包括铜。

124.在本实施例中,所述再布线绝缘层252的材料包括介电材料,具体的,所述介电材料包括有机材料,所述有机材料包括聚亚酰胺(polyimide,pi)或聚对苯撑苯并二恶唑(poly-p-phenylene benzobisoxazole,pbo)。

125.在本实施例中,所述焊接层260的材料包括焊锡、锡铅合金焊锡、加锑焊锡、加镉焊锡、加银焊锡或加铜焊锡。

126.另一些其他实施例中,第一半封装结构还包括:位于第二连接结构与第一钝化层和第一连接层之间的若干层堆叠的中间第一钝化层、以及位于每层中间第一钝化层内且贯穿所述中间第一钝化层的中间导电结构。从而,进一步提升了再布线的灵活性。

127.在本实施例中,若干第二电子部件包括:第二半封装结构410。

128.在本实施例中,所述第二半封装结构410包括:若干第二晶片411;位于若干所述第

二晶片411顶面、底面和侧壁面的第二钝化层412;位于所述第二钝化层412内且与所述第二晶片411耦合的第二布线层413;位于所述第二布线层413上的第二焊接层414。

129.在其他实施例中,第二半封装结构还可以是与第一半封装结构相同的半封装结构,以通过所述第三面所在的一侧实现多个半封装结构的堆叠。

130.在本实施例中,所述第二半封装结构410焊接于所述第三面223。

131.在本实施例中,所述第二半封装结构410还与第三导电结构240电连接。

132.在一些其他实施例中,第二电子部件不与第三导电结构电连接。

133.在又一实施例中,如图13所示,若干第二电子部件包括:若干电容420。具体的,若干电容420焊接于所述第三面223。

134.在一些其他实施例中,若干第二电子部件包括:若干电阻。具体的,所述电阻焊接于第三面。

135.在另一些其他实施例中,若干第二电子部件包括:若干电阻、若干电容和第二半封装结构中的至少二者。

136.在又一实施例中,如图14所示,若干第二电子部件包括:第三晶片430和若干导线431,所述第三晶片430键合于所述第一面211和第三面223中的至少一者,所述导线431与第三面223暴露的第一导电结构231表面接触,并且,所述导线431连接第三晶片430的电路。

137.在本实施例中,所述封装结构还包括:固定于所述第二连接结构270上的第三半封装结构。

138.在本实施例中,所述第三半封装结构是与所述第一半封装结构相同的半封装结构,以通过所述第二连接结构270所在的一侧实现多个半封装结构的堆叠外接。

139.在一些其他实施例中,第三半封装结构也可以是与所述第二半封装结构相同的半封装结构。

140.在另一些其他实施例中,第一半封装结构不外接第三半封装结构。

141.图15至图22是本发明另一实施例的封装结构的形成过程中各步骤的剖面结构示意图。

142.首先,形成第一半封装结构。

143.请在图3的基础上参考图15,提供2个以上的第一晶片310,所述第一晶片310具有相对的第一面311和第二面312。

144.需要说明的是,所述2个以上的第一晶片310可以是相同的第一晶片,也可以是不同的第一晶片。例如,所述2个以上的第一晶片310可以均为存储芯片,所述2个以上的第一晶片310也可以包括逻辑芯片和存储芯片等。后续通过将2个以上的第一晶片310共同进行封装,进一步提升了封装的自由度。

145.请参考图16,将2个以上的所述第一晶片310固定在所述承载基底200上,所述第一面311朝向所述承载基底200。

146.在本实施例中,将各所述第一晶片310固定在所述承载基底200上的方法包括:在所述承载基底200上形成粘合层305;将各所述第一晶片310的第一面311粘附于所述粘合层305。

147.所述粘合层305的材料具有粘性,因此,通过所述粘合层305能够将各所述第一晶片310固定在所述承载基底200上。

148.在本实施例中,所述粘合层305为daf膜(die attach film)。具体的,所述daf膜为高导热的树脂胶。

149.接着,形成第一钝化层、以及位于所述第一钝化层内的第一连接层,所述第一钝化层位于部分所述承载基底200、以及各所述第一晶片310的侧壁和第二面312上。

150.其中,所述第一钝化层具有相对的第三面和第四面,所述第三面固定于所述承载基底200,所述第四面高于所述第二面312。所述第一连接层包括若干第一导电结构和若干第二导电结构,所述第一导电结构自所述第四面朝向所述第三面贯穿所述第一钝化层,所述第二导电结构接触所述第二面312。

151.具体的,所述第一钝化层和所述第一连接层的形成过程请参考图14至图16。

152.请参考图17,在所述承载基底200上形成钝化材料层320a,所述钝化材料层320a的表面高于所述第二面312。

153.具体而言,所述钝化材料层覆盖各所述第一晶片310。

154.在本实施例中,所述钝化材料层320a的材料包括有机材料,所述有机材料包括聚亚酰胺或聚对苯撑苯并二恶唑。

155.在本实施例中,形成所述钝化材料层320a之后,对所述钝化材料层320a进行固化处理。

156.具体的,所述固化处理的工艺包括:热固化处理。

157.请参考图18,对所述钝化材料层320a进行刻蚀,形成位于各所述第一晶片310的侧壁和第二面312、以及部分所述承载基底200上的第一钝化层320b。

158.使所述第一钝化层320b位于部分所述承载基底200上的目的在于:将所述第一钝化层320b与承载基底200的其他区域上的钝化材料隔开,或者,去除承载基底200的其他区域上的钝化材料,以在后续去除所述承载基底200之后,能够直接形成独立的封装结构。

159.所述第一钝化层320b具有相对的第三面323和第四面324,所述第三面323固定于所述承载基底200,所述第四面324高于所述第二面312。此外,所述第一钝化层320b内具有若干第一开口321和若干第二开口322,所述第一开口321的底部暴露出所述承载基底200的表面,所述第二开口322的底部暴露出所述第二面312。

160.相应的,在本实施例中,所述第一钝化层320b的材料包括有机材料,所述有机材料包括聚亚酰胺或聚对苯撑苯并二恶唑。

161.本实施例中,对所述钝化材料层320a进行刻蚀的方法包括:在所述钝化材料层320a的表面形成掩膜层(未图示),所述掩膜层暴露出部分所述钝化材料层320a的表面;以所述掩膜层为掩膜,对所述钝化材料层320a进行刻蚀,直至形成所述第一钝化层320b。

162.请参考图19,在若干所述第一开口321内、若干所述第二开口322内、以及所述第四面324形成第一连接材料层(未图示);平坦化所述第一连接材料层直至暴露出所述第四面324,形成所述第一连接层330。

163.在本实施例中,所述第一连接层330与各所述第一晶片310的电路耦合。

164.在本实施例中,所述第一连接层330包括:若干第一导电结构331和若干第二导电结构332,所述第一导电结构331自所述第四面324朝向所述第三面323贯穿所述第一钝化层320b,所述第二导电结构332接触所述第二面312。

165.在本实施例中,所述第一连接层330的材料包括金属,具体的,所述金属包括铜。

166.本实施例中,平坦化所述第一连接材料层的工艺包括化学机械研磨工艺。

167.在一些其他实施例中,在形成所述第一钝化层320b和第一连接层230的过程中,在所述2个以上第一晶片310中的至少1个第一晶片310内形成若干第三导电结构,所述第三导电结构自所述第二面312朝向所述第一面311贯穿所述至少1个第一晶片310。具体的,在所述2个以上第一晶片310中的至少1个第一晶片310内形成若干第三导电结构的方法请参考图3至图12所示实施例中若干第三导电结构240的形成方法,在此不在赘述。

168.请参考图20,在所述第四面324上形成与所述第一连接层330电连接的第二连接结构370。

169.在本实施例中,所述第二连接结构370包括:再布线层350、以及位于所述再布线层350上的焊接层360。

170.在本实施例中,所述再布线层350包括:再布线导电层351、以及位于所述再布线导电层351侧壁面的再布线绝缘层352。

171.在本实施例中,所述再布线导电层351的材料包括金属,具体的,所述金属包括铜。

172.在本实施例中,所述再布线绝缘层352的材料包括介电材料,具体的,所述介电材料包括有机材料,所述有机材料包括聚亚酰胺(polyimide,pi)或聚对苯撑苯并二恶唑(poly-p-phenylene benzobisoxazole,pbo)。

173.在本实施例中,所述焊接层360的材料包括焊锡、锡铅合金焊锡、加锑焊锡、加镉焊锡、加银焊锡或加铜焊锡。

174.在本实施例中,形成所述第二连接结构370的具体方法请参考图3至图11中第二连接结构270的形成方法,在此不在赘述。

175.请参考图21,在形成所述第二连接结构370之后,去除所述承载基底200。

176.在本实施例中,去除所述承载基底200的具体方法请参考图3至图11所示实施例中承载基底200的去除方法,在此不再赘述。

177.在一些其他实施例中,在去除所述承载基底200的过程中,还通过背磨工艺自所述第一面311对所述第一晶片310、所述第一钝化层320b和若干所述第一导电结构331进行减薄。从而,进一步节约了封装结构所占的空间。

178.至此,形成第一半封装结构。

179.接着,请参考图22,提供若干第二电子部件。

180.在本实施例中,若干第二电子部件包括:第二半封装结构510。

181.在本实施例中,所述第二半封装结构510包括:若干第二晶片511;位于若干所述第二晶片511顶面、底面和侧壁面的第二钝化层512;位于所述第二钝化层512内且与所述第二晶片511耦合的第二布线层513;位于所述第二布线层513上的第二焊接层514。

182.在其他实施例中,第二半封装结构还可以是与第一半封装结构相同的半封装结构,以通过所述第三面所在的一侧实现多个半封装结构的堆叠。

183.在又一实施例中,若干第二电子部件包括:若干电容520(如图23所示)。

184.在一些其他实施例中,若干第二电子部件包括:若干电阻。

185.在另一些其他实施例中,若干第二电子部件包括:若干电阻、若干电容和第二半封装结构中的至少二者。

186.在又一实施例中,若干第二电子部件包括:第三晶片530(如图24所示)和若干导线

531(如图24所示)。

187.请继续参考图22,在去除所述承载基底200后,将若干第二电子部件固定于所述第三面323,所述第二电子部件与所述第一导电结构331电连接。

188.具体的,本实施例中,将所述第二半封装结构510固定于第三面323的工艺包括焊接。

189.在又一实施例中,如图23中所示,将所述电容520固定于第三面323的工艺包括焊接。

190.在一些其他实施例中,将所述电阻固定于第三面的工艺包括焊接。

191.在又一实施例中,如图24中所示,将若干第二电子部件固定于所述第三面323的方法包括:将所述第三晶片530与所述第一面311和第三面323中的至少一者键合;使所述导线531与第三面323暴露的第一导电结构331表面接触,并且,使所述导线531连接第三晶片530的电路。

192.在一些其他实施例中,第二电子部件还与第三导电结构电连接。

193.在本实施例中,所述封装结构的形成方法还包括:提供第三半封装结构(未图示);在去除所述承载基底200后,将所述第三半封装结构固定于所述第二连接结构370上。

194.需要理解的是,根据实际的工艺制造需求,若干所述第二电子部件可先于或者后于所述第三半封装结构与所述第一半封装结构进行固定及连接。

195.在本实施例中,所述第三半封装结构是与所述第一半封装结构相同的半封装结构,以通过所述第二连接结构370所在的一侧实现多个半封装结构的堆叠外接。

196.在一些其他实施例中,第三半封装结构也可以是与所述第二半封装结构相同的半封装结构。

197.在另一些其他实施例中,第一半封装结构不外接第三半封装结构。

198.相应的,本发明另一实施例还提供了一种上述封装结构的形成方法所形成的封装结构,请继续参考图22,包括:第一半封装结构和若干第二电子部件。

199.所述第一半封装结构包括:2个以上第一晶片310,所述第一晶片310具有相对的第二面311和第二面312;位于各所述第一晶片310的侧壁面和第二面312的第一钝化层320b,所述第一钝化层320b具有相对的第三面323和第四面324,所述第四面324高于所述第二面312;位于所述第一钝化层320b内的第一连接层330,所述第一连接层330包括若干第一导电结构331和若干第二导电结构332,所述第一导电结构331自所述第四面324朝向所述第三面323贯穿所述第一钝化层320b,所述第二导电结构332接触所述第二面312;位于所述第四面324上且与所述第一连接层330电连接的第二连接结构370。

200.若干所述第二电子部件固定于所述第三面323,所述第二电子部件与所述第一导电结构331电连接。

201.在本实施例中,所述第一钝化层320b的材料包括有机材料,所述有机材料包括聚亚酰胺或聚对苯撑苯并二恶唑。

202.在本实施例中,所述第一连接层330与各所述第一晶片310的电路耦合。

203.在本实施例中,所述第一连接层330的材料包括金属,具体的,所述金属包括铜。

204.在一些其他实施例中,所述第一半封装结构还包括:所述2个以上第一晶片310中的至少1个第一晶片310内的若干第三导电结构,所述第三导电结构自所述第二面312朝向

所述第一面311贯穿所述至少1个第一晶片310,所述第一面311暴露出所述第三导电结构的表面。若干所述第三导电结构与所述第一连接层330和所述至少1个第一晶片310的电路中的至少一者耦合。通过所述第三导电结构进一步增加了自第一晶片310向外引线的灵活性、以及后续形成的封装结构的外接方式的灵活性。

205.在一些其他实施例中,第二电子部件还与第三导电结构电连接。

206.在本实施例中,所述第二连接结构370包括:再布线层350、以及位于所述再布线层350上的焊接层360。

207.在本实施例中,所述再布线层350包括:再布线导电层351、以及位于所述再布线导电层351侧壁面的再布线绝缘层352。

208.在本实施例中,所述再布线导电层351的材料包括金属,具体的,所述金属包括铜。

209.在本实施例中,所述再布线绝缘层352的材料包括介电材料,具体的,所述介电材料包括有机材料,所述有机材料包括聚亚酰胺(polyimide,pi)或聚对苯撑苯并二恶唑(poly-p-phenylene benzobisoxazole,pbo)。

210.在本实施例中,所述焊接层360的材料包括焊锡、锡铅合金焊锡、加锑焊锡、加镉焊锡、加银焊锡或加铜焊锡。

211.在本实施例中,若干第二电子部件包括:第二半封装结构510。

212.在本实施例中,所述第二半封装结构510包括:若干第二晶片511;位于若干所述第二晶片511顶面、底面和侧壁面的第二钝化层512;位于所述第二钝化层512内且与所述第二晶片511耦合的第二布线层513;位于所述第二布线层513上的第二焊接层514。

213.在其他实施例中,第二半封装结构还可以是与第一半封装结构相同的半封装结构,以通过所述第三面所在的一侧实现多个半封装结构的堆叠。

214.在本实施例中,所述第二半封装结构510焊接于所述第三面323。

215.在又一实施例中,如图23所示,若干第二电子部件包括:若干电容520。具体的,若干电容520焊接于所述第三面323。

216.在一些其他实施例中,若干第二电子部件包括:若干电阻。具体的,所述电阻焊接于第三面。在另一些其他实施例中,若干第二电子部件包括:若干电阻、若干电容和第二半封装结构中的至少二者。

217.在又一实施例中,如图24所示,若干第二电子部件包括:第三晶片530和若干导线531,所述第三晶片530键合于所述第一面311和第三面323中的至少一者,所述导线531与第三面323暴露的第一导电结构331表面接触,并且,所述导线531连接第三晶片530的电路。

218.在本实施例中,所述封装结构还包括:固定于所述第二连接结构370上的第三半封装结构。本实施例中,所述第三半封装结构是与所述第一半封装结构相同的半封装结构,以通过所述第二连接结构370所在的一侧实现多个半封装结构的堆叠外接。

219.在一些其他实施例中,第三半封装结构也可以是与所述第二半封装结构相同的半封装结构。在另一些其他实施例中,第一半封装结构不外接第三半封装结构。

220.虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。