一种基于jesd204b协议的多板卡同步采样装置

技术领域

1.本发明属于模数转换器同步采样技术,具体为一种基于jesd204b协议的多板卡同步采样装置。

背景技术:

2.adc采样技术被广泛应用于雷达、通信、电子战和医疗成像等探测领域。随着adc分辨率和采样速率的提高,传统的lvds(低压差分信号)并行接口协议越来越不能满足更高速率的数据传输需求。为满足adc更高的传输速率需求,联合电子设备工程委员会提出了jesd204b协议,该协议是一种串行接口协议,主要用于adc/dac(模数/数模转换器)和逻辑器件之间的数据传输。相比较于lvds接口协议,jesd204b协议的速率带宽高达12.5g,且减少了adc芯片上的数据管脚,方便了电路布局设计。虽然基于jesd204b协议的adc芯片在传输速率和芯片尺寸上优势明显,但其需要额外的同步参考时钟,增加了硬件系统的复杂性。

3.此外,由于制造工艺的偏差,2个以上数量的adc通常会在上电周期间存在采样不同步现象,具体表现为采样数据在时间上具有不一样的时延。为解决2片以上adc的同步采样问题,许多研究人员使用基于jesd204b协议的adc芯片,在单块板卡上进行了相关研究。陈洋等人在《基于jesd204b协议的相控阵雷达下行同步采集技术应用》验证了单块板卡上8片adc的同步采样,黄润龙在专利cn211264148u中提出了在单块板卡上用24片adc的同步采样装置。

4.随着adc芯片数量进一步扩展,受限于板卡尺寸,更多的adc芯片将被分布在不同的板卡上。与单块板卡相比较,不同板卡间的数据传输链路更长,带来了更高的同步采样难度。为解决多板卡间的同步采样难题,刘仁华在《多路射频同步采集系统设计与实现》提出一种主从板卡架构,板间的同步采样由来自主板卡的时钟保证。然而,随着从板卡数量的进一步扩展,主板卡上输出的时钟数量也需要再增加,增加了硬件上设计的冗余度。同时到从板卡上时钟相位需要多次调整,同步速度慢。崔艳松等人在专利cn108134607a中提出一种板间adc同步采样电路及同步方法,但其同样需要额外的同步方法,来调整采集板上hm7043芯片输出采样时钟与参考时钟的相对相位关系,以获得相对时序要求,增加了板卡之间达到同步采样的时间。

5.综上,现有基于jesd204b协议的adc采样技术,在单块板卡内可以满足同步采样要求,但在扩展到多块板卡上时,都额外需要对时钟相位进行调整的步骤,使得多块板卡上电后不能及时获得同步采样的功能,具有一定的局限性。

技术实现要素:

6.本发明的目的是为了克服已有同步采样技术的不足,为了解决基于jesd204b协议的adc芯片,分布在多板卡上所带来的同步采样问题,提出一种多板卡同步采装置。

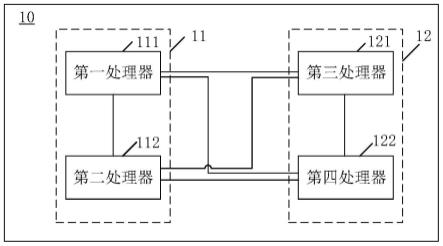

7.实现本发明目的的技术方案为:一种基于jesd204b协议的多板卡同步采样装置,包括n块同步控制板和m块中频采样板所;所述同步控制板用于向各个中频采样板发送相参

时钟和控制信号;所述m块中频采样板硬件结构相同,所述同步控制板通过射频电缆和控制电缆分别与所述m块中频采样板连接,所述射频电缆均为等相射频电缆,使同步控制板到各个中频采样板的相参时钟达到相位同步,所述控制电缆为等长电缆,使同步控制板到各个中频采样板的控制信号达到同步。

8.优选地,所述同步控制板包括1片fpga、x片lmk04828芯片和y片hmc7043芯片,y片hmc7043芯片放置在lmk04828芯片周边,lmk04828芯片扇出到hmc7043芯片的时钟线进行等长设计,满足从lmk04828芯片输出的时钟同步到达y片hmc7043芯片;fpga通过spi接口完成对x片lmk04828芯片和y片hmc7043芯片寄存器的并行配置;x片lmk04828芯片和y片hmc7043芯片实现到所有中频采样板的时钟相参;lmk04828芯片接收外部时钟,通过内部锁相环扇出2种时钟到各个hmc7043,一路时钟到fpga;y片hmc7043芯片接收来自lmk04828芯片的时钟后,扇出m个同频率的采样时钟,每路采样时钟通过射频电缆连接到任意一块中频采样板;fpga接收lmk04828芯片输出的一路时钟,在时钟节拍下,输出m路相同频率的sysref同步信号,每路sysref同步信号连接至任意一块中频采样板上,m路sysref同步信号实现所有中频采样板上lmk04828芯片输出的时钟同步。

9.优选地,单块中频采样板包括z片lmk04828芯片和i片j通道的adc芯片,用来实现i*j通道的采样功能;m块中频采样板实现总共m*i*j通道的采样功能。

10.优选地,i片adc芯片放置在lmk04828芯片周边,lmk04828芯片扇出到i片adc芯片的时钟线进行等长设计,满足从lmk04828芯片输出的时钟同步到达i片adc芯片。lmk04828芯片设计为分配功能模式,lmk04828芯片上clkin1引脚接收来自同步控制板的采样时钟,通过时钟分配路径扇出到各个adc芯片;lmk04828芯片上clkin0引脚,接收来自同步控制板的sysref同步信号,扇出到各个adc芯片;所有采样时钟和sysref同步信号,在中频采样板上满足布线等长设计,保证板内采样时钟和sysref同步信号的相对相位关系;i*j个通道的采样数据以jesd204b接口协议,送至中频采样板下的fpga芯片。

11.优选地,两种时钟为器件时钟和系统参考时钟,器件时钟作为hmc7043芯片的时钟输入,系统参考时钟用于同步hmc7043芯片输出的采样时钟。

12.优选地,器件时钟和系统参考时钟在pcb上满足布线等长设计。

13.优选地,sysref同步信号频率f

sysref

满足:

[0014][0015]

其中,f

bitrate

表示高速收发器的线速率,f表示每帧的字节数,k表示帧数,n为任意正整数,在满足信号传输质量的情况下,n越大越好。

[0016]

优选地,m个同频率的采样时钟满足布线等长设计。

[0017]

优选地,中频采样板上lmk04828芯片到i片adc芯片上的采样时钟和sysref同步信号要满足布线等长设计。

[0018]

本发明与有技术相比,具有以下优点:

[0019]

(1)通道扩展性高:同步控制板上每增加1片hmc7043,即可多扩展14个相参时钟,对应14块中频采样板,以每块中频采样板可完成8通道的采样为例,即增加14x8=112个通道的采样功能。

[0020]

(2)板卡间同步自动化:不需要进行额外的时钟相位调整步骤,上电即自动实现所

有中频采样板上adc的同步采样。

附图说明

[0021]

此处所说明的附图用来提供对本发明实施例的进一步理解,构成本技术的一部分,并不构成对本发明实施例的限定。在附图中:

[0022]

图1为实施例的电路原理图。

具体实施方式

[0023]

为使本发明的目的、技术方案和优点更加清楚明白,下面结合实施例的附图,以单块(n=1)同步控制板和8块(m=8)中频采样板为例,对本发明作进一步的详细说明。同步控制板包括1(x=1)片lmk04828芯片和2(y=1)片hmc7043芯片,单块中频采样板包括1(z=1)片lmk04828芯片,2(i=2)片4(j=4)通道的adc芯片。本发明的示意性实施方式及其说明仅用于解释本发明,并不作为对发明的限定。

[0024]

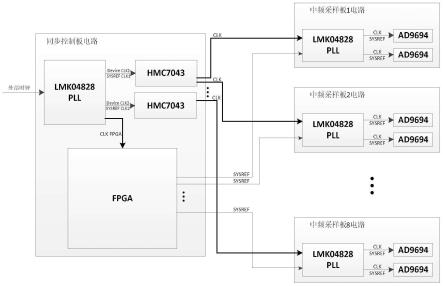

本实施例提出了一种基于jesd204b协议的多板卡同步采样装置,电路原理如图1所示,包括1块同步控制板和8块中频采样板;所述同步控制板用于向各个中频采样板发送相参时钟和控制信号;所述8块中频采样板硬件结构相同,所述同步控制板通过射频电缆和控制电缆分别与所述8块中频采样板连接,所述射频电缆均为等相射频电缆,使同步控制板到各个中频采样板的相参时钟达到相位同步,所述控制电缆为等长电缆,使同步控制板到各个中频采样板的控制信号达到同步。

[0025]

如图1所示同步控制板的电路图布局,左边位置是1片lmk04828芯片,右边是2片hmc7043芯片。2片hmc7043芯片与lmk04828芯片距离等长,便于对lmk04828芯片扇出到hmc7043芯片的时钟线进行等长设计。满足从lmk04828芯片输出的时钟同步到达2片hmc7043芯片。

[0026]

如图1所示中频采样板的电路图布局,左边位置是lmk04828芯片,右边2片adc芯片与lmk04828芯片距离等长。本发明中频采样板上adc芯片到lmk04828芯片的等长放置,便于对lmk04828芯片扇出到2片adc芯片的时钟线进行等长设计,满足从lmk04828芯片输出的时钟同步到达2片adc芯片。

[0027]

同步控制板是实现所有中频采集板进行同步采样的关键。同步控制板包括1片fpga、1片lmk04828芯片和2片hmc7043芯片。fpga通过spi接口完成对1片lmk04828芯片和2片hmc7043芯片寄存器的并行配置。1片lmk04828芯片和2片hmc7043芯片实现到所有中频采样板的时钟相参。lmk04828芯片接收外部时钟,通过内部锁相环扇出2种时钟到各个hmc7043,一路时钟到fpga。这两种时钟为器件时钟(device clk1~device clk2)和系统参考时钟(sysref clk1~sysref clk2)。器件时钟用于hmc7043芯片的时钟输入,系统参考时钟用于同步hmc7043芯片输出的采样时钟。每片hmc7043芯片接收来自lmk04828芯片的器件时钟后,扇出14个同频率的采样时钟(clk)。采样时钟通过射频电缆连接到任意一块中频采样板。fpga接收lmk04828芯片输出的一路时钟(clk_fpga),经过分频处理,通过引脚输出8路sysref同步信号至各个中频采样板上的lmk04828芯片。sysref同步信号与hmc7043芯片扇出至中频采样板的采样时钟满足确定性相位关系。8路sysref同步信号实现所有中频采样板上lmk04828芯片输出的时钟同步。

[0028]

中频采样板包括1片lmk04828芯片和2片adc芯片。lmk04828芯片设计为分配功能模式。lmk04828芯片上clkin1引脚,接收来自同步控制板的采样时钟,通过时钟分配路径扇出到各个adc芯片。lmk04828芯片上clkin0引脚,接收来自同步控制板的sysref同步信号,扇出到各个adc芯片。所有采样时钟和sysref同步信号,在中频采样板上要满足布线等长设计,从而设计保证板内采样时钟和sysref同步信号的相对相位关系。每片adc芯片完成4个通道的信号采样,单块中频采样板完成所有8个通道的信号采样。8个通道的采样数据以jesd204b接口协议送至中频采样板下的fpga芯片。

[0029]

以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。

[0030]

应当理解,为了精简本发明并帮助本领域的技术人员理解本发明的各个方面,在上面对本发明的示例性实施例的描述中,本发明的各个特征有时在单个实施例中进行描述,或者参照单个图进行描述。但是,不应将本发明解释成示例性实施例中包括的特征均为本专利权利要求的必要技术特征。

[0031]

应当理解,可以对本发明的一个实施例的设备中包括的模块、单元、组件等进行自适应性地改变以把它们设置在与该实施例不同的设备中。可以把实施例的设备包括的不同模块、单元或组件组合成一个模块、单元或组件,也可以把它们分成多个子模块、子单元或子组件。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。