1.本技术涉及核电厂转速设备控制技术领域,特别是涉及一种调速器和调速器的控制方法。

背景技术:

2.在核电站工艺系统设计中,给水流量控制系统控制整个核电站二回路用水需求。该给水流量控制系统基于汽动主给水泵转速调节来改变供水流量和压力,实现向三台蒸汽发生器供水,同时消除三台蒸汽发生器之间给水耦合现象,用以保证蒸汽发生器的给水母管和蒸汽母管之间的压差等于一个随机组负荷变化的整定值,因此汽动主给水泵的转速调节在维持蒸汽发生器水位稳定,保证机组安全中起到至关重要的作用。

3.现汽轮机的调速器多由电子调速器或单套控制系统进行控制,系统的可靠性低,经常由于单点故障引起停机。

技术实现要素:

4.基于此,有必要针对上述技术问题,提供一种冗余程度高可以避免单点故障的调速器和调速器的控制方法。

5.为了实现上述目的及其他目的,本技术的一方面提供了一种调速器,包括:两个控制电路,每一所述控制电路包括两个处理器,四个所述处理器之间彼此连接,同一所述控制电路中的两个所述处理器的类型不同;

6.当主控制电路中的处理器故障时,所述主控制电路中的故障处理器向从控制电路中的第一目标处理器发送同步信息,以使所述第一目标处理器与第二目标处理器连接构成目标数据传输通路,实现数据传输;

7.其中,所述第一目标处理器为所述从控制电路中与所述故障处理器的类型相同的处理器,所述第二目标处理器与所述第一目标处理器的类型不同,所述主控制电路为两个所述控制电路中的一个,所述从控制电路为两个所述控制电路中的另一个。

8.在其中一个实施例中,当主控制电路中的一个处理器故障时,所述第二目标处理器为所述主控制电路中的正常处理器;当主控制电路中的两个处理器均故障时,所述第二目标处理器为所述从控制电路中的处理器。

9.在其中一个实施例中,所述主控制电路中的待诊断处理器分别向其他三个处理器发送检验信息,以使所述其他三个处理器根据所述检验信息生成诊断信息;

10.所述调速器还包括:

11.仲裁模块,分别与四个所述处理器连接,用于根据所述其他三个处理器输出的诊断信息确定所述待诊断处理器是否故障,并向所述其他三个处理器输出所述待诊断处理器的诊断结果,所述待诊断处理器为所述主控制电路中的每一所述处理器;

12.当所述诊断结果为所述待诊断处理器为故障处理器时,所述故障处理器向所述第一目标处理器发送所述同步信息。

13.在其中一个实施例中,所述仲裁模块包括四个仲裁电路,每一所述待诊断处理器配置有一所述仲裁电路,每一所述仲裁电路分别与所述其他三个处理器连接,所述其他三个处理器为除所述仲裁电路配置的待诊断处理器以外的处理器;所述仲裁电路包括:三个仲裁单元,各所述仲裁单元的两个输入端分别与所述其他三个处理器中的两个处理器对应连接,各所述仲裁单元的输出端分别与所述其他三个处理器连接,且每两个所述仲裁单元的一个输入端连接同一处理器,各所述仲裁单元分别包括:与非门和反相器,其中,

14.所述与非门的两个输入端分别与所述其他三个处理器中的两个处理器对应连接,所述与非门的输出端与所述反相器的输入端连接;

15.所述反相器的输出端分别与所述其他三个处理器连接。

16.在其中一个实施例中,所述调速器还包括第一隔离电路,所述主控制电路中两个处理器分别经所述第一隔离电路对应与所述从控制电路的两个处理器连接;所述第一隔离电路包括:

17.第一隔离单元,分别与所述主控制电路的第一处理器、所述从控制电路的第一处理器连接;

18.第二隔离单元,分别与所述主控制电路的第一处理器、所述从控制电路的第二处理器连接;

19.第三隔离单元,分别与所述主控制电路的第二处理器、所述从控制电路的第一处理器连接;

20.第四隔离单元,分别与所述主控制电路的第二处理器、所述从控制电路的第二处理器连接;其中,所述主控制电路的第一处理器与所述从控制电路的第一处理器的类型相同;

21.当所述诊断结果为所述待诊断处理器为故障处理器时,所述其他三个处理器分别根据所述诊断结果控制与所述故障处理器连接的隔离单元,以分别断开与所述故障处理器连接的数据传输通路。

22.在其中一个实施例中,所述调速器还包括:

23.第一输入采集电路,分别与所述主控制电路、所述从控制电路连接,用于采集并处理接收的模拟量输入信号,并将处理后的所述模拟量输入信号传输至目标控制电路;

24.第一输出处理电路,分别与所述主控制电路、所述从控制电路连接,用于接收并处理来自所述目标控制电路的模拟量输出信号;

25.第二输入采集电路,分别与所述主控制电路、所述从控制电路连接,用于采集并处理接收的开关量输入信号,并将处理后的所述开关量输入信号传输至所述目标控制电路;

26.第二输出处理电路,分别与所述主控制电路、所述从控制电路连接,用于接收并处理来自所述目标控制电路的开关量输出信号;其中,所述目标控制电路为两个所述控制电路中的一个。

27.在其中一个实施例中,所述调速器还包括:

28.第二隔离电路,分别与所述第一输入采集电路、所述第一输出处理电路、所述第二输入采集电路、所述第二输出处理电路、所述主控制电路的第二处理器连接;

29.第三隔离电路,分别与所述第一输入采集电路、所述第一输出处理电路、所述第二输入采集电路、所述第二输出处理电路、所述从控制电路的第二处理器连接;其中,所述主

控制电路的第二处理器与所述从控制电路的第二处理器的类型相同;

30.当所述主控制电路中的处理器无故障时,所述主控制电路控制所述第三隔离电路处于闭锁状态;

31.当所述主控制电路中的所述第二处理器故障时,所述主控制电路控制所述第二隔离电路处于闭锁状态。

32.在其中一个实施例中,所述第二输入采集电路包括第一光电隔离器,用于对采集的所述开关量输入信号进行隔离处理;所述第二输出处理电路包括第二光电隔离器,用于对接收的所述开关量输出信号进行隔离处理;所述第二隔离电路包括:

33.第一磁隔离器,分别与所述第一输入采集电路、所述主控制电路的第二处理器连接;

34.第二磁隔离器,分别与所述第一输出处理电路、所述主控制电路的第二处理器连接;

35.第三磁隔离器,分别与所述第一光电隔离器、所述第二光电隔离器、所述主控制电路的第二处理器连接;

36.所述第三隔离电路包括:

37.第四磁隔离器,分别与所述第一输入采集电路、所述从控制电路的第二处理器连接;

38.第五磁隔离器,分别与所述第一输出处理电路、所述从控制电路的第二处理器连接;

39.第六磁隔离器,分别与所述第一光电隔离器、所述第二光电隔离器、所述从控制电路的第二处理器连接。

40.在其中一个实施例中,所述调速器还包括:

41.电源模块,分别与所述第一输入采集电路、所述第一输出处理电路、所述第二输入采集电路、所述第二输出处理电路、各所述控制电路连接,用于提供供电电压;

42.其中,所述电源模块包括:

43.逆变单元,用于接收外部电源电压,并对所述电源电压进行压降处理,得到压降电压;

44.第一系统电源单元,与所述逆变单元连接,用于对所述压降电压进行整流、调压、滤波处理得到第一供电电压,并输出至所述主控制电路;

45.第二系统电源单元,与所述逆变单元连接,用于对所述压降电压进行整流、调压、滤波处理得到第二供电电压,并输出至所述从控制电路;

46.接口电源单元,与所述逆变单元连接,用于对所述压降电压进行整流、调压、滤波处理得到第三供电电压,并输出至所述第一输入采集电路、所述第一输出处理电路、所述第二输入采集电路、所述第二输出处理电路。

47.在其中一个实施例中,当主控制电路中的一个处理器故障时,所述主控制电路中的故障处理器向从控制电路中的第一目标处理器发送同步信息,以使所述第一目标处理器经所述从控制电路中的另一处理器与所述主控制电路中的第二目标处理器连接构成目标数据传输通路,实现数据传输。

48.在其中一个实施例中,所述调速器还包括:

49.校验模块,分别与四个所述处理器连接,用于判断待诊断处理器是否故障,并向其他三个处理器输出所述待诊断处理器的诊断结果,所述待诊断处理器为所述主控制电路中的每一所述处理器;

50.当所述诊断结果为所述待诊断处理器为故障处理器时,所述故障处理器向所述第一目标处理器发送所述同步信息。

51.本技术的另一方面提供了一种调速器的控制方法,应用于如上述实施例中任一项所述的调速器,所述方法包括:

52.根据待启动信号获取温度值以判断启动状态;

53.若热启动状态,则控制汽轮机的转速按照第一预设速率增加,直至所述汽轮机的实时转速大于等于第一预设转速;

54.若冷启动状态,则控制所述汽轮机的转速按照第二预设速率增加,直至所述汽轮机的实时转速大于等于第二预设转速后进入暖机状态,预设时间后控制所述汽轮机的转速继续按照第二预设速率增加,直至所述汽轮机的实时转速大于等于第三预设转速后,控制所述汽轮机的转速按照第一预设速率增加,直至所述汽轮机的实时转速大于等于第一预设转速;

55.根据启动完成信号按照设定转速对所述汽轮机进行转速调节。

56.上述实施例的调速器和调速器的控制方法,主控制电路中的两个不同类型的处理器实现数据传输,通过从控制电路的设置,当主控制电路中的处理器故障时,采用从控制电路中与故障处理器类型相同的处理器进行替代,继续处理故障处理器将要处理的数据,与主控制电路中无故障的处理器实现数据传输,若主控制电路中的处理器均故障,则通过从控制电路的两个处理器进行数据处理与传输。通过将通过双控制电路的设计避免单点故障导致系统故障的情况发生。

附图说明

57.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

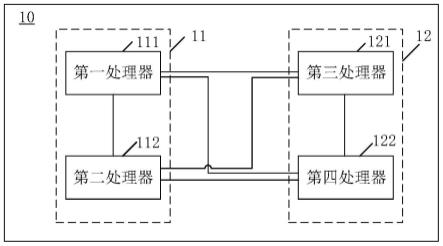

58.图1为本技术第一实施例中提供的调速器的结构框图;

59.图2为本技术第二实施例中提供的调速器的结构框图;

60.图3为本技术一实施例中提供的第一仲裁电路的结构示意图;

61.图4为本技术第三实施例中提供的调速器的结构框图;

62.图5为本技术第四实施例中提供的调速器的结构框图;

63.图6为本技术一实施例中提供的第一输入采集电路的原理图;

64.图7为本技术一实施例中提供的第一输出处理电路的原理图;

65.图8为本技术一实施例中提供的第二输入采集电路的原理图;

66.图9为本技术一实施例中提供的第二输出处理电路的原理图;

67.图10为本技术第五实施例中提供的调速器的结构框图;

68.图11为本技术一实施例中提供的电源模块的结构框图;

69.图12为本技术第六实施例中提供的调速器的结构框图

70.图13为本技术一实施例中提供的调速器的控制方法的流程示意图。

71.附图标记说明:

72.10、调速器;11、主控制电路;111、第一处理器;112、第二处理器;12、从控制电路;121、第三处理器;122、第四处理器;13、仲裁模块;131、仲裁电路;1311、第一仲裁单元;1312、第二仲裁单元;1313、第三仲裁单元;132、与非门;133、反相器;14、第一隔离电路;141、第一隔离单元;142、第二隔离单元;143、第三隔离单元;144、第四隔离单元;15、第一输入采集电路;151、模数转换器;152、第一场效应管;153、分压电路;154、第一运算放大器;155、电压跟随器;16、第一输出处理电路;161、数模转换器;162、第二运算放大器;163、第三运算放大器;164、第四运算放大器;165、第五运算放大器;166、第二场效应管;167、第三场效应管;17、第二输入采集电路;171、第一光电隔离器;18、第二输出处理电路;181、第二光电隔离器;19、第二隔离电路;191、第一磁隔离器;192、第二磁隔离器;193、第三磁隔离器;20、第三隔离电路;201、第四磁隔离器;202、第五磁隔离器;203、第六磁隔离器;21、电源模块;211、逆变单元;212、第一系统电源单元;213、第二系统电源单元;214、接口电源单元。

具体实施方式

73.为了便于理解本技术,下面将参照相关附图对本技术进行更全面的描述。附图中给出了本技术的实施例。但是,本技术可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使本技术的公开内容更加透彻全面。

74.除非另有定义,本文所使用的所有的技术和科学术语与属于本技术的技术领域的技术人员通常理解的含义相同。本文中在本技术的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本技术。

75.可以理解,本技术所使用的术语“第一”、“第二”等可在本文中用于描述各种元件,但这些元件不受这些术语限制。这些术语仅用于将第一个元件与另一个元件区分。

76.需要说明的是,当一个元件被认为是“连接”另一个元件时,它可以是直接连接到另一个元件,或者通过居中元件连接另一个元件。此外,以下实施例中的“连接”,如果被连接的对象之间具有电信号或数据的传递,则应理解为“电连接”、“通信连接”等。

77.如图1,在一个实施例中提供了一种调速器10,所述调速器10包括两个控制电路,每一所述控制电路包括两个处理器,四个所述处理器之间彼此连接,同一所述控制电路中的两个所述处理器的类型不同。

78.主控制电路11中的两个处理器的类型不同,从控制电路12中的两个处理器的类型不同,从控制电路12中的两个处理器分别与主控制电路11中的两个处理器类型对应相同。例如,主控制电路11中的第一处理器与从控制电路12中的第一处理器类型相同,主控制电路11中的第二处理器与从控制电路12中的第二处理器类型相同。处理器至少包括中央处理器(central processing unit,cpu)、现场可编程逻辑门阵列(field programmable gate array,fpga)。

79.示例性的,可以将主控制电路11中的两个处理器分别作为调速器10的第一处理器111和第二处理器112,可以将从控制电路12中的两个处理器分别作为调速器10的第三处理器121、第四处理器122。第一处理器111可以为第一cpu,第二处理器112可以为第一fpga;第

三处理器121可以为第二cpu,第四处理器122可以为第二fpga。第一cpu分别与第一fpga、第二cpu和第二fpga连接;第一fpga分别与第二cpu和第二fpga连接;第二cpu与第二fpga连接。

80.系统开始运作时,主控制电路11包括目标数据传输通路,即第一cpu与第一fpga连接构成目标数据传输通路,实现数据传输。也可以从控制电路12包括目标数据传输通路,即第二cpu与第二fpga连接构成目标数据传输通路,实现数据传输。

81.可选的,当主控制电路11中的一个处理器故障时,所述主控制电路11中的故障处理器向从控制电路12中的第一目标处理器发送同步信息,以使所述第一目标处理器经所述从控制电路12中的另一处理器与所述主控制电路11中的第二目标处理器连接构成目标数据传输通路,实现数据传输。

82.以主控制电路11为目标数据传输通路作为示例进行说明,当主控制电路11中的处理器故障时,所述主控制电路11中的故障处理器向从控制电路12中的第一目标处理器发送同步信息,以使所述第一目标处理器与第二目标处理器连接构成目标数据传输通路,实现数据传输。

83.其中,所述第一目标处理器为所述从控制电路12中与所述故障处理器的类型相同的处理器,所述第二目标处理器与所述第一目标处理器的类型不同。同步信息为可以表征故障处理器故障前处理或传输数据的信息。四个所述处理器中,由于相同类型的两个之间仅需传递同步信息,故采用串行通信方式进行通信;由于不同类型的两个处理器之间需要实现数据的传输且传输的数据量较大,为了保证数据的传输效率,故采用并行通信方式进行通信。

84.可选的,当主控制电路11中的一个处理器故障时,所述第二目标处理器为所述主控制电路11中的正常处理器。例如,当第一cpu故障时,第一目标处理器为第二cpu,第二目标处理器为第一fpga,第一cpu向从控制电路12中的第二cpu发送同步信息,以使第二cpu与第一fpga连接构成目标数据传输通路,实现数据传输;当第一fpga故障时,第一目标处理器为第二fpga,第二目标处理器为第一cpu,第一fpga向从控制电路12中的第二fpga发送同步信息,以使第一cpu与第二fpga连接构成目标数据传输通路,实现数据传输。

85.可选的,当主控制电路11中的两个处理器均故障时,所述第二目标处理器为所述从控制电路12中的处理器。例如,当第一cpu和第一fpga均故障时,第一cpu向第二cpu发送同步信息,第一fpga向第二fpga发送同步信息,以使第二cpu与第二fpga连接构成目标数据传输通路,实现数据传输。

86.上述调速器10,主控制电路11中的两个不同类型的处理器通过并口通信实现数据传输,通过从控制电路12的设置,当主控制电路11中的处理器故障时,故障处理器通过串行通信将同步信息传输至从控制电路12中与故障处理器类型相同的处理器,用从控制电路12中与故障处理器类型相同的处理器进行替代,继续处理故障处理器将要处理的数据,与主控制电路11中无故障的处理器实现数据传输,若主控制电路11中的处理器均故障,则通过从控制电路12的两个处理器进行数据处理与传输。通过双控制电路的设计避免单点故障导致系统故障的情况发生。

87.如图2,在一个实施例中,所述调速器10还包括仲裁模块13,分别与四个处理器连接。冲裁模块包括四个仲裁电路,每一所述待诊断处理器配置有一所述仲裁电路,每一所述

仲裁电路分别与所述其他三个处理器连接,所述其他三个处理器为除所述仲裁电路配置的待诊断处理器以外的处理器。仲裁电路包括三个仲裁单元,各所述仲裁单元的两个输入端分别与所述其他三个处理器中的两个处理器对应连接,各所述仲裁单元的输出端分别与所述其他三个处理器连接,且每两个所述仲裁单元的一个输入端连接同一处理器,各所述仲裁单元分别包括与非门132和反相器133。

88.以第一处理器111作为待诊断处理器进行说明,所述主控制电路11中的第一处理器111分别向第二处理器112、第三处理器121以及第四处理器122发送检验信息,第二处理器112、第三处理器121以及第四处理器122根据检验信息生成诊断信息。第一处理器111配置的仲裁电路131如图3所示,若其他三个处理器对第一处理器111的诊断结果为故障则输出高电平,第一仲裁单元1311中的与非门132分别与第二处理器112、第四处理器122连接,第二仲裁单元1312中的与非门132分别与第二处理器112、第三处理器121连接,第三仲裁单元1313中的与非门132分别与第三处理器121、第四处理器122连接,三个仲裁电路131采用三取二的方式判断第一处理器111是否故障。例如,若第二处理器112、第三处理器121以及第四处理器122均判断正常,输出低电平,则第一仲裁电路131、第二仲裁电路131以及第三仲裁电路131中,与非门132输出高电平,反相器133输出低电平,最后第一仲裁电路131输出低电平,第一处理器111没有故障;若第二处理器112以及第三处理器121判断正常、输出低电平,第四处理器122判断故障、输出高电平,则第一仲裁电路131、第二仲裁电路131以及第三仲裁电路131中,与非门132输出高电平,反相器133输出低电平,最后第一仲裁电路131输出低电平,第一处理器111没有故障;若第二处理器112以及第三处理器121判断故障、输出高电平,第四处理器122判断正常、输出低电平,则第一仲裁电路131和第三仲裁电路131中与非门132输出高电平,反相器133输出低电平,但是第二仲裁电路131中与非门132输出低电平、反相器133输出高电平,最后第一仲裁电路131输出高电平,第一处理器111故障。即除了待诊断处理器之外的其他三个处理器中,若有其中两个判断待诊断处理器故障,则待诊断处理器故障。

89.故障检测后,仲裁模块13向第二处理器112、第三处理器121以及第四处理器122输出第一处理器111的诊断结果。若诊断结果为第一处理器111故障,则第三处理器121为第一目标处理器,第二处理器112为第二目标处理器,第一处理器111向第三处理器121发送同步信息,第三处理器121根据同步信息与第二处理器112连接构成目标数据传输通路,实现数据传输。

90.当主控制电路11包括目标数据传输通路时,第一处理器111和第二处理器112均可作为待诊断处理器;当从控制电路12包括目标数据传输通路时,第三处理器121和第四处理器122均可作为待诊断处理器。

91.可选的,调速器10还包括校验模块,用于判断待诊断处理器是否故障,并向其他三个处理器输出所述待诊断处理器的诊断结果,所述待诊断处理器为所述主控制电路11中的每一所述处理器;当所述诊断结果为所述待诊断处理器为故障处理器时,所述故障处理器向所述第一目标处理器发送所述同步信息。

92.上述调速器10,待诊断处理器向其他三个处理器发送校验信息,其他三个处理器根据校验信息判断待诊断处理器是否故障,并将诊断信息传输至仲裁模块13根据三取二的方法生成诊断结果,三取二可以避免其他三个处理器中原本存在故障的处理器混淆待诊断

处理器的诊断结果。若待诊断处理器故障,则向从控制电路12中的同类型处理器发送同步信息,以使第一目标处理器与第二目标处理器构成新的目标数据传输通路,从而避免由于待诊断处理器单点故障而导致系统无法运行的情况发生。

93.如图4,在一个实施例中,所述调速器10还包括第一隔离电路14,所述主控制电路11中两个处理器分别经所述第一隔离电路14对应与所述从控制电路12的两个处理器连接。所述第一隔离电路14包括第一隔离单元141、第二隔离单元142、第三隔离单元143和第四隔离单元144。第一隔离单元141,分别与所述主控制电路11的第一处理器、所述从控制电路12的第一处理器连接;第二隔离单元142,分别与所述主控制电路11的第一处理器、所述从控制电路12的第二处理器连接;第三隔离单元143,分别与所述主控制电路11的第二处理器、所述从控制电路12的第一处理器连接;第四隔离单元144,分别与所述主控制电路11的第二处理器、所述从控制电路12的第二处理器连接;其中,所述主控制电路11的第一处理器与所述从控制电路12的第一处理器的类型相同。第一隔离单元141、第二隔离单元142、第三隔离单元143以及第四隔离单元144分别包括至少一磁隔离器。

94.示例性的,第一处理器111经第一隔离单元141与第三处理器121连接,第一处理器111经第二隔离单元142与第四处理器122连接,第二处理器112经第三隔离单元143与第三处理器121连接,第二处理器112经第四隔离单元144与第四处理器122连接。例如,当第一处理器111为待诊断处理器时,若诊断结果为第一处理器111故障,则第三处理器121接收到同步信息后根据诊断结果控制第一隔离单元141断开,第四处理器122根据诊断结果控制第二隔离单元142断开;当第二处理器112为待诊断处理器时,若诊断结果为第二处理器112故障,则第四处理器122接收到同步信息后根据诊断结果控制第四隔离单元144断开,第三处理器121根据诊断结果控制第三隔离单元143断开。

95.可选的,第一处理器111与第四处理器122之间的连接通路、第二处理器112与第三处理器121之间的连接通路可以包括同一个磁隔离器;第一处理器111与第四处理器122之间的连接通路中的磁隔离器、第二处理器112与第三处理器121之间的连接通路中的磁隔离器可以不同,在此不作限制。

96.上述调速器10,通过切断其他三个处理器与故障的待诊断处理器间连接的隔离单元的输出,从而避免故障处理器输出的错误信息使系统发生混乱。

97.如图5,在一个实施例中,调速器10还包括第一输入采集电路15、第一输出处理电路16、第二输入采集电路17、第二输出处理电路18、第二隔离电路19和第三隔离电路20。

98.第一输入采集电路15经第二隔离电路19中的第一磁隔离器191与主控制单元连接,经第三隔离电路20中的第四磁隔离器201与从控制单元连接,用于采集并处理接收的模拟量输入信号,并将处理后的所述模拟量输入信号传输至目标控制电路。第一输入采集电路15的电路原理图如图6所示,第一输入采集电路15包括模数转换器151,模拟输入信号包括电流信号。从印制电路板输入的电流信号通过第一场效应管152后,经过分压电路153形成电压信号,电压信号经第一运算放大器154调理后,通过电压跟随器155提升电压信号鲁棒性和负载能力,便于后续采样,最后进入模数转换器151进行模数转换生成数字信号,数字信号通过模数转换器151的spi接口传输至目标控制电路。

99.示例性的,当主控制电路11为目标数据传输通路时,若第一处理器111和第二处理器112无故障,则第一磁隔离器191不闭锁、第四磁隔离器201处于闭锁状态,第一输入采集

电路15输出的数字信号经过spi总线传输至第二处理器112进行处理;若仅第一处理器111故障,第三处理器121作为第一目标处理器、第二处理器112作为第二目标处理器,则第一磁隔离器191不闭锁、第四磁隔离器201处于闭锁状态,第一输入采集电路15输出的数字信号经过spi总线传输至第二处理器112进行处理;若仅第二处理器112故障,第四处理器122作为第一目标处理器,第一处理器111作为第二目标处理器,则第四磁隔离器201不闭锁、第一磁隔离器191闭锁,第一输入采集电路15输出的数字信号经过spi总线传输至第四处理器122进行处理;若第一处理器111和第二处理器112均故障,则第四磁隔离器201不闭锁、第一磁隔离器191闭锁,第一输入采集电路15输出的数字信号经过spi总线传输至第四处理器122进行处理。

100.第一输出处理电路16经第二隔离电路19中的第二磁隔离器192与主控制单元连接,经第三隔离电路20中的第五磁隔离器202与从控制单元连接,用于接收并处理来自所述目标控制电路的模拟量输出信号。第一输出处理电路16的电路原理图如图7所示,第一输出电路包括数模转换器161。目标控制电路的第二处理器112生成的数模转换指令经spi总线下发至数模转换器161,形成数模转换的初始信号,初始信号经过第二运算放大器162处理后生成供电流和电压输出的公共电压,一部分公共电压经第四运算放大器164、第五运算放大器165、第二场效应管166和第三场效应管167处理后生成标准电流信号,另一部分公共电压经第三运算放大器163处理后生成标准电压信号,标准电流信号和标准电压信号作为第一输出处理电路16输出的模拟量输出信号从印制电路板的接线端子输出。

101.示例性的,当主控制电路11为目标数据传输通路时,若第一处理器111和第二处理器112无故障,则第二磁隔离器192不闭锁、第五磁隔离器202处于闭锁状态,第二处理器112输出的数模转换指令经spi总线输入至第一输出处理电路16;若仅第一处理器111故障,第三处理器121作为第一目标处理器、第二处理器112作为第二目标处理器,则第二磁隔离器192不闭锁、第五磁隔离器202处于闭锁状态,第二处理器112输出的数模转换指令经spi总线输入至第一输出处理电路16;若仅第二处理器112故障,第四处理器122作为第一目标处理器,第一处理器111作为第二目标处理器,则第五磁隔离器202不闭锁、第二磁隔离器192闭锁,第四处理器122输出的数模转换指令经spi总线输入至第一输出处理电路16;若第一处理器111和第二处理器112均故障,则第五磁隔离器202不闭锁、第二磁隔离器192闭锁,第四处理器122输出的数模转换指令经spi总线输入至第一输出处理电路16。

102.第二输入采集电路17经第二隔离电路19中的第三磁隔离器193与主控制单元连接,经第三隔离电路20中的第六磁隔离器203与从控制电路12连接,用于采集并处理接收的开关量输入信号,并将处理后的所述开关量输入信号传输至所述目标控制电路。第二输入采集电路17的电路原理图如图8所示,第二输入采集电路17包括第一光电隔离器171。

103.第二输出处理电路18经第二隔离电路19中的第三磁隔离器193与主控制单元连接,经第三隔离电路20中的第六磁隔离器203与从控制电路12连接,用于接收并处理来自所述目标控制电路的开关量输出信号;其中,所述目标控制电路为两个所述控制电路中的一个。第二输出处理电路18的电路原理图如图9所示,第二输入采集电路17包括第二光电隔离器181。

104.上述调速器10,当第一处理器111与第二处理器112作为目标数据传输通路时,第一处理器111输出低电平从而控制第三隔离单元143闭锁,使能第三隔离单元143中的磁隔

离器不能输出,从而使第一输入采集电路15、第一输出处理电路16与第二处理器112进行信息交互;当第一处理器111与第四处理器122作为目标数据传输通路时,第一处理器111输出低电平从而控制第二隔离单元142的闭锁,使能第二隔离单元142中的磁隔离器不能输出,从而使第一输入采集电路15、第一输出处理电路16与第四处理器122进行信息交互。通过控制第二隔离单元142和第三隔离单元143从而避免spi总线权限冲突。

105.如图10和图11,在一个实施例中,调速器10还包括电源模块21,电源模块21包括逆变单元211、第一系统电源单元212、第二系统电源单元213和接口电源单元214。电源模块21的原理图如图11所示,逆变单元211,用于接收外部电源电压,并对所述电源电压进行压降处理,得到压降电压;第一系统电源单元212,与所述逆变单元211连接,用于对所述压降电压进行整流、调压、滤波处理得到第一供电电压,并输出至所述主控制电路11;第二系统电源单元213,与所述逆变单元211连接,用于对所述压降电压进行整流、调压、滤波处理得到第二供电电压,并输出至所述从控制电路12;接口电源单元214,与所述逆变单元211连接,用于对所述压降电压进行整流、调压、滤波处理得到第三供电电压,并输出至所述第一输入采集电路15、所述第一输出处理电路16、所述第二输入采集电路17、所述第二输出处理电路18。

106.上述调速器10,通过设置第一系统电源对主控制电路11进行供电,第二系统电源对从控制电路12进行供电,接口电源单元214对第一输入采集电路15、所述第一输出处理电路16、所述第二输入采集电路17、所述第二输出处理电路18进行供电,实现系统工作电源和接口电源的冗余,当其中一个系统电源发生故障时,另一系统电源给未发生故障的控制电路进行供电,使未故障的控制电路作为目标传输通路实现数据传输。

107.如图12,在一个实施例中,调速器10还包括人机界面(human machine interface,hmi),主控制电路11包括第一cpu和第一fpga,从控制电路12包括第二cpu和第二fpga。第一输入采集电路15包括模数转换器151(analog to digital converter,adc),第一输出处理电路16包括数模转换器161(digital-to-analog conversion,dac)。第二输入采集电路17包括第一光电隔离器171用于初级隔离,第二输出处理电路18包括第二光电隔离器181用于初级隔离。第一系统电源单元212为第一cpu和第一fpga供电,第二系统电源单元213为第二cpu和第二fpga供电,接口电源单元214为第一输入采集电路15、第一输出处理电路16、第二输入采集电路17和第二输出处理电路18供电。由于第一cpu与第二cpu、第二fpga之间采用不同的系统电源,故第一cpu通过磁隔离器与第二cpu、第一fpga连接;由于第一fpga与第二cpu、第二fpga采用不同的系统电源,故第一fpga通过磁隔离器与第二cpu、第二fpga连接;由于第一cpu与第一fpga,第二cpu与第二fpga采用相同的系统电源,故第一cpu与第一fpga直接连接,第二cpu与第二fpga直接连接。

108.系统上电,以选取主控制电路11作为目标控制电路为例进行说明,第一cpu向第二cpu、第一fpga、第二fpga发送校验信息,通过仲裁电路通过其他三个生成的诊断信息进行三取二来诊断第一cpu是否故障;第一fpga向第一cpu、第二cpu、第二fpga发送校验信息,通过仲裁电路通过其他三个生成的诊断信息进行三取二来诊断第一fpga是否故障。

109.若第一cpu故障,则第一cpu通过串行通信向第二cpu发送同步信息,以使第二cpu通过并口通信与第一fpga进行目标数据传输;若第一fpga故障,则第一fpga通过串行通信向第二fpga发送同步信息,以使第二fpga通过并口通信与第一cpu进行目标数据传输;若第

一cpu与第一fpga均未故障,则第一cpu输出低电平以控制第三隔离电路20闭锁,从而避免总线操纵权限冲突,第一cpu与第一fpga之间传输目标数据;若第一cpu与第一fpga均故障,则第一cpu通过串行通信向第二cpu发送同步信息,第一fpga通过串行通信向第二fpga发送同步信息,以使第二cpu通过并口通信与第二fpga进行目标数据传输。

110.上述调速器10,主控制电路11中的两个不同类型的处理器实现数据传输,通过从控制电路12的设置,当主控制电路11中的处理器故障时,采用从控制电路12中与故障处理器类型相同的处理器进行替代,继续处理故障处理器将要处理的数据,与主控制电路11中无故障的处理器实现数据传输,若主控制电路11中的处理器均故障,则通过从控制电路12的两个处理器进行数据处理与传输。通过双控制电路的设计避免单点故障导致系统故障的情况发生。

111.如图13,在一个实施例中,提供了一种调速器的控制方法,应用于如上述任一实施例中的调速器,方法包括:

112.步骤s100:根据待启动信号获取温度值以判断启动状态。

113.其中,待启动信号为指示调速器开始工作的信号,温度值为外部环境温度值,启动状态包括热启动状态和冷启动状态。当温度值大于等于预设温度值时,为热启动状态;当温度值小于预设温度值时,为冷启动状态。

114.当调速器上电后,首先进行自检,并判断当前状态是否满足状态要求,若满足,则根据待启动信号获取温度值,以判断调速器的启动状态。

115.步骤s210:若热启动状态,则控制汽轮机的转速按照第一预设速率增加,直至所述汽轮机的实时转速大于等于第一预设转速。

116.其中,第一预设速率可以为500rpm/min,第一预设转速可以为4440rpm。

117.当判断为热启动状态后,调速器输出开度信号以控制汽轮机的调节阀的开度从而控制汽轮机的转速,控制汽轮机的转速以每分钟500rpm增加,直至汽轮机转速达到4440rpm,启动完成。

118.步骤s220:若冷启动状态,则控制所述汽轮机的转速按照第二预设速率增加,直至所述汽轮机的实时转速大于等于第二预设转速后进入暖机状态,预设时间后控制所述汽轮机的转速继续按照第三预设速率增加,直至所述汽轮机的实时转速大于等于第三预设转速后,控制所述汽轮机的转速按照第一预设速率增加,直至所述汽轮机的实时转速大于等于第一预设转速。

119.其中,第二预设速率可以为125rpm/min,第二预设转速可以为700rpm,第三预设转速可以为3100rpm,预设时间可以为10min。

120.当判断为冷启动状态后,调速器输出开度信号以控制汽轮机的调节阀的开度从而控制汽轮机的转速,控制汽轮机的转速以每分钟125rpm增加,直至汽轮机转速达到700rpm后,调速器进入暖机状态,10分钟后,调速器继续控制汽轮机的转速以每分钟125rpm增加,直至汽轮机转速达到300rpm后,调速器控制汽轮机的转速以每分钟500rpm增加,直至汽轮机转速达到4440rpm,启动完成。

121.步骤s300:根据启动完成信号按照设定转速对所述汽轮机进行转速调节。

122.其中,设定转速为人为设定的转速。

123.上述调速器的控制方法,主控制电路中的两个不同类型的处理器实现数据传输,

通过从控制电路的设置,当主控制电路中的处理器故障时,采用从控制电路中与故障处理器类型相同的处理器进行替代,继续处理故障处理器将要处理的数据,与主控制电路中无故障的处理器实现数据传输,若主控制电路中的处理器均故障,则通过从控制电路的两个处理器进行数据处理与传输。通过双控制电路的设计避免单点故障导致系统故障的情况发生。使调速器可以正常的输入输出信号以控制汽轮机的调速,并按照温度改变调速方法,以更好的控制汽轮机的转速调节。

124.应该理解的是,虽然流程图中的各个步骤按照箭头的指示依次显示,但是这些步骤并不是必然按照箭头指示的顺序依次执行。除非本文中有明确的说明,这些步骤的执行并没有严格的顺序限制,这些步骤可以以其它的顺序执行。而且,流程图的至少一部分步骤可以包括多个步骤或者多个阶段,这些步骤或者阶段并不必然是在同一时刻执行完成,而是可以在不同的时刻执行,这些步骤或者阶段的执行顺序也不必然是依次进行,而是可以与其它步骤或者其它步骤中的步骤或者阶段的至少一部分轮流或者交替地执行。

125.在本说明书的描述中,参考术语“有些实施例”、“其他实施例”、“理想实施例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特征包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性描述不一定指的是相同的实施例或示例。

126.以上实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

127.以上所述实施例仅表达了本技术的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本技术构思的前提下,还可以做出若干变形和改进,这些都属于本技术的保护范围。因此,本技术专利的保护范围应以所附权利要求为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。