1.本文中描述的实施例涉及存储器装置,包含存储器装置的写入操作及写入操作的写入验证阶段。

背景技术:

2.存储器装置广泛用于计算机及许多其它电子物品中。存储器装置通常具有用于存储信息(例如数据)的众多存储器胞元。信息可在写入操作(例如编程操作)中存储于存储器胞元中。存储于存储器胞元中的信息值通常由存储器胞元的阈值电压电平定义。常规写入操作的部分包含写入验证操作(例如编程验证操作),其经执行以验证目标存储器胞元(经选择以存储信息的存储器胞元)是否达到其相应目标阈值电压电平。一些常规写入验证操作可在写入验证操作中并发地验证多个目标阈值电压电平。一些常规验证操作的部分包含使耦合到目标存储器胞元的数据线预充电。然而,常规验证操作中的此预充电可在数据线之间添加额外耦合电容。额外耦合电容将使数据线上的电荷需要更长时间来减少。因此,常规存储器装置的性能会受损。

技术实现要素:

3.本公开的一方面涉及一种设备,其包括:第一数据线;第一存储器胞元串,其耦合到所述第一数据线,所述第一存储器胞元串包含第一存储器胞元;第二数据线;第二存储器胞元串,其耦合到所述第二数据线,所述第二存储器胞元串包含第二存储器胞元;存取线,其由所述第一及第二存储器胞元共享;及控制单元,其包含用于执行操作的电路系统,所述操作包含:在对所述第一及第二存储器胞元执行的操作的第一时间间隔期间将所述第一数据线充电到第一电压;在所述第一时间间隔期间使所述第二数据线保持在第二电压,其中所述第二电压小于所述第一电压;在所述操作的第二时间间隔期间将所述第一数据线充电到第三电压,其中所述第三电压大于所述第一电压;在所述第二时间间隔期间将所述第二数据线充电到第四电压,其中所述第四电压小于所述第三电压且大于所述第二电压;在所述操作的所述第二时间间隔期间确定所述第一存储器胞元是否达到第一阈值电压;及在所述第二时间间隔期间确定所述第二存储器胞元是否达到第二阈值电压。

4.本公开的另一方面涉及一种设备,其包括:数据线;存储器胞元串,其在第一节点处耦合到所述数据线,所述存储器胞元串包含定位于所述设备的不同层阶上的存储器胞元;第一电路路径,其耦合于所述第一节点与第一供应节点之间;第二电路路径,其耦合于所述第一节点与第二节点之间;及第三电路路径,其耦合于所述第二节点与第二供应节点之间。

5.本公开的又一方面涉及一种方法,其包括:在存储器装置的写入验证阶段的第一时间间隔期间将第一数据线充电到第一正电压,所述第一数据线耦合到第一存储器胞元串;在所述第一时间间隔期间使第二数据线保持在接地电势,所述第二数据线耦合到第二存储器胞元串;在所述写入验证阶段的第二时间间隔期间将所述第一数据线充电到第二正

电压;在所述第二时间间隔期间将所述第二数据线充电到第三正电压;在所述第二时间间隔期间确定所述第一存储器胞元串的第一存储器胞元是否达到第一阈值电压;及在所述第二时间间隔期间确定所述第二存储器胞元串的第二存储器胞元是否达到第二阈值电压。

附图说明

6.图1展示根据本文中描述的一些实施例的呈包含存储器阵列及存储器胞元的存储器装置的形式的设备的框图。

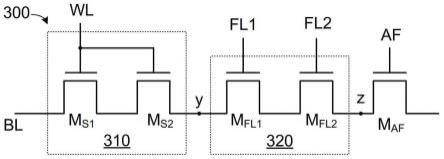

7.图2展示根据本文中描述的一些实施例的包含存储器阵列、数据线及页面缓冲器及感测电路的存储器装置的部分的示意图。

8.图3是展示根据本文中描述的一些实施例的对应于图2的存储器装置的数个存储器胞元的阈值电压范围的不同电平的图。

9.图4展示说明根据本文中描述的一些实施例的包含写入操作的写入阶段及写入验证阶段的图2的存储器装置的实例写入操作的图。

10.图5是展示根据本文中描述的一些实施例的在存储器装置中执行写入操作的方法的流程图。

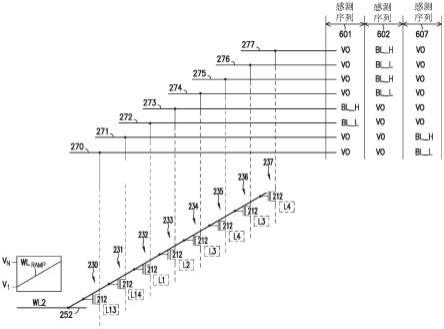

11.图6展示根据本文中描述的一些实施例的包含感测序列的写入验证阶段的实例。

12.图7a展示根据本文中描述的一些实施例的其中图2的存储器装置的存储器胞元串的存储器胞元经选择以存储具有对应于相应电平的值的信息的实例。

13.图7b、图7c及图7d展示根据本文中描述的一些实施例的在写入验证阶段的感测序列期间图7a的存储器装置的数据线上的信号的波形。

14.图8展示根据本文中描述的一些实施例的可为图2的存储器装置的缓冲器及感测放大器电路系统的部分的电路的示意图。

15.图9a及图9b展示根据本文中描述的一些实施例的图8且在图7b的感测序列的初始充电阶段期间与数据线相关联的电路的多个例子。

16.图10a及图10b展示根据本文中描述的一些实施例的图7b的感测序列的后续充电阶段期间的图9a及图9b的电路。

17.图11展示说明根据本文中描述的一些实施例的在图9a、图9b、图10a及图10b的电路的感测序列期间一些信号的波形的更多细节的时序图。

18.图12展示根据本文中描述的一些实施例的呈包含存储器装置的系统的形式的设备。

具体实施方式

19.本文中描述的技术包含具有高效执行包含写入操作的写入验证阶段的写入操作的结构及方法的存储器装置。所描述的存储器装置包含用于在写入验证操作中在数据线上施加电荷及向存储器装置的其它组件施加信号以允许存储器装置在写入操作的相同写入验证阶段中执行双重感测操作的电路及操作。双重感测操作涉及在写入操作的相同写入验证阶段中并发地(例如,同时)验证选定存储器胞元中的两个目标阈值电压电平。如上文提及,一些常规技术在写入验证阶段期间具有预充电技术,其可致使数据线上的电荷需要相对较长时间来减少。在实例中,所描述的技术包含控制数据线上的电荷,使得所描述技术的

写入验证阶段的时间可相对较短。所描述技术的其它实例、改进及益处在下文参考图1到图12论述。

20.图1展示根据本文中描述的一些实施例的呈包含存储器阵列101及存储器胞元102的存储器装置100的形式的设备的框图。在存储器装置100的物理结构中,存储器胞元102可布置成存储器胞元串。相同存储器胞元串内的存储器胞元102可垂直形成(例如,彼此堆叠)于存储器装置100的衬底(例如半导体衬底)之上。如图1中展示,存储器胞元102可组织成存储器块blk0到blki。存储器块blk0到blki中的每一者自身可具有存储器胞元串及相应存储器胞元102。

21.存储器装置100在相应存储器块中可包含存取线(其可包含局部字线)150。存储器装置100可包含数据线(其可包含局部位线)170,其可在存储器块blk0到blki之间共享。存取线150可载送信号(例如字线信号)wl0到wlm。数据线170可载送信号(例如位线信号)bl0到bln。存储器装置100可使用存取线150选择性存取相应存储器块blk0到blki中的存储器胞元102。存储器装置100可使用数据线170选择性与存储器块blk0到blki的存储器胞元102交换信息(例如数据)。

22.存储器装置100可包含可解码来自地址寄存器107的地址信息的行存取电路系统108及列存取电路系统109。基于经解码地址信息,存储器装置100可确定在存储器操作中将存取哪些存储器块blk0到blki的哪些子块的哪些存储器胞元102。

23.存储器装置100可执行写入(例如编程)操作以将信息存储(例如编程)于存储器块blk0到blki中选定存储器块的存储器胞元102中。存储器装置100可执行读取操作以从存储器块blk0到blki的存储器胞元102中的选定存储器块读取(例如感测)信息(例如先前存储信息)。存储器装置100可使用与信号bl0到bln相关联的数据线170提供存储于存储器块blk0到blki中的选定存储器块中的信息或从存储器块blk0到blki中的选定存储器块读取(例如感测)的信息。存储器装置100还可执行擦除操作以从存储器块blk0到blki中的一或多者擦除信息。

24.存储器装置100可接收供应电压,包含供应电压vcc及vss。供应电压vss可在接地电势(例如,具有约0伏特的值)操作。供应电压vcc可包含从例如电池或交流到直流(ac-dc)转换器电路系统的外部电源供应到存储器装置100的外部电压。存储器装置100可包含电压产生器115,其可产生不同电压用于在存储器操作(例如读取、写入及擦除操作)期间使用。

25.如图1中展示,存储器装置100可包含控制单元118,其可经配置以基于线104上的控制信号控制存储器装置100的存储器操作。控制信号的实例包含芯片启用信号ce#、写入启用信号we#及其它信号。线104上的控制信号可指示存储器装置100可执行哪一操作(例如读取、写入或擦除操作)。存储器装置100外部的其它装置(例如存储器控制器或处理器)可控制线104上的控制信号的值。线104上的信号组合的特定值可产生致使存储器装置100执行对应存储器操作(例如读取、写入或擦除操作)的命令(例如读取、写入或擦除命令)。

26.控制单元118可包含电路系统(及软件与固件的任何组合),其可经配置以执行具有额外功能性的存储器装置的共同操作以在存储器装置的写入操作的写入验证阶段期间执行双重感测技术,如本文中描述。控制单元118可经实现为可经配置以执行本文中描述的操作的存储器控制器。控制单元118可包含于下文描述的任何存储器装置(例如存储器装置200)中以执行本文中描述的操作。

27.如图1中展示,存储器装置100可包含感测及缓冲电路系统120,其可包含例如感测放大器及页面缓冲电路(例如数据锁存器)的组件。感测及缓冲电路系统120可响应来自列存取电路系统109的信号bl_sle0到bl_seln。感测及缓冲电路系统120可经配置以确定(例如,通过感测)从存储器块blk0到blki的存储器胞元102读取的信息值(例如,在读取操作期间)且将信息值提供到线(例如全局数据线)175。感测及缓冲电路系统120还可经配置以使用线175上的信号基于在写入操作中线175上的信号值(例如电压值)确定在写入操作中存储(例如编程)于存储器块blk0到blki的存储器胞元102中的信息值。

28.存储器装置100可包含输入/输出(i/o)电路系统117以通过线(例如i/o线)105与外部装置(例如存储器控制器或处理器)交换信息(例如数据、地址及指令信息)。线105上的信号i/o0到i/o

x

可表示从存储器块blk0到blki的存储器胞元102读取或存储于存储器胞元102中的信息。线104及线105可包含存储器装置100内的节点或存储器装置100可驻留于其中的封装上的引脚(或焊料凸块或焊料球)。存储器装置100外部的其它装置(例如存储器控制器或处理器)可通过线104及105与存储器装置100通信。

29.存储器胞元102中的每一者可经编程以存储表示至多一个位(例如单个位)的值或多个位(例如两个、三个、四个或另一数目个位)的值的信息。举例来说,存储器胞元102中的每一者可经编程以存储表示单个位的二进制值“0”或“1”的信息。每胞元单个位有时称为单电平胞元。在另一实例中,存储器胞元102中的每一者可经编程以存储表示多个位的值的信息,例如两个位的四个可能值“00”、“01”、“10”、“11”中的一者、三个位的八个可能值“000”、“001”、“010”、“011”、“100”、“101”、“110”及“111”中的一者或另一数目个多个位(例如每一存储器胞元中的多于三个位)的其它值中的一者。具有存储多个位的能力的胞元有时称为多电平胞元(或多状态胞元)。

30.存储器装置100可包含非易失性存储器装置,且存储器胞元102可包含非易失性存储器胞元,使得存储器胞元102可在电源(例如电压vcc、vss或两者)与存储器装置100断开时留存存储于其上的信息。举例来说,存储器装置100可为快闪存储器装置,例如nand快闪(例如3d nand)或nor快闪存储器装置或另一种类的存储器装置,例如可变电阻存储器装置(例如相变存储器装置或电阻随机存取存储器(ram)装置)。

31.所属领域的一般技术人员可认识到,存储器装置100可包含其它组件,其中若干者未展示于图1中以便不模糊本文中描述的实例实施例。存储器装置100的至少一部分可包含结构且执行操作,类似于或相同于下文参考图2到图10描述的存储器装置中的任何者的结构及操作。

32.图2展示根据本文中描述的一些实施例的包含存储器阵列201、数据线270、271、272及273及页面缓冲器及感测电路220、221、222及223的存储器装置200的部分的示意图。存储器装置200可对应于图1的存储器装置100,使得存储器阵列201可对应于存储器装置100的存储器阵列101。存储器阵列201可包含存储器块290,其可对应于图1的存储器块blk0到blki中的一者。为简单起见,图2展示存储器装置200的一个存储器块(例如存储器块290)。然而,存储器装置200可包含众多存储器块。在图2中,方向x、y及z可为相对于存储器装置200的结构的物理方向(例如三维(3d)尺寸)。举例来说,z方向可为垂直于存储器装置200的衬底的方向(例如相对于所述衬底的垂直方向)。z方向垂直于x方向及y方向(例如,z方向垂直于存储器装置200的x-y平面)。

33.存储器装置200的数据线270、271、272及273可对应于存储器装置100的数据线170。数据线270、271、272及273可经结构化为导电线以提供存储于存储器装置200中的选定存储器胞元中的信息或从所述选定存储器胞元读取(例如感测)的信息。

34.存储器装置200可包含可载送对应信号(例如字线信号)wl0、wl1、wl2及wl3的控制栅极250、251、252及253。控制栅极250、251、252及253中的每一者可形成存储器装置200的相应存取线的部分。数据线270、271、272及273中的每一者可经结构化为导电线且可形成存储器装置200的相应数据线的部分。作为实例,图2展示四个控制栅极250、251、252及253及四个数据线270、271、272及273。此类控制栅极及线的数目可变化。

35.存储器装置200可包含存储器胞元210、211、212及213、晶体管(例如源极选择晶体管)261及262及晶体管(例如漏极选择晶体管)263及264。存储器胞元210、211、212及213及晶体管261、262、263及264可布置成存储器胞元串,例如存储器胞元串230、231、232及233。为简单起见,仅标记四个存储器胞元串230、231、232及233。图2展示八个存储器胞元串及每一存储器胞元串中的四个存储器胞元210、211、212及213的实例。然而,存储器胞元串的数目及每一存储器胞元串中存储器胞元的数目可变化。

36.如图2中展示,每一存储器胞元串可耦合于源极299与相应数据线(例如数据线270、271、272及273中的一者)之间。举例来说,存储器胞元串232可包含耦合于数据线272与源极299之间的存储器胞元210、211、212及213及相应晶体管262及264。在另一实例中,存储器胞元串233可包含耦合于数据线273与源极299之间的存储器胞元210、211、212及213及相应晶体管262及264。

37.源极299可经结构化为导电线且可形成存储器装置200的源极线(例如导电区)的部分且可载送信号,例如信号sl(例如源极线信号)。在存储器装置200的结构中,存储器胞元210、211、212及213可物理定位于存储器装置200的多个层阶中,使得相同存储器胞元串中的存储器胞元210、211、212及213可彼此堆叠于存储器装置200的多个层阶中。

38.如图2中展示,晶体管261及262可共享相同栅极280。栅极280可形成存储器装置200的选择线(例如源极选择线)的部分。选择线(例如源极选择线)可经结构化为导电线(例如导电区的层阶(例如层))。晶体管261及262可由例如与栅极280相关联的sgs信号(例如源极选择栅极信号)的相同信号控制(例如接通或关断)。在例如读取或写入操作的存储器操作期间,晶体管261及262可经接通(例如,通过激活sgs信号)以将存储器装置200的存储器胞元串耦合到源极299。晶体管261及262可经关断(例如,通过取消激活sgs信号)以使存储器装置200的存储器胞元串与源极299解耦。

39.晶体管263可共享相同栅极(例如漏极选择栅极)285。晶体管264可共享相同栅极(例如漏极选择栅极)286。栅极285及286彼此分离(例如,彼此不电耦合)。栅极285及286中的每一者可形成存储器装置200的相应选择线(例如漏极选择线)的部分。选择线(例如漏极选择线)可经结构化为导电线(例如导电区的层阶(例如层))。

40.晶体管263及264可分别由sgd0及sgd1信号(例如漏极选择栅极信号)控制(例如接通或关断)以在存储器操作(例如读取或写入操作)期间选择性将存储器装置200的存储器胞元串耦合到其相应数据线270、271、272及273。在存储器操作(例如读取或写入操作)期间,一次仅可激活sgd0及sgd1信号中的一者。举例来说,在存储器操作期间,sgd1信号可经激活(以接通晶体管264)以通过相应晶体管264分别将存储器胞元串230、231、232及233耦

合到数据线270、271、272及273。在此实例中,sgd0信号可经取消激活以在存储器胞元串230、231、232及233分别耦合到数据线270、271、272及273时使其它存储器胞元串(图2中未标记)与相应数据线270、271、272及273解耦。在此实例中,信息可存储于存储器胞元串230、231、232及233(选定存储器胞元串)中的每一者中的选定存储器胞元中或从所述选定存储器胞元读取。

41.存储器胞元210、211、212及213中的每一者可经配置(例如,经结构化)以存储多个信息位。在写入操作中,存储器装置200可致使选定存储器胞元具有特定电平(例如阈值电压电平(还称为状态))以反映存储于选定存储器胞元中的信息值(例如二进制值)。在读取操作中,从选定存储器胞元读取的信息值(例如二进制值)可基于选定存储器胞元的阈值电压电平(例如状态)。在本描述中,“阈值电压”、“电平”及“状态”可互换使用。“目标阈值电压”、“目标电平”及“目标状态”也可互换使用。

42.在写入操作期间,页面缓冲器及感测电路220、221、222及223可操作以提供存储于分别选择的存储器胞元串230、231、232及233的选定存储器胞元中的信息。在读取操作期间,页面缓冲器及感测电路220、221、222及223可操作以提供从分别选择的存储器胞元串230、231、232及233的选定存储器胞元读取的信息。在写入操作的部分期间(例如,在写入验证阶段期间),页面缓冲器及感测电路220、221、222及223还可操作以允许存储器装置200确定选定存储器胞元(在存储器胞元210、211、212及213中)是否达到其相应目标电平(例如相应目标阈值电压)。目标电平是对应于希望在写入操作的另一部分期间(例如,在写入验证阶段之前执行的写入阶段期间)存储于选定存储器胞元中的信息值(例如目标值)的电平(例如阈值电压)。

43.图3是展示根据本文中描述的一些实施例的用于图2的存储器装置200的数个存储器胞元的不同电平(例如状态)l0到l15及对应阈值电压范围(例如阈值电压分布)300到315的图。如上文描述,存储器胞元210、211、212及213(图2)中的每一者可经配置以存储多个信息位。图3展示其中假设存储器装置200的存储器胞元210、211、212及213中的每一者经配置以存储四个信息位(例如“0000”、“0101”或四个位的16种组合中的另一值)的实例。然而,本文中描述的技术可应用于其中存储器胞元210、211、212及213中的每一者可经配置以存储少于四个位或多于四个位的其它配置。

44.在图3中,电平l0到l15(16个电平l0到l15)可对应于16个阈值电压范围。电平l0到l15中的每一者表示四个位的唯一组合。如图3中展示,电平l0可对应于最低阈值电压范围300(其具有16个阈值电压范围中的最低电压范围)。电平l15可对应于阈值电压范围315(其具有16个阈值电压范围中的最高电压范围)。针对每胞元4位(如上文假设),存储器胞元210、211、212及213中的每一者可经编程以具有对应于16个电平l0到l15中的一者的阈值电压以存储四个位的唯一组合(例如“0000”、“0001”或四个位的组合的另一值中的一者)。在写入操作期间,存储器装置200可致使选定存储器胞元的阈值电压在对应于电平l0到l15中的一者的目标阈值电压范围内以反映所存储信息的值(4位值),其取决于存储于选定存储器胞元中的信息值(二进制值)。举例来说,如果选定存储器胞元经选择以存储对应于电平l1(电平l1的目标电平)的信息,那么存储器装置200可致使选定存储器胞元具有(例如,保持)在阈值电压范围301(在此实例中,其对应于目标电平l1)内的阈值电压。因此,在图3的实例中的写入操作中,选定存储器胞元的目标阈值电压可对应于电平l0到l15中的电平(例

如目标状态)。

45.存储器装置200可在写入操作的写入阶段期间将信息存储于一选定存储器胞元(或若干选定存储器胞元)中。将信息存储于存储器胞元中包含致使选定存储器胞元的阈值电压在目标阈值电压范围内(例如,在阈值电压范围300到315中的一者内)。存储器装置200还可执行写入验证阶段作为写入操作的部分。写入验证阶段经执行以确定存储于选定存储器胞元中(在写入阶段期间)的信息是否达到其目标值。

46.图4展示说明根据本文中描述的一些实施例的包含写入操作410的不同写入阶段411、413及415及写入验证阶段412、414及416的图2的存储器装置200的实例写入操作410的图。如图4中展示,存储器装置200可执行写入阶段且接着在每一写入阶段之后立即执行写入验证阶段。举例来说,存储器装置200执行写入阶段411及接着写入阶段之后的写入验证阶段412、写入阶段413及接着写入阶段413之后的写入验证阶段414及写入阶段415及接着写入阶段415之后的写入验证阶段416。图4展示其中写入操作410具有三个写入阶段及三个对应写入验证阶段的实例。然而,写入操作410可具有不同数目个写入阶段及对应写入验证阶段,其取决于在写入操作的写入阶段期间选定存储器胞元多快或多慢达到其目标电平。

47.存储器装置200可执行写入阶段(例如写入阶段411、413及415中的一者)以将信息存储于选定存储器胞元中。存储器装置200可执行写入验证阶段以确定(例如,验证或检查)选定存储器胞元是否达到其相应目标电平(例如阈值电压范围300到315中的相应阈值电压)。

48.图5是展示根据本文中描述的一些实施例的用于在存储器装置200中执行写入操作的方法500的流程图。方法500可为包含(例如,配置)于存储器装置200中(例如,包含于存储器装置200的控制单元中,如图1的控制单元118)的算法的部分。方法500可由软件、固件、硬件电路系统(例如逻辑电路系统)或软件、固件及硬件电路系统的任何组合执行。此软件、固件、硬件电路系统或此软件、固件及硬件电路系统的任何组合可经配置(例如,可包含)于存储器装置200中(例如,在存储器装置200的控制单元中)。存储器装置200在方法500中用作实例。然而,方法500可用于其它存储器装置中。如图5中展示,方法500可包含活动(例如存储器操作)505、510、515、520、525及530。

49.方法500可在活动505开始写入存储器操作,其可包含在写入操作中选择存储器胞元(例如目标存储器胞元)来存储信息(例如数据)。选定存储器胞元可为图2的存储器装置200的一些存储器胞元210、211、212及213。存储器装置200可在其从外部装置(例如存储器控制器或处理器)接收写入命令(编程命令)之后开始方法500。

50.活动510可包含对选定存储器胞元(例如目标存储器胞元)执行写入阶段(例如编程阶段)以将信息存储于选定存储器胞元中。写入阶段可包含图4的写入阶段中的一者(例如写入阶段411)。在活动515中执行写入阶段可包含将编程电压施加到耦合到选定存储器胞元的选定控制栅极。举例来说,如果存储器胞元串230、231、232及233的存储器胞元212(图2)在方法500的写入操作期间被选择,那么编程电压可施加到控制栅极252(图2)。图5中的活动510可致使选定存储器胞元基于存储于选定存储器胞元中的信息值具有相应目标电平。举例来说,活动515可致使选定存储器胞元中的每一者具有图3的电平l0到l15中的一者。在一些实例中,存储器装置200的存储器胞元可在执行活动510之前处于电平l0(例如擦除状态)。因此,在方法500中,如果特定存储器胞元经选择以存储对应于电平l0的信息,那

么活动510可跳过编程所述特定存储器胞元,因为所述特定存储器胞元已处于目标电平(例如电平l0)。

51.活动515可包含执行方法500的写入操作的写入验证阶段(例如编程验证阶段)。写入验证阶段可包含图4的写入验证阶段412、414及416中的一者。在图5中的活动515中执行写入验证阶段可包含感测耦合到选定存储器胞元的存储器胞元串的数据线及响应于感测数据线而确定选定存储器胞元是否达到其相应目标电平。所属领域的技术人员可理解感测及确定选定存储器胞元是否达到其目标电平。在图5中,活动515中的写入验证阶段可包含下文参考图6描述的写入验证阶段612。

52.活动520(图5)可包含确定所有选定存储器胞元是否达到其相应目标电平。活动520中的标记“否”指示少于所有(非所有)选定存储器胞元达到其目标电平。在此情况中,方法500可继续活动525。活动520中的标记“是”指示所有选定存储器胞元已达到(或被认为已达到)其目标状态。在此情况中,方法500可继续活动530。

53.活动525可响应于确定(由活动520执行)少于所有(非所有)选定存储器胞元已达到(或被认为已达到)其相应目标状态而执行。活动525可包含调整(例如,增大)编程电压(在活动510中施加)的值。举例来说,活动525可增大用于活动510中的电压(例如,增大编程脉冲的振幅)。在执行活动525之后,方法500可执行重复序列(例如,执行重复环路)以响应于来自在重复序列中执行的活动520的结果而至少再一次重复活动510、515、520及525中的部分或所有。

54.活动530可包含响应于确定(由活动520执行)所有选定存储器胞元已达到(或被认为已达到)其相应目标状态而结束(完成)写入操作。

55.如上文活动510中描述,在一些实例中,存储器装置200的一些特定存储器胞元可经选择以存储对应于电平l0(例如目标电平l0)的信息。因此,在此类实例中,存储器装置200可不对特定存储器胞元(例如具有目标电平l0的存储器胞元)执行写入阶段(在活动510中)及写入验证阶段(在活动515中),因为存储器装置200可确定此类存储器胞元已具有电平l0。存储器装置200可从擦除验证阶段的结果确定具有电平l0的特定存储器胞元,擦除验证阶段可由存储器装置200在方法500的写入操作之前执行。因此,如果存储于选定存储器胞元中的目标电平是电平l0,那么活动515中的写入验证阶段可跳过确定选定存储器胞元是否具有目标电平l0。

56.图6展示根据本文中描述的一些实施例的包含感测序列601到608的写入验证阶段612的实例。如上文假设,存储器装置200的每一存储器胞元可经配置以存储多个信息位,例如四个信息位。在每胞元配置4位配置的实例中,存储器装置200的存储器胞元中的每一者可存储对应于对应于16个电平(例如图3的电平l0到l15)的四个位的16种可能组合中的一者的信息。在图6的实例中,存储器装置200可循序执行感测序列601到608以循序验证选定存储器胞元的电平l1到l15(目标电平l0到l15)。如上文描述,存储器装置200可经配置使得电平l0(例如擦除电平,图6中未展示)在图6的写入验证阶段612中可被跳过。举例来说,存储器装置200可经配置以在擦除操作期间验证电平l0。因此,在此实例中,写入验证阶段612可跳过验证一目标存储器胞元(或若干存储器胞元)的电平l0。

57.如图6中展示,在每一感测序列601到607中,存储器装置200可并发地(例如,同时)验证对应于存储于不同选定存储器胞元中的信息的两个电平(双电平)。举例来说,存储器

装置200可执行感测序列601以验证电平l1及l2(包含电平l1及l2的双电平),执行感测序列602以验证电平l3及l4(包含电平l3及l4的双电平),等等。存储器装置200可执行感测序列608以验证仅一个电平(例如电平l15)而非两个电平。

58.如图6中展示,感测序列601可经执行以确定(例如,验证或检查)经选择以存储对应于电平l1及l2的信息的存储器胞元是否达到其相应目标电平(电平l1及l2)。感测序列602可经执行以确定经选择以存储对应于电平l3及l4的信息的存储器胞元是否达到其相应目标电平(电平l3及l4)。以此模式,感测序列603、604、605、606、607及608可经执行以确定经选择以存储信息的存储器胞元是否达到其相应目标电平(相应电平l5到l15,如图6中展示)。

59.如图6中展示,存储器装置200可将信号(电压信号)wl

ramp

施加到选定控制栅极(例如控制栅极252)。选定控制栅极(例如此实例中的控制栅极252)上的信号可称为选定控制栅极信号。因此,在此实例中,信号wl2(其与图2中的控制栅极252相关联)可具有对应于图6的信号wl

ramp

的波形的波形。如图6中展示,信号wl

ramp

的波形可具有斜坡形状,使得其可具有正斜率,其中值(电压值)从一个感测序列到下一后续感测序列增大。信号wl

ramp

可为线性斜坡信号或非线性斜坡信号。如图6中展示,信号wl

ramp

可具有对应于从电压v1(正电压)到电压vn的电压的正斜率。在特定感测序列期间,信号wl

ramp

的值可在所述特定感测序列内保持不变。

60.存储器装置200可包含电压产生器(例如图1的电压产生器115)。存储器装置200可包含控制单元(例如图1的控制单元116)以致使电压产生器向信号wl

ramp

提供(例如,施加)适当电压,使得信号wl

ramp

可具有图6中展示的波形。

61.在特定感测序列期间,与在所述特定感测序列中验证的存储器胞元相关联的数据线可称为有效数据线。在特定感测序列期间,与未在所述特定感测序列中验证的存储器胞元相关联的数据线可称为无效数据线。

62.存储器装置200可在感测序列601、602及607中的每一者期间向存储器装置200的相应数据线施加信号bl_l、bl_h及v0。在每一感测序列(例如感测序列601到608中的每一者)期间,有效数据线可被施加(例如,可具有)信号bl_l或信号bl_h,其取决于在感测序列期间耦合到有效数据线的选定存储器胞元的目标电平。在每一感测序列(例如感测序列601到608中的每一者)期间,无效数据线可被施加(例如,可具有)信号v0。在本文的描述中,术语“信号v0”及“电压v0”可互换使用。电压v0可由可保持在0v(例如,保持耦合到接地)的信号(例如信号v0)提供。信号bl_l及bl_h可被提供不同电压,使得信号bl_l及bl_h的波形彼此不同。

63.写入验证阶段(例如写入验证阶段612)中的电平l1到l15可分成八个群组l1到l2、l3到l4、l5到l6、l7到l8、l9到l10、l11到l12、l13到l14及l15。每一群组中的电平可为彼此相邻电平。举例来说,电平l1及l2彼此相邻。电平l3及l4彼此相邻,以此类推。每一群组中的电平(例如电平l1及l2)可对应于在阈值电压范围(如图3中展示)内彼此相邻的阈值电压。群组可被循序(一个群组接一个群组)验证。举例来说,群组l1到l2可在感测序列601中验证,群组l3到l4可在感测序列602中验证,群组l4到l5可在感测序列603中验证,以此类推。

64.图7a展示根据本文中描述的一些实施例的其中存储器胞元串230到237的存储器胞元212经选择以存储具有对应于相应电平(例如目标电平)l1、l2、l3、l4、l13及l14的值的

信息的实例。为简单起见,图7中仅展示存储器胞元串230到237中的每一者的存储器胞元212。存储器胞元串230到237(如图2中展示)的其它存储器胞元210、211及213及晶体管(例如源极及漏极选择晶体管)262及264从图7省略。为简单起见,电平l0到l15中仅部分(例如电平l1、l2、l3、l4、l13及l14)被假设存储(例如,随机存储)于存储器胞元串230到237的相应存储器胞元212中。如图7a中展示,假设一些存储器胞元212存储对应于相同电平的信息。举例来说,假设存储器胞元串234及236的存储器胞元212存储对应于电平l3的信息。在另一实例中,假设存储器胞元串235及237的存储器胞元212存储对应于电平l4的信息。图7a中的感测序列601、602及607相同于上文参考图6描述的感测序列。

65.存储器装置200可执行感测序列601、602及607以验证存储器胞元212中的相应电平l1、l2、l3、l4、l13及l14。图7a仅展示三个感测序列601、602及607(在八个群组l1到l2、l3到l4、l5到l6、l7到l8、l9到l10、l11到l12、l13到l14及l15中),因为仅三个不同群组的电平(例如群组l1到l2、l3到l4及l13到l14)被假设存储于图7a的实例的存储器胞元212中。在写入验证阶段中执行的感测序列的数目取决于在先前写入阶段中存储于存储器胞元中的电平群组的数目。

66.如图7a中展示,存储器装置200可执行感测序列601(图7a)以验证电平l1及l2,其是图7a的实例中相应存储器胞元串232及233的存储器胞元212的目标电平。存储器装置200可执行感测序列602以验证电平l3及l4,其是图7a的实例中相应存储器胞元串234、235、236及237的存储器胞元212的目标电平。存储器装置200可执行感测序列607以验证电平l13及l14,其是图7a的实例中相应存储器胞元串230及231的存储器胞元212的目标电平。

67.在图7a的实例中的感测序列601期间,数据线272及273可称为有效数据线,因为数据线272及273与在感测序列601期间验证的存储器胞元串232及233的存储器胞元212相关联。在图7a的实例中的感测序列601期间,数据线270、271、274、275、276及277可称为无效数据线,因为这些数据线与未在感测序列601期间验证的存储器胞元串230、231、234、235、236及237的存储器胞元212相关联。类似地,在图7a的实例中的感测序列602期间,数据线274、275、276及277可称为有效数据线,且数据线270、271、272及273可称为无效数据线。在图7a的实例中的感测序列607期间,数据线270及271可称为有效数据线,且数据线272、273、274、275、276及277在感测序列607期间可称为无效数据线。

68.如图7a中展示,存储器装置200可将信号bl_l及bl_h施加到相应有效数据线且将信号v0施加到无效数据线。施加到控制栅极252的信号wl

ramp

相同于上文参考图6描述的信号wl

ramp

。在图7a的实例中,控制栅极252上的信号w2可对应于信号wl

ramp

。因此,在图7a的实例中,控制栅极252上的信号w2可在感测序列601、602及607期间具有如信号wl

ramp

的波形。图7b、图7c及图7d展示由存储器装置200在图7a的不同感测序列601、602及607期间执行的感测序列期间数据线270到277上的信号的波形。

69.图7b展示根据本文中描述的一些实施例的感测序列601期间图7a的存储器装置的数据线270到277上的信号的波形。如图7b中展示,感测序列601可包含初始充电阶段710及后续充电阶段711。存储器装置200可在时间ta到tb之间执行初始充电阶段710。存储器装置200可在时间tb到tc之间执行后续充电阶段711。初始充电阶段710发生于后续充电阶段711之前。

70.在初始充电阶段710期间,存储器装置200可操作以将数据线272及273(此实例中

的有效数据线)充电到不同电压。在后续充电阶段711的部分(例如接近时间tc的部分)期间,存储器装置200可操作以感测数据线272及273上的信号以确定耦合到数据线272及273的存储器胞元串的选定存储器胞元是否达到其相应目标电平。

71.存储器装置200可在初始充电阶段710期间及在感测序列601的后续充电阶段711期间将电压v0(例如0v)施加到数据线270、271、274、275、276及277(此实例中的无效数据线)。举例来说,存储器装置200可在初始充电阶段710期间及在后续充电阶段711期间将数据线270、271、274、275、276及277耦合到接地且使这些数据线保持接地。因此,在整个感测序列601期间,数据线270、271、274、275、276及277上的电压可保持不变(例如,可保持在0v),而相应数据线272及273上的电压可改变(如由相应信号bl_l及bl_h表示)。

72.在图7a的实例中,数据线272及273与经选择以分别存储对应于电平l1及l2的信息的(存储器胞元串232及233的)存储器胞元212相关联。电平l1对应于具有低于电平l2的阈值电压的目标电平。在图7b中的初始充电阶段710期间,存储器装置200可将与具有较高目标电平(例如较高目标阈值电压)的存储器胞元相关联的有效数据线充电到正电压,且使与具有较低目标电平(例如较低目标阈值电压)的存储器胞元相关联的有效数据线保持在电压v0(例如0v)。因此,如图7b中展示,存储器装置200可将数据线273从电压v0充电到电压vinit,同时使数据线272保持在电压v0(例如,通过将数据线272耦合到接地)。电压vinit是正电压。电压vinit可小于耦合到存储器装置200的相应数据线的晶体管(例如图8中展示的晶体管804或806)的阈值电压的值。

73.在本描述中,电压的特定值作为实例用于帮助描述电压之间的关系。然而,可使用其它电压值。举例来说,图7b展示0.3v的电压vinit作为实例。可使用其它正值。

74.在图7b中的后续充电阶段711期间,存储器装置200可将有效数据线充电到不同正电压vx'及vx”。电压vx”大于电压vx'。举例来说,电压vx”可为电压vinit与电压vx'之和(例如,vx”=vinit vx')。存储器装置200可将与具有较高目标电平及较低目标电平(例如,分别为电平l2及l1)的存储器胞元相关联的有效数据线分别充电到电压vx”及vx'。电压vx'可大于电压vinit。举例来说,电压vx'可为0.5v。因此,作为实例,如果vinit=0.3v且vx'=0.5v,那么电压vx”可为0.8v。

75.图7c及图7d分别展示根据本文中描述的一些实施例的感测序列602及607期间图7a的存储器装置的有效及无效数据线270到277上的信号的波形。数据线270到277的波形类似于图7b中的波形,只是感测序列602及607中的每一者中的有效数据线(及无效数据线)不同于图7b中感测序列601中的有效数据线(及无效数据线)。

76.如图7c中展示,感测序列602可包含在时间td到te之间执行的初始充电阶段720及在初始充电阶段720之后在时间te到tf之间执行的后续充电阶段721。在后续充电阶段721期间(例如,接近时间tf),存储器装置200可操作以感测数据线274、275、276及277以确定选定存储器胞元是否达到其相应目标电平。

77.数据线274及276(有效数据线)与经选择以存储对应于电平l3(如图7a中展示)的信息的存储器胞元相关联。数据线275及277(有效数据线)与经选择以存储对应于电平l4(如图7a中展示)的信息的存储器胞元相关联。在电平l3与l4之间,电平l3是较低电平,且电平l4是较高电平。

78.在初始充电阶段720期间,存储器装置200可将数据线275及277(有效数据线)充电

到电压vinit,同时使数据线274及276(有效数据线)保持在电压v0。在后续充电阶段721期间,存储器装置200可将数据线275及277充电到电压vx”且将数据线274及276充电到电压vx'。存储器装置200可在初始充电阶段720及后续充电阶段721期间使数据线270、271、272及273(无效数据线)保持在电压v0。

79.如图7d中展示,感测序列607可包含在时间tg到th之间执行的初始充电阶段730及在初始充电阶段730之后在时间th到ti之间执行的后续充电阶段731。在后续充电阶段731期间(例如,接近时间ti),存储器装置200可操作以感测数据线270及271以确定选定存储器胞元是否达到其相应目标电平。

80.数据线270及271(有效数据线)分别与经选择以存储对应于电平l13及l14(如图7a中展示)的信息的存储器胞元相关联。在电平l13与l14之间,电平l13是较低电平,且电平l14是较高电平。

81.在初始充电阶段730期间,存储器装置200可将数据线271(有效数据线)充电到电压vinit,同时使数据线270(有效数据线)保持在电压v0。在后续充电阶段731期间,存储器装置200可将数据线271充电到电压vx”且将数据线270充电到电压vx'。存储器装置200可在初始充电阶段730及后续充电阶段731期间使数据线272、273、274、275、276及277(无效数据线)保持在电压v0。

82.在参考图7a、图7b、图7c及图7d(及本文中描述的其它图(例如图11))的上文描述中,初始充电阶段(例如初始充电阶段710、720或730)期间信号bl_l及bl_h上的电压之间的差可由方程式vinit-v0=delta1(vinit减去v0等于delta1)表示。后续充电阶段(例如后续充电阶段711、721或731)期间信号bl_l及bl_h上的电压之间的差可由方程式vx

”‑

vx'=delta2(vx”减去vx'等于delta2)表示。delta2的值(电压值)可基于delta1的值(电压值)。举例来说,delta2的值可与delta1的值成比例,使得如果delta1的值增大(相对于选定值(例如0.3v)),那么delta2的值也增大。类似地,如果delta1的值减小(相对于选定值(例如0.3v)),那么delta2的值也减小。delta2的值可相同于delta1的值。举例来说,如果v0=0,那么delta2=delta1=vinit,如图7b、图7c及图7d中展示。作为实例,如果delta1的值是0.3v,那么delta2的值也可为0.3v。

83.在参考图7a、图7b、图7c及图7d(及本文中描述的其它图(例如图11))的上文描述中,电压v0的值可为0v,且vinit的值是正值。然而,只要电压v0的值小于电压vinit的值,那么电压v0的值可大于0v。

84.图8展示根据本文中描述的一些实施例的可为存储器装置200的缓冲器及感测放大器电路系统的部分的电路820的示意图。电路820可对应于(或可包含于)图2的页面缓冲器及感测电路220、221、222及223中的一者。如图8中展示,电路820可耦合到数据线270i,数据线270i可为存储器装置200的数据线中的一者(例如图2及图7a的数据线270到277中的一者)。存储器装置200的数据线中的每一者可耦合到相应电路820。因此,在图7a的实例中,可存在耦合到八个相应数据线(数据线270到277)的八个不同电路820。在写入验证阶段(例如图6的写入验证阶段612)期间,电路820(图8)可用作存储器装置200的缓冲器及感测电路系统的部分以将适当信号(图7a中的信号bl_l、bl_h及v0中的一者)施加到相应数据线(数据线270i)。

85.图8还展示可为存储器胞元串230到237(图2及图7a)中的一者的存储器胞元串

230i。存储器胞元串230i可在节点870i处耦合到数据线270i。每一电路820可由耦合到相同数据线的存储器胞元串共享。

86.如图8中展示,电路820可耦合到节点(例如供应节点)801及850。节点801可经配置以接收电压vsupply,电压vsupply可为存储器装置200的供应电压(例如电压vcc)。节点850可经配置以耦合到接地。因此,节点850可为存储器装置200的接地连接(例如接地节点或接地平面)的部分。电路820可包含锁存器a及b、晶体管802、804、806、808、810、812、814及818及具有图8中展示的连接的反相器819。电路820可经配置以在晶体管804、806及810的栅极处接收信号,例如信号clamp_l、clamp_h及sense。

87.如图8中展示,电路820可包含电路路径831、832及833。电路路径831及832可共享节点835。电路路径831、832及833可包含相应晶体管(例如晶体管802、804、806、808及816),其中晶体管可具有相同晶体管类型。举例来说,晶体管802、804、806、808及816(其包含于相应电路路径831、832及833中)可为n沟道金属氧化物半导体(nmos)晶体管。

88.晶体管802及804可为耦合于节点801与870i之间的电路路径831的部分(可包含于电路路径831中)。晶体管806及808可为耦合于节点835与870i之间的电路路径832的部分(可包含于电路路径832中)。晶体管816可为耦合于节点835与850之间的电路路径833的部分(可包含于电路路径833中)。如图8中展示,电路路径831可具有与节点835与870i之间的电路路径832平行的部分(在节点835与870i之间)。

89.电路820可包含节点840,其耦合到存储器装置200的其它电路。其它电路可为输入/输出电路系统的部分以在存储器装置200的数据线270i与其它电路之间传送信息(呈通过节点840的信号的形式)。举例来说,在存储器装置200的感测操作(其可为写入验证阶段的部分)期间,从耦合到电路820的存储器胞元串的选定存储器胞元感测到的信息可通过节点840提供到其它电路。

90.电路路径831可经配置以在与存储器装置200的写入操作的写入验证阶段相关联的初始充电阶段(例如图7b中的初始充电阶段710)期间传导电流(节点801与870i之间的电流)。当电路路径831传导电流时,电路路径832可经配置以在与存储器装置200的写入操作的写入验证阶段相关联的初始充电阶段(例如图7b中的初始充电阶段710)期间不传导电流。电路路径831及832可经配置以在与存储器装置200的写入操作的写入验证阶段相关联的后续充电阶段(例如图7b中的后续充电阶段711)期间传导电流(在节点801与870i之间)。

91.在操作中,晶体管804及806可分别为电路路径831及832上的箝位电路的部分。晶体管804及806可操作以在数据线270i上提供(例如,充电)适当电压(例如箝位电压)及在不同时间使数据线270i上的电压维持(例如,箝制)在特定(例如箝位)电压。晶体管802可为上拉电路,其可经接通(或关断)以通过电路路径831及832中的一或两者向数据线270i提供(或不提供)电压。晶体管816(其由反相器819的输出节点处的信号控制)可经接通以通过电路路径833将节点835耦合到节点850。晶体管816可经关断以使节点835与节点850解耦(以不将节点835耦合到节点850)。晶体管810及812可在感测阶段(例如写入验证阶段的部分)期间分别由信号sense及节点835处的信号控制。感测阶段期间节点840上的信息可对应于存储于存储器胞元串的选定存储器胞元中的信息值。

92.锁存器a及b可经配置以保持信息,其可用于提供信息(例如图9a、图9b、图10a及图10b中的信息l及h)以控制电路路径831、832及833上的晶体管。适当电压可在写入操作期间

(例如,在写入验证阶段期间)部分基于来自锁存器a及b的信息来提供到数据线270i、节点835及电路820的其它组件(例如晶体管的栅极)。开关817可在写入操作的写入验证阶段的部分期间接收信息transfer以改变(例如,更新)锁存器a及b中的信息值。电路820的更详细操作在下文参考图9a、图9b、图10a、图10b及图11描述。

93.图9a及图9b展示根据本文中描述的一些实施例的图7b的感测序列601的初始充电阶段710期间的电路820

272

及820

273

及相关联数据线272及273。电路820

272

及820

273

是分别可为图2的页面缓冲器及感测电路222及223的部分的两种不同电路。电路820

272

及820

273

是图8的电路820的两个不同副本。如图9a及图9b中展示,电路820

272

及820

273

耦合到不同数据线(数据线272及273)。举例来说,图9a中的数据线272可对应于图8的电路820的副本(例子)的数据线270i。图9b中的数据线273可对应于图8的电路820的另一副本的数据线270i。

94.如图9a及图9b中展示,存储器胞元串232及233分别耦合到数据线272及273。图9a中的存储器胞元串232(其耦合到数据线272)可对应于图8的电路820的副本的存储器胞元串230i。图9b中的存储器胞元串233(其耦合到数据线273)可对应于图8的电路820的另一副本的存储器胞元串230i。分别与图9a及图9b相关联的初始充电阶段710期间电路820

272

及820

273

的操作在下文描述。在下文描述中,感测序列601的初始充电阶段710及后续充电阶段711对应于图7b中展示的感测序列601的初始充电阶段710及后续充电阶段711。

95.在图9a及图9b中,在初始充电阶段710期间,信号clamp_h可被提供可为接地电势的0v(零伏特)。信号clamp_l可被提供具有由电压vt与电压vinit之和表示的值的电压。电压vt可表示电路820的晶体管(例如n沟道晶体管)的阈值电压。举例来说,电压vt对应于晶体管804及806的阈值电压。电压vinit可为预定电压,其可基于在后续充电阶段711接近结束的时间间隔(例如图11的时间间隔1105,如下文参考图11更详细描述)期间数据线272及273上的电压值之间的差。

96.在图9a及图9b中,信息l及信息h可呈提供到电路820

272

及820

273

的相应晶体管的栅极以控制(例如接通或关断)相应晶体管的信号(例如电压信号)的形式。信息l的值可对应于逻辑电平(例如二进制0)。信息h的值可对应于另一逻辑电平(例如二进制1)。信息l及h的值可基于含于(例如,存储于)锁存器a及b中的相应信息值。含于锁存器a及b中的值可基于在存储器装置200的写入操作期间选定存储器胞元的目标电平的值。举例来说,在写入验证阶段期间,信息可提供到(例如,锁存于)电路820

272

(图9a)的锁存器a及b,其可基于耦合到数据线272的存储器胞元串的选定存储器胞元的目标电平(例如电平l0到l15中的一者)。类似地,在写入验证阶段期间,信息可提供到电路820

273

(图9b)的锁存器a及b,其可基于耦合到数据线273的存储器胞元串的选定存储器胞元的目标电平(例如电平l0到l15中的一者)。

97.在与图9a及图9b相关联的初始充电阶段710期间,耦合到具有含较低目标电平(在所验证的两个目标电平之间)的选定存储器胞元的存储器胞元串的数据线(例如图9a中的数据线272)可保持在0v(例如,在节点850处)。耦合到具有含较高目标电平(在所验证的两个目标电平之间)的选定存储器胞元的存储器胞元串的数据线(例如图9b中的数据线273)可充电到正电压(例如电压vinit)。因此,在初始充电阶段710期间,数据线272(图9a)可保持在电压v0(例如0v),且数据线273(图9b)可充电到电压vinit(vinit》v0,其中v0=0v)。电压vinit的值可小于晶体管804或806的阈值电压的值。

98.在图9a中的初始充电阶段710期间,电路820

272

的锁存器b的输出节点处的信息l可

具有一值,使得晶体管816可经接通以将电路820

272

的节点835耦合到节点850(例如接地电势)。数据线272可通过晶体管804保持在接地电势(在节点850处)。信号clamp_h可被提供0v以关断晶体管806。此可停用包含节点835与数据线272之间的晶体管806及808的电路路径。

99.在图9b中的初始充电阶段710期间,信号clamp_h可被提供0v以关断晶体管806。此可停用包含节点835与数据线273之间的晶体管806及808的电路路径。电路820

273

的锁存器b的输出节点处的信息h可具有一值,使得晶体管816可被关断。因此,不同于图9a的电路820

272

的节点835(其耦合到节点850(接地)),图9b的电路820

273

的节点835不耦合到节点850(例如,不耦合到接地)。

100.晶体管802可基于图9b的电路820

273

的锁存器b的输出节点处的信息h的值来接通。电路820

273

的晶体管804还可由信号clamp_l接通。因此,如图9b中展示,电流路径931a可形成于节点801与数据线273之间。电流路径931a可为包含晶体管802及804的电路路径831(图8)的部分。电流路径931a允许数据线273充电到正电压(例如电压vinit)。

101.因此,如上文描述,在初始充电阶段710期间,数据线273(图9b)可充电到电压vinit(正电压),而数据线272(图9a)可保持在小于电压vinit的电压v0(例如0v)。

102.图10a及图10b展示根据本文中描述的一些实施例的图7b的感测序列601的后续充电阶段711期间的电路820

272

及820

273

及相关联数据线272及273。图10a中的电路820

272

相同于图9a的电路820

272

。然而,图10a中电路820

272

中的信号与后续充电阶段711相关联,而图9a中电路820

272

中的信号与初始充电阶段710相关联。类似地,图10b中的电路820

273

相同于图9b的电路820

273

。然而,图10b中电路820

273

中的信号与后续充电阶段711相关联,而图9b中电路820

273

中的信号与初始充电阶段710相关联。在关于图10a及图10b的描述中,感测序列601的后续充电阶段711指代图7b中展示的感测序列601的后续充电阶段711。

103.在图10a及图10b中,在后续充电阶段711期间,数据线272及273可充电到不同正电压。举例来说,数据线272(图10a)可充电到电压vx'(其中vx'》v0)且数据线273(图10b)可充电到电压vx”,其可为电压vinit与电压vx'之和(vx”=vinit vx')。

104.在图10a中,锁存器b的输出节点可变到信息h(从图9a中的信息l)。信息h可具有一值,使得电路820

272

(图10a)的晶体管816可被关断。因此,电路820

272

的节点835可在与图10a相关联的后续充电阶段711期间与节点850(接地)解耦。图10a中电路820

272

的锁存器a的输出节点可变到信息l(从图9a中的信息h)。图10a中的信息l可具有一值,使得电路820

272

的晶体管808可被关断。因此,在与图10a相关联的后续充电阶段711期间,通过晶体管806及808的电路电流未形成于节点835与数据线272之间。

105.电路820

272

的晶体管802可基于电路820

272

的锁存器b的输出节点处的信息h的值来接通。信号clamp_l可被提供一电压(例如电压vt与电压vx之和)以接通晶体管804,使得电流路径1031可通过晶体管802及804形成于节点801与数据线272之间。电流路径1031允许数据线272充电到vx'。电压vx'可基于(例如,等于)电压vx。

106.在图10b的电路820

273

中,电流路径931b可形成于节点801与数据线273之间。电流路径1032可形成于节点835与数据线273之间。电流路径1032可与节点835与数据线273之间的电流路径931b的部分平行(例如,作为所述部分的补充)。信号clamp_h被提供一电压(例如电压vt、电压vinit及电压vx之和)以接通晶体管806,使得电流路径1032可通过晶体管806及808形成于节点835与数据线273之间。平行电流路径931及1032的组合允许数据线273

充电到电压vx”。

107.尽管电流路径1032在本文中描述为与节点835与数据线273之间的电路路径相关联的电流,但电流路径1032可为通过晶体管802、808及806在节点801与数据线273之间的电流路径的部分。因此,电流路径1032可为在节点801与数据线273之间包含晶体管802、806及808的电路路径的部分。因此,电流路径1032及电流路径931b可由共享节点801与节点835之间的电路部分的相应电路路径(包含晶体管802及804的电路路径及包含晶体管802、806及808的电路路径)导通,其中电路部分包含晶体管802。

108.在图10b中,开关817及信息transfer可经配置以基于上文参考图9a、图9b、图10a及图10b描述的操作依适当时间间隔提供信息l及h(如上文描述)。

109.因此,如上文描述,在初始充电阶段710期间,数据线273(图9b)可充电到电压vinit,而数据线272(图9a)可保持在电压v0(例如0v)。在后续充电阶段711(图10a及图10b)期间,数据线272及273可充电到不同正电压(例如电压vx'及vx”(其中vx'《vx”))。

110.如上文参考图8、图9a及图10a描述,图8中的电路路径831可经配置以在其中执行初始充电阶段710的时间间隔期间(例如,在图7b中的时间ta到tb之间)不传导电流(图9a)。然而,图8的电路路径831可经配置以在其中执行后续充电阶段711的时间间隔期间(例如,在图7b中的时间tb到tc之间)传导电流(由图10a中的电流路径1031表示)。

111.如上文参考图8、图9b及图10b描述,图8中的电路路径831可经配置以在其中执行初始充电阶段710的时间间隔期间(例如,在图7b中的时间ta到tb之间)传导电流(由图9b中的电流路径931a表示)。图8的电路路径831也可经配置以在其中执行后续充电阶段711的时间间隔期间(例如,在图7b中的时间tb到tc之间)传导电流(由图10b中的电流路径931b表示)。

112.如上文参考图8、图9b及图10b描述,图8中的电路路径832可经配置以在一时间间隔期间(例如,在图7b中的时间ta到tb之间)不传导电流(图9b)。然而,图8的电路路径832可经配置以在其中执行后续充电阶段711的时间间隔期间(例如,在图7b中的时间tb到tc之间)传导电流(由图10b中的电流路径1032表示)。

113.图11展示说明根据本文中描述的一些实施例的感测序列601期间图9a、图9b、图10a及图10b中相应电路820

272

及820

273

的信号bl_l及bl_h及其它信号的波形的更多细节的时序图。图11中的信号bl_l及bl_h的波形分别相同于图7b中展示的信号bl_l及bl_h的波形。然而,图11展示信号bl_l及bl_h相对于图9a、图9b、图10a及图10b的电路820

272

及820

273

的其它信号的更多细节。

114.在图11中,时间t0到t5表示感测序列601的不同时间(不同时间点)。时间t0及t5可分别对应于图7b的时间ta及tc。在图11中,时间t0发生于时间t1之前。时间t1发生于时间t2之前,以此类推,其中时间t5最后发生。时间t0到t5可分成时间间隔(持续时间)1101、1102、1103、1104及1105。时间间隔1101发生于时间间隔1102之前,时间间隔1102发生于时间间隔1103之前,以此类推,其中时间间隔1105最后发生。

115.时间间隔1101可为感测序列601的初始充电阶段的部分,例如上文参考图7b、图9a及图9b描述的初始充电阶段710。时间间隔1103、1104及1105可为感测序列601的后续充电阶段的部分,例如上文参考图7b、图10a及图10b描述的后续充电阶段711。

116.时间间隔1102可发生于感测序列601的初始充电阶段(例如初始充电阶段710)与

后续充电阶段(例如后续充电阶段711)之间的过渡阶段期间。因此,时间间隔1102可为初始充电阶段的部分、后续充电阶段的部分或两者。

117.时间间隔1105(其可为后续充电阶段711的部分)可被视为感测序列601结束时(或接近结束)的时间间隔。在时间t5,相应数据线上的信号(例如信号bl_l及bl_h)可复位到复位电压,其可为电压v0(例如0v)。接着,新感测序列(例如图6中的感测序列602)可在时间t5之后开始以验证选定存储器胞元的下一目标电平。下一感测序列(例如感测序列602)中有效数据线上的信号的波形可类似于(或相同于)图11中展示的信号的波形。

118.以下描述参考图9a、图9b、图10a、图10b及图11。在图11中,信号clamp_l、clamp_h、bl_l、bl_h及sense相同于图9a、图9b、图10a、图10b中展示的信号。图11展示不同时间间隔期间电压信号clamp_l、clamp_h、bl_l、bl_h及sense的波形及其相对电压。

119.图11中展示的电压值是实例值。其它值可基于存储器装置200的配置使用。举例来说,图11展示具有0.3v的值的电压vinit作为实例。然而,电压vinit可具有其它正值。在另一实例中,图11展示具有0.5v的值的电压vx作为实例。然而,电压vx可具有其它正值。在图11中,电压vx'可基于(例如,等于)电压vx(例如,vx'=vx=0.5v)。因此,电压vx”(其是电压vinit与vx之和)可具有0.8v的实例值。

120.在图11中,在时间间隔1101、1102、1103、1104及1105期间含于电路820

272

及电路820

273

的锁存器a及b中的信息值可基于耦合到相应数据线272及273的存储器胞元串的选定存储器胞元的目标电平(例如图11的实例中的电平l1及l2)的值。信息l及信息h的值分别基于电平l1及l2的值。举例来说,在时间间隔1101期间,图9a中的电路820

272

的锁存器a及b可分别具有对应于电平l1及l2的值。因此,在图11中的时间间隔1101(其是初始充电阶段710的部分)期间,图9a中的电路820

272

的锁存器a及b的输出节点可分别具有信息l及信息h。在另一实例中,在图11中的时间间隔1101期间,电路820

273

的锁存器a及b两者可具有对应于电平l2的值。因此,在图11中的时间间隔1101(其是初始充电阶段710的部分)期间,图9b中的电路820

273

的锁存器a及b两者的输出节点可具有信息h。

121.时间间隔1101内电路820

272

及820

273

中的一或两者的锁存器a及b的值可在时间间隔1103内变到(换成)不同值。举例来说,存储器装置200可将电路820

272

的锁存器b的值从对应于l1的值切换到对应于电平l2的值及将锁存器a的值从电平l1切换到电平l2。在图11的时间间隔1102期间,存储器装置200可使用开关817(图8)将适当信息(例如电平l1或l2)提供到电路820

272

及820

273

中的一或两者的锁存器a及b。

122.如图9a及图11中展示,在时间间隔1101期间,锁存器a及b可被提供信息,使得锁存器a及b的输出(例如输出节点)可具有信息l或h。信息l可对应于可关断(或禁用)晶体管(例如n沟道晶体管,如图9a中展示的电路820的晶体管中的一者)的电压。信息h可对应于可接通(或启用)图9a中展示的电路820

272

的晶体管(例如n沟道晶体管)的电压。因此,信息l及h可具有相反值(例如互补值)。

123.在图11中,数据线272与273之间的电容耦合效应可发生于时间间隔1103期间。耦合效应可稳定于时间t3到t5之间,其中数据线272及273可在时间间隔1105期间达到其相应电压(例如vx'及vx”)。信号sense可在时间间隔1105期间从电压v0(例如0v)激活到电压v_en(例如感测放大器启用电压)。写入验证阶段的感测序列的感测阶段可发生于时间间隔1105期间。存储器装置200可操作以在时间间隔1105期间(例如,在感测阶段期间)感测数据

线272及273(例如,基于图10a及图10b中的820

272

及820

273

的节点835处的信号)。存储器装置200可在图11中的时间间隔1105期间基于图10a及图10b中的820

272

及820

273

的节点835处的信号的值来确定选定存储器胞元是否达到其相应目标电平(例如目标阈值电压)。

124.上文描述的结构化及操作存储器装置200允许存储器装置200具有相较于类似常规存储器装置的改进及益处。举例来说,存储器装置200可经配置成替代配置,其中存储器装置200可在初始充电阶段期间(例如,在图11中的时间间隔1101期间)将所有有效数据线(例如图11中的数据线272及273两者)充电到正电压,而无需使一些有效数据线保持接地。然而,与上述配置相比,此替代配置可具有缺点。举例来说,在替代配置中在初始充电时间期间使所有(例如两个或更多个)有效数据线充电可致使有效数据线具有比上文参考图7a到图11描述的配置的稳定时间更长的稳定时间。本文中论述的稳定时间包含时间t2到时间t5之间的时间间隔。

125.作为实例,在替代配置中,数据线272及273两者可从时间t0充电到正电压(例如电压vinit)。此可在数据线之间添加额外耦合电容且致使数据线272及273的充电时间显著增加。举例来说,在替代配置中,数据线272可向上耦合到数据线272(其具有比数据线273更高的电压)。因此,数据线272上的电荷将需要更多时间来恢复(例如,返回到预定电平)。由于替代配置中的更长充电时间,并发地验证选定存储器胞元的多个目标电平的益处将显著减少。

126.在本文中描述的存储器装置的配置(例如存储器装置200的电路及操作)中,通过使与选定存储器胞元相关联的数据线(例如图11中的数据线272)保持在电压v0(例如0v)及将另一数据线273(在图11中)充电到电压vinit,可在数据线272与273之间预先产生适当电势差(例如,在时间间隔1101期间产生)。此可显著减少数据线272及273的总充电时间。此可缩短稳定时间(例如,时间t2到时间t5之间的时间间隔可短于替代配置的时间间隔)。因此,可改进本文中描述的存储器装置(例如存储器装置200)的总体性能。

127.图12展示根据本文中描述的一些实施例的呈系统(例如电子系统)1200的形式的设备。系统1200的部分或整个系统1200可包含或包含于单芯片系统、系统级封装、固态硬盘(ssd)、手机、平板计算机、计算机、汽车中的电子模块或其它类型的电子系统中。如图12中展示,系统1200可包含处理器1210、存储器装置1220、存储器控制器1230、图形控制器1240、i/o控制器1250、显示器1252、键盘1254、指向装置1256、至少一个天线1258、连接器1215及总线1260(例如形成于系统1200的电路板(未展示)上的导电线)。

128.在一些布置中,系统1200不必包含显示器。因此,显示器1252可从系统1200省略。在一些布置中,系统1200不必包含任何天线。因此,天线1258可从系统1200省略。

129.处理器1210、存储器装置1220、存储器控制器1230、图形控制器1240及i/o控制器1250中的每一者可包含裸片且可为ic封装的部分。

130.处理器1210可包含通用处理器或专用集成电路(asic)。处理器1210可包含中央处理单元(cpu)。

131.存储器装置1220可包含动态随机存取存储器(dram)装置、静态随机存取存储器(sram)装置、快闪存储器装置(例如nand快闪存储器装置)、相变存储器、这些存储器装置的组合或其它类型的存储器。

132.在实例中,存储器装置1220可包含上文参考图1到图11描述的存储器装置100或

200。因此,存储器装置1220可包含上文参考图1到图11描述的存储器装置(例如存储器装置100或200)的结构及存储器操作(例如写入操作)。在图12中,处理器1210或存储器控制器1230可与存储器装置1220通信以致使存储器装置1220执行上文参考图1到图11描述的存储器操作。举例来说,处理器1210或存储器控制器1230可向存储器装置1220发送指令(例如呈信号的形式的命令)以致使存储器装置1220执行写入、读取或擦除操作。写入操作可包含上文参考图1到图11描述的写入操作中的任何者。

133.显示器1252可包含液晶显示器(lcd)、触摸屏(例如电容或电阻触摸屏)或另一类型的显示器。指向装置1256可包含鼠标、触控笔或另一类型的指向装置。

134.i/o控制器1250可包含用于有线或无线通信(例如通过一或多个天线1258的通信)的通信模块。此无线通信可包含根据wifi通信技术、长期演进高级(lte-a)通信技术或其它通信技术的通信。

135.i/o控制器1250还可包含一模块以允许系统1200根据以下标准或规范(例如i/o标准或规范)中的一或多者与其它装置或系统通信,包含通用串行总线(usb)、显示器端口(dp)、高清多媒体接口(hdmi)、雷电接口(thunderbolt)、外围组件互连快速(pcie)、以太网及其它规范。

136.连接器1215可经布置(例如,可包含端子,例如引脚)以允许系统1200耦合到外部装置(或系统)。此可允许系统1200通过连接器1215与此装置(或系统)通信(例如,交换信息)。连接器1215可通过连接1216(例如总线)耦合到i/o控制器1250。

137.连接器1215、连接1216及总线1260的至少一部分可包含符合usb、dp、hdmi、雷电接口、pcie、以太网及其它规范中的至少一者的元件(例如导电端子、导电线或其它导电元件)。

138.图12展示彼此单独布置的系统1200的元件(例如装置及控制器)作为实例。在一些布置中,系统1200的两个或更多个元件可定位于相同ic封装、相同子系统或相同装置上。举例来说,存储器装置1220及存储器控制器1230可包含于系统1200的相同ssd或相同存储器子系统中。

139.设备(例如存储器装置100、200及1220)及方法(例如操作存储器装置100、200及1220的方法,包含方法500)的说明希望提供各个实施例的结构的一般理解且不希望提供可使用本文中描述的结构的设备的所有元件及特征的完整描述。本文中的设备指代例如装置(例如存储器装置100、200及1220中的任何者)或包含例如存储器装置100、200及1220中的任何者的装置的系统(例如计算机、手机或其它电子系统)。

140.上文参考图1到图12描述的组件中的任何者可以众多方式实施,其包含经由软件模拟。因此,例如上述存储器装置100、200及1220或这些存储器装置中的每一者的部分的设备在本文中可全部特性化为“若干模块”(或“模块”)。此类模块可根据期望及/或根据各个实施例的特定实施方案的需要包含硬件电路系统、单处理器及/或多处理器电路、存储器电路、软件程序模块及对象及/或固件及其组合。举例来说,此类模块可经包含于系统操作模拟封装中,例如软件电信号模拟封装、功率使用及范围模拟封装、电容-电感模拟封装、功率/热耗散模拟封装、信号传输-接收模拟封装及/或用于操作或模拟各种潜在实施例的操作的软件与硬件的组合。

141.存储器装置100、200及1220可经包含于设备(例如电子电路系统)中,例如高速计

算机、通信及信号处理电路系统、单处理器或多处理器模块、单嵌入式或多嵌入式处理器、多核处理器、消息信息交换机及包含多层多芯片模块的专用模块。此类设备可进一步包含为各种其它设备(例如电子系统)内的子组件,例如电视机、手机、个人计算机(例如膝上型计算机、桌上型计算机、手持计算机、平板计算机等)、工作站、无线电、视频播放器、音频播放器(例如mp3(运动图像专家组、音频层3)播放器)、交通工具、医疗装置(例如心脏监测器、血压监测仪等)、机顶盒及其它。

142.上文参考图1到图12描述的实施例包含设备及形成设备的方法。设备中的一者包含:第一及第二数据线,其耦合到相应第一及第二存储器胞元串;存取线,其分别由第一及第二存储器胞元串的第一及第二存储器胞元共享;及控制单元,其包含用于执行操作的电路系统,操作包含:在对第一及第二存储器胞元执行的操作的第一时间间隔期间将第一数据线充电到第一电压;在第一时间间隔期间使第二数据线保持在第二电压;在操作的第二时间间隔期间将第一数据线充电到第三电压;在第二时间间隔期间将第二数据线充电到第四电压;及在操作的第二时间间隔期间确定第一存储器胞元是否达到第一阈值电压及第二存储器胞元是否达到第二阈值电压。描述包含额外设备及方法的其它实施例。

143.在具体实施方式及权利要求书中,关于一个在另一个“上”的两个或更多个元件(例如材料)使用的术语“上”意味着在元件之间(例如,在材料之间)存在至少一些接触。术语“之上”意味着元件(例如材料)紧密接近,但可能具有一或多个额外中介元件(例如材料),使得接触是可能的但不是必需的。“上”及“之上”两者不暗含本文中使用的任何方向性,除非如此陈述。

144.在具体实施方式及权利要求书中,术语“第一”、“第二”及“第三”等仅用作标记,且不希望对其对象强加数值要求。

145.在具体实施方式及权利要求书中,由术语

“…

中的至少一者”结合的项目列表可意味着所列项目的任何组合。举例来说,如果列举项目a及b,那么短语“a及b中的至少一者”意味着仅a、仅b或a及b。在另一实例中,如果列举项目a、b及c,那么短语“a、b及c中的至少一者”意味着仅a、仅b、仅c、a及b(排除c)、a及c(排除b)、b及c(排除a)或a、b及c所有。项目a可包含单个元件或多个元件。项目b可包含单个元件或多个元件。项目c可包含单个元件或多个元件。

146.在具体实施方式及权利要求书中,由术语

“…

中的一者”结合的项目列表可意味着所列项目中的仅一者。举例来说,如果列举项目a及b,那么短语“a及b中的一者”意味着仅a(排除b)或仅b(排除a)。在另一实例中,如果列举项目a、b及c,那么短语“a、b及c中的一者”意味着仅a、仅b或仅c。项目a可包含单个元件或多个元件。项目b可包含单个元件或多个元件。项目c可包含单个元件或多个元件。

147.上文描述及图式说明发明标的物的一些实施例以使所属领域的技术人员能够实践发明标的物的实施例。其它实施例可并入结构、逻辑、电、过程及其它变化。实例仅代表可能变化。一些实施例的部分及特征可经包含于其它实施例的部分及特征中或代替其它实施例的部分及特征。所属领域的技术人员将在阅读及理解上文描述之后明白许多其它实施例。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。