用于控制修复操作的半导体器件

1.相关申请的交叉引用

2.本技术要求在2021年8月5日提交的申请号为10-2021-0103266的韩国专利申请的优先权,该专利申请通过引用被整体合并于此。

技术领域

3.本公开的实施例涉及用于控制修复操作的半导体器件。

背景技术:

4.通常,在半导体器件中,在各种状态中执行的修复操作用于利用冗余单元来代替故障单元。可以在晶圆状态或者封装状态中执行在半导体器件中使用的修复操作。在封装状态中执行的修复操作被称为封装后修复(ppr)。

技术实现要素:

5.根据本公开的实施例,一种半导体器件包括标志生成电路,该标志生成电路被配置为:接收根据基于熔丝组选择信号从熔丝组中所选择的熔丝组所生成的区域熔丝数据和使用熔丝数据,以及基于区域熔丝数据和使用熔丝数据来生成存储体资源标志以控制对尚未被执行修复操作的存储体的修复操作。半导体器件还包括修复控制电路,该修复控制电路被配置为基于存储体资源标志来控制对共用熔丝组的存储体的修复操作。

6.此外,根据本公开的另一个实施例,一种半导体器件包括熔丝数据生成电路,该熔丝数据生成电路被配置为包括多个熔丝组,多个熔丝组的每一个都包括至少一个存储体熔丝、至少一个地址熔丝、以及使用熔丝,以及该熔丝数据生成电路被配置为根据通过熔丝组选择信号从熔丝组中选择的熔丝组来生成区域熔丝数据和使用熔丝数据。半导体器件还包括标志生成电路,该标志生成电路被配置为基于区域熔丝数据和使用熔丝数据来生成存储体资源标志以控制对尚未被执行修复操作的存储体的修复操作。

附图说明

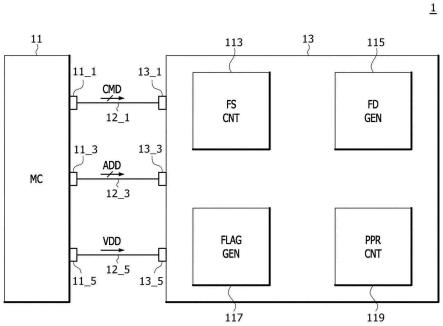

7.图1是图示出根据本公开的实施例的半导体系统的配置的图。

8.图2是图示出根据图1中所图示出的半导体系统中所包括的半导体器件的示例的配置的框图。

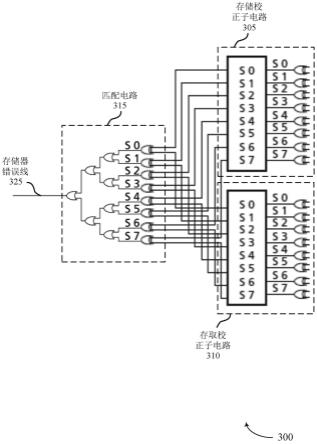

9.图3是图示出根据图2中所图示出的半导体器件中所包括的熔丝组选择控制电路的示例的配置的框图。

10.图4是图示出根据图2中所图示出的半导体器件中所包括的熔丝数据生成电路的示例的配置的框图。

11.图5是图示出根据图2中所图示出的半导体器件中所包括的标志生成电路的示例的配置的框图。

12.图6是图示出根据图2中所图示出的半导体器件中所包括的修复控制电路的示例

的配置的框图。

13.图7是图示出根据图2中所图示出的半导体器件中所包括的熔丝数据生成电路的另一个示例的配置的图。

14.图8和图9是图示出包括图7中所图示出的熔丝数据生成电路的半导体器件的操作的图。

15.图10是根据图5中图示出的标志生成电路中所包括的存储体资源标志生成电路的示例的电路图。

16.图11是图示出图10中所图示的存储体资源标志生成电路的操作的表格。

17.图12是图示出包括图7中所图示出的熔丝数据生成电路和图10中所图示的存储体资源标志生成电路的半导体器件的操作的时序图。

18.图13是图示出根据图2中所图示出的半导体器件中所包括的熔丝数据生成电路的另一个示例的配置的图。

19.图14是图示出包括图13中所图示出的熔丝数据生成电路的半导体器件的操作的时序图。

20.图15是图示出根据图2中所图示出的半导体器件中所包括的熔丝数据生成电路的另一个示例的配置的图。

21.图16是图示出包括图15中所图示出的熔丝数据生成电路的半导体器件的操作的时序图。

22.图17是图示出根据图2中所图示出的半导体器件中所包括的熔丝数据生成电路的另一个示例的配置的图。

23.图18是图示出包括图17中所图示出的熔丝数据生成电路的半导体器件的操作的时序图。

24.图19是图示出根据图2中所图示出的半导体器件中所包括的熔丝数据生成电路的另一个示例的配置的图。

25.图20是图示出包括图19中所图示出的熔丝数据生成电路的半导体器件的操作的时序图。

具体实施方式

26.在实施例的以下描述中,当参数被称为是“预先确定的”时,则可以旨在意味着:当在处理或算法中使用参数时,参数的值被提前确定。参数的值可以在处理或算法开始时被设置,或者可以在处理或算法被执行的时段期间被设置。

27.将理解的是,尽管在本文使用术语“第一”、“第二”、“第三”等等来描述各个要素,但这些要素不应当被这些术语所限制。这些术语仅用于将一个要素与另一个要素相区别,并且并不旨在暗示要素的顺序或数量。因此,在一些实施例中的第一要素可以在其他的实施例中被叫作第二要素,而不背离本公开的教导。

28.此外,当要素被称为“连接到”或“耦接到”另一个要素时,其能够直接地连接或耦接到另一要素,或者可以存在居间的要素。相比之下,当要素被称为“直接地连接”或“直接地耦接”到另一个要素时,不存在居间的要素。

29.逻辑“高”电平和逻辑“低”电平可以用于描述电信号的逻辑电平。具有逻辑“高”电

平的信号可以与具有逻辑“低”电平的信号相区分。例如,当具有第一电压的信号对应于具有逻辑“高”电平的信号时,具有第二电压的信号对应于具有逻辑“低”电平的信号。在实施例中,逻辑“高”电平可以被设置为比逻辑“低”电平的电压电平高的电压电平。而且,根据实施例,信号的逻辑电平可以被设置为不同或相反。例如,在一个实施例中具有逻辑“高”电平的某信号可以在另一个实施例中被设置为具有逻辑“低”电平。

30.在下文中,将参考附图详细描述本公开的各个实施例。然而,在本文描述的实施例仅仅是为了说明性目的并且并不旨在限制本公开的保护范围。

31.图1是图示出根据本公开的实施例的半导体系统1的配置的图。如图1所图示的,半导体系统1可以包括控制器(mc)11和半导体器件13。控制器11可以包括第一控制引脚11_1、第二控制引脚11_3以及第三控制引脚11_5。半导体器件13可以包括第一器件引脚13_1、第二器件引脚13_3以及第三器件引脚13_5。控制器11可以通过连接在第一控制引脚11_1与第一器件引脚13_1之间的第一传输线12_1来向半导体器件13传送命令cmd。第一控制引脚11_1、第一传输线12_1以及第一器件引脚13_1均可以根据命令cmd的比特位的数量而以复数个来实施。控制器11可以通过连接在第二控制引脚11_3与第二器件引脚13_3之间的第二传输线12_3来向半导体器件13传送地址add。第二控制引脚11_3、第二传输线12_3以及第二器件引脚13_3均可以根据地址add的比特位的数量而以复数个来实施。控制器11可以通过连接在第三控制引脚11_5与第三器件引脚13_5之间的第三传输线12_5来向半导体器件13传送电源电压vdd。

32.半导体器件13可以从控制器11接收命令cmd、地址add以及电源电压vdd。半导体器件13可以包括熔丝组选择控制电路(fs cnt)113,该熔丝组选择控制电路(fs cnt)113在基于电源电压vdd来执行启动操作时生成熔丝组选择信号(图2的fs_sel),用于逐个顺序地选择由多个存储体(未示出)共用的多个熔丝组(图4的fs1~fsn)。存储体指的是在半导体器件13中的包括了针对读操作和写操作由存储体地址(未示出)进行存取的单元阵列的区域。多个存储体的每一个可以共用多个熔丝组(图4的fs1~fsn),以便在修复操作中利用对应的冗余单元来代替通过故障地址进行存取的故障单元阵列。根据实施例,多个熔丝组(图4的fs1~fsn)的每一个可以由具有不同于存储体的区域集合的单元阵列来共用。半导体器件13可以包括由多个存储体共用的熔丝组(图4的fs1~fsn),并且可以包括熔丝数据生成电路(fd gen)115,该熔丝数据生成电路(fd gen)115从基于熔丝选择信号(图2的fs_sel)所选择的熔丝组来生成存储体熔丝数据(图2的bfd)和使用熔丝数据(图2的ufd)。半导体器件13可以包括标志生成电路(flag gen)117,该标志生成电路(flag gen)117基于存储体熔丝数据(图2的bfd)和使用熔丝数据(图2的ufd)来生成存储体资源标志(图2的brsf),该存储体资源标志(图2的brsf)包括关于对于每个存储体是否能够执行修复操作的信息。半导体器件13可以包括修复控制电路(ppr cnt)119,该修复控制电路(ppr cnt)119在修复操作被执行时基于存储体资源标志(图2的brsf)来控制对存储体的修复操作。

33.图2是图示出根据图1中所图示出的半导体系统1中所包括的半导体器件13的示例的半导体器件13a的配置的框图。

34.半导体器件13a可以包括启动脉冲生成电路(bup gen)110、命令解码器(cmd dec)111、内部地址生成电路(iadd gen)112、熔丝组选择控制电路(fs cnt)113、熔丝数据生成电路(fd gen)115、标志生成电路(flag gen)117以及修复控制电路(ppr cnt)119。

35.启动脉冲生成电路110可以基于电源电压vdd来生成启动脉冲bup。启动脉冲生成电路110可以在基于电源电压vdd设置的加电时段完成之后生成用于执行启动操作的启动脉冲bup。加电时段可以被设置为从施加电源电压vdd的时间点到电源电压vdd上升到预设电平的时间点的时段。可以执行启动操作以从熔丝数据生成电路115中所包括的多个熔丝组(图4的fs1至fsn)来生成存储体熔丝数据bfd和使用熔丝数据ufd。

36.命令解码器111可以基于命令cmd来生成内部命令icmd。命令解码器111可以解码命令cmd以生成内部命令icmd用于执行半导体器件13a的内部操作。在该实施例中,半导体器件13a的内部操作可以被设置为用于对存储体(未示出)中所包括的单元阵列进行存取的激活操作,但是根据实施例也可以被设置为另一个内部操作。

37.内部地址生成电路112可以基于地址add来生成内部地址iadd。内部地址生成电路112可以解码地址add以生成包括关于用于修复操作的故障单元阵列的地址信息的内部地址iadd。关于故障单元阵列的地址信息可以包括用于对包括故障单元阵列的存储体进行存取的存储体地址以及用于对故障单元阵列进行存取的地址。

38.熔丝组选择控制电路113可以从启动脉冲生成电路110接收启动脉冲bup。熔丝组选择控制电路113可以在基于启动脉冲bup执行启动操作时生成选择时钟sclk,并且可以同步于选择时钟sclk而生成熔丝组选择信号fs_sel,用于逐个顺序地选择由多个存储体(未示出)共用的多个熔丝组(图4的fs1~fsn)之一。例如,当两个存储体(未示出)共用三个熔丝组(图7的fs1~fs3)时,熔丝组选择控制电路113可以生成具有第一逻辑位组的熔丝组选择信号fs_sel以便选择第一熔丝组fs1、可以生成具有第二逻辑位组的熔丝组选择信号fs_sel以便选择第二熔丝组fs2,以及可以生成具有第三逻辑位组的熔丝组选择信号fs_sel以便选择第三熔丝组fs3。根据熔丝组选择信号fs_sel中所包括的各个比特位的逻辑电平的组合,第一至第三逻辑位组中的每一个可以根据实施例以各种方式来被设置。熔丝组选择控制电路113可以将选择时钟sclk延迟以生成延迟选择时钟sclkd。熔丝组选择控制电路113可以将选择时钟sclk延迟,使得延迟选择时钟sclkd在由熔丝数据生成电路115生成存储体熔丝数据bfd和使用熔丝数据ufd之后被生成。

39.熔丝数据生成电路115可以从熔丝组选择控制电路113接收熔丝组选择信号fs_sel。熔丝数据生成电路115可以包括多个熔丝组(图4的fs1~fsn),并且可以从多个熔丝组(图4的fs1~fsn)之中的基于熔丝组选择信号fs_sel所选择的熔丝组来生成存储体熔丝数据bfd和使用熔丝数据ufd。存储体熔丝数据bfd的逻辑电平可以根据基于熔丝组选择信号fs_sel所选择的熔丝组中所包括的存储体熔丝(图4的bf)中的至少一个是否被切断来确定。使用熔丝数据ufd的逻辑电平可以根据基于熔丝组选择信号fs_sel所选择的熔丝组中所包括的使用熔丝(图4的uf)是否被切断来确定。

40.标志生成电路117可以从熔丝组选择控制电路113接收延迟选择时钟sclkd,并且可以从熔丝数据生成电路115接收存储体熔丝数据bfd和使用熔丝数据ufd。标志生成电路117可以基于延迟选择时钟sclkd而从存储体熔丝数据bfd和使用熔丝数据ufd中提取关于已经被执行了修复操作的存储体的信息和关于未使用的熔丝组的信息,并且可以基于所提取的信息来生成包括关于对于每个存储体是否能够执行修复操作的信息的存储体资源标志brsf。

41.修复控制电路119可以从命令解码器111接收内部命令icmd、可以从内部地址生成

电路112接收内部地址iadd,并且可以从标志生成电路117接收存储体资源标志brsf。修复控制电路119可以基于模式信号md和内部命令icmd而在执行修复操作时从内部地址iadd中提取关于包括故障单元阵列的存储体的信息,并且可以基于存储体资源标志brsf来控制针对包括故障单元阵列的存储体的修复操作。模式信号md是针对修复操作而被激活的信号,并且可以被从外部施加到半导体器件13a或被在半导体器件13a内部生成。模式信号md可以被设置为通过模式寄存器设置操作设置的信号。修复控制电路119可以在基于存储体资源标志brsf而对包括故障单元阵列的存储体执行修复操作时来执行断裂操作,该断裂操作将关于用于对故障单元阵列进行存取的地址的信息存储在熔丝组中。可以通过将熔丝组中所包括的多个地址熔丝中的每一个(图4的af)电切断来执行断裂操作。

42.图3是图示出根据图2中所图示出的半导体器件13a中所包括的熔丝组选择控制电路113的示例的配置的框图。如在图3中所图示的,熔丝组选择控制电路113可以包括启动时段信号生成电路(bpd gen)121、选择时钟生成电路(sclk gen)123、时钟计数器(clk cnt)125以及时钟延迟单元(clk dly)127。

43.启动时段信号生成电路121可以从启动脉冲生成电路110接收启动脉冲bup,并且可以从时钟计数器125接收启动结束信号。启动时段信号生成电路121可以基于启动脉冲bup和启动结束信号bend来生成在执行启动操作期间被激活的启动时段信号bpd。启动时段信号生成电路121可以生成在启动脉冲bup被生成时被激活的所述启动时段信号bpd。启动时段信号生成电路121可以生成在启动结束信号bend被激活时被去激活的所述启动时段信号bpd。

44.选择时钟生成电路123可以从启动时段信号生成电路121接收启动时段信号bpd。选择时钟生成电路123可以基于启动时段信号bpd来生成选择时钟sclk。选择时钟生成电路123可以在执行激活启动时段信号bpd的启动操作期间生成选择时钟。

45.时钟计数器125可以从选择时钟生成电路123接收选择时钟sclk。时钟计数器125可以对选择时钟sclk进行计数以生成逻辑位组顺序地变化的熔丝组选择信号fs_sel。例如,时钟计数器125可以同步于选择时钟sclk的第一上升沿而生成具有第一逻辑位组的所述熔丝组选择信号fs_sel、可以同步于选择时钟sclk的第二上升沿而生成具有第二逻辑位组的所述熔丝组选择信号fs_sel、以及可以同步于选择时钟sclk的第三上升沿而生成具有第三逻辑位组的所述熔丝组选择信号fs_sel。在这里,上升沿可以被定义为从逻辑“低”电平向逻辑“高”电平转换的时间点或时段。当具有预设逻辑位组的熔丝组选择信号fs_sel被生成时,时钟计数器125可以生成启动结束信号bend。例如,时钟计数器125可以生成在具有第四逻辑位组的熔丝组选择信号fs_sel同步于选择时钟sclk的第四上升沿而被生成时被激活的启动结束信号bend。

46.时钟延迟单元127可以从选择时钟生成电路123接收选择时钟sclk。时钟延迟单元127可以通过将选择时钟sclk延迟预设延迟时段来生成延迟选择时钟sclkd。时钟延迟单元127的预设延迟时段可以被设置为以在熔丝数据生成电路115中生成存储体熔丝数据bfd和使用熔丝数据ufd之后生成延迟选择时钟sclkd。

47.图4是图示出根据图2中所图示出的半导体器件13a中所包括的熔丝数据生成电路115的示例的配置的框图。如图4所图示的,熔丝数据生成电路115可以包括由多个存储体(未示出)共用的第一至第n熔丝组fs1~fsn用于修复操作。例如,第一至第n熔丝组fs1~

fsn可以由两个存储体共用来用于修复操作。根据实施例,第一至第n熔丝组fs1~fsn可以由三个或更多存储体共用。熔丝数据生成电路115可以基于熔丝组选择信号fs_sel来顺序地选择第一至第n熔丝组fs1~fsn之一。例如,熔丝数据生成电路115可以在熔丝组选择信号fs_sel具有第一逻辑位组时选择第一熔丝组fs1,并且可以在熔丝组选择信号fs_sel具有一第n逻辑位组时选择第n熔丝组fsn。在这里,

‘

n’可以被设置为2或更大的自然数。第一至第n熔丝组fs1~fsn每一个可以包括多个存储体熔丝bf、多个地址熔丝af以及使用熔丝uf。熔丝数据生成电路115可以从基于熔丝组选择信号fs_sel而从第一至第n熔丝组fs1~fsn中选择的一个熔丝组来生成存储体熔丝数据bfd和使用熔丝数据ufd。熔丝数据生成电路115可以根据基于熔丝组选择信号fs_sel所选择的熔丝组中所包括的存储体熔丝bf中的至少一个是否被切断来生成存储体熔丝数据bfd。存储体熔丝数据bfd可以包括关于通过熔丝组选择信号fs_sel所选择的熔丝组被用在了哪个存储体用于修复操作的信息。例如,当熔丝组用于第一存储体(未示出)的修复操作时,可以以逻辑“低”电平生成存储体熔丝数据bfd,而当熔丝组用于第二存储体(未示出)的修复操作时,可以以逻辑“高”电平生成存储体熔丝数据bfd。熔丝数据生成电路115可以根据基于熔丝组选择信号fs_sel所选择的熔丝组中所包括的使用熔丝uf是否被切断来生成使用熔丝数据ufd。使用熔丝数据ufd可以包括关于通过熔丝组选择信号fs_sel所选择的熔丝组是否用在了对共用该熔丝组的存储体的修复操作中的信息。例如,当所选择的熔丝组未用于第一存储体(未示出)或第二存储体(未示出)的修复操作时,可以以逻辑“低”电平生成使用熔丝数据ufd,并且当所选择的熔丝组用于第一存储体或第二存储体的修复操作时,可以以逻辑“高”电平生成使用熔丝数据ufd。第一至第n熔丝组fs1~fsn每一个中所包括的每一个地址熔丝af可以存储关于用于对故障单元阵列进行存取的地址(在下文,被称为“故障单元地址”)的信息。在该实施例中,尽管第一至第n熔丝组fs1~fsn被设置为由多个存储体共用以用于修复操作,但根据实施例,第一至第n熔丝组fs1~fsn可以被设置为由具有各区域的单元阵列共用。

48.图5是图示出根据图2中所图示出的半导体器件13a中所包括的标志生成电路117的示例的配置的框图。如图5中所图示的,标志生成电路117可以包括存储体脉冲生成电路(bpul)131、存储体锁存信号生成电路(blat gen)133、资源脉冲生成电路(rpul gen)135、脉冲计数器(pul cnt)137、资源标志生成电路(rsf gen)138以及存储体资源标志生成电路(brsf gen)139。

49.存储体脉冲生成电路131可以接收使用熔丝数据ufd、存储体熔丝数据bfd以及延迟选择时钟sclkd以生成存储体脉冲bpul。存储体脉冲生成电路131可以从延迟选择时钟sclkd生成与基于使用熔丝数据ufd和存储体熔丝数据bfd被执行修复操作的存储体相对应的存储体脉冲bpul。例如,当其中生成了使用熔丝数据ufd和存储体熔丝数据bfd的熔丝组用在了对第一存储体(未示出)的修复操作中时,存储体脉冲生成电路131可以将延迟选择时钟sclkd输出作为与第一存储体相对应的存储体脉冲bpul的第一比特位bpul《1》。对于另一个示例,当其中生成了使用熔丝数据ufd和存储体熔丝数据bfd的熔丝组用在了对第二存储体(未示出)的修复操作中时,存储体脉冲生成电路131可以将延迟选择时钟sclkd输出作为与第二存储体相对应的存储体脉冲bpul的第二比特位bpul《2》。对于另一个示例,当其中生成了使用熔丝数据ufd和存储体熔丝数据bfd的熔丝组未用在对第一存储体或第二存储体的修复操作中时,存储体脉冲生成电路131可以停止生成存储体脉冲bpul。

50.存储体锁存信号生成电路133可以从存储体脉冲生成电路131接收存储体脉冲bpul。存储体锁存信号生成电路133可以基于存储体脉冲bpul来生成与被执行修复操作的存储体相对应的存储体锁存信号blat。例如,当熔丝组用在了对第一存储体的修复操作中并且延迟选择时钟sclkd作为存储体脉冲bpul的第一比特位bpul《1》被输出时,存储体锁存信号生成电路133可以生成被设置为具有逻辑“高”电平的存储体锁存信号blat的第一比特位blat《1》。对于另一个示例,当熔丝组用在了对第二存储体的修复操作中并且延迟选择时钟sclkd作为存储体脉冲bpul的第二比特位bpul《2》被输出时,存储体锁存信号生成电路133可以生成被设置为具有逻辑“高”电平的存储体锁存信号blat的第二比特位blat《2》。

51.资源脉冲生成电路135可以接收使用熔丝数据ufd和延迟选择时钟sclkd以生成资源脉冲rpul。当生成了使用熔丝数据ufd的熔丝组未用在修复操作中时,资源脉冲生成电路135可以输出延迟选择时钟sclkd作为资源脉冲rpul。例如,当因为熔丝组未用在修复操作中而生成被设置为具有逻辑“低”电平的使用熔丝数据ufd时,资源脉冲生成电路135可以输出延迟选择时钟sclkd作为资源脉冲rpul。对于另一个示例,当因为熔丝组已经用在了修复操作中而生成被设置为具有逻辑“高”电平的使用熔丝数据ufd时,资源脉冲生成电路135可以停止生成资源脉冲rpul。

52.脉冲计数器137可以从资源脉冲生成电路135接收资源脉冲rpul。脉冲计数器137可以对资源脉冲rpul进行计数以生成脉冲计数信号pcnt。例如,当因为由存储体共用的熔丝组中的一个熔丝组未用在修复操作中而使资源脉冲rpul出现一次时,脉冲计数器137可以生成被设置为具有第一逻辑位组的脉冲计数信号pcnt。对于另一个示例,当因为由存储体共用的熔丝组中的两个熔丝组未用在修复操作中而使资源脉冲rpul出现两次时,脉冲计数器137可以生成被设置为具有第二逻辑位组的脉冲计数信号pcnt。

53.资源标志生成电路138可以从脉冲计数器137接收脉冲计数信号pcnt。资源标志生成电路138可以基于脉冲计数信号pcnt来生成资源标志rsf,该资源标志rsf包括关于由存储体共用的熔丝组未用在修复操作中出现的次数的信息。例如,当因为由存储体共用的熔丝组中的一个熔丝组未用在修复操作中而生成被设置为具有第一逻辑位组的脉冲计数信号pcnt时,资源标志rsf的第一比特位rsf《1》可以被设置为具有逻辑“高”电平。对于另一个示例,当因为由存储体共用的熔丝组中的两个熔丝组未用在修复操作中而生成被设置为具有第二逻辑位组的脉冲计数信号pcnt时,资源标志rsf的第二比特位rsf《2》可以被设置为具有逻辑“高”电平。

54.存储体资源标志生成电路139可以从存储体锁存信号生成电路133接收存储体锁存信号blat,并且可以从资源标志生成电路138接收资源标志rsf。存储体资源标志生成电路139可以基于存储体锁存信号blat和资源标志rsf来生成存储体资源标志brsf。例如,当由第一存储体和第二存储体共用的熔丝组未用在对第一存储体和第二存储体的修复操作中时,存储体资源标志生成电路139可以生成逻辑位组被设置为使得能够执行对第一存储体和第二存储体的修复操作的存储体资源标志brsf。对于另一个示例,当由第一存储体和第二存储体共用的熔丝组已经用在了对第一存储体的修复操作中并且仅仅剩余一个未使用的熔丝组时,存储体资源标志生成电路139可以生成逻辑位组被设置为使得能够执行对第二存储体的修复操作的存储体资源标志brsf。对于另一个示例,当由第一存储体和第二存储体共用的熔丝组已经用在了对第一存储体的修复操作中并且剩余至少两个未使用的

熔丝组时,存储体资源标志生成电路139可以生成逻辑位组被设置为使得能够执行对第一存储体和第二存储体的修复操作的存储体资源标志brsf。对于另一个示例,当由第一存储体和第二存储体共用的熔丝组已经用在了对第二存储体的修复操作中并且剩余仅仅一个未使用的熔丝组时,存储体资源标志生成电路139可以生成逻辑位组被设置为使得能够执行对第一存储体的修复操作的存储体资源标志brsf。对于另一个示例,当由第一存储体和第二存储体共用的熔丝组用在了对第二存储体的修复操作中并且剩余至少两个未使用的熔丝组时,存储体资源标志生成电路139可以生成逻辑位组被设置为使得能够执行对第一存储体和第二存储体的修复操作的存储体资源标志brsf。对于另一个示例,当在由第一存储体和第二存储体共用的熔丝组中没有未使用的熔丝组剩余时,存储体资源标志生成电路139可以生成逻辑位组被设置为使得不执行对第一存储体和第二存储体的修复操作的存储体资源标志brsf。

55.图6是图示出根据图2中所图示出的半导体器件13a中所包括的修复控制电路119的示例的配置的框图。如图6中所图示的,修复控制电路119可以包括地址提取电路(add ext)141、断裂使能信号生成电路(ren gen)143以及断裂控制电路(rup cnt)145。

56.地址提取电路141可以基于模式信号md、内部命令icmd以及内部地址iadd来生成故障存储体地址fba和故障地址fadd。在模式信号md被激活用于修复操作时,地址提取电路141可以当用于激活操作的内部命令icmd被生成时从内部地址iadd中提取故障存储体地址fba和故障地址fadd。故障存储体地址fba被生成以选择将被执行修复操作的存储体,并且故障地址fadd被生成以对将被执行修复操作的存储体中所包括的故障单元阵列进行存取。

57.断裂使能信号生成电路143可以从地址提取电路141接收故障存储体地址fba。断裂使能信号生成电路143可以基于故障存储体地址fba和存储体资源标志brsf来确定对将被修复的存储体进行修复是否可能,以生成断裂使能信号ren。当对将被执行修复的存储体进行修复为可能时,断裂使能信号ren可以被使能。例如,当根据故障存储体地址fba将执行对第一存储体(未示出)的修复操作时,断裂使能信号生成电路143可以根据存储体资源标志brsf来确定对第一存储体的修复操作是否可能,以针对用于第一存储体的修复操作来生成断裂使能信号ren。

58.断裂控制电路145可以从地址提取电路141接收故障地址fadd,并且可以从断裂使能信号生成电路143接收断裂使能信号ren。当断裂使能信号ren(其通过确定对将被修复的存储体修复操作是可能的而被使能)被生成时,断裂控制电路145可以执行将故障地址fadd存储在熔丝组中的断裂操作。根据目前实施例执行的修复操作可以被实施为封装后修复(ppr)中所包括的硬ppr或软ppr。

59.图7是图示出根据图2中所图示出的半导体器件13a中所包括的熔丝数据生成电路115的另一个示例的熔丝数据生成电路115a的配置的图。如图7中所图示的,熔丝数据生成电路115a可以包括针对修复操作由第一存储体(未示出)和第二存储体(未示出)共用的第一至第三熔丝组fs1~fs3。熔丝数据生成电路115a可以基于熔丝组选择信号fs_sel《2:1》来顺序地选择第一至第三熔丝组fs1~fs3之一。例如,熔丝数据生成电路115a可以在具有第一逻辑位组的熔丝组选择信号fs_sel《2:1》被接收时来选择第一熔丝组fs1、可以在具有第二逻辑位组的熔丝组选择信号fs_sel《2:1》被接收时来选择第二熔丝组fs2、以及可以在具有第三逻辑位组的熔丝组选择信号fs_sel《2:1》被接收时来选择第三熔丝组fs3。第一熔

丝组fs1可以包括存储体熔丝bf、多个地址熔丝af以及使用熔丝uf。当基于熔丝组选择信号fs_sel《2:1》而选择第一熔丝组fs1时,熔丝数据生成电路115a可以生成各自具有根据第一熔丝组fs1中所包括的存储体熔丝bf和使用熔丝uf各自是否被切断所确定的逻辑电平的存储体熔丝数据bfd和使用熔丝数据ufd。当第一熔丝组fs1被选择时,熔丝数据生成电路115a可以基于未切断的存储体熔丝bf来生成逻辑“低”电平的存储体熔丝数据bfd,并且可以基于未切断的使用熔丝uf来生成逻辑“低”电平的使用熔丝数据ufd。通过由熔丝数据生成电路115a生成的逻辑“低”电平的使用熔丝数据ufd,可以确认第一熔丝组fs1未用在第一存储体和第二存储体的修复操作中。第二熔丝组fs2可以包括存储体熔丝bf、多个地址熔丝af以及使用熔丝uf。当基于熔丝组选择信号fs_sel《2:1》而选择第二熔丝组fs2时,熔丝数据生成电路115a可以生成各自具有根据第二熔丝组fs2中所包括的存储体熔丝bf和使用熔丝uf各自是否被切断所确定的逻辑电平的存储体熔丝数据bfd和使用熔丝数据ufd。当第二熔丝组fs2被选择时,熔丝数据生成电路115a可以基于未切断的存储体熔丝bf来生成逻辑“低”电平的存储体熔丝数据bfd,并且可以基于未切断的使用熔丝uf来生成逻辑“低”电平的使用熔丝数据ufd。通过由熔丝数据生成电路115a生成的逻辑“低”电平的使用熔丝数据ufd,可以确认第二熔丝组fs2未用在第一存储体和第二存储体的修复操作中。第三熔丝组fs3可以包括存储体熔丝bf、多个地址熔丝af以及使用熔丝uf。当基于熔丝组选择信号fs_sel《2:1》而选择第三熔丝组fs3时,熔丝数据生成电路115a可以生成各自具有根据第三熔丝组fs3中所包括的存储体熔丝bf和使用熔丝uf各自是否被切断所确定的逻辑电平的存储体熔丝数据bfd和使用熔丝数据ufd。当第三熔丝组fs3被选择时,熔丝数据生成电路115a可以基于被切断的存储体熔丝bf来生成逻辑“高”电平的存储体熔丝数据bfd,并且可以基于被切断的使用熔丝uf来生成逻辑“高”电平的使用熔丝数据ufd。在图中,通过圆圈来指示被切断熔丝。通过由熔丝数据生成电路115a生成的逻辑“高”电平的存储体熔丝数据bfd和逻辑“高”电平的使用熔丝数据ufd,可以确认第三熔丝组fs3已经用于第二存储体的修复操作。

60.图8和图9是图示出包括图7中所图示出的熔丝数据生成电路115a的半导体器件13a的操作的图。

61.如图8中所图示出的,当熔丝组选择信号fs_sel《2:1》具有第一逻辑位组

‘

01’时,可以选择第一熔丝组fs1。当熔丝组选择信号fs_sel《2:1》具有第一逻辑位组

‘

01’时,可以意指:熔丝组选择信号的第二比特位fs_sel《2》具有逻辑“低”电平,并且熔丝组选择信号的第一比特位fs_sel《1》具有逻辑“高”电平。因为图7中示出的第一熔丝组fs1中所包括的存储体熔丝bf未被切断,所以可以以逻辑“低”电平生成存储体熔丝数据bfd,并且因为第一熔丝组fs1中所包括的使用熔丝uf未被切断,所以可以以逻辑“低”电平生成使用熔丝数据ufd。

62.如图9中所图示的,当以逻辑“低”电平生成存储体熔丝数据bfd时,可以以逻辑“高”电平生成存储体锁存信号blat的与第一存储体(未示出)相对应的第一比特位blat《1》,并且可以以逻辑“低”电平生成存储体锁存信号blat的与第二存储体(未示出)相对应的第二比特位blat《2》。当使用熔丝数据ufd第一次以逻辑“低”电平生成时,可以以逻辑“高”电平生成资源标志rsf的第一比特位rsf《1》,并且可以以逻辑“低”电平生成资源标志rsf的第二比特位rsf《2》。

63.如图8中所图示出的,当熔丝选择信号fs_sel《2:1》具有第二逻辑位组

‘

10’时,可

以选择第二熔丝组fs2。当熔丝组选择信号fs_sel《2:1》具有逻辑位组

‘

10’时,可以意指:熔丝组选择信号的第二比特位fs_sel《2》具有逻辑“高”电平,并且熔丝组选择信号的第一比特位fs_sel《1》具有逻辑“低”电平。因为图7中示出的第二熔丝组fs2中所包括的存储体熔丝bf未被切断,所以可以以逻辑“低”电平生成存储体熔丝数据bfd,并且因为第二熔丝组fs2中所包括的使用熔丝uf未被切断,所以可以以逻辑“低”电平生成使用熔丝数据ufd。

64.如图9中所图示的,当以逻辑“低”电平生成存储体熔丝数据bfd时,存储体锁存信号blat的与第一存储体(未示出)相对应的第一比特位blat《1》可以维持逻辑“高”电平,并且存储体锁存信号blat的与第二存储体(未示出)相对应的第二比特位blat《2》可以维持逻辑“低”电平。当使用熔丝数据ufd第二次以逻辑“低”电平生成时,可以以逻辑“高”电平生成资源标志rsf的第一比特位rsf《1》和资源标志rsf的第二比特位rsf《2》两者。

65.如图8中所图示出的,当熔丝选择信号fs_sel《2:1》具有第三逻辑位组

‘

11’时,可以选择第三熔丝组fs3。当熔丝组选择信号fs_sel《2:1》具有第三逻辑位组

‘

11’时,可以意指:熔丝组选择信号的第二比特位fs_sel《2》具有逻辑“高”电平,并且熔丝组选择信号的第一比特位fs_sel《1》具有逻辑“高”电平。因为图7中示出的第三熔丝组fs3中所包括的存储体熔丝bf被切断,所以可以以逻辑“高”电平生成存储体熔丝数据bfd,并且因为第三熔丝组fs3中所包括的使用熔丝uf被切断,所以可以以逻辑“高”电平生成使用熔丝数据ufd。

66.如图9中所图示的,当以逻辑“高”电平生成存储体熔丝数据bfd时,存储体锁存信号blat的与第一存储体(未示出)相对应的第一比特位blat《1》可以维持逻辑“高”电平,并且可以以逻辑“高”电平生成存储体锁存信号blat的与第二存储体(未示出)相对应的第二比特位blat《2》。当以逻辑“高”电平生成使用熔丝数据ufd时,资源标志rsf的第一比特位rsf《1》和资源标志rsf的第二比特位rsf《2》可以维持先前设置的逻辑电平。

67.图10是根据图5中图示出的标志生成电路117中所包括的存储体资源标志生成电路139的示例的电路图。如图10所图示的,存储体资源标志生成电路139可以包括与门151和155,以及或门153和157。与门151可以接收资源标志rsf的第一比特位rsf《1》和存储体锁存信号blat的第二比特位blat《2》,以对资源标志rsf的第一比特位rsf《1》和存储体锁存信号blat的第二比特位blat《2》执行逻辑与运算。或门153可以接收资源标志rsf的第二比特位rsf《2》和与门151的输出信号,并且对资源标志rsf的第二比特位rsf《2》和与门151的输出信号执行逻辑或运算以生成存储体资源标志brsf的第一比特位brsf《1》。与门155可以接收资源标志rsf的第一比特位rsf《1》和存储体锁存信号blat的第一比特位blat《1》,以对资源标志rsf的第一比特位rsf《1》和存储体锁存信号blat的第一比特位blat《1》执行逻辑与运算。或门157可以接收资源标志rsf的第二比特位rsf《2》和与门155的输出信号,并且对资源标志rsf的第二比特位rsff《2》和与门155的输出信号执行逻辑或运算,以生成存储体资源标志brsf的第二比特位brsf《2》。

68.图11是图示出图10中所图示的存储体资源标志生成电路139的操作的表格。

69.如图11的第一行中所图示的,通过当在顺序地选择的熔丝组中在第一存储体(未示出)和第二存储体(未示出)的修复操作方面包括至少两个未使用的熔丝组时被设置为具有逻辑“高”电平的资源标志rsf的第二比特位rsf《2》,存储体资源标志生成电路139可以生成全部都被设置为具有逻辑“高”电平的存储体资源标志brsf的第一比特位brsf《1》和存储体资源标志brsf的第二比特位brsf《2》。通过全部都被设置为逻辑“高”电平的存储体资源

标志brsf的第一比特位brsf《1》和存储体资源标志brsf的第二比特位brsf《2》,未使用的熔丝组可以用于第一存储体或第二存储体的修复操作。

70.如图11的第二行中所图示的,当在被顺序地选择的熔丝组中在第一存储体和第二存储体的修复操作方面包括一个未使用的熔丝组时,存储体资源标志生成电路139可以生成被设置为具有逻辑“低”电平的资源标志rsf的第二比特位rsf《2》和被设置为具有逻辑“高”电平的资源标志rsf的第一比特位rsf《1》,并且当确认已经执行了对第二存储体的修复操作时,存储体资源标志生成电路139可以生成被设置为具有逻辑“高”电平的存储体锁存信号blat的第二比特位blat《2》和具有逻辑“低”电平的存储体锁存信号blat的第一比特位blat《1》。通过被设置为具有逻辑“高”电平的资源标志rsf的第一比特位rsf《1》、被设置为具有逻辑“高”电平的存储体锁存信号blat的第二比特位blat《2》、被设置为具有逻辑“低”电平的存储体锁存信号blat的第一比特位blat《1》以及被设置为具有逻辑“低”电平的资源标志rsf的第二比特位rsf《2》来生成被设置为具有逻辑“高”电平的存储体资源标志brsf的第一比特位brsf《1》和被设置为具有逻辑“低”电平的存储体资源标志brsf的第二比特位brsf《2》。根据被设置为具有逻辑“高”电平的存储体资源标志brsf的第一比特位brsf《1》,未使用的熔丝组可以被用在尚未被执行修复操作的第一存储体的修复操作中。

71.如图11的第三行中所图示的,当顺序地选择的熔丝组中包括一个未用在第一存储体和第二存储体的修复操作中的熔丝组时,存储体资源标志生成电路139可以生成被设置为具有逻辑“低”电平的资源标志rsf的第二比特位rsf《2》和被设置为具有逻辑“高”电平的资源标志rsf的第一比特位rsf《1》,并且当确认已经执行了对第一存储体的修复操作时,存储体资源标志生成电路139可以生成被设置为具有逻辑“高”电平的存储体锁存信号blat的第一比特位blat《1》和被设置为具有逻辑“低”电平的存储体锁存信号blat的第二比特位blat《2》。可以通过被设置为具有逻辑“高”电平的资源标志rsf的第一比特位rsf《1》、被设置为具有逻辑“高”电平的存储体锁存信号blat的第一比特位blat《1》、被设置为具有逻辑“低”电平的存储体锁存信号blat的第二比特位blat《2》以及被设置为具有逻辑“低”电平的资源标志rsf的第二比特位rsf《2》来生成被设置为具有逻辑“低”电平的存储体资源标志brsf的第一比特位brsf《1》和被设置为具有逻辑“高”电平的存储体资源标志brsf的第二比特位brsf《2》。通过被设置为具有逻辑“高”电平的存储体资源标志brsf的第二比特位brsf《2》,未使用的熔丝组可以用于尚未被执行修复操作的第二存储体的修复操作。

72.如图11的第四行中所图示出的,当在顺序地选择的熔丝组中包括一个未用在第一存储体和第二存储体的修复操作中的熔丝组时,存储体资源标志生成电路139可以生成被设置为具有逻辑“低”电平的资源标志rsf的第二比特位rsf《2》和被设置为具有逻辑“高”电平的资源标志rsf的第一比特位rsf《1》,并且当确认已经执行了对第一存储体和第二存储体的修复操作时,存储体资源标志生成电路139可以生成两者都被设置为逻辑“高”的存储体锁存信号blat的第一比特位blat《1》和存储体锁存信号blat的第二比特位blat《2》。可以通过被设置为具有逻辑“高”电平的资源标志rsf的第一比特位rsf《1》、两者都被设置为具有逻辑“高”的存储体锁存信号blat的第一比特位blat《1》和存储体锁存信号blat的第二比特位blat《2》来生成两者都被设置为具有逻辑“高”电平的存储体资源标志brsf的第一比特位brsf《1》和存储体资源标志brsf的第二比特位brsf《2》。通过两者都被设置为具有逻辑“高”电平的存储体资源标志brsf的第一比特位brsf《1》和存储体资源标志brsf的第二比特

位brsf《2》,未使用的熔丝组可以用在第一存储体或第二存储体的修复操作中。

73.如图11的第五行中所图示出的,当在顺序地选择的熔丝组中不存在未用在第一存储体和第二存储体的修复操作中的熔丝组时,存储体资源标志生成电路139可以生成全部被设置为具有逻辑“低”电平的资源标志rsf的第二比特位rsf《2》和资源标志rsf的第一比特位rsf《1》。因为不存在未使用的熔丝组来用于修复操作,所以不执行第一存储体或第二存储体的修复操作。

74.图12是图示出包括图7中所图示出的熔丝数据生成电路115a和图10中所图示的存储体资源标志生成电路139的半导体器件13a的操作的时序图。

75.参考图12,当在时间点t111生成启动脉冲bup用于启动操作时,可以以逻辑“高”电平使能启动时段信号bpd,使得可以执行启动操作,并且在执行启动操作的时间期间可以生成选择时钟sclk。熔丝选择信号fs_sel《2:1》的逻辑位组可以同步于选择时钟sclk的上升沿而顺序地改变。更具体地,在时间点t113,熔丝选择信号fs_sel《2:1》可以同步于选择时钟sclk的第一上升沿而被设置为具有第一逻辑位组

‘

01’,在时间点t115,熔丝选择信号fs_sel《2:1》可以同步于选择时钟sclk的第二上升沿而被设置为具有第二逻辑位组

‘

10’,在时间点t117,熔丝选择信号fs_sel《2:1》可以同步于选择时钟sclk的第三上升沿而被设置为具有第三逻辑位组

‘

11’,并且在时间点t119,熔丝选择信号ffs_sel《2:1》可以同步于选择时钟sclk的第四上升沿而被设置为具有第四逻辑位组

‘

00’。

76.如图7和图12中所图示的,在从时间点t113到时间点t115的时段期间,熔丝数据生成电路115a可以接收被设置为具有第一逻辑位组

‘

01’的熔丝选择信号fs_sel《2:1》以选择第一熔丝组fs1,并且可以根据未切断的存储体熔丝bf和未切断的使用熔丝uf两者来生成两者都被设置为具有逻辑“低”电平的存储体熔丝数据bfd和使用熔丝数据ufd。在从时间点t115到时间点t117的时段的期间,熔丝数据生成电路115a可以接收被设置为具有第二逻辑位组

‘

10’的熔丝选择信号fs_sel《2:1》以选择第二熔丝组fs2,并且可以根据未切断的存储体熔丝bf和未切断的使用熔丝uf两者来生成两者都被设置为具有逻辑“低”电平的存储体熔丝数据bfd和使用熔丝数据ufd。在从时间点t117到时间点t119的时段期间,熔丝数据生成电路115a可以接收被设置为具有第三逻辑位组

‘

11’的熔丝选择信号fs_sel《2:1》以选择第三熔丝组fs3,并且可以根据被切断的存储体熔丝bf和被切断的使用熔丝uf两者来生成两者都被设置为具有逻辑“高”电平的存储体熔丝数据bfd和使用熔丝数据ufd。在时间点t119之后,当启动结束信号bend根据被设置为具有第四逻辑位组

‘

00’的熔丝选择信号fs_sel而被激活时,启动时段信号bpd可以以逻辑“低”电平被禁止以结束启动操作。

77.如图12中所图示的,在从时间点t113到时间点t117的时段期间,使用熔丝数据ufd维持逻辑“低”电平,使得通过将选择时钟sclk延迟一延迟时段所生成的延迟选择时钟sclkd可以作为资源脉冲rpul被输出。同步于资源脉冲rpul的第一上升沿,脉冲计数信号pcnt的第一比特位pcnt《1》可以从逻辑“低”电平转换为逻辑“高”电平。同步于脉冲计数信号pcnt的第一比特位pcnt《1》的上升沿,资源标志rsf的第一比特位rsf《1》可以从逻辑“低”电平转换为逻辑“高”电平。同步于资源脉冲rpul的第二上升沿,脉冲计数信号pcnt的第一比特位pcnt《1》可以从逻辑“高”电平转换为逻辑“低”电平,并且脉冲计数信号pcnt的第二比特位pcnt《2》可以从逻辑“低”电平转换为逻辑“高”电平。同步于脉冲计数信号pcnt的第二比特位pcnt《2》的上升沿,资源标志rsf的第二比特位rsf《2》可以从逻辑“低”电平转换为

逻辑“高”电平。

78.如图12中所图示的,在时间点t117之后,以逻辑“高”电平生成使用熔丝数据ufd,但是资源标志rsf的第二比特位rsf《2》维持逻辑“高”电平,使得通过图10中所图示的存储体资源标志生成电路139所生成的存储体资源标志brsf《2:1》的逻辑位组可以被设置为

‘

11’。当存储体资源标志brsf《2:1》的逻辑位组是

‘

11’时,可以意指:存储体资源标志brsf的第二比特位brsf《2》具有逻辑“高”电平,并且存储体资源标志brsf的第一比特位brsf《1》具有逻辑“高”电平。当在启动操作完成之后执行修复操作时,存储体资源标志brsf《2:1》的逻辑位组被设置为

‘

11’,使得可以对第一存储体(未示出)和第二存储体(未示出)执行修复操作。更具体地,在图7中所图示出的熔丝数据生成电路115a的情况下,因为第一熔丝组fs1和第二熔丝组fs2未使用,所以在启动操作中可以确认对第一存储体和第二存储体的修复操作可以使用未使用的第一熔丝组fs1和第二熔丝组fs2来执行。

79.图13是图示出根据图2中所图示出的半导体器件13a中所包括的熔丝数据生成电路115的另一个示例的熔丝数据生成电路115b的配置的图。如图13中所图示的,熔丝数据生成电路115b可以包括针对修复操作由第一存储体(未示出)和第二存储体(未示出)共用的第一至第三熔丝组fs1~fs3。熔丝数据生成电路115b可以基于熔丝组选择信号fs_sel《2:1》来顺序地选择第一至第三熔丝组fs1~fs3之一。当基于熔丝组选择信号fs_sel《2:1》而选择第一熔丝组fs1时,熔丝数据生成电路115b可以基于未切断的存储体熔丝bf来生成逻辑“低”电平的存储体熔丝数据bfd,并且可以基于未切断的使用熔丝uf来生成逻辑“低”电平的使用熔丝数据ufd。当基于熔丝组选择信号fs_sel《2:1》而选择第二熔丝组fs2时,熔丝数据生成电路115b可以基于被切断的存储体熔丝bf来生成逻辑“高”电平的存储体熔丝数据bfd,并且基于被切断的使用熔丝uf来生成逻辑“高”电平的使用熔丝数据ufd。当基于熔丝组选择信号fs_sel《2:1》而选择第三熔丝组fs3时,熔丝数据生成电路115b可以基于被切断的存储体熔丝bf来生成逻辑“高”电平的存储体熔丝数据bfd,并且可以基于被切断的使用熔丝uf来生成逻辑“高”电平的使用熔丝数据ufd。

80.图14是图示出包括图13中图示出的熔丝数据生成电路115b的半导体器件13a的操作的时序图。

81.参考图13和图14,当在时间点t121生成启动脉冲bup用于启动操作时,以逻辑“高”电平使能启动时段信号bpd以执行启动操作,并且在执行启动操作时可以生成选择时钟sclk。熔丝选择信号fs_sel《2:1》的逻辑位组可以同步于选择时钟sclk的上升沿而顺序地改变。在从时间点t123到时间点t125的时段期间,熔丝数据生成电路115b可以接收被设置为具有第一逻辑位组

‘

01’的熔丝选择信号fs_sel《2:1》以选择第一熔丝组fs1,并且可以根据未切断的存储体熔丝bf和未切断的使用熔丝uf两者来生成两者都被设置为具有逻辑“低”电平的存储体熔丝数据bfd和使用熔丝数据ufd。在从时间点t125到时间点t127的时段期间,熔丝数据生成电路115b可以接收被设置为具有第二逻辑位组

‘

10’的熔丝选择信号fs_sel《2:1》以选择第二熔丝组fs2,并且可以根据被切断的存储体熔丝bf和被切断的使用熔丝uf两者来生成两者都被设置为逻辑“高”电平的存储体熔丝数据bfd和使用熔丝数据ufd。在从时间点t127到时间点t129的时段期间,熔丝数据生成电路115b可以接收被设置为具有第三逻辑位组

‘

11’的熔丝选择信号fs_sel《2:1》以选择第三熔丝组fs3,并且可以根据被切断的存储体熔丝bf和被切断的使用熔丝uf两者来生成两者都被设置为逻辑“高”电平

的存储体熔丝数据bfd和使用熔丝数据ufd。在时间点t129之后,当启动结束信号bend根据被设置为具有第四逻辑位组

‘

00’的熔丝选择信号fs_sel《2:1》而被激活时,启动时段信号bpd可以以逻辑“低”电平被禁止以结束启动操作。

82.如图14中所图示的,在从时间点t123到时间点t125的时段期间,使用熔丝数据ufd维持逻辑“低”电平,使得通过将选择时钟sclk延迟一延迟时段所生成的延迟选择时钟sclkd可以作为资源脉冲rpul被输出。同步于资源脉冲rpul的第一上升沿,脉冲计数信号pcnt的第一比特位pcnt《1》可以从逻辑“低”电平转换为逻辑“高”电平。同步于脉冲计数信号pcnt的第一比特位pcnt《1》的上升沿,资源标志rsf的第一比特位rsf《1》从逻辑“低”电平转换为逻辑“高”电平。

83.如图14中所图示出的,在时间点t125之后,使用熔丝数据ufd和存储体熔丝数据bfd两者以逻辑“高”电平被生成,使得存储体锁存信号blat的第二比特位blat《2》可以从逻辑“低”电平转换为逻辑“高”电平。在资源标志rsf的第一比特位rsf《1》被设置为具有逻辑“高”电平的情况下当存储体锁存信号blat的第二比特位blat《2》被设置为具有逻辑“高”电平时,存储体资源标志brsf《2:1》的逻辑位组可以被设置为

‘

01’。当存储体资源标志brsf《2:1》的逻辑位组是

‘

01’时,可以意指:存储体资源标志brsf的第二比特位brsf《2》具有逻辑“低”电平,并且存储体资源标志brsf的第一比特位brsf《1》具有逻辑“高”电平。当在启动操作完成之后执行修复操作时,存储体资源标志brsf《2:1》的逻辑位组被设置为

‘

01’,使得可以执行对第一存储体(未示出)的修复操作。更具体地,在图13中示出的熔丝数据生成电路115b的情况下,因为第一熔丝组fs1未使用,所以在启动操作中可以确认对第一存储体的修复操作可以使用未使用的第一熔丝组fs1来执行。

84.图15是图示出根据图2中所图示出的半导体器件13a中所包括的熔丝数据生成电路115的另一个示例的熔丝数据生成电路115c的配置的图。如图15中所图示的,熔丝数据生成电路115c可以包括针对修复操作由第一存储体(未示出)和第二存储体(未示出)共用的第一至第三熔丝组fs1~fs3。熔丝数据生成电路115c可以基于熔丝组选择信号fs_sel《2:1》来顺序地选择第一至第三熔丝组fs1~fs3之一。当基于熔丝组选择信号fs_sel《2:1》而选择第一熔丝组fs1时,熔丝数据生成电路115c可以基于未切断的存储体熔丝bf来生成逻辑“低”电平的存储体熔丝数据bfd,并且可以基于未切断的使用熔丝uf来生成逻辑“低”电平的使用熔丝数据ufd。当基于熔丝组选择信号fs_sel《2:1》而选择第二熔丝组fs2时,熔丝数据生成电路115c可以基于未切断的存储体熔丝bf来生成逻辑“低”电平的存储体熔丝数据bfd,并且可以基于被切断的使用熔丝uf来生成逻辑“高”电平的使用熔丝数据ufd。当基于熔丝组选择信号fs_sel《2:1》而选择第三熔丝组fs3时,熔丝数据生成电路115c可以基于未切断的存储体熔丝bf来生成逻辑“低”电平的存储体熔丝数据bfd,并且可以基于被切断的使用熔丝uf来生成逻辑“高”电平的使用熔丝数据ufd。

85.图16是图示出包括图15中图示出的熔丝数据生成电路115c的半导体器件13a的操作的时序图。

86.参考图15和图16,当在时间点t131生成启动脉冲bup用于启动操作时,可以以逻辑“高”电平使能启动时段信号bpd,使得可以执行启动操作,并且在执行启动操作时可以生成选择时钟sclk。熔丝选择信号fs_sel《2:1》的逻辑位组可以同步于选择时钟sclk的上升沿而顺序地改变。在从时间点t133到时间点t135的时段期间,熔丝数据生成电路115c可以接

收被设置为具有第一逻辑位组

‘

01’的熔丝选择信号fs_sel《2:1》以选择第一熔丝组fs1,并且可以根据未切断的存储体熔丝bf和未切断的使用熔丝uf两者来生成两者都被设置为具有逻辑“低”电平的存储体熔丝数据bfd和使用熔丝数据ufd。在从时间点t135到时间点t137的时段期间,熔丝数据生成电路115c可以接收被设置为具有第二逻辑位组

‘

10’的熔丝选择信号fs_sel《2:1》以选择第二熔丝组fs2、可以根据未切断的存储体熔丝bf来生成被设置为逻辑“低”电平的存储体熔丝数据bfd、并且可以根据被切断的使用熔丝uf来生成被设置为逻辑“高”电平的使用熔丝数据ufd。在从时间点t137到时间点t139的时段期间,熔丝数据生成电路115c可以接收被设置为具有第三逻辑位组

‘

11’的熔丝选择信号fs_sel《2:1》以选择第三熔丝组fs3、可以根据未切断的存储体熔丝bf来生成被设置为逻辑“低”电平的存储体熔丝数据bfd、并且可以根据被切断的使用熔丝uf来生成被设置为逻辑“高”电平的使用熔丝数据ufd。在时间点t139之后,当启动结束信号bend根据被设置为具有第四逻辑位组

‘

00’的熔丝选择信号fs_sel《2:1》而被激活时,启动时段信号bpd可以以逻辑“低”电平被禁止以结束启动操作。

87.如图16中所图示的,在从时间点t133到时间点t135的时段期间,使用熔丝数据ufd维持逻辑“低”电平,使得通过将选择时钟sclk延迟一延迟时段所生成的延迟选择时钟sclkd可以作为资源脉冲rpul被输出。同步于资源脉冲rpul的第一上升沿,脉冲计数信号pcnt的第一比特位pcnt《1》可以从逻辑“低”电平转换为逻辑“高”电平。同步于脉冲计数信号pcnt的第一比特位pcnt《1》的上升沿,资源标志rsf的第一比特位rsf《1》从逻辑“低”电平转换为逻辑“高”电平。

88.如图16中所图示的,在时间点t135之后,使用熔丝数据ufd以逻辑“高”电平生成并且存储体熔丝数据bfd以逻辑“低”电平生成,使得存储体锁存信号blat的第一比特位blat《1》可以从逻辑“低”电平转换为逻辑“高”电平。当资源标志rsf的第一比特位rsf《1》被设置为具有逻辑“高”电平并且存储体锁存信号blat的第一比特位blat《1》被设置为具有逻辑“高”电平时,存储体资源标志brsf《2:1》的逻辑位组可以被设置为

‘

10’。当存储体资源标志brsf《2:1》的逻辑位组是

‘

10’时,可以意指:存储体资源标志brsf的第二比特位brsf《2》具有逻辑“高”电平,并且存储体资源标志brsf的第一比特位brsf《1》具有逻辑“低”电平。因为当启动操作完成时存储体资源标志brsf《2:1》的逻辑位组被设置为

‘

10’,所以可以执行对第二存储体(未示出)的修复操作。更具体地,在图15中示出的熔丝数据生成电路115c的情况下,因为第一熔丝组fs1未使用,所以在启动操作中可以确认对第二存储体的修复操作可以使用未使用的第一熔丝组fs1来执行。

89.图17是图示出根据图2中所图示出的半导体器件13a中所包括的熔丝数据生成电路115的另一个示例的熔丝数据生成电路115d的配置的图。

90.如图17中所图示的,熔丝数据生成电路115d可以包括针对修复操作由第一存储体(未示出)和第二存储体(未示出)共用的第一至第三熔丝组fs1~fs3。熔丝数据生成电路115d可以基于熔丝组选择信号fs_sel《2:1》来顺序地选择第一至第三熔丝组fs1~fs3之一。当基于熔丝组选择信号fs_sel《2:1》而选择第一熔丝组fs1时,熔丝数据生成电路115d可以基于未切断的存储体熔丝bf来生成逻辑“低”电平的存储体熔丝数据bfd,并且可以基于未切断的使用熔丝uf来生成逻辑“低”电平的使用熔丝数据ufd。当基于熔丝组选择信号fs_sel《2:1》而选择第二熔丝组fs2时,熔丝数据生成电路115d可以基于未切断的存储体熔

丝bf来生成逻辑“低”电平的存储体熔丝数据bfd,并且可以基于被切断的使用熔丝uf来生成逻辑“高”电平的使用熔丝数据ufd。当基于熔丝组选择信号fs_sel而选择第三熔丝组fs3时,熔丝数据生成电路115d可以基于被切断的存储体熔丝bf来生成逻辑“高”电平的存储体熔丝数据bfd,并且可以基于被切断的使用熔丝uf来生成逻辑“高”电平的使用熔丝数据ufd。

91.图18是图示出包括图17中所图示出的熔丝数据生成电路115d的半导体器件13a的操作的时序图。

92.参考图17和图18,当在时间点t141生成启动脉冲bup用于启动操作时,以逻辑“高”电平使能启动时段信号bpd,使得可以执行启动操作,并且在执行启动操作时可以生成选择时钟sclk。熔丝选择信号fs_sel《2:1》的逻辑位组可以同步于选择时钟sclk的上升沿而顺序地改变。在从时间点t143到时间点t145的时段期间,熔丝数据生成电路115d可以接收被设置为具有第一逻辑位组

‘

01’的熔丝选择信号fs_sel《2:1》以选择第一熔丝组fs1,并且可以根据未切断的存储体熔丝bf和未切断的使用熔丝uf两者来生成两者都被设置为具有逻辑“低”电平的存储体熔丝数据bfd和使用熔丝数据ufd。在从时间点t145到时间点t147的时段期间,熔丝数据生成电路115d可以接收被设置为具有第二逻辑位组

‘

10’的熔丝选择信号fs_sel《2:1》以选择第二熔丝组fs2、可以根据未切断的存储体熔丝bf来生成被设置为具有逻辑“低”电平的存储体熔丝数据bfd、并且可以根据被切断的使用熔丝uf来生成被设置为具有逻辑“高”电平的使用熔丝数据ufd。在从时间点t147到时间点t149的时段期间,熔丝数据生成电路115d可以接收被设置为具有第三逻辑位组

‘

11’的熔丝选择信号fs_sel《2:1》以选择第三熔丝组fs3、可以根据被切断的存储体熔丝bf来生成被设置为逻辑“高”电平的存储体熔丝数据bfd、并且可以根据被切断的使用熔丝uf来生成被设置为具有逻辑“高”电平的使用熔丝数据ufd。在时间点t149之后,当启动结束信号bend根据被设置为具有第四逻辑位组

‘

00’的熔丝选择信号fs_sel《2:1》而被激活时,启动时段信号bpd可以以逻辑“低”电平被禁止以结束启动操作。

93.如图18中所图示的,因为使用熔丝数据ufd在从时间点t143到时间点t145的时段期间维持逻辑“低”电平,所以通过将选择时钟sclk延迟一延迟时段所生成的延迟选择时钟sclkd可以作为资源脉冲rpul被输出。同步于资源脉冲rpul的第一上升沿,脉冲计数信号pcnt的第一比特位pcnt《1》可以从逻辑“低”电平转换为逻辑“高”电平。同步于脉冲计数信号pcnt的第一比特位pcnt《1》的上升沿,资源标志rsf的第一比特位rsf《1》可以从逻辑“低”电平转换为逻辑“高”电平。

94.如图18中所图示的,在从时间点t145到时间点t147的时段期间,使用熔丝数据ufd以逻辑“高”电平生成,并且存储体熔丝数据bfd以逻辑“低”电平生成,使得存储体锁存信号blat的第一比特位blat《1》可以从逻辑“低”电平转换为逻辑“高”电平。在时间点t147之后,使用熔丝数据ufd以逻辑“高”电平生成并且存储体熔丝数据bfd以逻辑“高”电平生成,使得存储体锁存信号blat的第二比特位blat《2》可以从逻辑“低”电平转换为逻辑“高”电平。在资源标志rsf的第一比特位rsf《1》被设置为逻辑“高”电平的情况下当存储体锁存信号blat的第一比特位blat《1》和存储体锁存信号blat的第二比特位blat《2》两者都被设置为具有逻辑“高”电平时,存储体资源标志brsf《2:1》的逻辑位组可以被设置为

‘

11’。当存储体资源标志brsf《2:1》的逻辑位组是

‘

11’时,可以意指:存储体资源标志brsf的第二比特位brsf《2

》和存储体资源标志brsf的第一比特位brsf《1》全部都具有逻辑“高”电平。在启动操作完成之后当执行修复操作时,因为存储体资源标志brsf《2:1》的逻辑位组被设置为

‘

11’,所以可以对第一存储体(未示出)和第二存储体(未示出)执行修复操作。更具体地,在图17中示出的熔丝数据生成电路115d的情况下,因为对第一存储体(未示出)和第二存储体(未示出)两者的修复操作尚未执行,所以通过启动操作可以确认在对第一存储体的修复操作中或在对第二存储体的修复操作中可以使用未使用的第一熔丝组fs1。

95.图19是图示出根据图2中所图示出的半导体器件13a中所包括的熔丝数据生成电路115的另一个示例的熔丝数据生成电路115e的配置的图。如图19中所图示的,熔丝数据生成电路115e可以包括针对修复操作由第一存储体(未示出)和第二存储体(未示出)共用的第一至第三熔丝组fs1~fs3。熔丝数据生成电路115e可以基于熔丝组选择信号fs_sel《2:1》来顺序地选择第一至第三熔丝组fs1~fs3之一。当基于熔丝组选择信号fs_sel《2:1》而选择第一熔丝组fs1时,熔丝数据生成电路115e可以基于未切断的存储体熔丝bf来生成逻辑“低”电平的存储体熔丝数据bfd,并且可以基于被切断的使用熔丝uf来生成逻辑“高”电平的使用熔丝数据ufd。当基于熔丝组选择信号fs_sel《2:1》而选择第二熔丝组fs2时,熔丝数据生成电路115e可以基于被切断的存储体熔丝bf来生成逻辑“高”电平的存储体熔丝数据bfd,并且可以基于被切断的使用熔丝uf来生成逻辑“高”电平的使用熔丝数据ufd。当基于熔丝组选择信号fs_sel而选择第三熔丝组fs3时,熔丝数据生成电路115e可以基于被切断的存储体熔丝bf来生成逻辑“高”电平的存储体熔丝数据bfd,并且可以基于被切断的使用熔丝uf来生成逻辑“高”电平的使用熔丝数据ufd。

96.图20是图示出包括图19中所图示出的熔丝数据生成电路115e的半导体器件13a的操作的时序图。

97.参考图19和图20,当在时间点t151生成启动脉冲bup用于启动操作时,以逻辑“高”电平使能启动时段信号bpd,使得可以执行启动操作,并且在执行启动操作时可以生成选择时钟sclk。熔丝选择信号fs_sel《2:1》的逻辑位组可以同步于选择时钟sclk的上升沿而顺序地改变。在从时间点t153到时间点t155的时段期间,熔丝数据生成电路115e可以接收被设置为具有第一逻辑位组

‘

01’的熔丝选择信号fs_sel《2:1》以选择第一熔丝组fs1、可以根据未切断的存储体熔丝bf来生成被设置为具有逻辑“低”电平的存储体熔丝数据bfd,并且可以根据被切断的使用熔丝uf来生成被设置为具有逻辑“高”电平的使用熔丝数据ufd。在从时间点t155到时间点t157的时段期间,熔丝数据生成电路115e可以接收被设置为具有第二逻辑位组

‘

10’的熔丝选择信号fs_sel《2:1》以选择第二熔丝组fs2、可以根据被切断的存储体熔丝bf来生成被设置为具有逻辑“高”电平的存储体熔丝数据bfd、并且可以根据被切断的使用熔丝uf来生成被设置为具有逻辑“高”电平的使用熔丝数据ufd。在从时间点t157到时间点t159的时段期间,熔丝数据生成电路115e可以接收被设置为具有第三逻辑位组

‘

11’的熔丝选择信号fs_sel《2:1》以选择第三熔丝组fs3、可以根据被切断的存储体熔丝bf来生成被设置为逻辑“高”电平的存储体熔丝数据bfd、并且可以根据被切断的使用熔丝uf来生成被设置为具有逻辑“高”电平的使用熔丝数据ufd。在时间点t159之后,当启动结束信号根据被设置为具有第四逻辑位组

‘

00’的熔丝选择信号fs_sel《2:1》而被激活时,启动时段信号bpd可以以逻辑“低”电平被禁止以结束启动操作。

98.如图20中所图示的,在时间点t153之后,使用熔丝数据ufd维持逻辑“高”电平,并

且资源脉冲rpul、脉冲计数信号pcnt的第一比特位pcnt《1》、脉冲计数信号pcnt的第二比特位pcnt《2》、资源标志rsf的第一比特位rsf《1》、以及资源标志rsf的第二比特位rsf《2》全部都维持逻辑“低”电平,使得存储体资源标志brsf《2:1》的逻辑位组可以被设置为

‘

00’。当存储体资源标志brsf《2:1》的逻辑位组是

‘

00’时,可以意指:存储体资源标志brsf的第二比特位brsf《2》和存储体资源标志brsf的第一比特位brsf《1》全部都处于逻辑“低”电平。因为当启动操作完成时存储体资源标志brsf《2:1》的逻辑位组被设置为

‘

00’,所以不能对第一存储体(未示出)和第二存储体(未示出)执行修复操作。更具体地,因为图19中示出的熔丝数据生成电路115e中不存在未使用的熔丝组,所以通过启动操作可以确认不能对第一存储体(未示出)和第二存储体(未示出)执行修复操作。

99.如上所述,根据目前实施例的半导体器件13a通过启动操作来确认在熔丝组中是否存在至少一个未使用于修复操作的熔丝组,并且可以通过使用未使用的熔丝组来保证对未被执行修复操作的存储体的至少一次的修复操作。

100.已经结合如上所述的一些实施例而公开了概念。本领域技术人员将理解,在不背离本公开的范围和精神的情况下,各种修改、添加以及置换是可能的。因此,应当从说明性立场而并非从限制性立场来考虑在本说明书中公开的实施例。概念的范围不局限于以上描述,而是通过所附权利要求来限定,并且等同范围中的所有不同特征应当被理解为被包括在概念中。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。