1.本技术涉及天线封装领域,尤其涉及一种天线封装体的制作方法以及天线封装体。

背景技术:

2.随着5g高速率通信时代的来临,毫米波通信逐步成为焦点,毫米波天线的设计和应用需求也越来越旺盛。由于毫米波频段传输路径长短对信号幅度损耗影响非常大,且毫米波天线的加工精度要求非常高,因此具有极短天线馈线路径和高加工精度的封装天线技术成为毫米波天线领域的主流技术之一。

3.通常的天线封装技术包括:先以模压树脂包覆芯片后,再进一步加工重布线层(rdl),或者在载具上形成rdl并与芯片暂时结合,再压模成型。上述制作方法通常需要多次配线,会因热效应的产生而提高剥离或歪斜风险;所使用的暂时性结合材料,需要具有高粘度、高耐温、高耐化等特性,材料的使用和贴合制程增加了成本。

技术实现要素:

4.有鉴于此,有必要提供一种减少压合制程、减少成本的天线封装体的制作方法,以解决上述问题。

5.另,还有必要提供一种天线封装体。

6.一种天线封装体的制作方法,包括以下步骤:提供第一中间体,所述第一中间体包括层叠设置的第一线路基板、馈线层以及第二线路基板,所述第二线路基板背离所述馈线层的表面开设有空腔,所述第一线路基板包括天线层;提供第二中间体,所述第二中间体包括第三线路基板以及芯片,所述芯片位于所述第三线路基板的表面;将所述芯片与所述空腔对应设置,压合所述第一中间体与所述第二中间体,形成所述天线封装体。

7.在一些实施方式中,形成所述第二中间体的步骤包括:提供所述第三线路基板,所述第三线路基板包括层叠设置的第三介质层以及第三线路层;以及在所述第三线路基板的一表面电连接所述芯片。

8.在一些实施方式中,所述第三线路层包括铜层,所述铜层沿所述第三线路基板的层叠方向的面积大于所述芯片的面积,所述芯片位于所述铜层的投影面积内。

9.在一些实施方式中,所述第三线路基板背离所述第一中间体的表面为所述第三介质层。

10.在一些实施方式中,所述第一线路基板与所述馈线层通过导电膏电连接,所述导电膏在所述第一中间体的层叠方向上重合。

11.一种天线封装体,包括第一线路基板、馈线层、第二线路基板、第三线路基板以及芯片;第一线路基板包括天线层;馈线层位于所述第一线路基板的一表面;第二线路基板位于所述馈线层背离所述第一线路基板的表面;第三线路基板位于所述第二线路基板背离所述馈线层的表面;芯片内埋于所述第二线路基板中并与所述第三线路基板电连接。

12.在一些实施方式中,所述第一线路基板还包括第一介质层以及第一线路层;所述第一介质层与所述第一线路层层叠设置,所述天线层的至少部分位于所述第一介质层背离所述馈线层的表面。

13.在一些实施方式中,所述天线层包括激励辐射贴片与主辐射贴片,所述激励辐射贴片位于所述第一介质层背离所述馈线层的表面,所述主辐射贴片埋设于所述第一介质层中。

14.在一些实施方式中,所述馈线层包括中间介质层以及中间线路层,所述中间线路层位于所述中间介质层相对两表面并通过贯穿所述中间介质层的导电孔电连接;所述第二线路基板包括层叠设置的第二介质层以及第二线路层,所述第二线路层与所述中间线路层电连接。

15.在一些实施方式中,所述第一线路基板包括第一介质层,所述馈线层包括中间介质层,所述第二线路基板包括第二介质层,其中,所述第一介质层与所述第二介质层的介电常数小于所述中间介质层的介电常数,所述第一介质层与所述第二介质层的介质损耗因素小于所述中间介质层的介质损耗因素。

16.在一些实施方式中,所述第一介质层与所述第二介质层的材质为热塑性树脂;所述中间介质层的材质为热固性树脂。

17.在一些实施方式中,所述第三线路基板突出于所述第二线路基板。

18.本技术提供的天线封装体的制作方法,可以仅通过一次压合形成所述天线封装体,减少压合制程,节约成本,同时减少压合制程带来的风险,例如天线封装体的各个部分剥离或者歪斜;另外,本技术的制作方法,无需采用暂时性结合材料,进一步简化制程,节约成本;再者,本技术将各个元件(包括天线层、接地层、线路层、芯片等)整合在同一天线封装体中,降低了天线封装体中各个元件之间的信号损耗。

附图说明

19.图1为本技术实施例提供的第一线路基板的截面示意图。

20.图2为本技术实施例提供的馈线层的截面示意图。

21.图3为本技术实施例提供的第二线路基板的截面示意图。

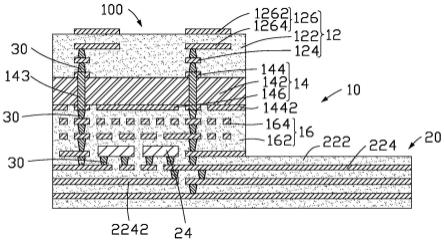

22.图4为本技术实施例提供的包括第一线路基板、馈线层以及第二线路基板的第一中间体的截面示意图。

23.图5为本技术实施例提供的第二中间体的截面示意图。

24.图6为本技术实施例提供的压合图4所示的第一中间体与图5所示的第二中间体得到的天线封装体的截面示意图。

25.主要元件符号说明

[0026][0027][0028]

如下具体实施方式将结合上述附图进一步说明本技术。

具体实施方式

[0029]

为了能够更清楚地理解本技术的上述目的、特征和优点,下面结合附图和具体实施方式对本技术进行详细描述。需要说明的是,在不冲突的情况下,本技术的实施方式及实施方式中的特征可以相互组合。在下面的描述中阐述了很多具体细节以便于充分理解本技术,所描述的实施方式仅仅是本技术一部分实施方式,而不是全部的实施方式。

[0030]

除非另有定义,本文所使用的所有的技术和科学术语与属于本技术的技术领域的技术人员通常理解的含义相同。本文中在本技术的说明书中所使用的术语只是为了描述具体的实施方式的目的,不是旨在于限制本技术。本文所使用的术语“和/或”包括一个或多个相关的所列项目的所有的和任意的组合。

[0031]

在本技术的各实施例中,为了便于描述而非限制本技术,本技术专利申请说明书以及权利要求书中使用的术语“连接”并非限定于物理的或者机械的连接,不管是直接的还是间接的。“上”、“下”、“上方”、“下方”、“左”、“右”等仅用于表示相对位置关系,当被描述对象的绝对位置改变后,则该相对位置关系也相应地改变。

[0032]

请参阅图1至图6,本技术实施例提供一种天线封装体100的制作方法,包括以下步骤:

[0033]

步骤s1:请参阅图1至图4,提供第一中间体10,所述第一中间体10包括层叠设置的第一线路基板12、馈线层14以及第二线路基板16,所述第二线路基板16背离所述馈线层14的表面开设有空腔166。

[0034]

请参阅图1,所述第一线路基板12包括天线层126、第一介质层122以及第一线路层124。所述第一介质层122与所述第一线路层124层叠设置。所述天线层126的至少部分位于所述第一介质层122背离所述馈线层14的表面。

[0035]

请参阅图2,所述馈线层14包括中间介质层142以及中间线路层144,所述中间线路层144位于所述中间介质层142相对两表面并通过贯穿所述中间介质层142的导电孔143电连接。所述中间线路层144与所述第一线路层124电连接。

[0036]

请参阅图3,所述第二线路基板16包括层叠设置的第二介质层162以及第二线路层164,所述第二线路层164与所述中间线路层144电连接。

[0037]

所述空腔166贯穿所述第二介质层162的至少部分。在本实施方式中,所述空腔166还贯穿所述第二线路层164的至少部分。所述空腔166的大小可以根据后续容置的芯片24的体积以及数量进行设置。

[0038]

所述第一介质层122与所述第二介质层162的材质为热塑性树脂;所述中间介质层142的材质为热固性树脂。所述第一介质层122与所述第二介质层162的dk小于中间介质层142的dk,所述第一介质层122与所述第二介质层162的df(介质损耗因素)小于中间介质层142的df,可以降低信号损耗。

[0039]

所述中间介质层142在固化后的模量大于所述第一介质层122以及第二介质层162固化后的模量,所述中间介质层142在后续压合步骤之前固化,可以为后续的压合制程提供刚性支撑,保证压合制程后所得到的天线封装体100的平整度;另外,中间介质层142的厚度选择范围广,可以根据所述天线封装体100满足特定频段需要,调整所述中间介质层142的厚度,从而减小所述第一线路基板12的层叠数,减小加工成本。

[0040]

请参阅图4,形成所述第一中间体10的步骤可以由第一线路基板12、馈线层14以及

第二线路基板16依次叠加后压合而成。在一些实施方式中,压合第一线路基板12、馈线层14以及第二线路基板16的步骤也可以在后续与所述第二中间体20同时压合形成所述天线封装体100,即采用一步压合形成所述天线封装体100。

[0041]

步骤s2:请参阅图5,提供第二中间体20,所述第二中间体20包括第三线路基板22以及芯片24,所述芯片24位于所述第三线路基板22的表面。

[0042]

所述第三线路基板22包括层叠设置的第三介质层222以及第三线路层224。所述芯片24与所述第三线路基板22电连接。所述芯片24突出于所述第三线路基板22的表面。

[0043]

所述第三介质层222的材质可以与所述第二介质层162的材质相同,例如均选择热塑性树脂。

[0044]

所述芯片24的数量可以为一个或多个。当所述芯片24的数量为多个时,多个所述芯片24位于所述第三线路基板22的同一表面。

[0045]

在一些实施方式中,所述第二中间体20可以通过以下步骤形成:

[0046]

步骤s201:提供一第三线路基板22,所述第三线路基板22包括层叠设置的第三介质层222以及第三线路层224。

[0047]

所述第三介质层222与所述第三线路层224的层数并不限制。所述第三线路基板22既用于与所述第一中间体10电连接,又用于与外电路电连接。所述第三线路基板22沿所述第三线路基板22的延伸方向l2(垂直于第三介质层222以及第三线路层224的层叠方向l1)的长度大于所述第一中间体10的长度。

[0048]

步骤s202:在所述第三线路基板22的一表面电连接芯片24。

[0049]

所述芯片24通过导电膏30与所述第三线路层224电连接。在本实施方式中,所述导电膏30贯穿位于所述第三线路基板22表面的一层第三介质层222,从而与所述芯片24电连接。其中,所述导电膏30可以是铜膏或者锡膏。

[0050]

步骤s3:请参阅图6,将所述芯片24与所述空腔166对应设置,压合所述第一中间体10与所述第二中间体20,形成所述天线封装体100。

[0051]

在一些实施方式中,所述芯片24与第二线路层164以及第三线路层224中线路密度较高的区域错开,防止压合制程中芯片24以及线路层(包括第二线路层164以及第三线路层224)产生偏移。另外,所述中间线路层144与第三线路层224包括大面积的铜层146、2242与所述芯片24相对应,其中,沿层叠方向l1,所述铜层146、2242的面积大于所述芯片24的面积,压合制程中,所述芯片24位于所述铜层146、2242的投影面积内,防止芯片24以及线路层(包括第二线路层164以及第三线路层224)产生偏移。

[0052]

请参阅图6,本技术还提供一种天线封装体100,包括第一中间体10与第二中间体20,所述第一中间体10与所述第二中间体20层叠设置。

[0053]

所述第一中间体10包括层叠设置的第一线路基板12、馈线层14与第二线路基板16。

[0054]

所述第一线路基板12包括天线层126、第一介质层122以及第一线路层124。所述第一介质层122与所述第一线路层124层叠设置。所述天线层126的至少部分位于所述第一介质层122背离所述馈线层14的表面。

[0055]

在一些实施方式中,所述天线层126包括激励辐射贴片1262与主辐射贴片1264,所述激励辐射贴片1262位于所述第一介质层122背离所述馈线层14的表面,所述主辐射贴片

1264埋设于所述第一介质层122中,所述主辐射贴片1264与所述激励辐射贴片1262相距设置,所述主辐射贴片1264与所述第一线路层124电连接。

[0056]

所述馈线层14包括中间介质层142以及中间线路层144,所述中间线路层144位于所述中间介质层142相对两表面并通过贯穿所述中间介质层142的导电孔143电连接。所述中间线路层144与所述第一线路层124电连接。其中,所述中间线路层144包括接地层1442,所述接地层1442位于所述中间介质层142背离所述第一线路基板12的表面。

[0057]

在一些实施方式中,所述主辐射贴片1264与所述激励辐射贴片1262之间的距离可以为100μm-500μm;所述激励辐射贴片1262与所述接地层1442之间的距离可以为300μm-900μm。

[0058]

所述第二线路基板16包括层叠设置的第二介质层162以及第二线路层164,所述第二线路层164与所述中间线路层144电连接。

[0059]

在一些实施方式中,所述第一线路层124、中间线路层144以及第二线路层164之间通过导电膏30电连接,均无需设置其他用于电连接的连接头,可以降低信号损失。所述导电膏30可以是铜膏或者锡膏。

[0060]

在一些实施方式中,用于电连接第一线路层124以及中间线路层144的导电膏30在层叠方向l1上重合(即采用叠孔的方式),可以减少第一中间体10的寄生参数。

[0061]

所述第一介质层122与所述第二介质层162的材质为热塑性树脂;所述中间介质层142的材质为热固性树脂。所述第一介质层122与所述第二介质层162的dk小于中间介质层142的dk,所述第一介质层122与所述第二介质层162的df小于中间介质层142的df,可以降低信号损耗。

[0062]

所述中间介质层142在固化后的模量大于所述第一介质层122以及第二介质层162固化后的模量,所述中间介质层142在后续压合步骤之前固化,可以为后续的压合制程提供刚性支撑,保证压合制程后所得到的天线封装体100的平整度;另外,中间介质层142的厚度选择范围广,可以根据所述天线封装体100满足特定频段需要,调整所述中间介质层142的厚度,从而减小所述第一线路基板12的层叠数,减小加工成本。

[0063]

所述第二中间体20与所述第二线路基板16邻接。所述第二中间体20包括第三线路基板22与芯片24,所述芯片24位于所述第三线路基板22的表面并内埋于所述第二线路基板16中。

[0064]

所述第三线路基板22的所述第三线路基板22的延伸方向l2的长度大于所述第一中间体10的长度,即所述第三线路基板22突出于所述第一中间体10。所述第三线路基板22可以直接用于与外电路进行电连接,无需再额外设置用于电连接的连接头等,可以降低信号损失。

[0065]

所述第三线路层224可以通过导电膏30与所述芯片24以及所述第二线路层164电连接。

[0066]

在一些实施方式中,所述第三线路基板22背离所述第一中间体10的表面为所述第三介质层222,位于最外层的第三介质层222可以作为绝缘保护层,可以减少形成其他保护层的步骤。

[0067]

本技术提供的天线封装体100的制作方法,可以仅通过一次压合形成所述天线封装体100,减少压合制程,节约成本,同时减少压合制程带来的风险,例如天线封装体100的

各个部分剥离或者歪斜;另外,本技术的制作方法,无需采用暂时性结合材料,进一步简化制程,节约成本;再者,本技术将各个元件(包括天线层126、接地层1442、线路层、芯片24等)整合在同一天线封装体100中,降低了天线封装体100中各个元件之间的信号损耗。

[0068]

以上实施方式仅用以说明本技术的技术方案而非限制,尽管参照以上较佳实施方式对本技术进行了详细说明,本领域的普通技术人员应当理解,可以对本技术的技术方案进行修改或等同替换都不应脱离本技术技术方案的精神和范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。